Изобретение относится к области автоматики и измерительной техники и предназначено для сравнения двух независимых частот.

Известны цифровые схемы сравнения частот, содержащие два накопительных счетчика или два сдвигающих регистра, выходы которых подключены к цифровой схеме сравнения кодов, наличие которых значительно усложняет устройство [1]

Наиболее близким по технической сущности к заявляемому изобретению является цифровой частотный дискриминатор [2] который содержит два формирователя импульсов, выход которых через входную логику (схемы И, ИЛИ и три тригера) подключены к двум счетчикам импульсов. Выходы счетчиков через логику подключены к тригеру Знак, состояние которого указывает какая из двух частот больше. Разность частот в зависимости от знака получается либо на одном, либо на другом счетчике.

Данный дискриминатор не является функционально завершенным узлом, так как цикл сравнения начинается с запускающего сигнала, для формирования которого требуется дополнительное оборудование, кроме того, ограничен диапазон сравнения частот, так как разность частот Δf между частотой сигнального fс и частотой опорного fо колебаний не верна если fс > 2fо. Результат сравнения (разность частот) получается то на одном, то на другом счетчике, что затрудняет съем информации и, кроме того, схема дискриминатора несколько усложнена.

Решаемая задача направлена на создание простой, технологичной, функционально завершенной схемы цифрового дискриминатора, работающего в широком диапазоне частот без дополнительного оборудования.

Поставленная задача решается устройством, содержащим первый и второй счетчик импульсов, первый и второй формирователи импульсов, три тригера, логический элемент И, отличающимся тем, что второй счетчик выполнен с предварительной установкой и в устройство введен дешифратор, входы которого подключены к выходам первого счетчика, счетный вход которого подключен к выходу первого формирователя, первый выход дешифратора подключен к первым входам первого и второго тригеров и к первому управляющему входу второго счетчика; второй выход дешифратора к первому входу третьего тригера, третий выход дешифратора ко второму входу этого тригера, выход которого подключен ко второму управляющему входу второго счетчика, выход которого подключен ко второму входу первого тригера и к одному из входов логического элемента И, другой вход которого подключен к выходу первого тригера, а выход подключен ко второму входу второго тригера, счетный вход второго счетчика подключен к выходу второго формирователя импульсов, а информационные входы второго счетчика подсоединены к потенциалам логической 1 или логического 0.

Выполнение второго счетчика с предварительной установкой позволяет уйти от традиционного способа сравнения частот, где подсчет импульсов для сравнения кодов ведется за одинаковый промежуток времени.

Время счета второго счетчика меньше, так как счет начинается не с нулевого состояния. Полученная разница во времени позволяет получить управляющие сигналы для синхронизации работы дискриминатора путем дешифрации выходных сигналов состояния первого счетчика и таким образом исключаются дополнительные элементы и упрощается схема дискриминатора.

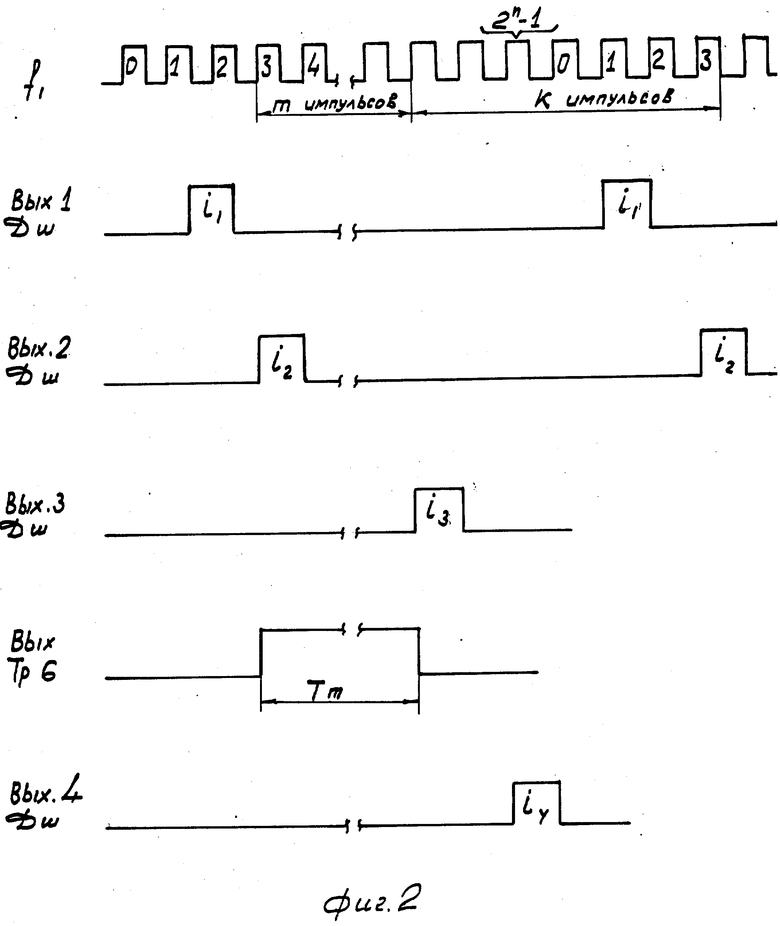

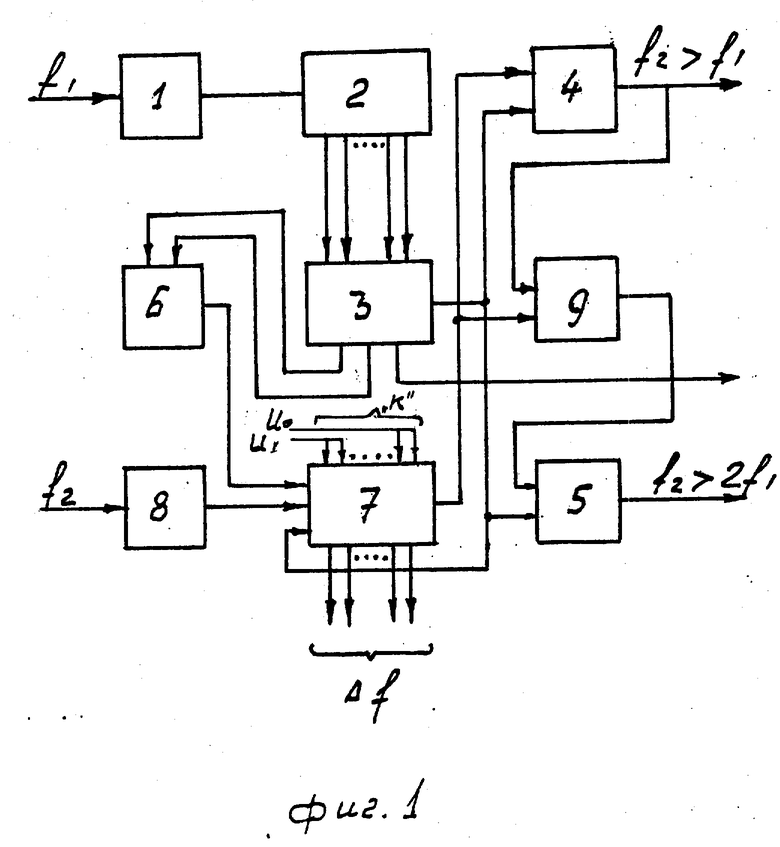

На фиг. 1 приведена функциональная схема цифрового частотного дискриминатора; на фиг. 2 временная диаграмма.

Устройство содержит первый формирователь 1, первый счетчик 2, дешифратор 3, первый тригер 4, второй тригер 5, третий тригер 6, второй счетчик 7, второй формирователь 8 и логический элемент И 9.

Выход формирователя 1 соединен с счетным входом счетчика 1, выходы которого соединены с входами дешифратора 3. Первый выход дешифратора подключен на входы сброса тригеров 4 и 5 и управляющий вход предустановки счетчика 7. Второй выход дешифратора соединен с входом установки тригера 6, выход которого соединен с входом разрешения счета счетчика 7, счетный вход счетчика 7 соединен с выходом формирователя 8. Выход переноса счетчика 7 соединен с первым входом логического элемента И 9 и с установочным входом тригера 4.

Выход тригера 4 соединен со вторым входом логического элемента И 9, выход которой соединен с входом установки тригера 5. Информационные входы (Д-входы) счетчика 7 подключены к потенциалам логического 0 U0 или логической 1 U1. Таким образом формируется двоичное число k.

Устройство работает следующим образом.

Сигнал с частотой f1 поступает через формирователь 1 на счетчик 2, который работает в неуправляемом режиме. Дешифратор 3 вырабатывает четыре управляющих импульса i1-in (см. фиг. 2). По импульсу i1 происходит сброс тригеров 4 и 5 в исходное состояние и занесение в счетчик 7 двоичного числа k. Далее импульс i2 устанавливает в 1 тригер 6, который сбрасывается импульсом i3. Тригер 6 формирует временной интервал Tm, в течение которого ведется подсчет импульсов с частотой f2 счетчиком 7. Двоичные числа k и m связаны соотношением k + m 2n, где: n разрядность каждого счетчика, m число равное разности i3-i2, k равно или больше числа управляющих импульсов.

Если частота f2>f1, то в течение интервала Tm счетчик 7 переполнится и возникнет импульс переноса, который установит тригер 4, далее счетчик обнулится и продолжит счет. После окончания интервала Tm на счетчике 7 будет находиться двоичный прямой код разности частот Δf f2 f1, а тригер 4 будет в состоянии 1.

Если частота f2>2f1, то возникнет больше одного переполнения и установится дополнительно тригер 5.

Если частота f2<f1, то в течение интервала Tm счетчик 7 не переполняется, тригер 4 остается в состоянии 0 и по окончании интервала на счетчике 7 будет находиться разность частот Δf f1-f2 в обратном двоичном коде.

Во временном интервале между импульсами i3 и i1 на счетчике 7 и тригерах 4 и 5 находится результат сравнения частот, который можно фиксировать по импульсу i4 (строб результата).

После импульса i4 цикл сравнения повторяется. Таким образом происходит непрерывное сравнение частот двух независимых колебаний.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ ИЗМЕРИТЕЛЬНОГО ИНТЕРВАЛА ВРЕМЕНИ ДЛЯ ЦИФРОВЫХ ТАХОМЕТРОВ | 2000 |

|

RU2171474C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1712961A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФИЗИЧЕСКОГО ПАРАМЕТРА В СКВАЖИНЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013534C1 |

| УСТРОЙСТВО ДЛЯ ПСИХОЛОГИЧЕСКИХ ИССЛЕДОВАНИЙ | 2000 |

|

RU2195172C2 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЭЛЕКТРОМАГНИТНОЙ ОБСТАНОВКИ | 1995 |

|

RU2126975C1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Цифровой частотный детектор | 1979 |

|

SU815863A1 |

Изобретение относится к области автоматики и измерительной техники и может быть использовано для сравнения двух независимых частот. Технический результат изобретения - создание простой, технологичной, функционально завершенной схемы цифрового дискриминатора, работающего в широком диапазоне частот без дополнительного оборудования. Схема содержит первый и второй счетчики импульсов, два формирователя импульсов, три тригера, логический элемент И, при этом второй счетчик выполнен с предварительной установкой и в устройство введен дешифратор, входы которого подключены к выходам первого счетчика, счетный вход которого подключен к выходу первого формирователя, первый выход дешифратора подключен к первым входам первого и второго тригеров и к первому управляющему входу второго счетчика; второй выход дешифратора - к первому входу третьего тригера, третий выход дешифратора - ко второму входу этого тригера, выход которого подключен ко второму управляющему входу второго счетчика, выход которого подключен ко второму входу первого тригера и к одному из входов логического элемента И, другой вход которого подключен к выходу первого тригера, а выход подключен ко второму входу второго тригера, счетный вход второго счетчика подключен к выходу второго формирователя импульсов, а информационные входы второго счетчика подсоединены к потенциалам логической 1 или логического 0. 2 ил.

Цифровой частотный дискриминатор, содержащий первый и второй счетчики импульсов, первый и второй формирователи импульсов, три триггера, логический элемент И, отличающийся тем, что в него введен дешифратор, а второй счетчик импульсов выполнен в виде счетчика импульсов с предварительной установкой, при этом входы дешифратора подключены к соответствующим выходам первого счетчика импульсов, счетный вход которого подключен к выходу первого формирователя импульсов, первый выход дешифратора подключен к первым входам первого и второго триггеров и к первому управляющему входу второго счетчика импульсов с предварительной установкой, второй выход дешифратора подключен к первому входу третьего триггера, третий выход дешифратора подключен к второму входу триггера, выход которого подключен к второму управляющему входу второго счетчика импульсов с предварительной установкой, выход которого подключен к второму входу первого триггера и одному из входов логического элемента И, другой вход которого подключен к выходу первого триггера, а выход к второму входу второго триггера, счетный вход второго счетчика импульсов с предварительной установкой подключен к выходу второго формирователя импульсов, а информационные входы второго счетчика импульсов с предварительной установкой являются входами сигналов логической единицы и логического нуля.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПОРОГОВЫЙ РЕГИСТРАТОР | 0 |

|

SU354522A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой частотный дискриминатор | 1974 |

|

SU484620A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1997-10-20—Публикация

1995-09-12—Подача