Изобретение относится к области измерительной техники и может быть использовано для помехоустойчивого измерения параметров сигнала в различных радиотехнических устройствах и системах, например, в цифровой аппаратуре потребителя глобальных навигационных спутниковых систем.

Известен способ измерения фазового сдвига, основанный на формировании ограниченного измеряемого сигнала и квадратурных составляющих опорного сигнала, логического перемножения импульсов, соответствующих измеряемому сигналу и квадратурным составляющим опорного сигнала, формировании квантующих импульсов, подсчете числа квантующих импульсов, совпавших с последовательностью импульсов, сформированных в результате указанного логического перемножения, и вычислении фазового сдвига.

Известен цифровой измеритель фазового сдвига, содержащий формирующий узел, первый и второй логические элементы, первый и второй реверсивный счетчики, генератор образцового напряжения, узел управления, генератор импульсов и микропроцессорный вычислительный блок, причем вход формирующего узла подключен ко входу измеряемого сигнала, а выход к первым входам первого и второго логических элементов, выходы генератора образцового напряжения подключены ко вторым входом логических элементов и к первому входу узла управления, выход которого подключен к управляющему входу микропроцессорного вычислительного блока, выходы логических элементов подключены к управляющим входам реверсивных счетчиков, выходы которых подключены информационным входам микропроцессорного вычисляемого блока, выходы генератора импульсов подключены счетным входам реверсивных счетчиков и к узлу управления. [1, с. 130]

Общим недостатком этого способа и устройства является низкая точность измерения фазового сдвига при отношениях сигнал-шум более единицы. Как показано в [1, c. 116] в цифровых измерителях фазового сдвига этого класса систематическая погрешность может достигать 4,07o. Кроме этого, недостатком способа и устройства является низкая точность измерения при воздействии сосредоточенных по спектру помех или при обработке многочастотных сигналов. Эти недостатки связаны с тем, что в данных способе и устройстве используется ограничение опорного сигнала. Широкий спектр ограниченного сигнала приводит к появлению в спектре сигналов, поступающих на вычисление фазового сдвига, составляющих, которые приводят к появлению больших погрешностей и снижают помехоустойчивость.

Известен также способ, взятый в качестве прототипа, основанный на дискретизации измеряемого сигнала и его преобразовании в цифровую форму, формировании цифровых квадратурных составляющих опорного сигнала, перемножении цифровых измеряемого сигнала и квадратурных составляющих опорного сигнала, суммировании результатов перемножения за время измерения и вычислении фазового сдвига.

Известен также цифровой измеритель фазового сдвига, также взятый в качестве прототипа, содержащий последовательно включенные узел выборки и хранения, аналого-цифровой преобразователь, накопитель, первый узел перемножения, включающий в себя собственно перемножитель, накапливающий сумматор и буферный регистр памяти, а также микропроцессорный вычислительный блок, блок синхронизации, блок цифрового опорного сигнала, второй перемножитель, также включающий в себя собственно перемножитель, накапливающий сумматор и буферный регистр памяти, причем вход узла выборки и хранения подключен к входу измеряемого сигнала, выход блока синхронизации подключен к входам синхронизации узла выборки и хранения, накопителя и блока цифрового опорного сигнала, выходы блока цифрового опорного сигнала подключены ко вторым входам перемножителей, выход накопителя подключен также к первому входу второго перемножителя, а выходы перемножителей подключены к информационным входам микропроцессорного вычислительного блока [1, с. 143 прототип]

Эти способ и устройство имеют недостаток, который заключается в ограничении сверху частотного диапазона измеряемого сигнала. Это связано с невысоким быстродействием логических операций, в частности операций перемножения и суммирования, выполняемых перемножителями и накапливающими сумматорами. Так, при их быстродействии порядка 0,1 мкс и числе точек дискретизации за период сигнала, равном десяти, верхняя рабочая частота этого цифрового измерителя фазового сдвига составит 1 МГц. Это существенно ограничивает возможности цифрового измерения фазового сдвига, так как имеется необходимость увеличения частотного диапазона до десятков мегагерц и выше.

Как видно из анализа рассмотренных способов и устройств измерения фазового сдвига, они имеют ряд недостатков, не позволяющих производить высокоточное измерение фазового сдвига в широком диапазоне частот.

В основу изобретения положена задача расширения частотного диапазона путем, с одной стороны, использования неограниченного опорного сигнала (без использования операции ограничения опорного сигнала), а, с другой стороны, исключения операции перемножения измеряемого и опорного сигнала, при этом дополнительно предусматриваются меры по снижению требований к быстродействию операции суммирования.

Поставленная задача решается тем, что в способе измерения фазового сдвига, основанном на дискретизации измеряемого сигнала и его преобразовании в цифровой сигнал, суммировании кодов и вычислении фазового сдвига, согласно изобретению, формируют группы из взятых последовательно n выборок дискретизированного цифрового измеряемого сигнала, кроме того, с частотой дискретизации, уменьшенной в n раз, формируют одно- или многоразрядные цифровые сигналы, зависящие от группы n выборок дискретизированиого цифрового измеряемого сигнала и номера группы n выборок цифровых синусной и косинусной составляющих опорного сигнала, которые поступают на суммирование кодов.

Поставленная задача решается тем, что устройство, содержащее аналого -цифровой преобразователь, вход которого является входом устройства, блок синхронизации, подключенный по первому выходу синхронизации к аналого-цифровому преобразователю, включенные последовательно два накапливающих сумматора, два регистра памяти и микропроцессорный вычислительный блок, согласно изобретению, дополнительно снабжено регистром сдвига, информационный вход которого подключен к выходу аналого-цифрового преобразователя, вход синхронизации подключен к первому выходу синхронизации блока синхронизации, запоминающим устройством, два информационных выхода которого подключены к информационным входам накапливающих сумматоров, первым дополнительным регистром памяти, информационный вход которого подключен к шине данных микропроцессорного вычислительного блока, а выход к первому адресному входу запоминающего устройства, вход "запись" подключен к выходу "запись" микропроцессорного вычислительного блока, а также вторым дополнительным регистром памяти, информационный вход которого подключен к выходу регистра сдвига, а выход ко второму адресному входу запоминающего устройства, и счетчиком, информационные выходы которого подключены к третьему адресному входу запоминающего устройства, вход предустановки кода подключен к дополнительному информационному выходу запоминающего устройства, а информационный вход подключен ко второму информационному выходу первого дополнительного регистра памяти, причем второй выход синхронизации блока синхронизации подключен ко входам синхронизации накапливающих сумматоров, дополнительного регистра памяти и счетчика, а третий выход синхронизации блока синхронизации подключен ко входу сброса накапливающих сумматоров, входу синхронизации регистров памяти и входу "запрос прерывания" микропроцессорного вычислительного блока, выход "чтение" которого подключен к входам "чтение" двух регистров памяти.

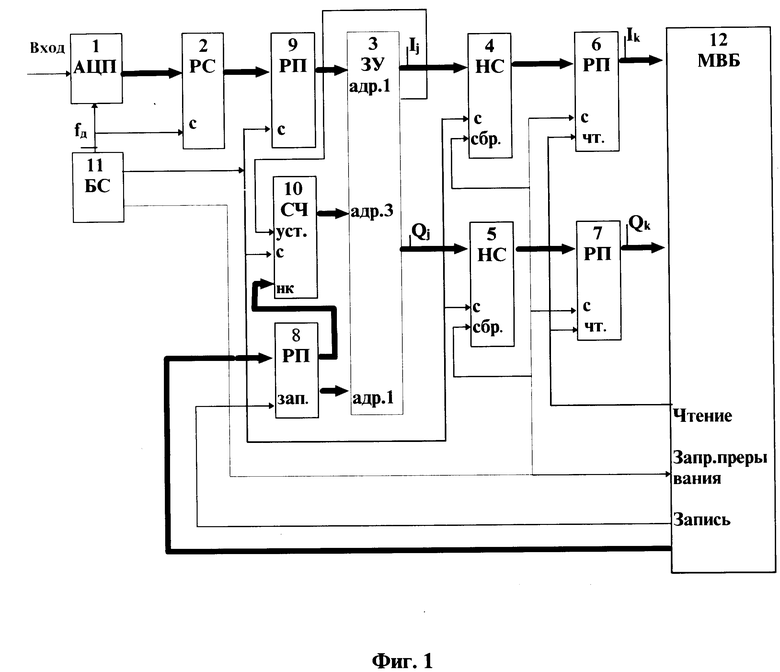

На фиг. 1 приведена структурная схема устройства для осуществления способа, на фиг. 2 структурная схема накапливающего сумматора, на фиг. 3 структурная схема микропроцессорного вычислительного блока, на фиг. 4 - алгоритм работы микропроцессорного вычислительного блока.

Устройство для осуществления способа (фиг. 1) содержит аналого -цифровой преобразователь 1, вход которого является входом устройства; регистр сдвига 2, информационный вход которого подключен к выходу аналого-цифрового преобразователя 1; запоминающее устройство 3; первый 4 и второй 5 накапливающие сумматоры, информационные входы которых подключены соответственно к первому и второму информационным выходам запоминающего устройства 3; первый 6 и второй 7 регистр памяти, информационные входы которых подключены к информационным выходам соответственно накапливающих сумматоров 4 и 5; третий регистр памяти 8, первый информационный выход которого подключен к первому адресному входу запоминающего устройства 3; четвертый регистр памяти 9, информационный вход которого подключен к выходу регистра сдвига 2, а выход ко второму адресному входу запоминающего устройства 3; счетчик 10, информационный вход которого подключен ко второму информационному выходу регистра памяти 8, а информационный выход подключен к третьему адресному входу запоминающего устройства 3, а вход предустановки кода к дополнительному выходу запоминающего устройства 3; блок синхронизации II, первый выход которого подключен ко входам синхронизации аналого-цифрового преобразователя 1 и регистру сдвига 2, второй выход ко входам синхронизации накапливающих сумматоров 4 и 5, регистра памяти 9 и счетному входу счетчика 10, а третий выход к входам синхронизации начала-окончания накопления накапливающих сумматоров 4 и 5 и регистров памяти 6 и 7; и микропроцессорный вычислительный блок 12, шина данных которого подключена к выходу регистров памяти 6 и 7 и информационному входу регистра памяти 8, вход "запрос прерывания" подключен к третьему выходу блока синхронизации 11, выход "запись" к входу "запись" регистра памяти 8, а выход "чтение" ко входам "чтение" регистров памяти 6 и 7.

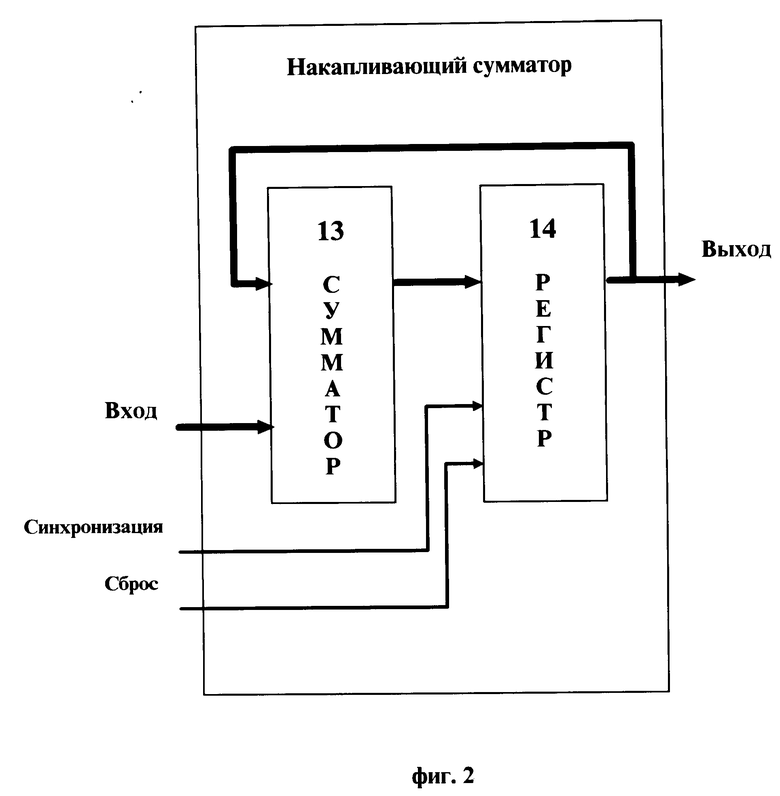

Накапливающий сумматор, приведенный на фиг. 2, состоит из многоразрядного сумматора 13 и регистра памяти 14, причем первый информационный вход сумматора 13 является информационным входом накапливающего сумматора, а второй информационный вход сумматора подключен к выходу регистра 14, который также является информационным выходом накапливающего сумматора, вход синхронизации и регистра 14 является входом синхронизации накапливающего сумматора.

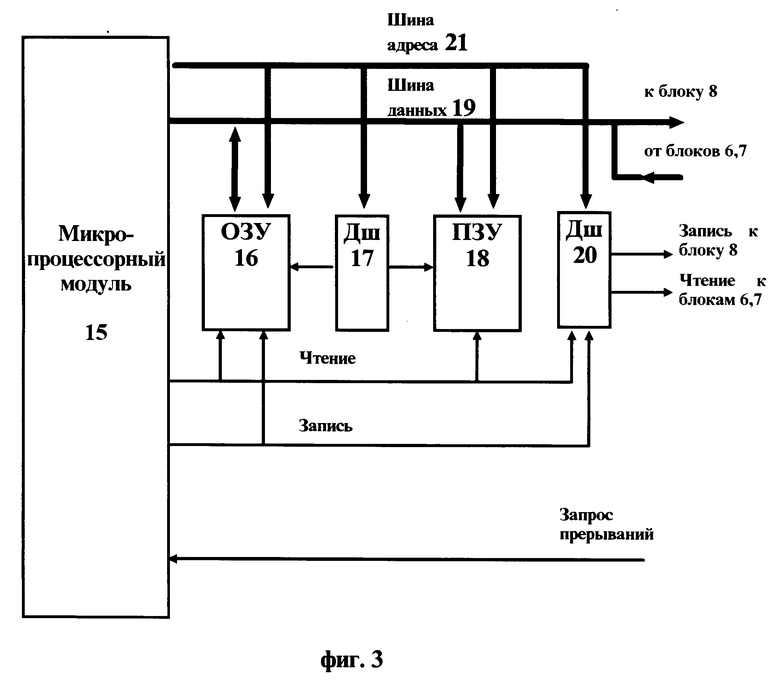

Микропроцессорный вычислительный блок, приведенный на фиг. 3, состоит из микропроцессорного модуля 15, оперативного запоминающего устройства 16, первого дешифратора 17, постоянного запоминающего устройства 18, шины данных 19, связывающей микропроцессорный модуль 15 с оперативным 16 и постоянным 18 запоминающими устройствами и являющейся информационными выходами и информационным входом микропроцессорного вычислительного блока, второго дешифратора 20, шины адреса 21, связывающей микропроцессорный модуль 15 с оперативным 16 и постоянным 18 запоминающими устройствами, первым 17 и вторым 20 дешифраторами, причем выходы дешифратора 17 подключены к оперативному 16 и постоянному 18 запоминающим устройствам, выходы дешифратора 20 являются выходами "запись" и "чтение" микропроцессорного вычислительного блока, выход "запись" микропроцессорного модуля 15 подключен к входам оперативного запоминающего устройства 16 и дешифратора 20, а выход "чтение" подключен к соответствующим входам оперативного 16 и постоянного 18 запоминающих устройств и дешифратора 20, а вход "запрос прерывания" микропроцессорного модуля является входом "запрос прерывания" микропроцессорного вычислительного блока.

Устройство для осуществления способа работает следующим образом. Измеряемый сигнал поступает на аналого -цифровой преобразователь (АЦП) 1, который преобразует его в цифровую форму с частотой дискретизации fд. Импульсы синхронизации с первого выхода блока синхронизации 11 с частотой fд поступают на аналого-цифровой преобразователь 1. Цифровой дискретизированный (с частотой fд) сигнал с выхода АЦП 1 подается на регистр сдвига (PC) 2, записывается в первую ячейку регистра сдвига 2 и продвигается с частотой fд. Регистр сдвига содержит n многоразрядных (по числу разрядов АЦП 1) ячеек, т.е. через n тактов информация в регистре сдвига 2 полностью обновляется. Через каждые n тактов импульсами синхронизации со второго выхода блока синхронизации 11, следующими с частотой fд/n, информация, записанная в n ячейках регистра сдвига 2, переписывается в регистр памяти 9, который является буферным между регистром сдвига 2 и запоминающим устройством 3.

Информация, представляющая из себя группу n выборок дискретизированного цифрового измеряемого сигнала, поступает на один из трех адресных входов запоминающего устройства 3. Одновременно с информационного выхода счетчика 10 на другой адресной вход запоминающего устройства 3 поступает код номера группы n выборок цифровых синусных и косинусных составляющих опорного сигнала (ОС). Кроме того, на третий адресной вход запоминающего устройства 3 от микропроцессорного вычислительного блока 12 через буферный регистр памяти 8 поступает информация о значении частоты опорного сигнала, т.е. код частоты ОС.

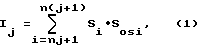

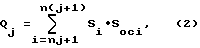

Формирование кода номера группы n выборок опорных сигналов производится путем подсчета счетчиком 10 импульсов, поступающих со второго выхода блока синхронизации 11. Эти импульсы имеют частоту fд/n, где n число выборок измеряемого сигнала в группе. Зная номер группы j и частоту f0 OC, можно определить фазу синусной и косинусной составляющих OC на момент времени tj= tд•n•j, где tд l/fд. По кодам частоты f0 OC с выхода регистра памяти 8, номеру группы j с выхода счетчика 10 и по комбинации кодов в группе n выборок дискретизированного цифрового измеряемого сигнала с выхода регистра памяти 9 определяются номера ячеек запоминающего устройства 3, в которых хранятся коды, соответствующие суммам:

где

Sosi = sin(2πfoitд) (3)

Soci = cos(2πfoitд) (4)

В выражениях (3), (4)

tд=1/fд

Для фиксированной частоты f0 и фиксированного номера группы j значения (коды) Ii и Qj зависят от комбинации n значений Si в j-ой группе n выборок дискретизированного цифрового измеряемого сигнала. Учитывая, что выборка сигнала Si является m - разрядной, число таких комбинаций равно

M 2mn,

где m- число разрядов дискретизированного цифрового сигнала с выхода АЦП 1.

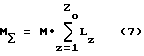

Общее число ячеек запоминающего устройства 3 MΣ будет определяться числом комбинаций M в соответствии с (6), числом частот Z0 OC и числом неповторяющихся групп Lz значений S0ci и S0si (3, 4) для каждой частоты f0z опорного сигнала.

Например, для m= 3 (трехразрядный АЦП), n=4, Z0=10, Lz=100 значение MΣ составит: MΣ 212•103 4096000 или 4 МБ, что для современного этапа развития элементной базы запоминающих устройств является вполне достижимым.

Далее коды, соответствующие Ij и Qj, с тактом fд/n поступают на накапливающие сумматоры 4 и 5, где суммируются в течение некоторого времени Tu, равного длительности K тактов, т.е.

Tu K•n•tд,

где tд определяется в соответствии с (5).

С точки зрения минимизации построения аппаратуры число тактов K=Tu/ntд, от которых зависит разрядность накапливающих сумматоров 4 и 5, должно быть минимальным. Минимальное число тактов накопления определяется только возможностями микропроцессорного вычислительного блока 12. В пределе, коды, соответствующие Ij и Qj, могут непосредственно передаваться для окончательного суммирования в микропроцессорный вычислительный блок 12. Но при этом загрузка микропроцессорного вычислительного блока по запросу прерывания существенно увеличивается.

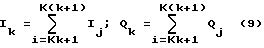

Полученные в результате накопления в накапливающих сумматорах коды

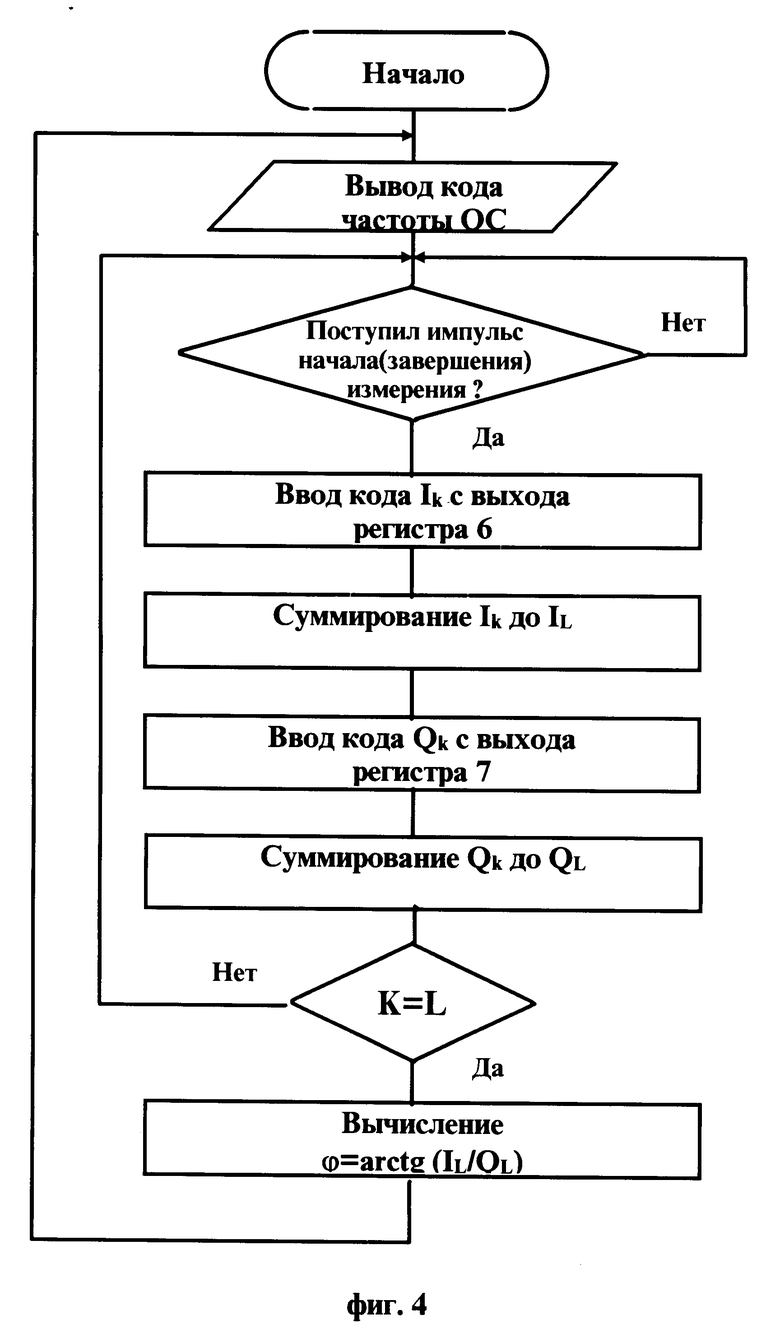

где k номер интервала накопления кодов в накапливающих сумматорах 4 и 5, передаются по окончании накопления через буферные регистры памяти 6 и 7 в микропроцессорный вычислительный блок 12, где производится дополнительное суммирование Ik и Qk, например, P раз.

По полученным значениям I и Q, равным

производится вычисление фазового сдвига по формуле

Φ = arctg(I/Q). (11)

Моменты окончания накопления в накапливающих сумматорах определяются импульсами синхронизации окончания (начала) времени накопления, поступающих на накапливающие сумматоры 4 и 5, регистры памяти 6 и 7 и микропроцессорный вычислительный блок 12 с третьего выхода блока синхронизации 11.

Номер группы j задается счетчиком 10, на счетный вход которого поступают импульсы со второго выхода блока синхронизации 11 с частотой fд/n. Число неповторяющихся значений OC для разных частот может быть разным. Поэтому с ячейки запоминающего устройства 3, в которой записан код последнего в реализации для данной частоты OC значения опорного сигнала, формируется импульс, который поступает на предустановку счетчика 10. Код, в который следует установить счетчик 10, чтобы обеспечить перебор реализации ОС для данной частоты OC, подается на информационный вход счетчика 10 со второго информационного выхода регистра 8.

Аналого-цифровой преобразователь 1 представляет из себя классический АЦП. Следует отметить, что в качестве АЦП может быть использован ограничитель (компаратор) одноразрядный АЦП.

Накапливающий сумматор 4 (5) может быть выполнен в соответствии со структурной схемой, приведенной на фиг. 2.

Блок синхронизации 11 представляет из себя последовательно включенный опорный генератор с частотой fд, делитель на n и дополнительный делитель, формирующий импульсы синхронизации начала-окончания накопления.

Микропроцессорный вычислительный блок 12 выполняется в соответствии с фиг. 3 по классической структуре и работает по алгоритму, приведенному на фиг.4.

Ограничения по расширению вверх частотного диапазона применения предложенного способа и устройства для его осуществления определяются только быстродействием операции запоминания n выборок дискретизированного цифрового измеряемого сигнала (регистра сдвига 2), операцией аналого-цифрового преобразования (АЦП (компаратора) 1), которые работают с частотой fд, и информационной емкостью (разрядностью адреса) запоминающего устройства 3. Влияние информационной емкости (разрядности) запоминающего устройства 3 на расширение частотного диапазона связано с тем, что при уменьшении требований к быстродействию элементов устройства в n раз (кроме АЦП 1 и регистра сдвига 2), достигаемого путем параллельной обработки n выборок входного сигнала, запомненных в регистре сдвига 2, требуется увеличивать информационную емкость запоминающего устройства 3 в 2n раз. Существующая элементная база позволяет производить обработку сигналов с частотами до 50-100 МГц и выше.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1995 |

|

RU2089920C1 |

| ПЕЛЕНГАТОР | 1995 |

|

RU2099732C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182724C2 |

| Устройство контроля веществ | 2016 |

|

RU2618488C1 |

| УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 2000 |

|

RU2182358C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ АМПЛИТУДЫ СИГНАЛА | 2000 |

|

RU2212676C2 |

| Устройство для задания фазового сдвига | 1990 |

|

SU1721537A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДВУМЕРНЫХ РАСПРЕДЕЛЕНИЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2003 |

|

RU2253892C1 |

| СПОСОБ ФОРМИРОВАНИЯ ДИАГРАММЫ НАПРАВЛЕННОСТИ | 1993 |

|

RU2072525C1 |

| Устройство контроля веществ | 2016 |

|

RU2632633C1 |

В настоящее время является актуальной задача высокоточного и помехоустойчивого измерения фазового сдвига в широком диапазоне частот. Недостатком известных способов и устройств для высокоточного и помехоустойчивого измерения фазового сдвига является ограниченный сверху диапазон частот. В предложенном способе этот недостаток устраняется путем исключения операции перемножения и уменьшения требований по быстродействию к операции суммирования. Сущность предложенного способа заключается в том, что в способе измерения фазового сдвига, основанном на дискретизации измеряемого сигнала и его преобразовании в цифровой сигнал, суммировании кодов и вычислении фазового сдвига, формируют группы из взятых последовательно n выборок дискретизированного цифрового измеряемого сигнала, кроме того, с частотой дискретизации, уменьшенной в n раз, формируют одно- или многоразрядные цифровые сигналы, зависящие от группы n выборок дискретизированного цифрового измеряемого сигнала и номера группы n выборок цифровых синусной и косинусной составляющих опорного сигнала, которые поступают на суммирование их кодов. Сущность предложенного устройства для осуществления способа заключается в том, что известное устройство, содержащее аналого-цифровой преобразователь, вход которого является входом устройства, блок синхронизации, подключенный по первому выходу синхронизации к аналого -цифровому преобразователю, включенные последовательно два накапливающих сумматора, два регистра памяти и микропроцессорный вычислительный блок, дополнительно снабжено регистром сдвига, информационный вход которого подключен к выходу аналого-цифрового преобразователя, вход синхронизации подключен к первому выходу синхронизации блока синхронизации, дополнительным регистром памяти, информационный вход которого подключен к выходу регистра сдвига, запоминающим устройством, первый адресный вход которого подключен к выходу дополнительного регистра памяти, а два информационных выхода подключены к информационным входам накапливающих сумматоров, а также вторым дополнительным регистром памяти, информационный вход которого подключен к шине данных микропроцессорного вычислительного блока, а выход - ко второму адресному входу запоминающего устройства, вход "запись" подключен к выходу "запись" микропроцессорного вычислительного блока, и счетчиком, информационные выходы которого подключены к третьему адресному входу запоминающего устройства, а вход предустановки кода подключен к дополнительному информационному выходу запоминающего устройства, причем второй выход синхронизации блока синхронизации подключен ко входам синхронизации накапливающих сумматоров, дополнительного регистра памяти и счетчика, а третий выход синхронизации блока синхронизации подключен ко входу сброса накапливающих сумматоров, входу синхронизации регистров памяти и входу "запрос прерывания" микропроцессорного вычислительного блока, а выход "чтение" микропроцессорного вычислительного блока подключен к соответствующим входам двух регистров памяти. 2 с.п. ф-лы; 4 ил.

| Чмых М.К | |||

| Цифровая фазометрия | |||

| - М.: Радио и связь, 1993. |

Авторы

Даты

1997-12-20—Публикация

1996-08-26—Подача