4

N3

сл

CJ

VJ

Изобретение относится к фазоизмери- тельной технике и может быть использовано для калибровки фазометров, а также для создания многофазных систем с высокой точностью задания фазового сдвига.

Известно устройство для задания фазового сдвига, содержащее блок установки, широкодиапазонный генератор м два канала формирования сдвинутых по фазе синусоидальных сигналов, каждый из которых содержит цифроаналоговый преобразователь (ЦАП), сумматор, регулируемый источник постоянного напряжения и последовательно соединенные блок выборки и запоминания, аналого-цифровой преобразователь, арифметический блок и фильтры нижних частот, второй вход которого соединен с выходом ЦАП, а выход фильтра нижних частот соединен с первым входом блока выборки и запоминания и второй выход арифметического блока через ре- гулируемый источник постоянного напряжения соединен с вторым входом сумматора. Также в устройстве имеются счетчик и микропроцессорный вычислитель, вход которого соединен с выходом блока установки, а выход-суправляющим входом широкодиапазонного генератора, выход которого последовательно соединен с входом счетчика, а в каждом из каналов формирования двух сдвинутых по фазе-сигналов содержатся блок оперативной памяти и блок, сравнения кодов, причем первый вход бло- ка сравнения кодов и .вход блока оперативной памяти соединены с выходом микропроцессорного вычислителя и являются входом соответствующего канала формирования, а выход счетчика1 соединен с адресным входом блока оперативной памяти каждого канала формирования, выход которого соединен с входом ЦАП и с вторым входом блока сравнения кодов, первый выход соединен с вторым входом арифметического блока, а второй - о вторым входом блока выборки и запоминания.

Недостатком данного устройства явля- етсязависимостьточностиустановления фазового сдвига от разрядности ЦАП.

Наиболее близким к предлагаемому является устройство для поверки фазометров, содержащее последовательно соединенные в первом и втором каналах регистр, ЦАП и аттенюатор, а также частотозадаю- щий генератор, соединенный с входом записи регистров, регистр кода частоты, счетчик, коммутатор, два оперативных запоминающих элемента, два регистра кода ослабления сигнала, блок управления и вычислительный блок, соединенный с блоком управления двунаправленной шиной

управляющих сигналов, шиной адреса и двунаправленной шиной данных, к которой также подключены информационные входы регистров кода ослабления сигнала, оперативных запоминающих элементов и регистра кода частоты, входы записи которых, а также управляющий вход коммутатора подключены к соответствующим выходам блока управления, выходы оперативных заломинающих элементов соединены с информационными входами соответственно регистров первого и второго каналов, адресные входы оперативных запоминающих элементов объединены и соединены через

коммутатор с выходами разрядов счетчика и шиной адреса вычислительного блока, вход счетчика соединен с выходом частотозада- ющего генератора, выходы регистров кода частоты и кода ослабления сигнала соединены соответственно с частотозадающим генератором и аттенюатором первого и второго каналов, выходы которых соединены с выходами устройства.

Недостатками данного устройства явля ются невысокая точность и большая зависимость погрешности от разрядности ЦАП.

Целью изобретения является повышение точности задания фазового сдвига. Для достижения поставленной цели известное устройство, содержащее первый (опорный) канал, который включает в себя первый оперативный запоминающий элемент, второй (фазозадающий) канал, содержащий второй оперативный запоминающий

элемент и ЦАП, а также последовательно соединенные частотозадающий генератор, счетчик и коммутатор, регистр кода частоты, выход которого соединен с частотозадающим генератором, вычислительный блок и

блок управления, которые соединены друг с другом шиной адреса, двунаправленной шиной управляющих сигналов и двунаправленной шиной данных, к которой также подключены информационные входы (О)

оперативных запоминающих элементов и регистра кода частоты, второй информационный вход коммутатора подключен к шине адреса вычислительного блока, а выход - к объединенным адресным входам (А) оперативных запоминающих элементов, снабжено блоком опорных напряжений, двумя аналоговыми коммутаторами, двумя фильтрами нижних частот, сумматором и третьим оперативным запоминающим элементом,

причем управляющие входы первого аналогового коммутатора соединены с выходом первого оперативного запоминающего элемента, а выход - с входом первого фильтра нижних частот, выход которого является

дервым выходом устройства, управляющие

входы второго аналогового коммутатора соединены с выходом третьего оперативного запоминающего элемента, вход данных которого соединен с шиной данных, а адресный вход объединен с адресными входами первого и второго оперативных запоминающих элементов, выход второго аналогового коммутатора подсоединен к входу сумматора, входы ЦАП соединены с выходами второго оперативного запоминающего элемента, в выход - с вторым входом сумматора, выход которого соединен с входом второго фильтра нижних частот, выход которого является вторым выходом устройства, выходы блока опорных напряжений подключены к аналоговым входам аналоговых коммутаторов, а выход Е - подключен к входу опорного напряжения (Е) ЦАГ, выходы вычислительного блока соединены с вторым входом регистра входа частоты и с третьими входами коммутатора и оперативных запоминающих элементов,

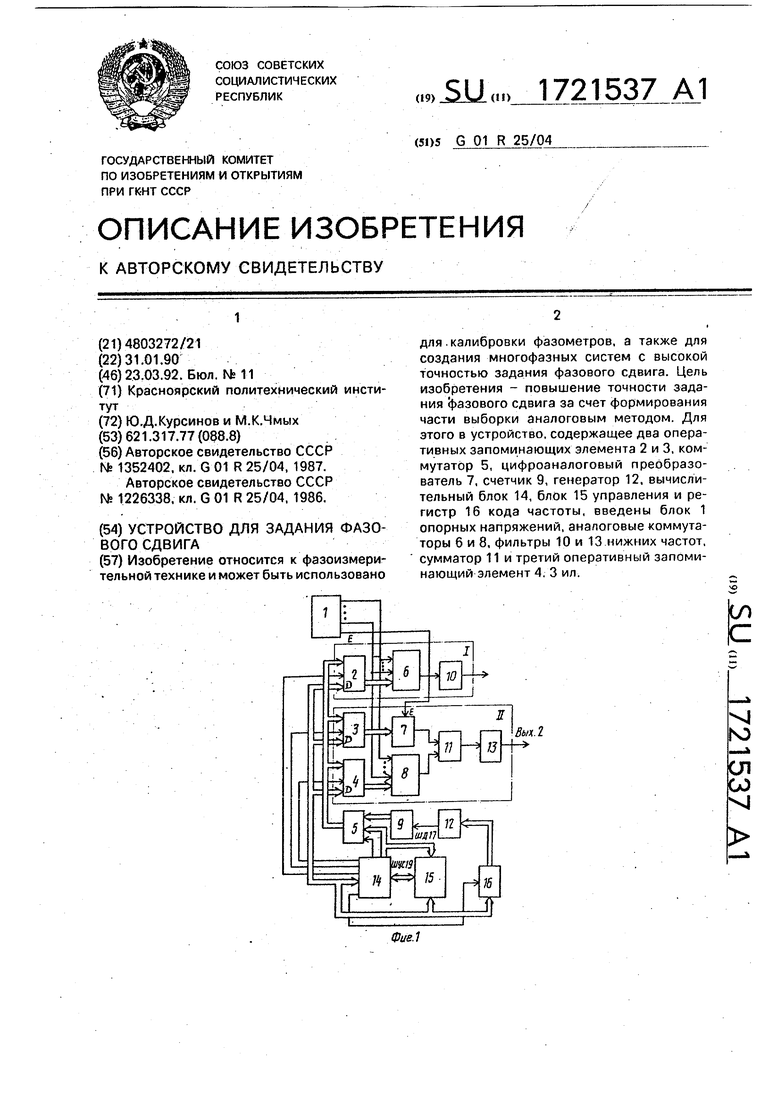

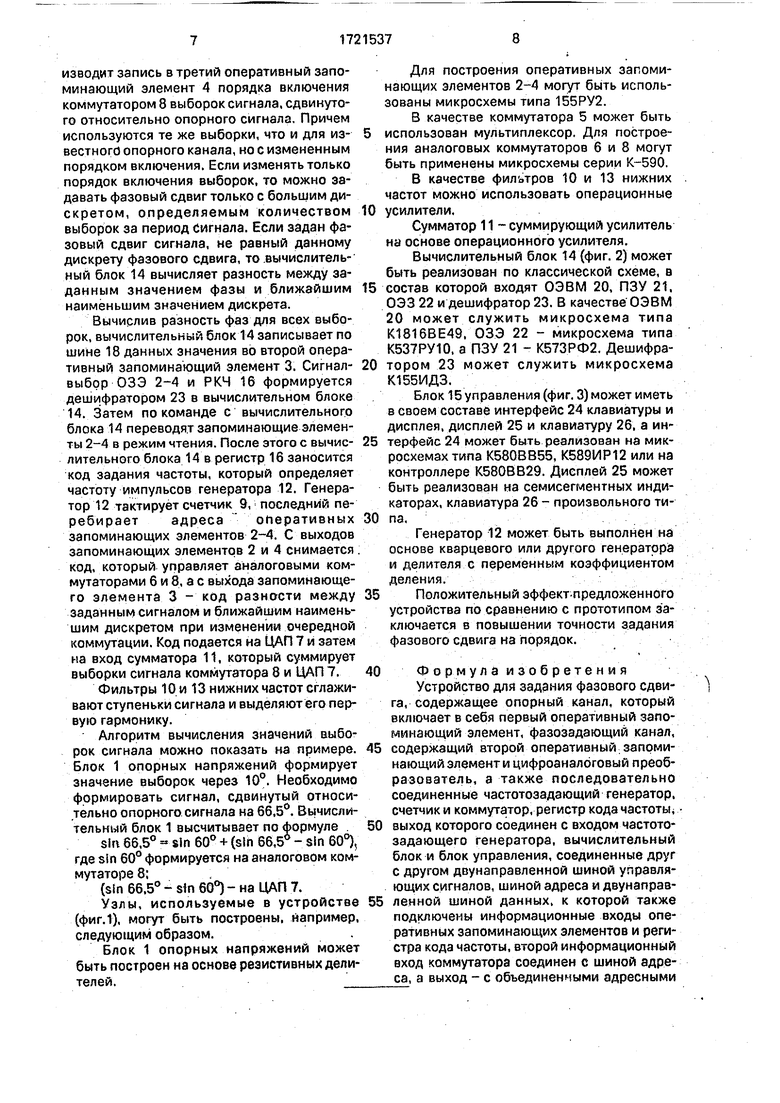

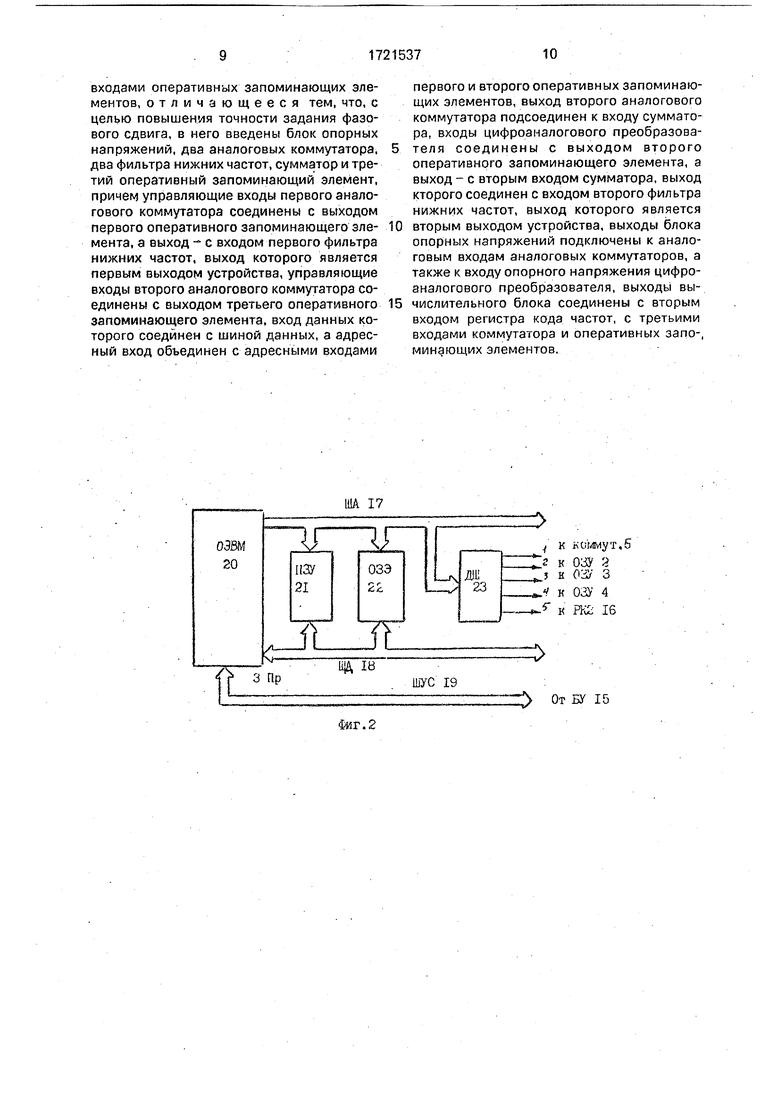

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 и 3. - структурные схемы вычислительного .блока и блока управления соответственно.

Устройство (фиг. 1) содержит блок 1 опорных напряжений, оперативные запоминающие элементы 2-4, коммутатор 5, первый аналоговый коммутатор 6, ЦАП 7, второй аналоговый коммутатор 8, счетчик 9, первый фильтр 10 нижних частот, сумматор 11, частотозадающий генератор 12, второй фильтр 13 нижних частот, вычислительный блок 14, блок 15 управления, регистр 16 кода частоты и шины 17-19, причем аналоговые входы аналоговых коммутаторов 6 и 8 объединены и подключены к блоку 1 опорных напряжений, а управляющие входы по шинам соединены с выходами первого 2 и третьего 4 оперативных запоминающих элементов, цифровые входы ЦАП 7 соединены по шине-с выходом второго оперативного запоминающего элемента 3,а вход опорных напряжений соединен с выходом Е блока 1 опорных напряжений, выходы счетчика 9 соединены по шине с входом коммутатора . 5, выходы которого подключены к объединенным адресным входам/оперативных запоминающих элементов 2-4, вход первого фильтра 10 нижних частот соединен с выходом первого аналогового коммутатора б, а выход является выходом первого (опорного) канала и первым выходом устройства, входы сумматора 11 соединены с выходами ЦАП 7 и второго аналогового коммутатора 8, а выход-с входом второго фильтра 13 нижних частот, выход которого является выходом второго (фазозадающего) канала и вторым выходом устройства, выход частотозадающего генератора соединен с входом счетчика 9, а вход - с выходом регистра 16 кода частоты, вычислительный блок 14 и блок 15 управления соединены между собой 5 двунаправленной шиной 19 управляющих сигналов, шиной 17 адреса и двунаправленной шиной 18 данных, к которой также подключены информационные входы оперативных запоминающих элементов 2-4 10 и регистра 16 кода частоты, информационный вход коммутатора 5 подключен к шине 17 адреса, а выход вычислительного блока 14 соединены с вторым входом регистра 16 кода частоты, с третьими входами оператив- 15 ных запоминающих элементов 2-4 и коммутатора 5.

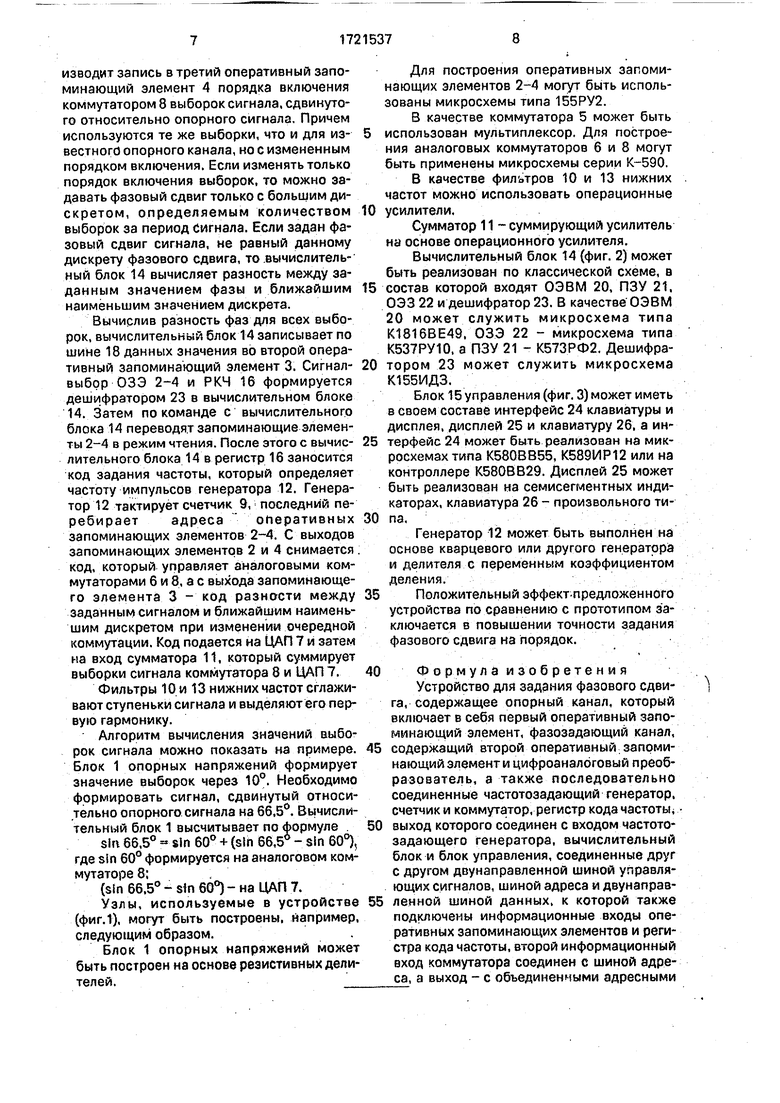

Вычислительный блок (фиг. 2) содержит, однокристальную ЭВМ (ОЭВМ) 20, постоянное запоминающее устройство (ПЗУ) 21, 0 оперативный запоминающий элемент (ОЗЭ) 22 и дешифратор 23, причем выход ОЭВМ 20 соединен с помощью шины 17 адреса с входами ПЗУ 21, оперативного запоминающего элемента 22 и дешифратора 23, а вход 5 ОЭВМ 20 по шине 18 данных подключен к вторым входам ПЗУ 21 и ОЗЭ 22, шины 17- 19, последняя из которых соединена с вторым входом ОЭВМ 20. Кроме того, выходы 1-5 дешифратора 23 являются входами и 0 выходами вычислительного блока.

Блок управления (фиг. 3) содержит интерфейс 24 клавиатуры и дисплея, .дисплей 25, клавиатуру 26, причем выход интерфейса 24 по шине соединен с входом дисплея 5 25, вход интерфейса 24 соединен с двунаправленной шиной с клавиатурой 26, шины 17 и 18, подключенные к второму и третьему входам интерфейса 24, шину 19, подключенную к второму входу клавиатуры 26, которые 0 являются входами блока управления.

Устройство (фиг, 1) работает следующим образом.

Блок 1 опорных напряжений формирует высокостабильные напряжения амплиту- 5 дои, равной дискретным значениям сигнала , количество значений напряжений определяется количеством выборок на период сигнала.

Для формирования сигналов с задан- 0 ным сдвигом фаз при помощи блока 15 управления в прибор вводят данные о сигнале, т.е. частоту и фазу сигнала. После ввода данных вычислительный блок 14 по шине 18 данных производит запись в первый опера- 5 тивный запоминающий элемент 2 последовательности включения выборок сигнала первым аналоговым коммутатором 6. Сформированный сигнал принимают за опорный, т.е. за сигнал с нулевой фазой. Далее вычислительный блок 14 по шине 18 данных производит запись в третий оперативный запоминающий элемент 4 порядка включения коммутатором 8 выборок сигнала, сдвинутого относительно опорного сигнала. Причем используются те же выборки, что и для из- вестного опорного канала, но с измененным порядком включения. Если изменять только порядок включения выборок, то можно задавать фазовый сдвиг только с большим дискретом, определяемым количеством выборок за период Сигнала. Если задан фазовый сдвиг сигнала, не равный данному дискрету фазового сдвига, то .вычислительный блок 14 вычисляет разность между заданным значением фазы и ближайшим наименьшим значением дискрета.

Вычислив разность фаз для всех выборок, вычислительный блок 14 записывает по шине 18 данных значения во второй оперативный запоминающий элемент 3. Сигнал- выбор ОЗЭ 2-4 и РКЧ 16 формируется дешифратором 23 в вычислительном блоке 14. Затем по команде с вычислительного блока 14 переводят запоминающие элементы 2-4 в режим чтения. После этого с вычис- лительного блока 14 в регистр 16 заносится код задания частоты, который определяет частоту импульсов генератора 12. Генератор 12 тактирует счетчик 9, последний перебирает адреса оперативных запоминающих элементов 2-4. С выходов запоминающих элементов 2 и 4 снимается код, который управляет аналоговыми коммутаторами 6 и 8, а с выхода запоминающего элемента 3 - код разности между заданным сигналом и ближайшим наименьшим дискретом при изменении очередной коммутации. Код подается на ЦАП 7 и затем на вход сумматора 11, который суммирует выборки сигнала коммутатора 8 и ЦАП 7.

Фильтры 10 и 13 нижних частот сглаживают ступеньки сигнала и выделяют его первую гармонику.

Алгоритм вычисления значений выборок сигнала можно показать на примере. Блок 1 опорных напряжений формирует значение выборок через 10°. Необходимо формировать сигнал, сдвинутый относительно опорного сигнала на 66,5°. Вычислительный блок 1 высчитывает по формуле .

sin66,5° -sin 60° + (sin 66,5й- sin 60°), где sin 60° формируется на аналоговом коммутаторе 8;

(sin 66,5° sin 60°)-на ЦАП7. Узлы, используемые в устройстве (фиг.1), могут быть построены, например, следующим образом.

Блок 1 опорных напряжений может быть построен на основе резистивных делителей.

Для построения оперативных запоминающих элементов 2-4 могут быть использованы микросхемы типа 155РУ2.

В качестве коммутатора 5 может быть использован мультиплексор. Для построения аналоговых коммутаторов 6 и 8 могут быть применены микросхемы серии К-590.

В качестве фильтров 10 и 13 нижних частот можно использовать операционные усилители.

Сумматор 11 - суммирующий усилитель на основе операционного усилителя.

Вычислительный блок 14 (фиг. 2) может быть реализован по классической схеме, в состав которой входят ОЭВМ 20, ПЗУ 21, ОЭЗ 22 и дешифратор 23. В качестве ОЭВМ 20 может служить микросхема типа К1816ВЕ49, ОЗЭ 22 - микросхема типа К537РУ10, а ПЗУ 21 - К573РФ2. Дешифратором 23 может служить микросхема К155ИДЗ.

Блок 15 управления (фиг. 3) может иметь в своем составе интерфейс 24 клавиатуры и дисплея, дисплей 25 и клавиатуру 26, а интерфейс 24 может быть реализован на микросхемах типа K58QBB55, К589ИР12 или на контроллере К580ВВ29. Дисплей 25 может быть реализован на семисегментных индикаторах, клавиатура 26- произвольного типа.

Генератор 12 может быть выполнен на основе кварцевого или другого генератора и делителя с переменным коэффициентом деления.

Положительный эффекТ Предложенного устройства по сравнению с прототипом заключается в повышении точности задания фазового сдвига на порядок.

Формула изобретени я Устройство для задания фазового сдвига, содержащее опорный канал, который включает в себя первый оперативный запоминающий элемент, фазозадающий канал, содержащий второй оперативный запоминающий элемент и цифроаналоговый преобразователь, а также последовательно соединенные частотозадающий генератор, счетчик и коммутатор, регистр кода частоты выход которого соединен с входом частото- задающего генератора, вычислительный блок и блок управления, соединенные друг с другом двунаправленной шиной управляющих сигналов, шиной адреса и двунаправленной шиной данных, к которой также подключены информационные входы оперативных запоминающих элементов и регистра кода частоты, второй информационный вход коммутатора соединен с шиной адреса, а выход - с объединенными адресными

входами оперативных запоминающих элементов, отличающееся тем, что, с целью повышения точности задания фазового сдвига, в него введены блок опорных напряжений, два аналоговых коммутатора, два фильтра нижних частот, сумматор и третий оперативный запоминающий элемент, причем управляющие входы первого аналогового коммутатора соединены с выходом первого оперативного запоминающего элемента, а выход - с входом первого фильтра нижних частот, выход которого является первым выходом устройства, управляющие входы второго аналогового коммутатора соединены с выходом третьего оперативного запоминающего элемента, вход данных которого соединен с шиной данных, а адресный вход объединен с адресными входами

первого и второго оперативных запоминающих элементов, выход второго аналогового коммутатора подсоединен к входу сумматора, входы цифроаиалогового преобразователя соединены с выходом второго оперативного запоминающего элемента, а выход - с вторым входом сумматора, выход кторого соединен с входом второго фильтра нижних частот, выход которого является

0 вторым выходом устройства, выходы блока опорных напряжений подключены к аналоговым входам аналоговых коммутаторов, а также к входу опорного напряжения цифро- аналогового преобразователя, выходы вы5 числительного блока соединены с вторым входом регистра кода частот, с третьими входами коммутатора и оперативных запо-, минающих элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки фазометров | 1984 |

|

SU1226338A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1119051A1 |

| Устройство синтеза испытательного сигнала измерителей фазочастотных характеристик | 1990 |

|

SU1795415A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2004 |

|

RU2262190C1 |

Изобретение относится к фазоизмери- тельной технике и может быть использовано для .калибровки фазометров, а также для создания многофазных систем с высокой точностью задания фазового сдвига. Цель изобретения - повышение точности задания фазового сдвига за счет формирования части выборки аналоговым методом. Для этого в устройство, содержащее два оперативных запоминающих элемента 2 и 3, коммутатор 5, цифроаналоговый преобразователь 7, счетчик 9, генератор 12, вычислительный блок 14, блок 15 управления и регистр 16 кода частоты, введены блок 1 опорных напряжений, аналоговые коммутаторы 6 и 8, фильтры 10 и 13 нижних частот, сумматор 11 и третий оперативный запоминающий элемент 4, 3 ил.

ft

3 Пр

ШУС 19

У От БУ 15

| Цифровой калибратор фазы | 1986 |

|

SU1352402A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для поверки фазометров | 1984 |

|

SU1226338A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-03-23—Публикация

1990-01-31—Подача