Предлагаемое изобретение относится к области электрорадиоизмерений и может быть использовано для измерения амплитуды гармонического сигнала за малое время измерения, в том числе и за время, меньшее периода (полупериода) гармонического сигнала и некратное периоду сигнала, с повышенной точностью и помехоустойчивостью.

Известно устройство, реализующее способ измерения амплитуды сигнала по А. С. СССР 1465786, содержащее генератор опорного напряжения, восемь перемножителей, четыре квадратора, четыре интегратора, два преобразователя отношений, два сумматора, три блока вычислений и один индикатор, а также блок управления. Недостатком его является невозможность измерения значения амплитуды сигнала при нефиксированном однозначно времени измерения. Невозможно также проведение нескольких промежуточных измерений в рамках одного измерительного интервала. Это связано с тем, что в данном устройстве форма опорного сигнала зависит от величины времени измерения, так как опорный сигнал формируется за время, менее периода измеряемого сигнала, и привязан к середине измерительного интервала.

Наиболее близким по технической сущности к предлагаемому устройству является устройство, реализующее оптимальную по критерию максимального правдоподобия оценку амплитуды гармонического сигнала при неизвестном фазовом сдвиге для сигнала с шумами, содержащее генератор опорного напряжения, два перемножителя, два интегратора, вычислительный блок и индикатор, причем входы первого и второго перемножителей подключены к входу измеряемого сигнала и выходам генератора опорного напряжения, вход первого интегратора подключен к выходу первого перемножителя, вход второго интегратора подключен к выходу второго перемножителя, выходы интеграторов подключены к входу вычислительного блока, выходом подключенного к индикатору результата измерения (см. кн. Б.Р. Левин, Теоретические основы статистической радиотехники, - М.: Радио и связь, 1989. с.593).

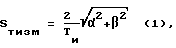

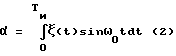

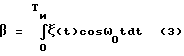

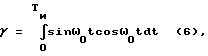

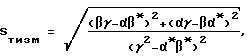

В соответствии с прототипом результат измерения определяется в вычислительном блоке устройства по формуле

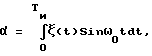

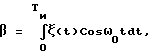

где

Здесь ξ(t) - измеряемый гармонический сигнал, Ти - время интегрирования (измерения).

Данный алгоритм вычисления амплитуды в устройстве обеспечивает оптимальное но критерию максимального правдоподобия измерение амплитуды при времени измерения. равном или, в более общем случае, кратном периоду сигнала, позволяя проводить непрерывные измерения, не ограниченные длительностью времени измерения и производить несколько измерений в течение времени измерения, при условии, что между моментами измерения укладывается целое число периодов измеряемого сигнала.

Однако при времени измерения, меньшем периода (полупериода) сигнала, измерение амплитуды указанным устройством становится практически невозможным из-за возникновения большой систематической погрешности.

Продемонстрируем сказанное следующим образом.

Измеряемый гармонический сигнал с учетом наличия шумовой составляющей определится следующим выражением:

ξ(t) = E0+Sт0sin(ω0t+ϕ0)+n(t), (4)

где E0, Sт0, ω0, ϕ0 - постоянная составляющая, амплитуда, частота и фазовый сдвиг исследуемого сигнала, n(t) - флуктуационный шум, присутствующий совместно с полезным сигналом.

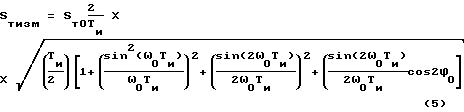

Подставив (4) в (2) и (3), взяв интегралы и подставив результат в (1), получим выражение для измеренной амплитуды

Как видно из (5), при Tи, равном или кратном периоду сигнала Т0, Sтизм = Sт0. Если же Tи меньше или некратно периоду сигнала; то возникает постоянная систематическая погрешность, зависящая как от времени измерения, так и от начального фазового сдвига измеряемого сигнала. В этих условиях измерения практически невозможны.

В основу настоящего изобретения положена задача разработки устройства для осуществления текущего, непрерывного измерения амплитуды гармонического сигнала при времени измерения, менее и некратном периоду гармонического сигнала без систематической погрешности при априорно неизвестном фазовом сдвиге измеряемого сигнала.

Поставленная задача решается тем, что устройство измерения амплитуды сигнала, содержащее генератор опорного напряжения, два перемножителя, два интегратора, вычислительный блок и индикатор, причем первые входы первого и второго перемножителей соединены и являются входом устройства, а вторые входы этих перемножителей соответственно подключены к выходам генератора опорного напряжения, являющимися выходами синусной и косинусной составляющих опорного сигнала, вход первого интегратора подключен к выходу первого перемножителя, вход второго интегратора подключен к выходу второго перемножителя, выходы интеграторов подключены к соответствующим входам вычислительного блока, выходом соединенного с индикатором результата измерения согласно предлагаемому изобретению снабжено третьим перемножителем, двумя квадраторами, третьим, четвертым и пятым интеграторами и блоком управления, причем входы третьего перемножителя подключены к выходам генератора опорного напряжения, являющимися выходами синусной и косинусной составляющих опорного сигнала, а выход третьего перемножителя подключен к информационному входу третьего интегратора, выходом соединенного с соответствующим входом вычислительного блока, первый квадратор входом подключен к выходу генератора опорного напряжения, являющемуся выходом синусной составляющей опорного сигнала, а вход второго квадратора подключен к выходу генератора опорного напряжения, являющемуся выходом косинусной составляющей опорного сигнала, выходы первого и второго квадраторов подключены соответственно к информационным входам четвертого и пятого интеграторов, которые выходами соединены с соответствующими входами вычислительного блока, чьи управляющие выходы являются входами блока управления, при этом один из выходов блока управления является входом генератора опорного напряжения и одним из входов управления всех интеграторов, а другой выход блока управления является управляющим входом индикатора и вторым входом управления всех интеграторов.

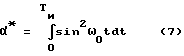

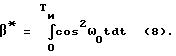

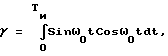

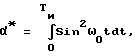

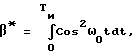

Сущность работы предлагаемого устройства можно пояснить следующим образом. В соответствии с формулой изобретения к формируемым в прототипе двум сигналам (2) и (3) для вычисления результата измерения предлагается добавить сформированные на выходе дополнительных интеграторов сигналы

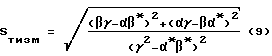

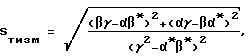

При этом вычислительный блок определит результат измерения амплитуды сигнала по формуле

Выражение (9) является алгоритмом оптимальной оценки амплитуды гармонического сигнала с привязкой результата измерения к началу измерительного интервала при неизвестном фазовом сдвиге измеряемого сигнала в условиях воздействия "белого шума" совместно с полезным сигналом и не имеющим систематической погрешности при любом времени измерения, как меньше периода, так и некратном периоду гармонического сигнала. Одновременно устройство, работающее по алгоритму (9), имеет возможность не только осуществлять измерения за время менее периода, но и осуществлять при этом непрерывные текущие измерения, так как момент измерения привязан к началу измерительного интервала, что позволяет получать промежуточные значения измеряемой величины без формирования нового измерительного интервала, и не требует формирования опорных сигналов сложной формы с привязкой их к середине измерительного интервала. Достаточно начать их формирование с началом времени измерения по законам синуса и косинуса на известной частоте сигнала, что не представляет практической сложности.

Для того, чтобы убедиться в отсутствии систематической погрешности алгоритма (9) найдем математическое ожидание результата измерения, для чего подставим в (9) измеряемый сигнал (4) без шумов (n(t)=0). Для составляющих (2), (3) и (6-8) получим

α = Sт0(α*cosϕ0+γsinϕ0) (10),

β = Sт0(β*sinϕ0+γcosϕ0) (11),

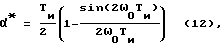

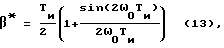

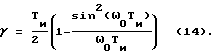

где

Если подставить (10-14) в (9), то получим Sтизм=Sт0, причем данное равенство справедливо для любого времени измерения, как кратного, так и не кратного периоду сигнала, в том числе и меньше периода измеряемого гармонического сигнала.

Как видно из данного анализа, предлагаемое устройство обладает принципиально новым по сравнению с прототипом свойством - обеспечивает измерение амплитуды гармонического сигнала в текущем режиме из-за привязки результата измерения к началу измерительного интервала при времени измерения, меньшем периода сигнала, а в общем случае и при времени измерения, не кратном периоду, с нулевой систематической погрешностью. При времени измерения, равном или кратном периоду сигнала предлагаемое устройство дает результат измерения, аналогичный результату при использовании известного устройства.

Что касается случайной погрешности, вносимой в результат измерения предлагаемым устройством, то можно показать, на основе исследования функции правдоподобия, что используемый в вычислительном блоке алгоритм является оптимальным по критерию максимального правдоподобия и обеспечивает минимально возможную случайную погрешность для устройств, осуществляющих измерение амплитуды гармонического сигнала за время, менее периода при априорно неизвестном фазовом сдвиге измеряемого сигнала. Это объясняется тем, что алгоритм (9) получен из функции правдоподобия и является оптимальной оценкой амплитуды гармонического сигнала с шумами при неизвестном фазовом сдвиге, полученном для случая привязки результата измерения к началу измерительного интервала, что и позволяет проводить предлагаемому устройству непрерывные текущие измерения амплитуды.

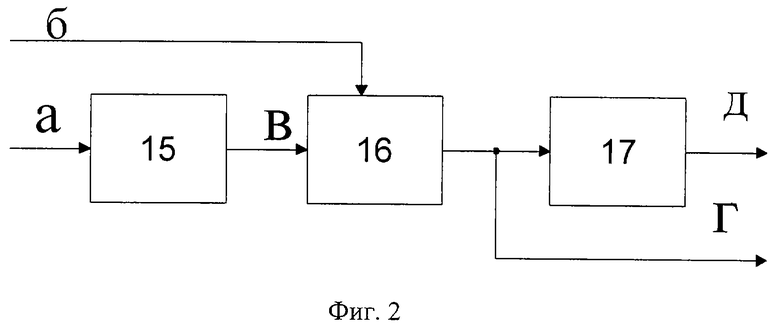

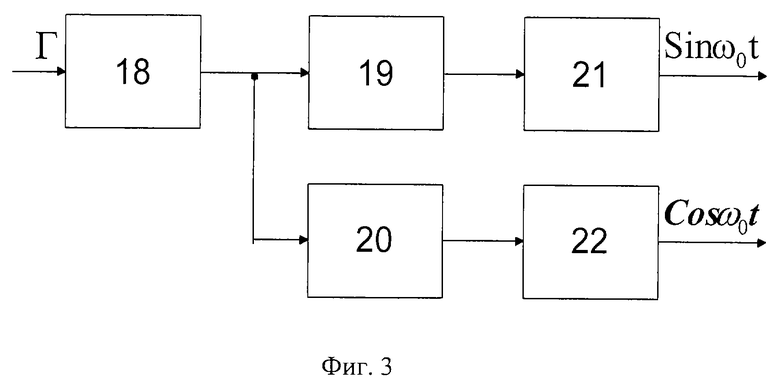

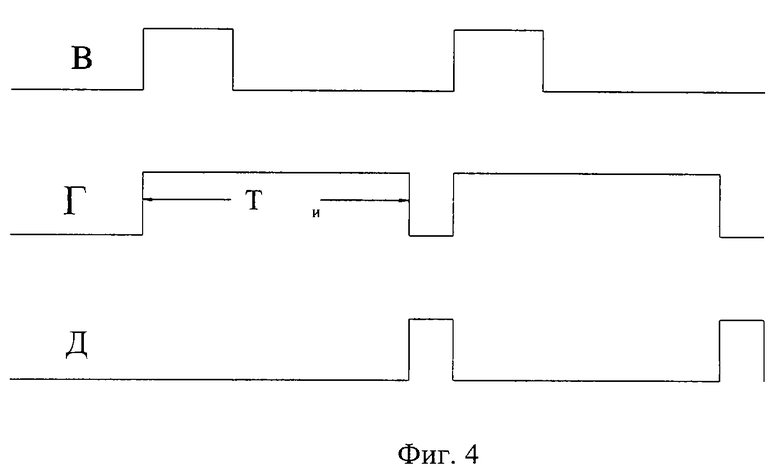

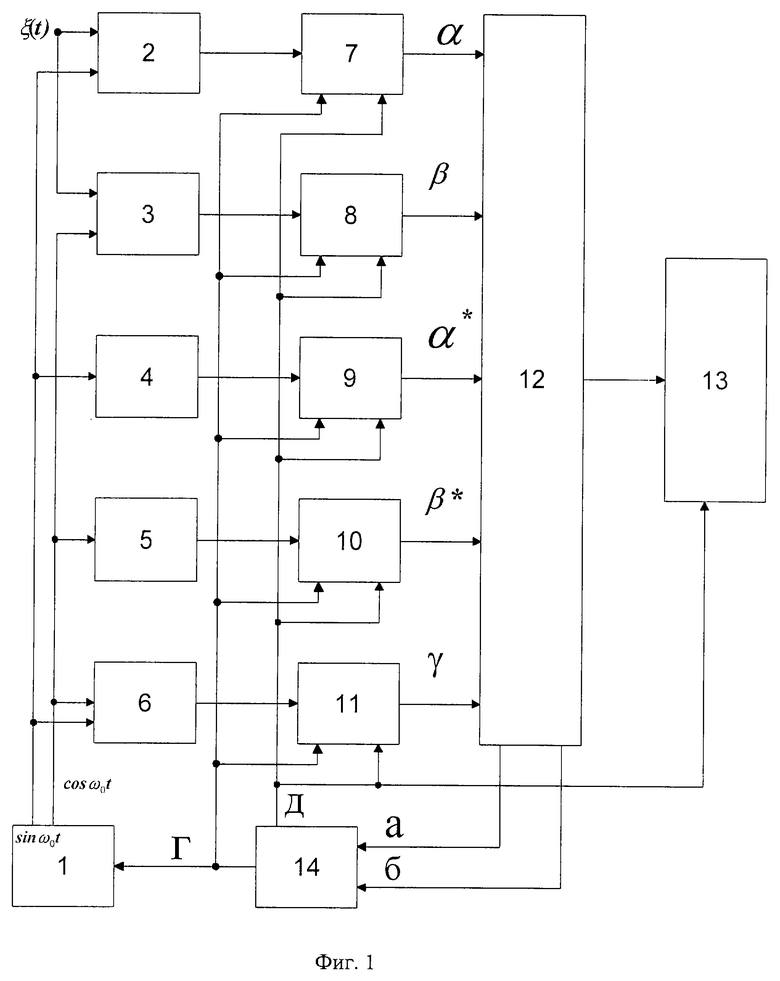

На фиг.1 приведена структурная схема предлагаемого устройства, на фиг.2 - структурная схема блока управления, на фиг.3 - структурная схема генератора опорного напряжения, на фиг.4 - эпюры напряжений в блоке управления.

Устройство содержит генератор опорного напряжения 1, первый и второй перемножители 2 и 3, первые входы которых являются входом устройства, второй вход перемножителя 2 подключен к выходу генератора 1 опорного напряжения, являющемуся выходом синусной составляющей опорного сигнала, а второй вход перемножителя 3 подключен к выходу генератора 1 опорного напряжения, являющемуся выходом косинусной составляющей опорного сигнала, первый 4 и второй 5 квадраторы, входы которых подключены соответственно к выходам синусной и косинусной составляющей опорного сигнала генератора 1 опорного напряжения, третий перемножитель 6, входами подключенный к обоим выходам генератора 1 опорного напряжения, интеграторы 7, 8, 9, 10 и 11, информационные входы которых подключены соответственно к выходам первого 2 и второго 3 перемножителей, первого 4 и второго 5 квадраторов и третьего 6 перемножителя, вычислительный блок 12, информационные входы которого являются выходами интеграторов 7, 8, 9, 10 и 11, сигнальный выход является одним из входов индикатора 13, а управляющие выходы - шины "а" и "б" подключены к управляющим входам блока управления 14, выходы которого - шины "г" и "д" подключены к соответствующим управляющим входам интеграторов 7, 8, 9, 10 и 11, кроме этого, шина "г" соединена с управляющим входом генератора 1 опорного напряжения, а шина "д" - с управляющим входом индикатора 13.

Блок 14 управления содержит формирователь 15 импульсов пуска (ФИП), времязадающий элемент (ВЗЭ) 16 и формирователь 17 импульсов (ФИ), последовательно соединенные между собой. Выходом блока 14 управления являются шины "г" и "д", причем шина "г" является выходом времязадающего элемента 16, а шина "д" - формирователя 17 импульсов. Шина "г" подключена к входу генератора 1 опорного напряжения и одному из управляющих входов интеграторов 7-11, а шина "д" - к другим управляющим входам интеграторов 7-11 и к управляющему входу индикатора 13. Входом блока 14 управления являются шины "а" и "б", причем шина "а" подключена к управляющему входу формирователя 15 импульсов пуска, а шина "б" - к управляющему входу времязадающего элемента 16.

Генератор 1 опорного напряжения содержит тактовый генератор (ТГ) 18, вход которого подключен к шине "г" блока 14 управления, два запоминающих устройства (ЗУ) 19 и 20, входы которых подключены к выходу тактового генератора 18, и два цифроаналоговых преобразователя (ЦАП) 21 и 22, входы которых подключены к соответствующим выходам запоминающих устройств 19 и 20, а выходы являются выходами соответственно синусной sinω0t и косинусной cosω0t составляющих опорного сигнала генератора 1 опорного напряжения.

Устройство работает следующим образом.

На первый и второй перемножители 2 и 3 поступает измеряемый сигнал вида (4), а также синусная и косинусная составляющие опорного сигнала с выхода генератора 1 опорного напряжения. Генератор 1 опорного напряжения может работать в автономном режиме либо синхронизироваться от блока управления 14. На выходе первого интегратора 7 формируется сигнал α, определяемый (2). На выходе второго интегратора 8 формируется сигнал β, определяемый (3). Кроме того, синусная и косинусная составляющие опорного сигнала с выхода генератора 1 опорного напряжения возводятся в квадрат при помощи первого и второго квадратора 4 и 5, а также перемножаются между собой при помощи третьего перемножителя 6. На выходе третьего интегратора 9 формируется сигнал α*, определяемый (7), на выходе четвертого интегратора 10 формируется сигнал β*, определяемый (8), а на выходе пятого интегратора 11 - сигнал γ, определяемый (6).

Вычислительный блок 12, куда поступают сигналы со всех интеграторов 7-11: α, β, α*, β* и γ осуществляет перевод их в цифровую форму и вычисление результата измерения. На индикаторе 13 формируется результат измерения амплитуды измеряемого сигнала

что, как показано выше, соответствует результату измерения амплитуды гармонического сигнала без систематической погрешности при любом времени измерения.

Синхронизацию работы интеграторов 7-11 и индикатора 13 осуществляет блок 14 управления.

Блок 14 управления (фиг.2) работает следующим образом.

Формирователь 15 импульсов пуска формирует одиночные импульсы (точка "в") либо в автономном режиме, либо по команде с вычислительного блока 12, которые запускают времязадающий элемент 16. Последний формирует импульс, равный по длительности требуемому времени измерения Tи, определяемой с вычислительного блока 12. Этот импульс поступает на выход - шину "г" блока 14 управления и на вход формирователя 17 импульсов, на выходе которого формируется импульс, поступающий на выход "д" блока 14 управления. В течение длительности импульса на выходе "г" длительностью Ти происходит интегрирование сигналов, поступающих на входы интеграторов 7-11. В течение действия импульса на выходе "д" происходит запоминание результатов интегрирования, вычисление результата измерения и подключение элемента памяти индикатора 13 к выходу вычислительного блока 12. Индикатор 13 запоминает результат измерения и отображает его до прихода следующего импульса по шине "д".

Для пояснения работы блока 14 управления на фиг.4 приведены эпюры напряжений в элементах блока 14 управления: в точке "в" (фиг.2) и на шинах "г" и "д".

Используемые в устройстве, реализующем предлагаемый способ, узлы могут быть построены следующим образом.

Перемножители и квадраторы могут быть построены по схемам логарифмических функциональных генераторов (У.Титце, К.Шенк. Полупроводниковая схемотехника. М., Мир, 1982, с.156).

Интеграторы могут быть построены на основе операционных усилителей. Для обеспечения интегрирования в течение времени Ти применяются интеграторы с синхронизацией и памятью. Схема такого интегратора приведена на стр. 144 в кн. У.Титце, К.Шенк. Полупроводниковая схемотехника. М., Мир, 1982.

Индикатор 13 может быть выполнен в виде последовательно включенных элемента выборки и хранения и стрелочного прибора. Элемент выборки и хранения можно реализовать на основе цифровых запоминающих устройств, а стрелочный прибор заменить на цифровой индикатор.

Формирователь импульса пуска 15 может быть реализован по схеме сихронизируемого мультивибратора, а времязадающий элемент 16 и формирователь импульсов 17 могут быть реализованы по схемам одновибраторов.

Вычислительный блок 12 может быть реализован на основе микропроцессора Intel 80386 по типовой структуре с аналогоцифровыми преобразователями на входе. Вычислительный блок 12 выполняет следующие функции, вытекающие из описания работы предлагаемого устройства:

1. Выдача управляющих сигналов для блока управления;

2. Подключение выходов интеграторов к входам АЦП, содержащихся в вычислительном блоке. Причем это может происходить как автоматически, по концу времени измерения Ти, так и ранее времени Ти, по командам оператора или в соответствии с программой для обеспечения режима текущих измерений и получения нескольких значений измеряемой амплитуды;

3. Считывание цифровых кодов с выходов АЦП и занесение их в память;

4. Вычисление результата измерения по указанной выше формуле и преобразование его к виду, удобному для отображения на индикаторе;

5. Переход в режим ожидания для повторения всех операций.

Таким образом, в предлагаемом устройстве решена поставленная задача - осуществление непрерывного, текущего измерения амплитуды гармонического сигнала при времени измерения менее или некратном периоду гармонического сигнала, устройство физически реализуемо из известных элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ ГАРМОНИЧЕСКОГО СИГНАЛА | 2005 |

|

RU2281519C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ АМПЛИТУДЫ СИГНАЛА | 2004 |

|

RU2280877C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ ГАРМОНИЧЕСКОГО СИГНАЛА | 2000 |

|

RU2196998C2 |

| СПОСОБ ИЗМЕРЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ СИГНАЛА | 2003 |

|

RU2239842C1 |

| Способ определения амплитуды сигнала | 1989 |

|

SU1674003A1 |

| Способ определения фазового сдвига | 1988 |

|

SU1651227A2 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

| Способ измерения амплитуды сигнала | 1986 |

|

SU1465786A1 |

| Способ измерения амплитуды сигнала | 1988 |

|

SU1564557A1 |

| Устройство изменения фазового сдвига | 1988 |

|

SU1647446A1 |

Устройство измерения амплитуды сигнала содержит генератор опорного напряжения, первый и второй перемножители, на первые входы которых поступает измеряемый сигнал, а вторые входы подключены к выходам генератора опорного напряжения; первый и второй квадраторы, входы которых также подключены к выходам генератора опорного напряжения, третий перемножитель, оба входа которого также подключены к выходам генератора опорного напряжения, пять интеграторов, входы которых соединены соответственно с выходами первого и второго перемножителей, первого и второго квадратора и третьего перемножителя, вычислительный блок, входы которого подключены к выходам всех интеграторов, а информационный выход - к входу индикатора, управляющие выходы - к управляющим входам блока управления, выходы блока управления подключены к управляющим входам интеграторов, индикатора и генератора опорного напряжения. Технический результат - расширение области применения. 4 ил.

Устройство измерения амплитуды сигнала, содержащее генератор опорного напряжения, два перемножителя, два интегратора, вычислительный блок и индикатор, причем первые входы первого и второго перемножителей соединены и являются входом устройства, а вторые входы этих перемножителей соответственно подключены к выходам генератора опорного напряжения, являющимися выходами синусной и косинусной составляющих опорного сигнала, вход первого интегратора подключен к выходу первого перемножителя, вход второго интегратора подключен к выходу второго перемножителя, выходы интеграторов подключены к соответствующим входам вычислительного блока, выходом соединенного с индикатором результата измерения, отличающееся тем, что оно дополнительно содержит третий перемножитель, два квадратора, третий, четвертый и пятый интеграторы и блок управления, причем входы третьего перемножителя подключены к выходам генератора опорного напряжения, являющимися выходами синусной и косинусной составляющих опорного сигнала, а выход третьего перемножителя подключен к информационному входу третьего интегратора, выходом соединенного с соответствующим входом вычислительного блока, первый квадратор входом подключен к выходу генератора опорного напряжения, являющемуся выходом синусной составляющей опорного сигнала, а вход второго квадратора подключен к выходу генератора опорного напряжения, являющемуся выходом косинусной составляющей опорного сигнала, выходы первого и второго квадраторов подключены соответственно к информационным входам четвертого и пятого интеграторов, которые выходами соединены с соответствующими входами вычислительного блока, чьи управляющие выходы являются входами блока управления, на одном из выходов блока управления формируется импульс, в течение длительности которого происходит интегрирование сигналов, поступающих на входы интеграторов, указанный выход блока управления подключен ко входу генератора опорного напряжения и к одному из входов управления каждого из интеграторов, на другом выходе блока управления формируется импульс, в течение длительности которого происходит запоминание результатов интегрирования, вычисление результата измерения и подключение элемента памяти индикатора к выходу вычислительного блока, указанный другой выход блока управления подключен к управляющему входу индикатора и вторым входам управления каждого из интеграторов, кроме того, вычислительный блок определяет результаты измерения амплитуды сигнала по формуле

где

где ξ(t) - исследуемый сигнал;

Ти - время интегрирования (измерения) сигнала;

ω0 - частота исследуемого сигнала.

| ЛЕВИН Б.Р | |||

| Теоретические основы статистической радиотехники | |||

| - М.: Радио и связь, 1989, с.593 | |||

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УРОВНЯ НАПРЯЖЕНИЯ | 1990 |

|

RU2018140C1 |

| US 6084394 А, 04.07.2000. | |||

Авторы

Даты

2003-09-20—Публикация

2000-12-04—Подача