Изобретение относится к электросвязи и может быть использовано для поиска информации и идентификации применяемых в цифровых системах связи и, в частности, в сетях передачи данных (СПД) кадров коммуникационных протоколов, относящихся к подмножеству известных процедур HDLC (Протоколы информационно-вычислительных сетей. Справочник. /Под ред. И.А.Мизина, П.А.Кулешова. M. радио и связь, 1990, 503 с.), стандартизированному Международным консультативным комитетом по телефонии и телеграфии в рекомендации X.25/2.

Известно устройство, содержащее регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации [1]

В ходе выполнения задачи по приему и поиску цифровых потоков информации необходимо определить параметры цифрового потока, по которым производится поиск информации и идентификации кадров, а известный аналог не выполняет этих требований определение коммуникационных кадров реализуется в нем с вероятностью правильного распознания значительно меньше 0,1, так как распознавание производится статистическим способом, а каждый кадр является в своем роде уникальным.

Наиболее близким к предлагаемому является устройство поиска информации, содержащее регистры верхней и нижней границы, сумматор-вычислитель, регистр стратегии поиска, вычитающий и суммирующие счетчики, схемы сравнения, блок памяти, регистр ключа, выходной регистр, группу элементов И или ИЛИ, триггер, вход запуска, входы адресов верхней и нижней границы, вход кода критерия смены стратегии поиска, вход ключа, выход адреса, выход признака отсутствия информации и распределитель импульса [2]

Недостатком данного устройства является невозможность получения однозначного решения (вероятность выделения параметров и идентификации кадра цифрового потока порядка 0,3), так как прототип реализует поиск информационных блоков в массиве посредством дихотомического метода без учета наличия большого числа типов возможных кадров.

Целью изобретения является разработка устройства поиска информации по цифровому потоку с конечной априорной неопределенностью относительно его параметров, обеспечивающего повышение достоверности поиска, идентификации информации за счет получения однозначного решения.

Цель достигается тем, что в устройство поиска информации, содержащее блок сравнения и регистр стратегии поиска, дополнительно введены следующие элементы: коммутатор, первый, второй и третий регистры, блок коррекции, блок дешифрации. Первый вход блока коррекции, параллельно соединенный с вторым входом первого регистра и девятым входом блока сравнения, является первым входом Ft устройства поиска информации. Первый вход первого регистра, параллельно соединенный с вторым входами коммутатора и блока коррекции, является вторым входом Fs устройства поиска информации. Выход коммутатора соединен с первым входом третьего регистра. Первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы первого регистра соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами блока сравнения. Выход блока сравнения параллельно соединен с первыми входами регистра стратегии поиска и коммутатора. Выход блока коррекции параллельно соединен с вторыми входами регистра стратегии поиска, второго регистра и третьим входом третьего регистра. Выход регистра стратегии поиска параллельно соединен с первыми входами второго регистра, блока дешифрации и третьим входом коммутации. Выход второго регистра соединен с вторым входом третьего регистра. Первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы третьего регистра соединены соответственно с вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым входами блока дешифратора. С первого по двадцать второй выходы блока дешифрации являются соответственно с первого по двадцать второй выходами устройства поиска информации.

Блок коррекции содержит первый и второй последовательные регистры, блок сравнения и повторитель. Первый вход блока коррекции параллельно соединен с первыми входами первого и второго последовательных регистров, блока сравнения и повторителя. Второй вход блока коррекции является вторым входом первого последовательного регистра, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с вторым, третьим, четвертым, пятым и шестым входами блока сравнения. Выход блока сравнения соединен с вторым входом второго последовательного регистра, выход которого соединен с вторым входом повторителя. Выход повторителя является выходом блока коррекции.

Блок дешифрации содержит первый, второй и третий дешифраторы. Первый вход блока дешифратора является первым входом первого дешифратора. Второй, третий, четвертый и пятый входы блока дешифратора являются соответственно вторым, третьим, четвертым и пятым входами третьего дешифратора. Шестой вход блока дешифрации параллельно соединен с шестым входом третьего дешифратора и первым входом второго дешифратора. Седьмой вход блока дешифрации параллельно соединен с седьмым входом третьего дешифратора и вторым входом второго дешифратора. Восьмой и девятый входы блока дешифрации являются соответственно вторым и третьим входами первого дешифратора, первый выход которого соединен с первым входом третьего дешифратора. Второй выход первого дешифратора соединен с третьим входом второго дешифратора, а третий выход первого дешифратора является двадцать вторым выходом блока дешифрации. Первый, второй, третий и четвертый выходы второго дешифратора являются соответственно с восемнадцатого по двадцать первый выходами блока дешифрации. С первого по семнадцатый выходы третьего дешифратора являются соответственно с первого по семнадцатый выходами блока дешифрации.

В отличии от известных устройств, обеспечивающих правильное распознавание информации с некоторой вероятностью, в зависимости от различных условий, предлагаемое устройство выдает однозначное решение о типе передаваемых кадров коммуникационных протоколов подмножества процедур HDLC, при условии их качественного приема. Полезный эффект состоит в выделении параметров цифрового потока и получении однозначного решения о присутствии (или отсутствии) кадров определенного типа в общем информационном цифровом потоке.

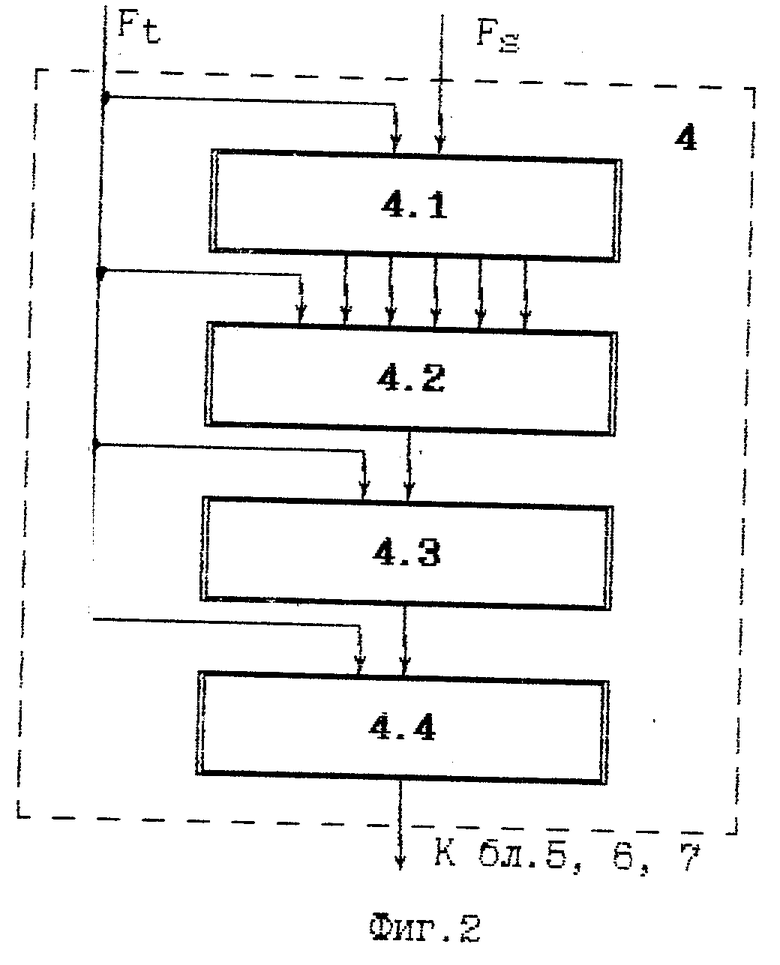

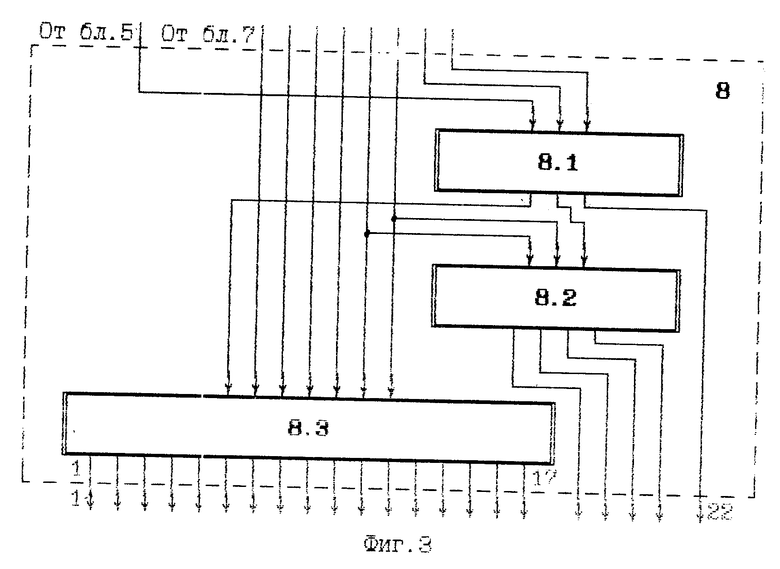

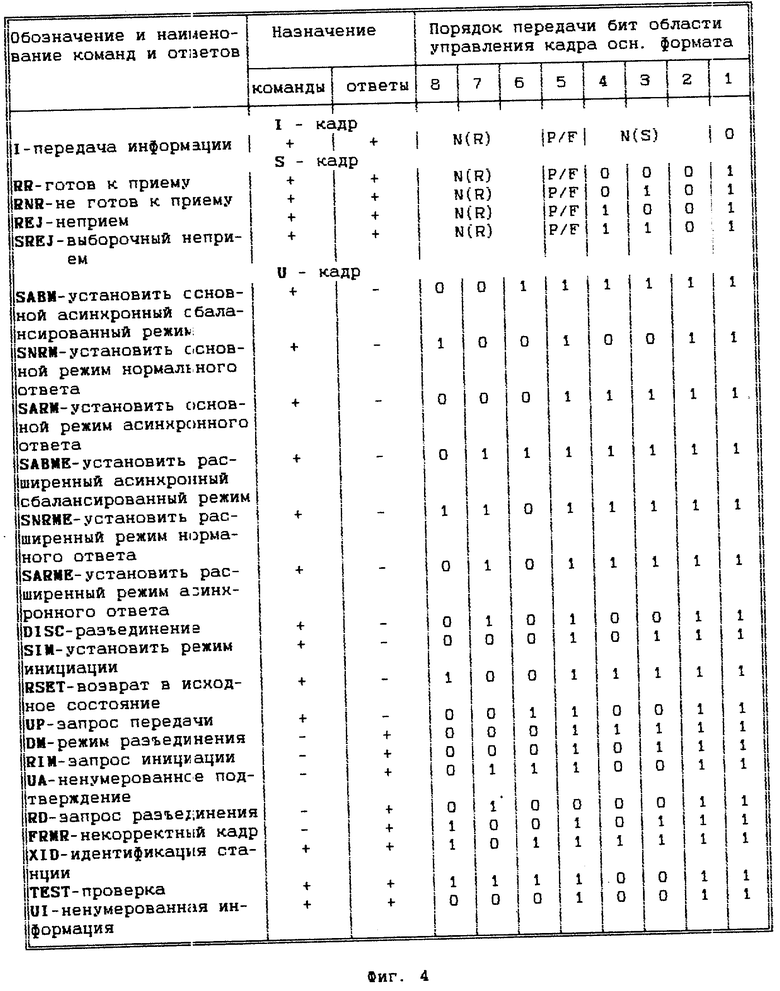

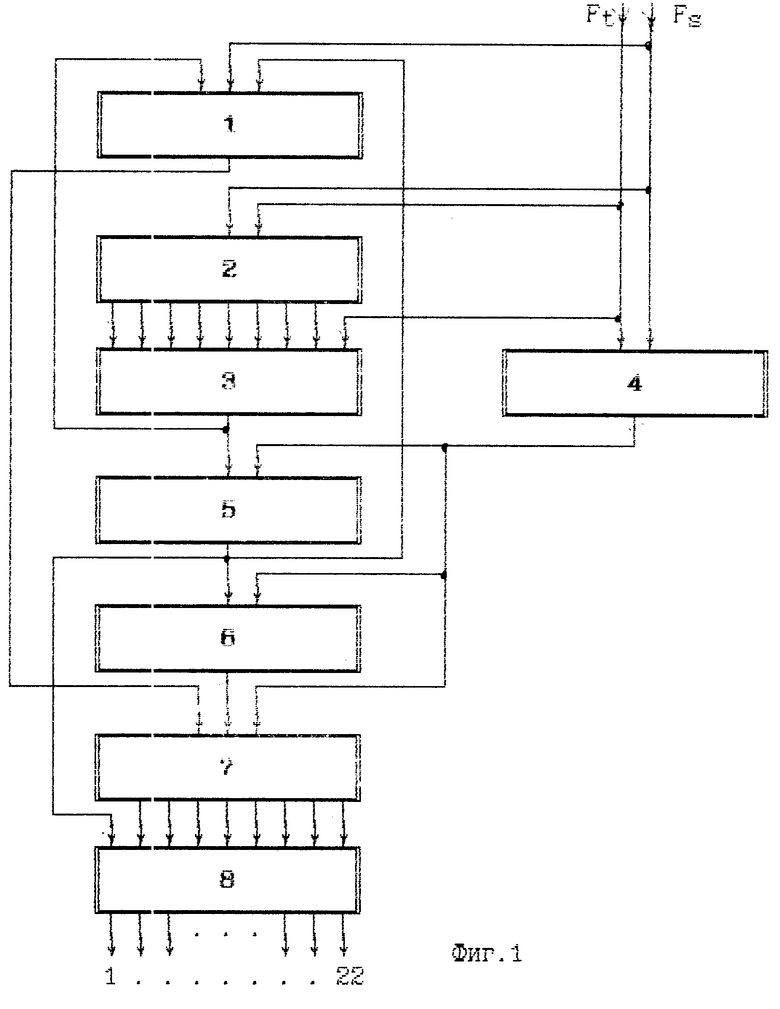

На фиг. 1 представлена электрическая функциональная схема предлагаемого устройства; на фиг. 2 электрическая функциональная схема блока коррекции; на фиг. 3 электрическая функциональная схема блока дешифрации; на фиг. 4 - структура области управления кадров основного формата коммуникационных протоколов подмножества процедур HDLC.

Устройство поиска информации, показанное на фиг. 1, содержит коммутатор 1, первый регистр 2, блок сравнения 3, блок коррекции 4, регистр стратегии поиска 5, второй 6 и третий 7 регистры, блок дешифрации 8. При этом первый вход блока коррекции 4, параллельно соединенный с вторым входом первого регистра 2 и девятым входом блока сравнения 3, является первым входом Ft устройства поиска информации. Первый вход первого регистра 2, параллельно соединенный с вторыми входами коммутатора 1 и блока коррекции 4, является вторым входом Fs устройства поиска информации. Выход коммутатора 1 соединен с первым входом третьего регистра 7. Первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы первого регистра 2 соединены соответственно с первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым входами блока сравнения 3. Выход блока сравнения 3 параллельно соединен с первым входами регистра стратегии поиска 5 и коммутатора 1. Выход блока коррекции 4 параллельно соединен с вторыми входами регистра стратегии поиска 5, второго регистра 6 и третьим входом третьего регистра 7. Выход регистра стратегии поиска 5 параллельно соединен с первыми входами второго регистра 6, блока дешифрации 8 и третьим входом коммутатора 1. Выход второго регистра 6 соединен с вторым входом третьего регистра 7. Первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой выходы третьего регистра 7 соединены соответственно с вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым входами блока дешифрации 8. С первого по двадцать второй выходы блока дешифрации 8 являются соответственно с первого по двадцать второй выходами устройства поиска информации.

Блок коррекции 4, показанный на фиг. 2, содержит первый последовательный регистр 4.1, блок сравнения 4.2, второй последовательный регистр 4.3 и повторитель 4.4. Первый вход блока коррекции 4 параллельно соединен с первыми входами первого 4.1 и второго 4.3 последовательных регистров, блока сравнения 4.2 и повторителя 4.4. Второй вход блока коррекции 4 является вторым входом первого последовательного регистра 4.1, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с вторым, третьим, четвертым, пятым и шестым входами блока сравнения 4.2. Выходы блока сравнения 4.2 соединен с вторым входом второго последовательного регистра 4.3, выход которого соединен с вторым входом повторителя 4.4. Выход повторителя 4.4 является выходом блока коррекции 4.

Блок дешифрации 8, показанный на фиг.3, содержит первый 8.1, второй 8.2 и третий 8.3 дешифраторы. Первый вход блока дешифрации 8 является первым входом первого дешифратора 8.1. Второй, третий, четвертый и пятый входы блока дешифрации 8 являются соответственно вторым, третьим, четвертым и пятым входами третьего дешифратора 8.3. Шестой вход дешифрации 8 параллельно соединен с шестым входом третьего дешифратора 8.3 и первым входом второго дешифратора 8.2. Седьмой вход блока дешифрации 8 параллельно соединен с седьмым входом третьего дешифратора 8.3 и вторым входом второго дешифратора 8.2. Восьмой и девятый входы блока дешифрации 8 соединены соответственно с вторым и третьим входами первого дешифратора 8.1, первый выход которого соединен с первым входом третьего дешифратора 8.3. Второй выход первого дешифратора 8.1 соединен с третьим входом второго дешифратора 8.2, а третий выход первого дешифратора 8.1 является двадцать вторым выходом блока дешифрации 8. Первый, второй, третий и четвертый выходы второго дешифратора 8.2 являются соответственно с восемнадцатого по двадцать первый выходами блока дешифрации 8. С первого по семнадцатый выходы третьего дешифратора 8.3 являются соответственно с первого по семнадцатый выходами блока дешифрации 8.

Устройство работает следующим образом.

Входными сигналами для устройства поиска информации (фиг.1) являются сигнальная цифровая последовательность Fs и сигнал тактовой частоты Ft, поступающие с модема.

Коммутатор 1 служит для коммутации входной цифровой последовательности на вход третьего 7 регистра. При поступлении на первый вход коммутатора 1 управляющего сигнала осуществляется коммутация входного потока, поступающего на второй вход коммутатора 1, к его выходу. При приходе управляющего сигнала на третий вход коммутатора 1 происходит отключение второго входа коммутатора 1 от его выхода.

Первый регистр предназначен для последовательного выделения восьми элементов входного цифрового потока, поступающего на его первый вход.

Блок сравнения 3 предназначен для определения наличия на его первом - восьмом входах кодовой комбинации 01111110, соответствующей "флагу". В случае получения положительного решения на выходе блока сравнения 3 формируется управляющий сигнал. Тактовая синхронизация работы первого регистра 2 и блока сравнения 3 обеспечивается с помощью Ft.

Блок коррекции 4 предназначен для выделения и удаления бит "прозрачности", включаемых в цифровую последовательность на передающей станции с целью исключения случайного появления комбинации, соответствующей "флагу". Данная цель достигается путем удаления из Ft тактового импульса, соответствующего биту "прозрачности". Скорректированная Fti, поступающая с выхода блока коррекции 4, обеспечивает тактовую синхронизацию работы регистра стратегии поиска 5, второго 6 и третьего 7 регистров.

Регистр стратегии поиска 5 предназначен для определения момента времени, в течение которого на ячейках третьего регистра 7 находятся биты входного цифрового потока, соответствующие области управления кадра, и обеспечения кадровой синхронизации работы блока дешифрации 8. Регистр стратегии поиска 5 представляет собой шестнадцатиразрядный последовательный регистр, в котором при поступлении на его первый вход управляющего импульса производится запись 1 в первую ячейку и обнуление содержания других ячеек. Перемещение управляющего импульса, поступившего с блока сравнения 3, осуществляется под воздействием Fti. После прохождения шестнадцати тактовых импульсов Fti управляющий импульс появляется на выходе регистра стратегии поиска 5.

Второй регистр 6 предназначен для выработки управляющего импульса на обнуление содержания ячеек третьего регистра 7 после считывания с него информации. Он представляет собой двухразрядный последовательный регистр, с выхода второго разряда которого управляющий сигнал поступает на второй вход обнуления третьего регистра 7.

Третий регистр 7 предназначен для последовательного выделения восьми элементов входного цифрового потока, поступающего на его первый вход. При наличии управляющего импульса на втором входе происходит обнуление содержания ячеек третьего регистра 7.

Блок дешифровки 8 предназначен для преобразования восьми элементов кода области управления кадра (фиг. 4), поступившего с третьего регистра 7, в информацию о наличии одного из двадцатиодного возможного типа кадра или комбинации, не соответствующей ни одному из разрешений значений области управления кадра. Срабатывание блока дешифрации 8 осуществляется в момент прихода управляющего сигнала с выхода регистра стратегии поиска 5.

Блок коррекции 4 (фиг. 2) работает следующим образом:

Первый последовательный регистр 4.1 служит для выявления пяти бит входного цифрового потока, поступающего на его второй вход.

Блок сравнения 4.2 служит для выделения наличия на ячейках первого последовательного регистра 4.1 кодовой комбинации 11111. При появлении данной комбинации на втором шестом входах блока сравнения на его выходе вырабатывается управляющий импульс.

Второй последовательный регистр 4.3 предназначен для определения момента времени прихода на вход устройства бита "прозрачности". Управляющий сигнал, поступивший на первый вход второго последовательного регистра 4.3, с приходом следующего тактового импульса поступает на его выход. Тактовая синхронизация работы первого 4.1 и второго 4.3 последовательных регистров и блока сравнения 4.2 обеспечивается Ft, поступающей на их первые входы.

Повторитель 4.4 предназначен для изъятия из Ft тактового импульса, соответствующего моменту прихода на вход устройства бита "прозрачности". Он представляет собой ретранслятор Ft, поступающей на его первый вход. Однако в момент прихода на второй вход повторителя 4.4 управляющего сигнала с второго последовательного регистра 4.3 ретрансляция Ft прекращается. Таким образом, на выходе повторителя 4.4, являющемся выходом блока коррекции 4, мы имеем Fti, в которой отсутствует тактовый импульс, соответствующий биту "прозрачности".

Блок дешифрации 8 (фиг. 3) работает следующим образом.

Первый дешифратор 8.1 предназначен для определения класса кадра (I, S или U-кадр). Если на третьем входе первого дешифратора 8.1 присутствует 0, то принимается решение о том, что данный кадр является I-кадром и на третьем выходе первого дешифратора 8.1 формируется информационный сигнал. Если на втором и третьем входах первого дешифратора 8.1, являющихся соответственно восьмым и девятым входами блока дешифрации 8, присутствует кодовая комбинация 01, то принимается решение о том, что данный кадр является S-кадром и управляющий сигнал формируется на втором выходе первого дешифратора 8.1, а если на втором и третьем входах первого дешифратора 8.1 присутствует кодовая комбинация 11, то принимается решение о том, что данный кадр является U-кадром и управляющий сигнал формируется на первом выходе первого дешифратора 8.1. Кадровая синхронизация работы первого дешифратора 8.1 осуществляется с помощью управляющего сигнала, поступающего на его первый вход, являющийся первым входом блока дешифрации 8, с выхода регистра стратегии поиска 5.

Второй дешифратор 8.2 обеспечивает определение типа кадра класса S. При наличии на его первом и втором входах, являющихся шестым и седьмым входами блока дешифрации 8, кодовых комбинаций 00, 01, 10, 11 принимается решение о том, что данный кадр является соответственно кадром RR, RNR, REJ или SREJ и соответственно на первом четвертом выходах второго дешифратора 8.2, являющихся соответственно восемнадцатым двадцать первым выходами блока дешифрации 8, формируется информационный сигнал. Принятие решения вторым дешифратором 8.2 возможно только в момент поступления на его третий вход управляющего импульса с второго выхода первого дешифратора 8.1.

Третий дешифратор 8.3 обеспечивает определение типа кадра класса U. При наличии на его втором седьмом входах, являющихся соответственно вторым - седьмым входами блока дешифрации 8, кодовых комбинаций 000100, 001100, 001111, 010000, 010100, 010111, 011100, 011111, 100100, 100101, 101111, 10111, 110111, 111100 принимается решение о том, что данный кадр является соответственно кадром UI, UP, SABM, RD, DISC, SARME, UA, SNRM, FRMR, RSET, XID, SNRME, TEST и соответственно на втором, пятом семнадцатом выходах третьего дешифратора 8.3, являющихся соответственно вторым, пятым семнадцатым выходами блока дешифрации 8, формируется информационный сигнал. При наличии на втором седьмом входах третьего дешифратора кодовой комбинации 000101 принимается решение о том, что данный кадр является кадром SIM или RIM (в зависимости от того принимается сигнал главной или подчиненной станции) и на третьем выходе третьего дешифратора 8.3, являющемся третьим выходом блока дешифрации 8, формируется информационный сигнал. При наличии на втором седьмом входах третьего дешифратора кодовой комбинации 000111 принимается решение о том, что данный кадр является кадром SARM или DM (в зависимости от того принимается сигнал главной или подчиненной станции) и на четвертом выходе третьего дешифратора 8.3, являющемся четвертым выходом блока дешифрации 8, формируется информационный сигнал. Принятие решения третьим дешифратором 8.3 возможно только в момент прихода на его первый вход управляющего сигнала с первого выхода первого дешифратора 8.1.

Таким образом, в целом устройство работает следующим образом: с помощью первого регистра 2 осуществляется последовательное выделение восьми элементов цифрового потока, которые в блоке сравнения 3 сопоставляются с образом "флаговой" комбинации. При совпадении восьмиэлементного кода и образа "флаговой" комбинации блок сравнения 3 генерирует управляющий сигнал, под воздействием которого происходит подключение входного цифрового потока на вход третьего регистра 7 и начинает функционировать регистр стратегии поиска 5. Тактовая синхронизация работы первого регистра 2 и блока сравнения 3 осуществляется с помощью Ft, поступающей с модема. Регистр стратегии поиска 5, в соответствии с априорно известной информацией о структуре кадров цифрового потока, после поступления на его вход управляющего сигнала производит отсчет 16 тактовых импульсов с целью определения момента нахождения на ячейках третьего регистра 7 кодовой комбинации, соответствующей области управления кадра. С приходом шестнадцатого тактового импульса регистр стратегии поиска генерирует управляющий сигнал, под воздействием которого блоком дешифрации 8 производится дешифрация кодовой комбинации области управления кадра, находящейся в данный момент времени на ячейках третьего регистра 7, с выделением информации о типе кадра и отключение входного цифрового потока от входа третьего регистра 7, а также начало функционирования второго регистра 6, который с приходом следующего тактового импульса генерирует управляющий сигнал на обнуление содержания ячеек третьего регистра 7 после снятия с них информации о содержании области управления кадра. Тактовая синхронизация работы регистра стратегии поиска 5, второго 6 и третьего 7 регистров осуществляется с помощью Fti, поступающей от блока коррекции 4. Fti отличается от Ft тем, что в блоке коррекции 4 из Ft изъят тактовый импульс, соответствующий моменту прихода на вход устройства бита "прозрачности".

С позиций классификации по функциональному назначению следует отметить, что коммутатор 1 может быть реализован на микросхемах серии К555ИП7; первый регистр 2, регистр стратегии поиска 5, второй регистр 6, третий регистр 7, первый последовательный регистр 4.1, второй последовательный регистр 4.3 на К555ИР8; блоки сравнения 3 и 4.2 на К555СП1; повторитель 4.4 на К555ЛИ1; первый 8.1, второй 8.2 и третий 8.3 дешифраторы на К555ИД7 (Шило В.Л. Популярные цифровые микросхемы: Справочник. М. Радио и связь, 1987, 352 с. ил. Массовая радиобиблиотека. Вып.1111).

Таким образом, преимущества данного устройства состоят в возможности работы в режиме реального времени, нулевой вероятности пропуска (в случае наличия априорной достоверной информации о структуре области управления кадра в коммуникационных протоколах), простоте реализации и модификации под любые семейства коммуникационных протоколах диалогового типа. Вероятность ложных тревог зависит от устойчивости приема сигнала в канале передачи данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1996 |

|

RU2115952C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2000 |

|

RU2179334C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2094845C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2001 |

|

RU2199148C1 |

| АВТОМАТ УПРАВЛЕНИЯ КОМАНДАМИ ПО ПЕРЕДАЧЕ ПАКЕТОВ ДАННЫХ | 1997 |

|

RU2116002C1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ИСКАЖЕНИЯ ИНФОРМАЦИОННОГО ЦИФРОВОГО ПОТОКА | 2004 |

|

RU2273045C1 |

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

Изобретение относится к электросвязи и может быть использовано для поиска информации и идентификации применяемых в цифровых системах связи кадров коммуникационных протоколов, относящихся к подмножеству процедур HDLC. Целью изобретения является разработка устройства поиска информации по цифровому потоку с конечной априорной неопределенностью относительно его параметров, обеспечивающего повышение достоверности поиска, идентификации информации за счет получения однозначности решения. Для реализации этой цели в устройство введены коммутатор 1, регистр стратегии поиска 5, третий регистр 7. Первый регистр 2 и блок сравнения осуществляют поиск и идентификацию "флаговой" комбинации. Третий регистр 7 и блок дешифрации 8 осуществляют выделение из цифрового потока кодовой комбинации области управления кадра и ее дешифрацию для получения информации о типе кадра. Блок коррекции 4 обеспечивает выявление и удаление из сигнала тактовой синхронизации импульсов, соответствующих времени поступления на вход устройства бит "прозрачности". При таком построении устройства достигается возможность работы в режиме реального времени, нулевая вероятность пропуска /в случае наличия априорной достоверной информации о структуре области управления кадра в коммуникационных протоколах/, простота реализации и модификации под любые семейства коммуникационных протоколов диалогового типа. 2 з. п. ф-лы, 4 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| SU, авторское свидетельство, 1621049, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| SU, авторское свидетельство, 1711185, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-12-27—Публикация

1995-05-18—Подача