Изобретение относится к электросвязи и может быть использовано для поиска информации и оперативной идентификации применяемого в цифровых системах связи и, в частности, в сети передачи данных (СПД) типа Internet коммуникационного протокола TFTP (Trivial File Transfer Protocol), относящихся к семейству известных процедур DARPA (Протоколы информационно-вычислительных сетей. Справочник. Под ред. И.А.Мизина, А.П.Кулешова. - М.: Радио и связь, 1990, с. 503), стандартизированному министерством обороны США.

Известный аналог предлагаемого устройства описан в авторском свидетельстве СССР N 1621049, кл. G 06 F 15/40, 09.01.89 и содержит регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации.

В ходе выполнения задачи по приему и поиску цифровых потоков сообщений необходимо определить параметры цифрового потока, по которым производится поиск информации, идентификация пакетов и соответствие последовательности передачи кадров правилам обмена данными, установленным для данного протокола, а известный аналог не выполняет этих требований - определение коммуникационных пакетов реализуется в нем с вероятностью правильного распознавания значительно меньше 0,1, так как распознавание производится статистическим способом, а каждый сеанс связи является в своем роде уникальным и не учитывает признаков последовательности передачи информации (правил обмена).

Ближайшее устройство поиска информации (прототип) к предлагаемому описано в авторском свидетельстве СССР N 1711185, кл. G 06 F 15/40, 05.04.89. В указанном изобретении описано устройство поиска информации, содержащее регистры верхней и нижней границ, сумматор-вычислитель, регистр стратегии поиска, вычитающий и суммирующие счетчики, схемы сравнения, блок памяти, регистр ключа, выходной регистр, группу элементов И и ИЛИ, триггер, вход запуска, входы адресов верхней и нижней границ, вход кода критерия смены стратегии поиска, вход ключа, выход адреса, выход признака отсутствия информации и распределитель импульса.

Недостатком данного устройства является невозможность получения однозначного решения в связи с низким уровнем достоверности и вероятности идентификации (вероятность выделения параметров цифрового потока и идентификации коммуникационного протокола менее 0,3), так как прототип реализует поиск информационных блоков в массиве посредством дихотомического метода без учета наличия большого числа типов возможных пакетов и их допустимой последовательности.

Целью изобретения является разработка устройства поиска информации по цифровому потоку с конечной априорной неопределенностью относительно его параметров, обеспечивающего повышение достоверности поиска, идентификации информации за счет получения однозначного решения о том, является ли данный цифровой поток цифровым потоком протокола TFTP.

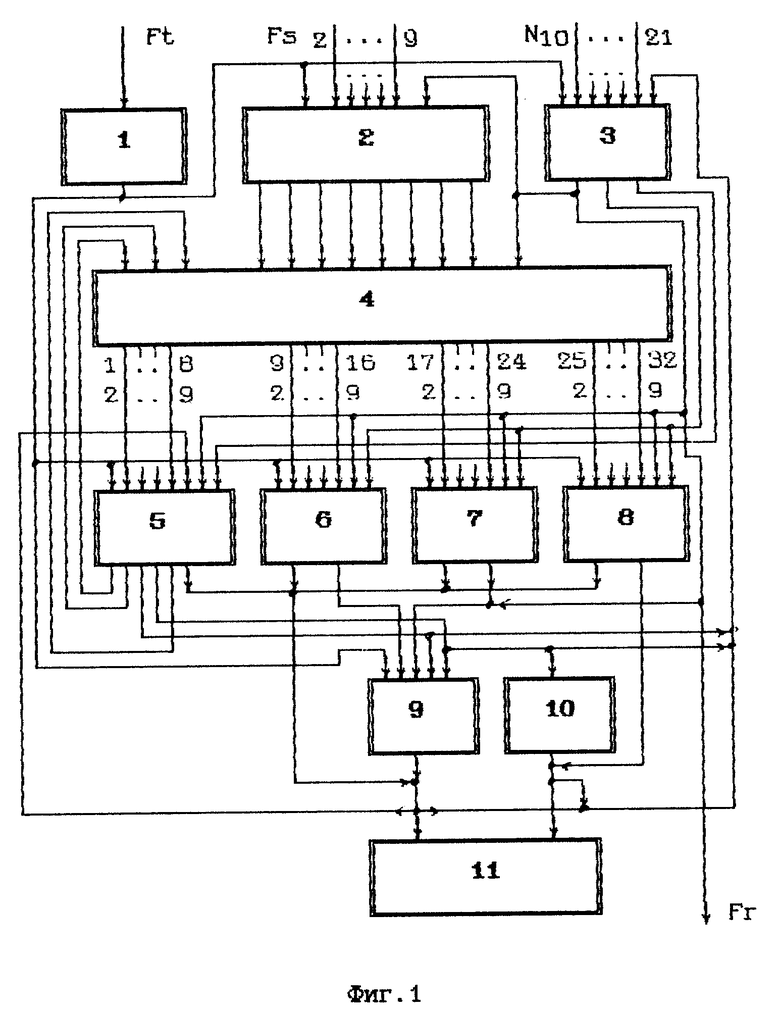

Поставленная цель достигается тем, что в известное устройство поиска информации, содержащее блок памяти, регистр стратегии поиска и вычитающий счетчик, дополнительно введены следующие элементы: делитель частоты, коммутатор, первый, второй, третий и четвертый блоки селекции, формирователь временных интервалов и блок индикации. Выход делителя частоты соединен с первыми входами блока памяти, вычитающего счетчика, первого, второго, третьего и четвертого блоков селекции, регистра стратегии поиска. Выходы блока памяти соединены соответственно с четвертым - одиннадцатым входами коммутатора, а первый выход вычитающего счетчика соединен с десятым входом блока памяти, двенадцатым входом коммутатора, одиннадцатым входом первого блока селекции, десятыми входами второго, третьего и четвертого блоков селекции, третьим входом регистра стратегии поиска и является командным выходом устройства. Второй выход вычитающего счетчика соединен с одиннадцатыми входами второго, третьего и четвертого блоков селекции, а третий выход вычитающего счетчика соединен с двенадцатым входом первого блока селекции. Выходы коммутатора соединены с вторым - девятым входами первого, второго, третьего и четвертого блоков селекции соответственно, а первый и второй выходы первого блока селекции соединены соответственно с первым и вторым входами коммутатора. При этом третий выход первого блока селекции соединен с четвертым входом регистра стратегии поиска и четырнадцатым входом вычитающего счетчика, а четвертый выход первого блока селекции соединен с пятым входом регистра стратегии поиска, четырнадцатым входом вычитающего счетчика и входом формирователя временных интервалов. Пятый выход первого блока селекции соединен с третьим входом коммутатора. Шестой выход первого блока селекции и первые выходы второго, третьего и четвертого блоков селекции, выход регистра стратегии поиска соединены с первым входом блока индикации, десятым входом первого блока селекции и четырнадцатым входом вычитающего счетчика. Второй выход второго блока селекции соединен с вторым входом регистра стратегии поиска, а второй выход третьего блока селекции соединен с третьим входом регистра стратегии поиска. При этом второй выход четвертого блока селекции и выход формирователя временных интервалов соединены с вторым входом блока индикации и четырнадцатым входом вычитающего счетчика. Вход делителя частоты, второй - девятый входы блока памяти и второй - тринадцатый входы вычитающего счетчика являются соответственно входом тактовой частоты, сигнальными и информационными входами устройства.

Блок памяти содержит инвертор, первый и второй суммирующий счетчики, коммутатор, элемент И, дифференцирующую цепь и ОЗУ. Выходы первого и второго суммирующих счетчиков соединены с соответствующими входами оперативного запоминающего узла (ОЗУ), другие входы которого соединены с соответствующими входами коммутатора. При этом выходы первого суммирующего счетчика через элемент И соединены с одним из входов второго суммирующего счетчика, другой вход которого соединен с соответствующим входом первого суммирующего счетчика и с выходом дифференцирующей цепи. Вход дифференцирующей цепи соединен с соответствующим входом коммутатора и ОЗУ, с входом инвертора, выход которого соединен с соответствующим входом коммутатора. Другой вход первого суммирующего счетчика, другие входы коммутатора и вход инвертора являются соответствующими входами блока памяти, выходами которого являются соответствующие выходы коммутатора.

Коммутатор содержит первый, второй, третий и четвертый триггеры, первый, второй, третий и четвертый буферные элементы. Один из входов первого, второго, третьего и четвертого триггеров является соответствующими входами коммутатора, а другие входы соединены с соответствующими входами коммутатора. Выход первого, второго, третьего и четвертого триггеров соединен с одним из входов соответственно первого, второго, третьего и четвертого буферных элементов; другие входы которых являются соответствующими входами коммутатора, а их выходы являются соответствующими выходами коммутатора.

Первый блок селекции содержит первую, вторую и третью линии задержки, первый, второй и третий коммутаторы первый, второй, третий и четвертый дешифраторы, элемент И. Один из входов первого, второго, третьего и четвертого дешифраторов является соответствующим входом первого блока селекции. Другие входы первого и второго дешифраторов соединены с соответствующими выходами второго коммутатора, а другие входы третьего и четвертого дешифраторов соединены с соответствующими выходами третьего коммутатора. При этом один из выходов первого дешифратора через вторую линию задержки соединен с соответствующим входом второго коммутатора. Вход первой линии задержки соединен с соответствующими выходами второго дешифратора, являющимися соответствующими выходами первого блока селекции, а выход первой линии задержки соединен с одним из входов первого коммутатора, выходы которого соединены с соответствующими входами второго и третьего коммутаторов. При этом другой вход второго коммутатора соединен с одним из входов первого коммутатора и является соответствующим входом первого блока селекции. Один из выходов третьего дешифратора через третью линию задержки соединен с соответствующим входом третьего коммутатора. Один из входов элемента И соединен с соответствующим выходом четвертого дешифратора, при этом другие выходы первого, второго и третьего дешифраторов соединены с соответствующим выходом четвертого дешифратора и являются соответствующим выходом первого блока селекции. Другие выходы четвертого дешифратора и выход элемента И являются соответствующими выходами первого блока селекции. Другие входы первого, третьего коммутаторов и элемента И являются соответствующими входами первого блока селекции.

Второй блок селекции содержит первый, второй, третий и четвертый дешифраторы, первый и второй коммутаторы, линию задержки, суммирующий счетчик и элемент И. Один из входов первого, второго, третьего и четвертого дешифраторов соединены между собой и являются соответствующим входом второго блока селекции. Другие входы первого дешифратора, соединенные с соответствующими входами второго дешифратора, и другие входы третьего дешифратора, соединенные с соответствующими входами второго дешифратора, являются соответствующими входами второго блока селекции. Другие входы четвертого дешифратора соединены с соответствующими выходами первого коммутатора, причем выход первого дешифратора соединен с соответствующими входами первого коммутатора и с соответствующим входом второго коммутатора. Выход второго дешифратора соединен с соответствующим входом первого, второго коммутаторов, суммирующего счетчика и через линию задержки соединен с соответствующим входом первого коммутатора. Выход третьего дешифратора соединен с соответствующим входом второго коммутатора, выход которого соединен с соответствующим входом первого коммутатора. Один ив выходов суммирующего счетчика соединен с соответствующим входом элемента И. Другой вход суммирующего счетчика и элемента И являются соответствующими входами второго блока селекции. Другие выходы первого коммутатора, суммирующего счетчика, соединенные с выходом четвертого дешифратора, и выход элемента И являются соответствующими выходами второго блока селекции.

Третий блок селекции содержит первый, второй, третий и четвертый дешифраторы, первый и второй коммутаторы, линию задержки, суммирующий счетчик и элемент И. Один из входов первого, второго, третьего и четвертого дешифраторов соединены между собой и являются соответствующим входом третьего блока селекции. Другие входы первого дешифратора, соединенные с соответствующими входами второго дешифратора, и другие входы третьего дешифратора, соединенные с соответствующими входами второго дешифратора, являются соответствующими входами третьего блока селекции. Другие входы четвертого дешифратора соединены с соответствующими выходами первого коммутатора, причем выход первого дешифратора соединен с соответствующими входами первого коммутатора и с соответствующим входом второго коммутатора. Выход второго дешифратора соединен с соответствующим входом первого, второго коммутаторов, суммирующего счетчика и через линию задержки соединен с соответствующим входом первого коммутатора. Выход третьего дешифратора соединен с соответствующим входом второго коммутатора, выход которого соединен с соответствующим входом первого коммутатора. Один из выходов суммирующего счетчика соединен с соответствующим входом элемента И, причем другой вход суммирующего счетчика и элемента И являются соответствующими входами третьего блока селекции. Другие выходы первого коммутатора, суммирующего счетчика, соединенные с выходом четвертого дешифратора, и выход элемента И являются соответствующими выходами третьего блока селекции.

Четвертый блок селекции содержит первый и второй коммутаторы, линию задержки, первый, второй и третий дешифраторы, суммирующий счетчик и элемент И. Один из входов первого, второго коммутаторов и суммирующего счетчика соединены между собой и являются соответствующим входом четвертого блока селекции. Выход суммирующего счетчика через линию задержки соединен с соответствующим входом второго коммутатора. Один из входов первого, второго, третьего дешифраторов, суммирующего счетчика и элемента И, соединенные между собой, являются соответствующим входом четвертого блока селекции. Один из входов первого коммутатора соединен с соответствующим входом элемента И и является соответствующим входом четвертого блока селекции, а другие входы первого коммутатора являются соответствующими входами четвертого блока селекции. Другие входы первого и второго дешифраторов соединены с соответствующими выходами второго коммутатора. Другие входы второго коммутатора и третьего дешифратора соединены с соответствующими выходами первого коммутатора. Один из выходов первого дешифратора соединен с другим входом суммирующего счетчика. Другой выход первого дешифратора, соединенный с выходом второго дешифратора и элемента И, и выход третьего дешифратора, соединенный с другим входом элемента И, являются соответствующими выходами четвертого блока селекции.

Регистр стратегии поиска содержит триггер, первый - четвертый элементы И и линию задержки. Один из входов первого и второго элементов И, соединенные между собой, являются соответствующим входом регистра стратегии поиска. При этом выход первого элемента И соединен с выходом четвертого элемента И и является выходом регистра стратегии поиска. Выход второго и третьего элементов И через линию задержки соединены с соответствующим входом триггера, выход которого соединен с соответствующим входом первого, второго, третьего и четвертого элементов И. Другой вход первого элемента И соединен с соответствующим входом второго, третьего и четвертого элементов И и является соответствующим входом регистра стратегии поиска. Другие входы триггера, соединенные между собой, другой вход третьего и четвертого элементов И являются соответствующими входами регистра стратегии поиска.

В отличие от известных устройств, обеспечивающих только вероятностное распознавание информации, в зависимости от различных условий, предлагаемое устройство выдает однозначное решение о наличии (либо отсутствии) в данной СПД коммуникационного протокола TFTP, при условии качественного приема цифрового потока. Полезный эффект состоит в выделении параметров цифрового потока и получении однозначного решения о присутствии (или отсутствии) протокола TFTP в общем информационном цифровом потоке.

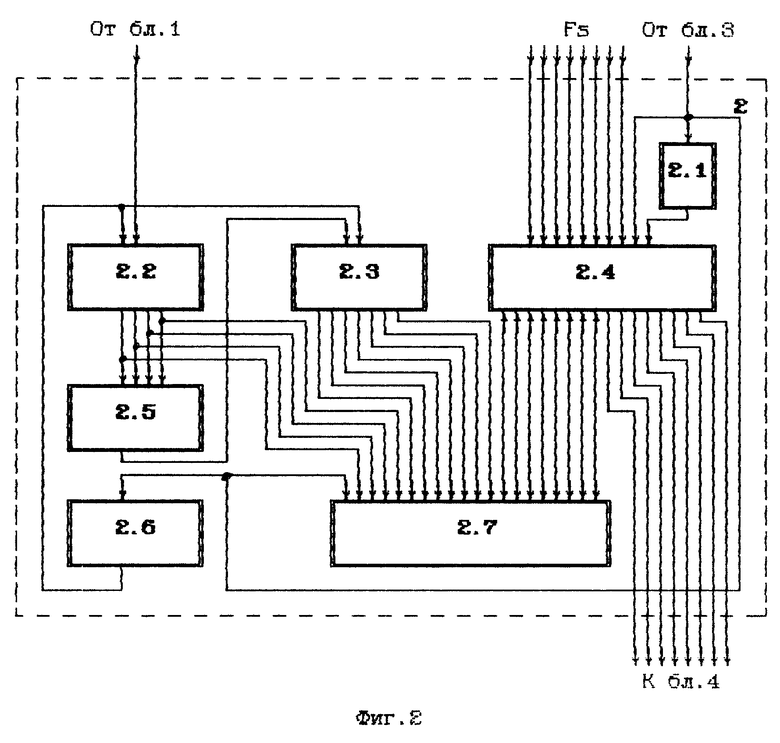

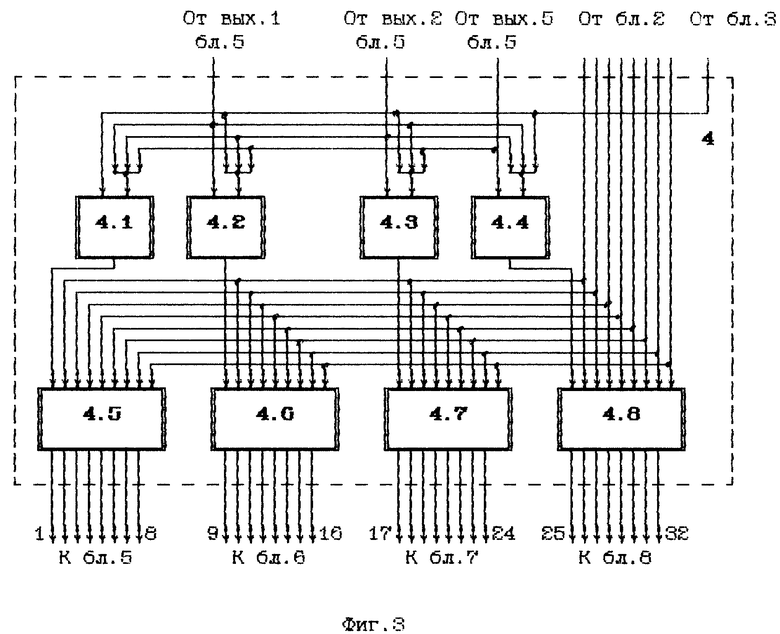

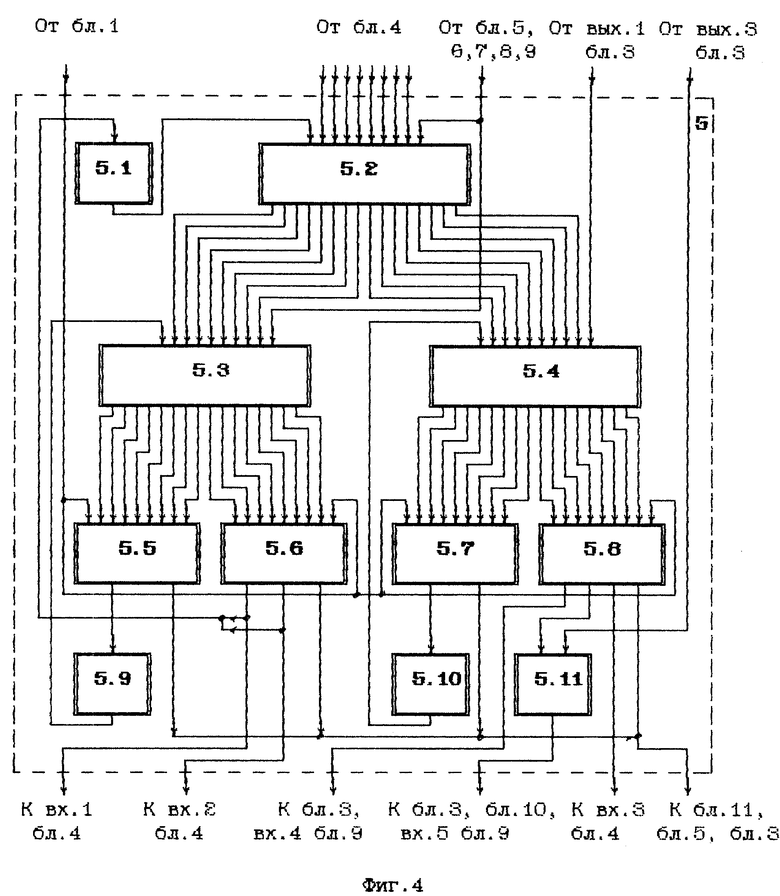

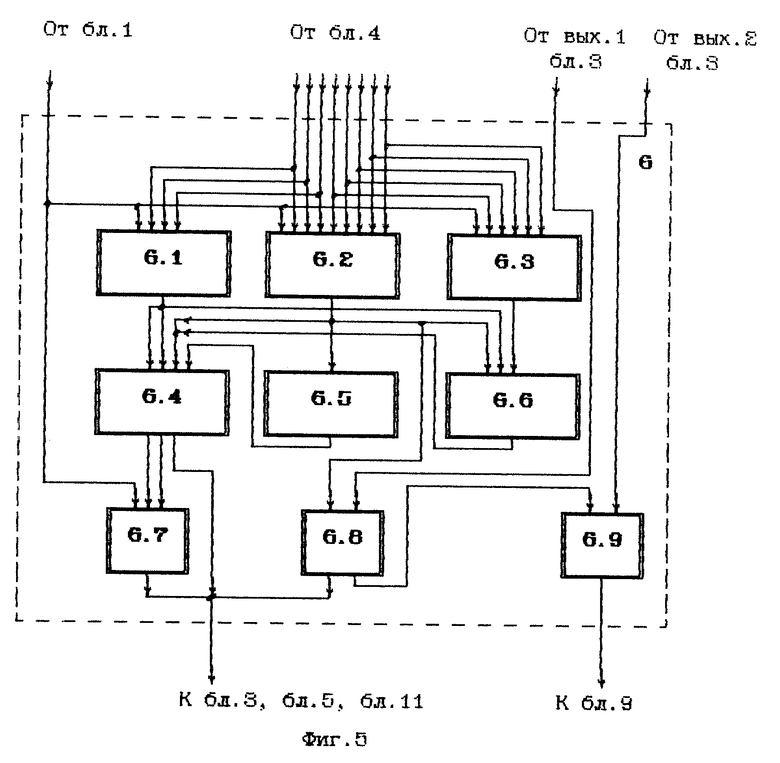

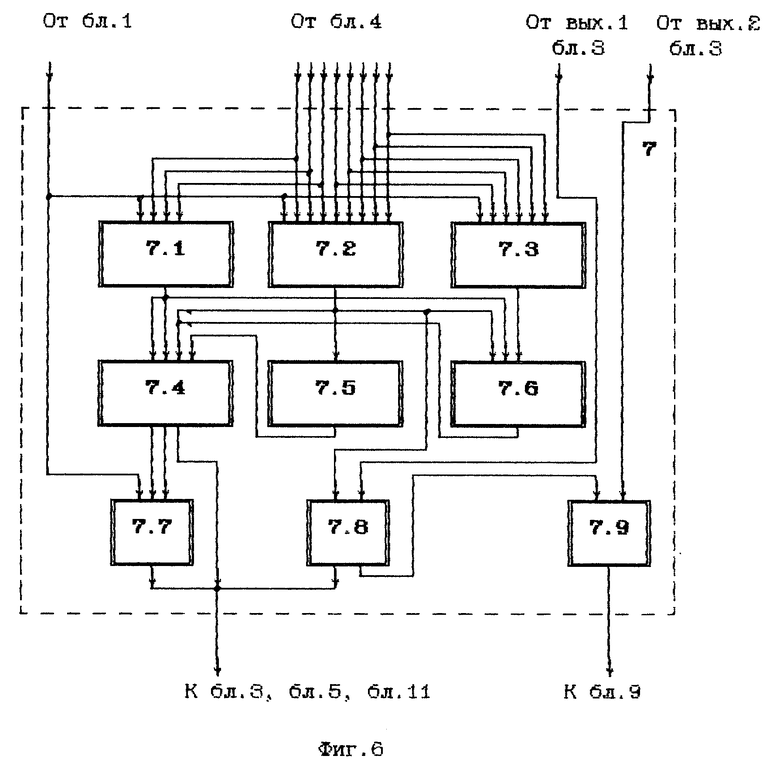

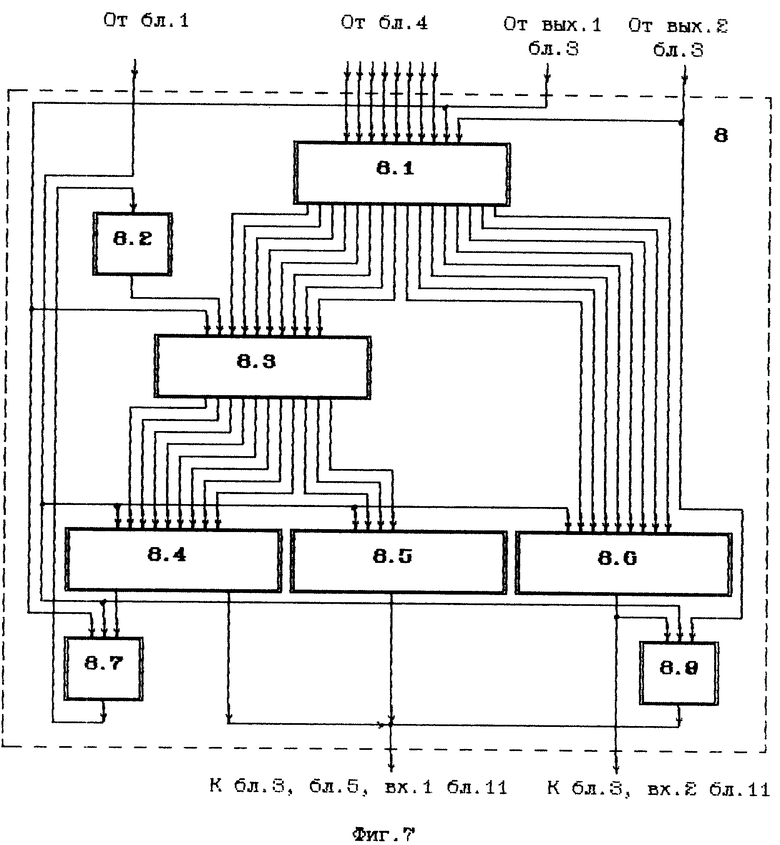

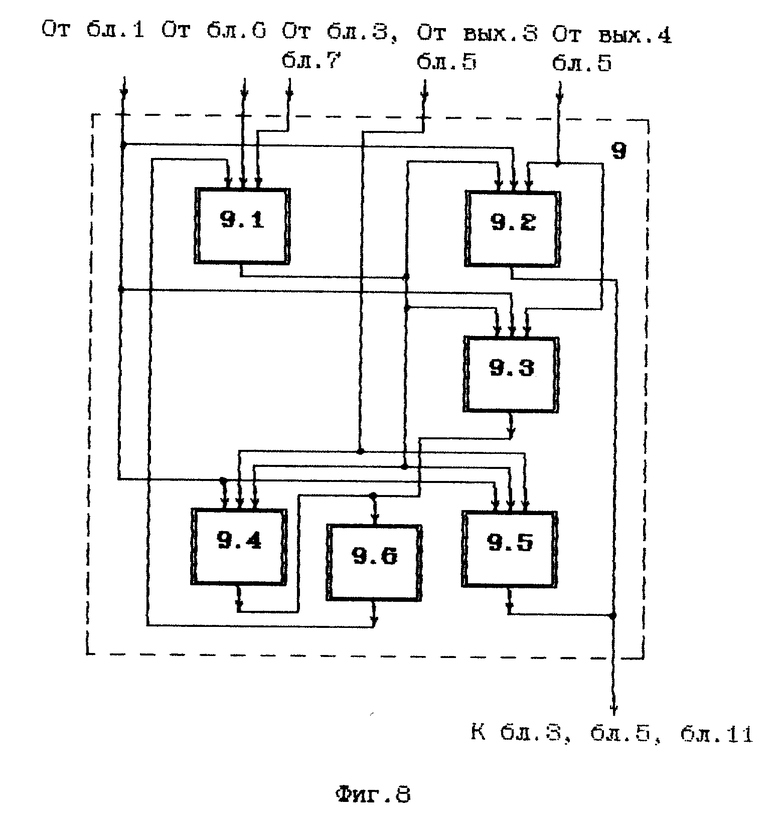

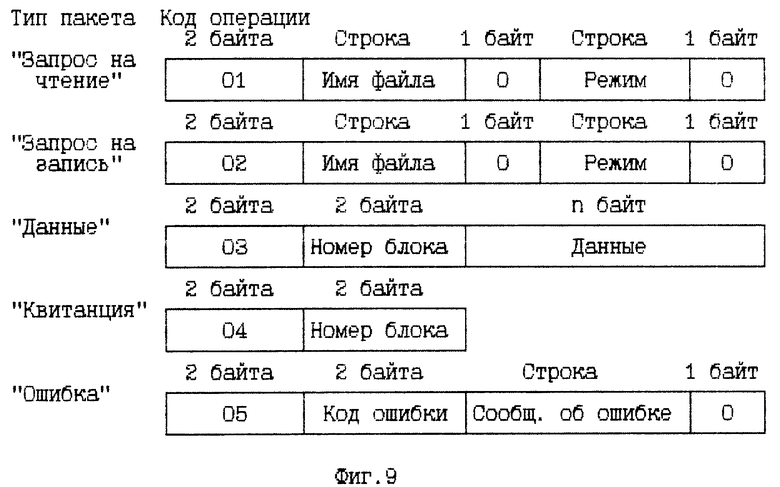

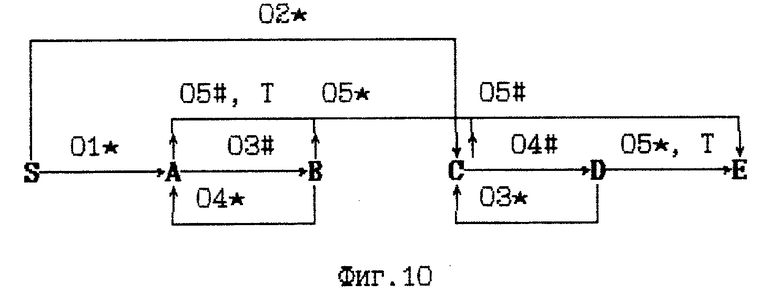

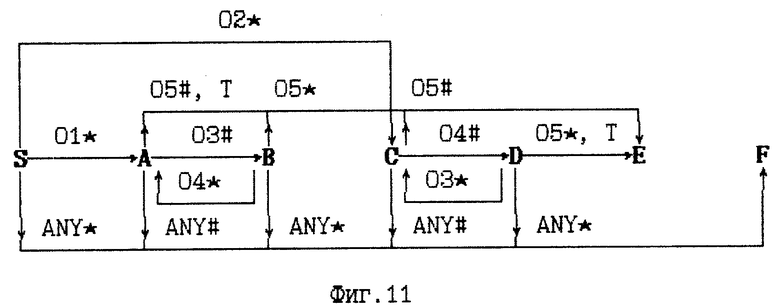

На фиг. 1 представлена электрическая функциональная схема предлагаемого устройства; на фиг.2 - электрическая функциональная схема блока памяти; на фиг. 3 - электрическая функциональная схема коммутатора; на фиг.4 - электрическая функциональная схема первого блока селекции; на фиг.5 - электрическая функциональная схема второго блока селекции; на фиг.6 - электрическая функциональная схема третьего блока селекции; на фиг.7 - электрическая функциональная схема четвертого блока селекции; на фиг.8 - электрическая функциональная схема регистра стратегии поиска; на фиг.9 - структура пакетов протокола TFTP; на фиг. 10 - алгоритм функционирования коммуникационного протокола TFTP; на фиг.11 - алгоритм синтаксического распознавания коммуникационного протокола TFTP.

Устройство поиска информации, показанное на фиг.1, содержит делитель 1 частоты, блок 2 памяти, вычитающий счетчик 3, коммутатор 4, первый 5, второй 6, третий 7 и четвертый 8 блоки селекции, регистр 9 стратегии поиска, формирователь 10 временных интервалов и блок 11 индикации. При этом вход делителя 1 частоты является входом тактовой частоты Ft устройства поиска информации. Второй - девятый входы блока 2 памяти являются соответствующими сигнальными входами Fs устройства. Второй - тринадцатый входы вычитающего счетчика 3 являются соответствующими информационными входами N устройства поиска информации. Выход делителя 1 частоты соединен с первыми входами блока 2 памяти, вычитающего счетчика 3, первого 5, второго 6, третьего 7 и четвертого 8 блоков селекции, регистра 9 стратегии поиска. Первый - восьмой выходы блока 2 памяти соединены соответственно с четвертым - одиннадцатым входами коммутатора 4. Первый выход вычитающего счетчика 3 соединен с десятым входом блока 2 памяти, двенадцатым входом коммутатора 4, одиннадцатым входом первого блока 5 селекции, десятыми входами второго 6, третьего 7 и четвертого 8 блоков селекции, третьим входом регистра 9 стратегии поиска и является командным выходом Fr устройства. Второй выход вычитающего счетчика 3 соединен с одиннадцатыми входами второго 6, третьего 7 и четвертого 8 блоков селекции, а третий выход вычитающего счетчика 3 соединен с двенадцатым входом первого блока 5 селекции. Первый - восьмой, девятый - шестнадцатый, семнадцатый - двадцать четвертый и двадцать пятый - тридцать второй выходы коммутатора 4 соответственно соединены с вторыми - девятыми входами соответственно первого 5, второго 6, третьего 7 и четвертого 8 блоков селекции. Первый и второй выходы первого блока 5 селекции соединены соответственно с первым и вторым входами коммутатора 4, третий выход первого блока 5 селекции соединен с четвертым входом регистра 9 стратегии поиска и четырнадцатым входом вычитающего счетчика 3, четвертый выход первого блока 5 селекции соединен с пятым входом регистра 9 стратегии поиска, четырнадцатым входом вычитающего счетчика 3 и входом формирователя 10 временных интервалов. Пятый выход первого блока 5 селекции соединен с третьим входом коммутатора 4. Шестой выход первого блока 5 селекции, выход регистра 9 стратегии поиска и первые выходы второго 6, третьего 7 и четвертого 8 блоков селекции соединены с первым входом блока 11 индикации, десятым входом первого блока 5 селекции и четырнадцатым входом вычитающего счетчика 3. Второй выход второго блока 6 селекции соединен с вторым входом регистра 9 стратегии поиска, а второй выход третьего блока 7 селекции соединен с третьим входом регистра 9 стратегии поиска. Второй выход четвертого блока 8 селекции и выход формирователя 10 временных интервалов соединены с вторым входом блока 11 индикации и четырнадцатым входом вычитающего счетчика 3.

Блок 2 памяти, показанный на фиг.2, содержит инвертор 2.1, первый 2.2 и второй 2.3 суммирующие счетчики, коммутатор 2.4, элемент И 2.5, дифференцирующую цепь 2.6 и ОЗУ 2.7. Второй вход первого суммирующего счетчика 2.2 является первым входом блока 2 памяти, первый - восьмой входы коммутатора 2.4 являются соответственно вторым - девятым входами блока 2 памяти, а десятый вход блока 2 памяти соединен с девятым входом коммутатора 2.4, первым входом ОЗУ 2.7 и входами инвертора 2.1 и дифференцирующей цепи 2.6. Выход инвертора 2.1 является десятым входом коммутатора 2.4. Первый, второй, третий и четвертый выходы первого суммирующего счетчика 2.2 соединены соответственно с первым входом элемента И 2.5 и вторым входом ОЗУ 2.7, с вторым входом элемента И 2.5 и третьим входом ОЗУ 2.7, с третьим входом элемента И 2.5 и четвертым входом ОЗУ 2.7, с четвертым входом элемента И 2.5 и пятым входом ОЗУ 2.7. Первый - седьмой выходы второго суммирующего счетчика 2.3 являются соответственно шестым - двенадцатым входами ОЗУ 2.7. Первый - восьмой вход/выход коммутатора 2.4 соединены соответственно с тринадцатым - двадцатым входом/выходом ОЗУ 2.7. Девятый - шестнадцатый выходы коммутатора 2.4 являются соответственно первым - восьмым выходом блока 2 памяти. Выход элемента И 2.5 является первым входом второго суммирующего счетчика 2.3, а выход дифференцирующей цепи 2.6 соединен с первым входом первого суммирующего счетчика 2.2 и вторым входом второго суммирующего счетчика 2.3.

Коммутатор 4. показанный на фиг. 3, содержит первый 4.1, второй 4.2, третий 4.3 и четвертый 4.4 триггеры, первый 4.5, второй 4.6, третий 4.7 и четвертый 4.8 буферные элементы. Первый вход коммутатора 4 соединен с первым входом второго триггера 4.2 и вторыми входами первого 4.1, третьего 4.3 и четвертого 4.4 триггеров. Второй вход коммутатора 4 соединен с первым входом третьего триггера 4.3 и вторыми входами первого 4.1, второго 4.2 и четвертого 4.4 триггеров. Третий вход коммутатора 4 соединен с первым входом четвертого триггера 4.4 и вторыми входами первого 4.1, второго 4.2 и третьего 4.3 триггеров. Четвертый - одиннадцатый входы коммутатора 4 являются соответственно вторыми - девятыми входами первого 4.5, второго 4.6, третьего 4.7 и четвертого 4.8 буферных элементов. Двенадцатый вход коммутатора 4 соединен параллельно с первым входом первого триггера 4.1 и вторыми входами второго 4.2, третьего 4.3 и четвертого 4.4 триггеров. Выходы первого 4.1, второго 4.2, третьего 4.3 и четвертого 4.4 триггеров являются первыми входами соответственно первого 4.5, второго 4.6, третьего 4.7 и четвертого 4.8 буферных элементов. Первый - восьмой выходы первого буферного элемента 4.5 являются соответственно первым - восьмым выходами коммутатора 4, первый - восьмой выходы второго буферного элемента 4.6 являются соответственно девятым - шестнадцатым выходами коммутатора 4, первый - восьмой выходы третьего буферного элемента 4.7 являются соответственно семнадцатым - двадцать четвертым выходами коммутатора 4, а первый - восьмой выходы четвертого буферного элемента 4.8 являются соответственно двадцать пятым - тридцать вторым выходами коммутатора 4.

Первый блок 5 селекции, показанный на фиг.4, содержит первую линию 5.1 задержки, первый 5.2, второй 5.3 и третий 5.4 коммутаторы, первый 5.5, второй 5.6, третий 5.7 и четвертый 5.8 дешифраторы, вторую 5.9 и третью 5.10 линии задержки, элемент И 5.11. При этом первый вход первого блока 5 селекции соединен с первыми входами первого 5.5, третьего 5.7 дешифраторов и девятыми входами второго 5.6 и четвертого 5.8 дешифраторов. Второй - девятый входы первого блока 5 селекции являются соответственно вторым - девятым входами первого коммутатора 5.2. Десятый вход первого блока 5 селекции соединен с десятыми входами первого 5.2 и второго 5.3 коммутаторов. Одиннадцатый вход первого блока 5 селекции является десятым входом третьего коммутатора 5.4. Двенадцатый вход первого блока 5 селекции является вторым входом элемента И 5.11. Выход первой линии 5.1 задержки является первым входом первого коммутатора 5.2. Первый - восьмой и девятый - шестнадцатый выходы первого коммутатора 5.2 являются соответственно вторым - девятым входами соответственно второго 5.3 и третьего 5.4 коммутаторов. Первый - восьмой и девятый - шестнадцатый выходы второго коммутатора 5.3 являются соответственно вторым - девятым входами первого дешифратора 5.5 и первым - восьмым входами второго дешифратора 5.6. Первый - восьмой и девятый - шестнадцатый выходы третьего коммутатора 5.4 являются соответственно вторым - девятым входами третьего дешифратора 5.7 и первым - восьмым входами четвертого дешифратора 5.8. Первый выход первого дешифратора 5.5 является входом второй линии 5.9 задержки, выход которой является первым входом второго коммутатора 5.3. Первый и второй выходы второго дешифратора 5.6 являются соответственно первым и вторым выходами первого блока 5 селекции, а их соединение является входом первой линии 5.1 задержки. Первый выход третьего дешифратора 5.7 является входом третьей линии 5.10 задержки. Первый, второй и третий выходы четвертого дешифратора 5.8 являются соответственно третьим выходом первого блока 5 селекции, первым входом элемента И 5.11 и пятым выходом первого блока 5 селекции. Соединение вторых выходов первого 5.5 и третьего 5.7 дешифраторов, третьего выхода второго дешифратора 5.6 и четвертого выхода четвертого дешифратора 5.8 является шестым выходом первого блока 5 селекции. Выход третьей линии 5.10 задержки является первым входом третьего коммутатора 5.4, а выход элемента И 5.11 является четвертым выходом первого блока 5 селекции.

Второй блок 6 селекции, показанный на фиг.5, содержит первый 6.1, второй 6.2, третий 6.3 и четвертый 6.7 дешифраторы, первый 6.4 и второй 6.6 коммутаторы, линию 6.5 задержки, суммирующий счетчик 6.8 и элемент И 6.9. Первый вход второго блока 6 селекции является первыми входами первого 6.1, второго 6.2, третьего 6.3 и четвертого 6.7 дешифраторов. Второй, третий и четвертый входы второго блока 6 селекции соединены соответственно с вторыми, третьими и четвертыми входами первого 6.1 и второго 6.2 дешифраторов. Пятый - девятый входы второго блока 6 селекции являются соответственно пятым - девятым и вторым - шестым входами соответственно второго 6.2 и третьего 6.3 дешифраторов. Десятый вход второго блока 6 селекции является вторым входом суммирующего счетчика 6.8, а его одиннадцатый вход является вторым входом элемента И 6.9. Выход первого дешифратора 6.1 соединен с первым и вторым входами первого коммутатора 6.4 и вторым входом второго коммутатора 6.6. Выход второго дешифратора 6.2 соединен с третьим входом первого коммутатора 6.4, входом линии 6.5 задержки и первыми входами суммирующего счетчика 6.8 и второго коммутатора 6.6. Выход третьего дешифратора 6.3 является третьим входом второго коммутатора 6.6. Выход линии 6.5 задержки является четвертым входом первого коммутатора 6.4. Выход второго коммутатора 6.6 соединен с третьим входом первого коммутатора 6.4. Первый и второй выходы первого коммутатора 6.4 являются соответственно вторым и третьим входами четвертого дешифратора 6.7. Соединение выхода четвертого дешифратора 6.7, третьего выхода первого коммутатора 6.4, первого выхода суммирующего счетчика 6.8 является первым выходом второго блока 6 селекции. Второй выход суммирующего счетчика 6.8 является первым входом элемента И 6.9, выход которого является вторым выходом второго блока 6 селекции.

Третий блок 7 селекции, показанный на фиг.6, содержит первый 7.1, второй 7.2, третий 7.3 и четвертый 7.7 дешифраторы, первый 7.4 и второй 7.6 коммутаторы, линию 7.5 задержки, суммирующий счетчик 7.8 и элемент И 7.9. Первый вход третьего блока 7 селекции является первыми входами первого 7.1, второго 7.2. третьего 7.3 и четвертого 7.7 дешифраторов. Второй, третий и четвертый входы третьего блока 7 селекции соединены соответственно с вторыми, третьими и четвертыми входами первого 7.1 и второго 7.2 дешифраторов. Пятый - девятый входы третьего блока 7 селекции являются соответственно пятым - девятым и вторым - шестым входами - соответственно второго 7.2 и третьего 7.3 дешифраторов. Десятый вход третьего блока 7 селекции является вторым входом суммирующего счетчика 7.8, а его одиннадцатый вход является вторым входом элемента И 7.9. Выход первого дешифратора 7.1 соединен с первым и вторым входами первого коммутатора 7.4 и вторым входом второго коммутатора 7.6. Выход второго дешифратора 7.2 соединен с третьим входом первого коммутатора 7.4, входом линии 7.5 задержки и первыми входами суммирующего счетчика 7.8 и второго коммутатора 7.6. Выход третьего дешифратора 7.3 является третьим входом второго коммутатора 7.6. Выход линии 7.5 задержки является четвертым входом первого коммутатора 7.4. Выход второго коммутатора 7.6 соединен с третьим входом первого коммутатора 7.4. Первый и второй выходы первого коммутатора 7.4 являются соответственно вторым и третьим входами четвертого дешифратора 7.7. Соединение выхода четвертого дешифратора 7.7, третьего выхода первого коммутатора 7.4, первого выхода суммирующего счетчика 7.8 является первым выходом третьего блока 7 селекции. Второй выход суммирующего счетчика 7.8 является первым входом элемента И 7.9, выход которого является вторым выходом третьего блока 7 селекции.

Четвертый блок 8 селекции, показанный на фиг.7, содержит первый коммутатор 8.1, линию 8.2 задержки, второй коммутатор 8.3, первый 8.4, второй 8.5 и третий 8.6 дешифраторы, суммирующий счетчик 8.7 и элемент И 8.8. Первый вход четвертого блока 8 селекции является первыми входами первого 8.4, второго 8.5 и третьего 8.6 дешифраторов и вторыми входами суммирующего счетчика 8.7 и элемента И 8.8. Второй - девятый входы четвертого блока 8 селекции являются соответственно первым - восьмым входами первого коммутатора 8.1. Десятый вход четвертого блока 8 селекции является девятым входом первого коммутатора 8.1, первыми входами второго коммутатора 8.3 и суммирующего счетчика 8.7. Одиннадцатый вход четвертого блока 8 селекции является десятым входом первого коммутатора 8.1 и третьим входом элемента И 8.8. Первый - восьмой и девятый - шестнадцатый выходы первого коммутатора 8.1 являются соответственно третьим - десятым входами второго коммутатора 8.3 и вторым - девятым входами третьего дешифратора 8.6. Выход линии 8.2 задержки является вторым входом второго коммутатора 8.3. Первый - восьмой и девятый - одиннадцатый выходы второго коммутатора 8.3 являются соответственно вторым - девятым входами первого дешифратора 8.4 и вторым - четвертым входами второго дешифратора 8.5. Выход первого дешифратора 8.4 является третьим входом суммирующего счетчика 8.7. Выход суммирующего счетчика 8.7 является входом линии 8.2 задержки. Соединение второго выхода первого дешифратора 8.4, выходов второго дешифратора 8.5 и элемента И 8.8 является первым выходом четвертого блока 8 селекции. Выход третьего дешифратора 8.6 соединен с первым входом элемента И 8.8 и является вторым выходом четвертого блока 8 селекции.

Регистр 9 стратегии поиска, показанный на фиг.8, содержит триггер 9.1, первый 9.2, второй 9.3, третий 9.4 и четвертый 9.5 элементы И и линию 9.6 задержки. При этом первый вход регистра 9 стратегии поиска соединен с вторыми входами первого 9.2 и второго 9.3 элементов И и первыми входами третьего 9.4 и четвертого 9.5 элементов И. Второй вход регистра 9 стратегии поиска является вторым входом триггера 9.1, а третий вход регистра 9 стратегии поиска является третьим входом триггера 9.1. Четвертый вход регистра 9 стратегии поиска соединен параллельно с третьим входом четвертого 9.5 элемента И и вторым входом третьего элемента И 9.4. Пятый вход регистра 9 стратегии поиска соединен с третьими входами первого 9.2 и второго 9.3 элементов И. Выход триггера 9.1 соединен с первыми входами первого 9.2, второго 9.3 элементов И, вторым входом четвертого элемента И 9.5 и третьим входом третьего элемента И 9.4. Соединение выходов второго 9.3 и третьего 9.4 элементов И является входом линии 9.6 задержки, выход которой соединен с первым входом триггера 9.1. Соединение выходов первого 9.2 и четвертого 9.5 элементов И является выходом регистра 9 стратегии поиска.

Заявленное устройство работает следующим образом.

Устройство поиска информации предназначено для выявления в цифровом потоке, передаваемом в канале связи, сообщений, соответствующих протоколу типа TFTP, отличающегося от других подобных протоколов передачи файлов конкретным набором служебных и информационных сообщений (пакетов) и правилами обмена ими корреспондирующими станциями в ходе сеанса межмашинного обмена.

В целом ряде задач технического характера в области электросвязи возникает проблема поиска информации определенного типа в общем информационном потоке, которая может решаться статистическим (аналог), логическим (прототип) способами или методами теории распознавания образов (предлагаемое устройство, реализующее принципы теории синтаксического анализа), описанными в книге Дж. Ту, Р. Гонсалес. Принципы распознавания образов. Пер. с англ. -М.: Мир, 1978, с. 411.

В отличие от известных устройств, обеспечивающих правильное распознавание информации с некоторой вероятностью, в зависимости от различных условий, предлагаемое устройство вырабатывает однозначное решение о наличии (отсутствии) сообщений определенного типа в общем информационном потоке.

Собственно алгоритм функционирования протокола TFTP состоит в следующем (фиг. 10): взаимодействие между ЭВМ по чтению/записи файлов осуществляется пакетами стандартной длины в стартстопном режиме. Пакеты TFTP переносятся в отдельных межсетевых дейтаграммах (или пакетах сетевого протокола).

Любая передача начинается с передачи пакета "Запрос на чтение" (на фиг. 10, 11 обозначен 01) или "Запрос на запись" (02), передаваемого от пользователя в удаленную ЭВМ, что соответствует запросу на установление соединения. Если ЭВМ принимает запрос, соединение устанавливается и далее файл передается блоками фиксированной длины в 512 байт. Каждый пакет данных ("Данные" - 03) последовательно нумеруется, начиная с 1, содержит один блок и до передачи следующего пакета должен быть подтвержден пакетом "Квитанция" (04), который также имеет номер. Подтверждение пакета "Запрос на запись" имеет номер 0, подтверждением на пакет "Запрос на чтение" является первый блок данных. Пакет длиной менее 512 байт является признаком завершения передачи. Закрытие соединения осуществляется по тайм-ауту после приема последнего пакета на приемной стороне и приема подтверждения последнего пакета на передающей стороне.

Ошибка отмечается посылкой пакета "Ошибка" (05) и приводит к разрыву соединения.

Форматы используемых в TFTP пакетов приведены на фиг.8.

Поиск (распознавание) информации осуществляется с использованием признаков двух групп:

качественных признаков, присущих как TFTP, так и ряду других типов коммуникационных протоколов, которыми являются используемые пакеты;

структурных признаков, присущих только TFTP, которыми является исчерпывающее конечное множество разрешенных последовательностей пакетов.

Предлагаемое устройство, реализующее способ поиска информации по указанным признакам, заключается в анализе сеансов связи в СПД и сравнении их структуры с априорно известными правилами организации передачи данных при использовании протокола TFTP. При их совпадении принимается решение о том, что сеанс связи проводится с использованием искомого типа протокола.

Реализуемый в предлагаемом устройстве способ синтаксического распознавания протокола TFTP (фиг.11) основан на операции идентификации, передаваемой по каналу пакетов (01, 02, 03, 04, 05) и правилам обмена ими в ходе сеанса связи.

Спецификация протокола описывается следующей регулярной грамматикой:

G = (Vn, Vt, P, S),

где

Vn = (01*, 02*, 03*,03#, 04*, 04#, 05*, 05#, ANY*, ANY#, T) - множество пакетов, предусмотренных протоколом (символом * обозначены пакеты пользователя, символом # - пакеты удаленной ЭВМ, Т - тайм-аут);

Vt = (S, A, B, C, D, E, F) - множество возможных состояний логического соединения между прикладными процессами передачи файла;

P = (S--->01* A, S--->02* C, S--->ANY* F, A--->03# B, A--->05# E, A--->ANY# F, A--->T E, B--->04* A, D--->05* E, B--->ANY* F, C--->04# D, C--->05# E, C--->ANY# F, D--->03* C, D--->05* E, D--->T E, D--->ANY* F) - множество правил обмена пакетами в ходе сеанса связи.

S - исходное состояние логического соединения между прикладными процессами передачи файла.

Входными сигналами для устройства поиска информации (фиг.1) являются сигнальная цифровая последовательность Fs, сигнал тактовой частоты Ft и данные N о длительности анализируемых пакетов, поступающие с демодулирующего устройства (канального контроллера).

Делитель 1 частоты служит для деления тактовой частоты Ft на 8 с целью обеспечения побайтного анализа сигнальной цифровой последовательности Fs.

Блок 2 памяти предназначен для обеспечения побайтной записи/чтения одного пакета сигнальной цифровой последовательности

Вычитающий счетчик 3 предназначен для определения количества байтов пакета, включая байт, который анализируется в текущий момент времени, находящихся в блоке 2 памяти, управления функционированием блока 2 памяти, первого 5, второго 6, третьего 7 и четвертого 8 блоков селекции, регистра 9 стратегии поиска и формирования управляющего сигнала (логическая "1") Fr разрешения трансляции сигнальной цифровой последовательности Fs, поступающего на демодулирующее устройство (канальный контроллер).

Информация N о количестве байт, содержащихся в пакете, поступившем в блок 2 памяти, записывается в вычитающий счетчик 3 в параллельном виде по его второму - тринадцатому входам в момент поступления последнего байта пакета в блок 2 памяти. Уменьшение показания счетчика на единицу происходит при каждом поступлении на его первый вход управляющего сигнала с выхода делителя 1 частоты. Обнуление показания счетчика происходит при поступлении управляющего сигнала на четырнадцатый вход вычитающего счетчика. При значении вычитающего счетчика 3, равном 0, на его первом выходе формируется управляющий сигнал, при значении вычитающего счетчика 3, равном 1, на его втором выходе формируется управляющий сигнал, а при значении вычитающего счетчика 3, равном 3, управляющий сигнал формируется на его третьем выходе.

Коммутатор 4 предназначен для побайтной коммутации сигнальной цифровой последовательности Fs, поступающей с блока 2 памяти, к входам первого 5, второго 6, третьего 7 и четвертого 8 блоков селекции. При поступлении управляющего сигнала на первый вход коммутатора 4 происходит коммутация четвертого - одиннадцатого входов коммутатора 4 соответственно к его девятому - шестнадцатому выходам, при поступлении управляющего сигнала на второй вход коммутатора 4 происходит коммутация четвертого - одиннадцатого входов коммутатора 4 соответственно к его семнадцатому - двадцать четвертому выходам, при поступлении управляющего сигнала на третий вход коммутатора 4 происходит коммутация четвертого - одиннадцатого входов коммутатора 4 соответственно к его двадцать пятому - тридцать второму выходам, а при поступлении управляющего сигнала на двенадцатый вход коммутатора 4 происходит коммутация четвертого - одиннадцатого входов коммутатора 4 соответственно к его первому - восьмому выходам.

Первый блок 5 селекции предназначен для предварительного определения типа пакетов по содержанию его первых двух байтов (фиг.8).

Второй блок 6 селекции предназначен для идентификации пакета "Запрос на чтение" по априорно известной его структуре.

Третий блок 7 селекции предназначен для идентификации пакета "Запрос на запись" по априорно известной его структуре.

Четвертый блок 8 селекции предназначен для идентификации пакета "Ошибка" по априорно известной его структуре.

Регистр 9 стратегии поиска предназначен для проверки соответствия порядка поступления пакетов сигнальной цифровой последовательности Fs правилам организации обмена данными протокола TFTP.

Формирователь 10 временных интервалов предназначен для генерации сигнала, свидетельствующего о завершении сеанса связи, по тайм-ауту после приема последнего пакета "Квитанция". Он представляет собой таймер, формирующий на своем выходе управляющий сигнал по истечению промежутка времени, устанавливаемого в соответствии с принятыми в данном канале связи правилами обмена данными. Обнуление формирователя 10 временных интервалов происходит при поступлении на его вход управляющего сигнала.

Блок 11 индикации предназначен для формирования информационного сигнала об использовании (или не использовании) в данном сеансе связи протокола TFTP. При поступлении управляющего сигнала на первый вход блока 11 индикации он формирует сигнал, свидетельствующий об использовании в данном сеансе связи коммуникационного протокола, отличного от TFTP, а при поступлении информационного сигнала на второй вход блока 11 индикации он формирует сигнал, свидетельствующий о том, что в данном сеансе связи используется коммуникационный протокол TFTP.

Блок 2 памяти (фиг.2) работает следующим образом:

Инвертор 2.1 служит для формирования управляющего сигнала, поступающего на десятый вход коммутатора 2.4.

Первый 2.2 и второй 2.3 суммирующие счетчики предназначены для обеспечения адресации ячеек ОЗУ 2.7 при записи или считывании информации, при этом первый суммирующий счетчик 2.2 производит адресацию шестнадцати столбцов, а второй суммирующий счетчик 2.3 - ста двадцати восьми строчек матрицы ОЗУ 2.7. Обнуление первого 2.2 и второго 2.3 счетчиков происходит при поступлении управляющего сигнала соответственно на первый и второй входы. Второй вход первого 2.2 и первый вход второго 2.3 суммирующих счетчиков являются сигнальными.

Коммутатор 2.4 обеспечивает запись байтов сигнальной цифровой последовательности Fs в ОЗУ 2.7 и их последующего считывания. При поступлении управляющего сигнала ("1") на девятый вход коммутатора 2.4 его первый - восьмой входы подключаются соответственно к его первому - восьмому входам/выходам, а при поступлении управляющего сигнала на десятый вход коммутатора 2.4 его первый - восьмой входы/выходы подключаются соответственно к его девятому - шестнадцатому выходам.

Элемент И 2.5 обеспечивает поступление управляющего импульса на первый вход второго суммирующего счетчика 2.3 после отсчета каждых шестнадцати импульсов, поступивших на второй вход первого суммирующего счетчика 2.2.

Дифференцирующая цепь 2.6 обеспечивает преобразование двухпозиционного управляющего сигнала ("0" и "1") в последовательность двухполярных импульсов с дальнейшим преобразованием двухполярной последовательности в последовательность однополярных импульсов.

ОЗУ 2.7 предназначено для хранения байтов одного пакета. При наличии на первом входе ОЗУ 2.7 логической "1" ОЗУ 2.7 находится в режиме записи, а при наличии логического "0" - в режиме считывания. Адресация ячеек ОЗУ 2.7 при записи/считывании обеспечивается комбинацией управляющих сигналов на его втором - двенадцатом входах.

Коммутатор 4 (фиг.3) работает следующим образом.

Первый 4.1, второй 4.2, третий 4.3 или четвертый 4.4 триггеры при поступлении на их первые входы управляющего сигнала формируют сигнал разрешения трансляции, поступающий соответственно на первый 4.5, второй 4.6, третий 4.7 или четвертый 4.8 буферные элементы.

При поступлении управляющего сигнала на вторые входы первого 4.1, второго 4.2, третьего 4.3 или четвертого 4.4 триггеров происходит обнуление соответствующего триггера. Следует отметить, что при наличии управляющего сигнала на первом входе какого-либо из триггеров на вторых входах других трех триггеров будет также присутствовать управляющий сигнал, таким образом в любой момент времени сигнал разрешения трансляции будет присутствовать на выходе только одного из триггеров.

При поступлении сигнала разрешения трансляции на первый вход первого 4.5, второго 4.6, третьего 4.7 или четвертого 4.8 буферных элементов информационный сигнал, поступивший на их второй - девятый входы будет транслироваться соответственно по первому - восьмому выходам соответственно первого 4.5. второго 4.6, третьего 4.7 или четвертого 4.8 буферных элементов.

Первый блок 5 селекции (фиг.4) работает следующим образом.

Первая линия 5.1 задержки обеспечивает задержку поступающего на ее вход управляющего сигнала на время Tz= 4/Ft для недопущения возникновения переходных процессов при переключениях первого коммутатора 5.2.

Первый коммутатор 5.2 обеспечивает подключение поступающего на его второй - девятый входы сигнала на входы второго 5.3 и третьего 5.4 коммутаторов. При поступлении на первый вход первого коммутатора 5.2 управляющего сигнала происходит коммутация второго - девятого входов первого коммутатора 5.2 с его девятым - шестнадцатым выходами, а при поступлении управляющего сигнала на десятый вход первого коммутатора 5.2 второй - девятый входы первого коммутатора 5.2 соединяются с его первым - восьмым выходами.

Второй коммутатор 5.3 обеспечивает подключение входного сигнала, поступающего на его второй - девятый входы, на входы первого 5.5 и второго 5.6 дешифраторов. При поступлении на первый вход второго коммутатора 5.3 управляющего сигнала происходит коммутация второго - девятого входов второго коммутатора 5.3 с его девятым - шестнадцатым выходами, а при поступлении управляющего сигнала на десятый вход второго коммутатора 5.3 второй - девятый входы второго коммутатора 5.3 соединяются с его первым - восьмым выходами.

Третий коммутатор 5.4 обеспечивает подключение входного сигнала, поступающего на его второй - девятый входы, на входы третьего 5.7 и четвертого 5.8 дешифраторов. При поступлении на первый вход третьего коммутатора 5.4 управляющего сигнала происходит коммутация второго - девятого входов третьего коммутатора 5.4 с его девятым - шестнадцатым выходами, а при поступлении управляющего сигнала на десятый вход третьего коммутатора 5.4 второй - девятый входы третьего коммутатора 5.4 соединяются с его первым - восьмым выходами.

Первый дешифратор 5.5 обеспечивает проверку на соответствие нулевому значению поступившей на его второй - девятый входы кодовой комбинации. При поступлении нулевой комбинации на эти входы на первом выходе первого дешифратора 5.5 формируется управляющий сигнал, а при наличии во входной кодовой комбинации хотя бы одной единицы управляющий сигнал формируется на втором выходе первого дешифратора 5.5.

Второй дешифратор 5.6 обеспечивает проверку входной кодовой комбинации, поступившей на его первый - восьмой входы. При поступлении кодовой комбинации, соответствующей единице, на первом выходе второго дешифратора 5.6 формируется управляющий сигнал, при поступлении кодовой комбинации, соответствующей двойке, на втором выходе второго дешифратора 5.6 формируется управляющий сигнал, а при поступлении любой другой кодовой комбинации управляющий сигнал формируется на третьем выходе второго дешифратора 5.6.

Третий дешифратор 5.7 обеспечивает проверку на соответствие нулевому значению поступившей на его второй - девятый входы кодовой комбинации. При поступлении нулевой комбинации на входы на первом выходе третьего дешифратора 5.7 формируется управляющий сигнал, а при наличии во входной кодовой комбинации хотя бы одной единицы управляющий сигнал формируется на втором выходе третьего дешифратора 5.7.

Четвертый дешифратор 5.8 обеспечивает проверку входной кодовой комбинации, поступившей на его первый - восьмой входы. При поступлении кодовой комбинации, соответствующей трем, на первом выходе четвертого дешифратора 5.8 формируется управляющий сигнал, при поступлении кодовой комбинации, соответствующей четырем, на втором выходе четвертого дешифратора 5.8 формируется управляющий сигнал, при поступлении кодовой комбинации, соответствующей пяти, на третьем выходе четвертого дешифратора 5.8 формируется управляющий сигнал, а при поступлении любой другой кодовой комбинации управляющий сигнал формируется на четвертом выходе четвертого дешифратора 5.8.

Тактирование работы первого 5.5, третьего 5.7 дешифраторов осуществляется сигналом, поступающим на их первые входы, а тактирование работы второго 5.6 и четвертого 5.8 дешифраторов осуществляется сигналом, поступающим на их девятые входы.

Вторая 5.9 и третья 5.10 линии задержки обеспечивают задержку поступающего на их вход управляющего сигнала на время задержки Tz = 4/Ft для недопущения возникновения переходных процессов при переключениях соответственно второго 5.3 и третьего 5.4 коммутаторов.

Элемент И 5.11 обеспечивает проверку структуры пакета "Квитанция" на количество байт.

Второй блок 6 селекции (фиг.5) работает следующим образом.

Первый дешифратор 6.1 обеспечивает проверку входной кодовой комбинации, поступающей на его второй - четвертый входы, на наличие хотя бы одной единицы на этих входах, что свидетельствует о передаче информационных символов в коде ASCII (Абель П. Язык Ассемблера для IBM PC и программирования./ Пер. с англ. Ю.В.Салтыкова. -М.: Высшая школа. 1992, т.47 с. 447), в этом случае на выходе первого дешифратора 6.1 формируется управляющий сигнал.

Второй дешифратор 6.2 обеспечивает проверку входной кодовой комбинации, поступающей на его второй - девятый входы, при отсутствии единиц на этих входах, что свидетельствует о передаче нулевого байта, на выходе второго дешифратора 6.2 формируется управляющий сигнал.

Третий дешифратор 6.3 при наличии хотя-бы одной единицы на его втором - шестом входах формирует на своем выходе управляющий сигнал.

Первый коммутатор 6.4 при поступлении на его первый вход управляющего сигнала производит коммутацию второго и третьего входов первого коммутатора 6.4 соответственно к его первому и второму выходам, при поступлении управляющего сигнала на четвертый вход первого коммутатора 6.4 происходит коммутация его третьего входа и третьего выхода. Наличие на третьем выходе первого коммутатора 6.4 логической "1" свидетельствует о том, что после прихода нулевого байта на вход второго блока 6 селекции поступил второй подряд нулевой байт либо байт, который не является ни нулевым, ни информационным, что не допускается правилами организации обмена данными.

Линия 6.5 задержки обеспечивает задержку поступающего на ее вход управляющего сигнала на время задержки Tz= 4/Ft для недопущения возникновения переходных процессов при переключениях первого коммутатора 6.4.

Второй коммутатор 6.6 при поступлении на его первый вход управляющего сигнала подключает выход третьего дешифратора 6.3 к третьему входу первого коммутатора 6.4, а при поступлении управляющего сигнала на второй вход второго коммутатора 6.6 данное соединение разрывается.

Четвертый дешифратор 6.7, суммирующий счетчик 6.8 и элемент И 6.9 обеспечивают проверку структуры пакета "Запрос на чтение" на количество нулевых байтов и разрешенный правилами организации обмена данными порядок взаимного следовании нулевых и информационных байтов.

Четвертый дешифратор 6.7 при, поступлении на его второй и третий входы логических "0" (это означает, что первая поступившая на второй - девятый входы второго блока 6 селекции кодовая комбинация не является ни нулевой, ни информационной) на своем выходе формирует управляющий сигнал.

Тактирование работы первого 6.1, второго 6.2, третьего 6.3 и четвертого 6.7 дешифраторов осуществляется по сигналам, поступающим на их первые входы.

Суммирующий счетчик 6.8 обеспечивает контроль за количеством нулевых байтов в одном пакете. При поступлении на первый вход суммирующего счетчика 6.8 двух импульсов на его втором выходе формируется управляющий сигнал, а при поступлении на первый вход суммирующего счетчика 6.8 трех импульсов управляющий сигнал формируется на его первом выходе. Обнуление суммирующего счетчика 6.8 происходит при поступлении на его второй вход управляющего сигнала.

Элемент И 6.9 формирует положительное решение о соответствии структуры исследуемого пакета структуре пакета "Запрос на чтение" только при совпадении времени прихода управляющих сигналов, свидетельствующих о наличии двух нулевых байтов в пакете и о том, что обрабатывается последний байт пакета.

Третий блок 7 селекции (фиг.6) работает следующим образом.

Первый дешифратор 7.1 обеспечивает проверку входной кодовой комбинации, поступающей на его второй - четвертый входы, на наличие хотя бы одной единицы на этих входах, что свидетельствует о передаче информационных символов в коде ASCII, в этом случае на выходе первого дешифратора 7.1 формируется управляющий сигнал.

Второй дешифратор 7.2 обеспечивает проверку входной кодовой комбинации, поступающей на его второй - девятый входы, при отсутствии единиц на этих входах, что свидетельствует о передаче нулевого байта, на выходе второго дешифратора 7.2 формируется управляющий сигнал.

Третий дешифратор 7.3 при наличии хотя бы одной единицы на его втором - шестом входах формирует на своем выходе управляющий сигнал.

Первый коммутатор 7.4 при поступлении на его первый вход управляющего сигнала происходит коммутация второго и третьего входов первого коммутатора 7.4 соответственно к его первому и второму выходам, при поступлении управляющего сигнала на четвертый вход первого коммутатора 7.4 происходит коммутация его третьего входа и третьего выхода. Наличие на третьем выходе первого коммутатора 7.4 логической "1" свидетельствует о том, что после прихода нулевого байта на вход третьего блока 7 селекции поступил второй подряд нулевой байт либо байт, который не является ни нулевым, ни информационным, что не допускается правилами организации обмена данными.

Линия 7.5 задержки обеспечивает задержку поступающего на ее вход управляющего сигнала на время задержки Tz = 4/Ft для недопущения возникновения переходных процессов при переключениях первого коммутатора 7.4.

Второй коммутатор 7.6 при поступлении на его первый вход управляющего сигнала подключает выход третьего дешифратора 7.3 к третьему входу первого коммутатора 7.4, а при поступлении управляющего сигнала на второй вход второго коммутатора 7.6 данное соединение разрывается.

Четвертый дешифратор 7.7, суммирующий счетчик 7.8 и элемент И 7.9 обеспечивают проверку структуры пакета "Запрос на запись" на количество нулевых байтов и разрешенный правилами организации обмена данными порядок взаимного следовании нулевых и информационных байтов.

Четвертый дешифратор 7.7 при поступлении на его второй и третий входы логических "0" (что означает, что первая поступившая на второй - девятый входы третьего блока 7 селекции кодовая комбинация не является ни нулевой, ни информационной) на своем выходе формирует управляющий сигнал.

Тактирование работы первого 7.1, второго 7.2, третьего 7.3 и четвертого 7.7 дешифраторов осуществляется по сигналам, поступающим на их первые входы.

Суммирующий счетчик 7.8 обеспечивает контроль за количеством нулевых байтов в одном пакете. При поступлении на первый вход суммирующего счетчика 7.8 двух импульсов на его втором выходе формируется управляющий сигнал, а при поступлении на первый вход суммирующего счетчика 7.8 трех импульсов управляющий сигнал формируется на его первом выходе. Обнуление суммирующего счетчика 7.8 происходит при поступлении на его второй вход управляющего сигнала.

Элемент И 7.9 формирует положительное решение о соответствии структуры исследуемого пакета структуре пакета "Запрос на запись" только при совпадении времени прихода управляющих сигналов, свидетельствующих о наличии двух нулевых байтов в пакете и о том, что обрабатывается последний байт пакета.

Четвертый блок 8 селекции (фиг.7) работает следующим образом.

Первый коммутатор 8.1 предназначен для коммутации входного потока, поступающего на его первый - восьмой входы, на входы второго коммутатора 8.3 и третьего дешифратора 8.6. При поступлении на девятый вход первого коммутатора 8.1 управляющего сигнала происходит подключение первого - восьмого входов первого коммутатора 8.1 соответственно к его первому - восьмому выходам, а при поступлении управляющего сигнала на десятый вход первого коммутатора 8.1 происходит подключение первого - восьмого входов первого коммутатора 8.1 соответственно к его девятому - шестнадцатому выходам.

Линия 8.2 задержки обеспечивает задержку поступающего на ее вход управляющего сигнала на время задержки Tz = 4/Ft для недопущения возникновения переходных процессов при переключениях второго коммутатора 8.3.

Второй коммутатор 8.3 предназначен для коммутации входного потока, поступающего на его третий - десятый входы, на входы первого 8.4 и второго 8.5 дешифраторов. При поступлении на первый вход второго коммутатора 8.3 управляющего сигнала происходит подключение третьего - десятого входов второго коммутатора 8.3 соответственно к его первому - восьмому выходам, а при поступлении управляющего сигнала на второй вход второго коммутатора 8.3 происходит подключение третьего - пятого входов второго коммутатора 8.3 соответственно к его девятому - одиннадцатому выходам.

Первый дешифратор 8.4 проверяет наличие кода ошибки и при поступлении на его второй - девятый входы хотя бы одной единицы формирует управляющий сигнал на своем первом выходе, а при наличии на входах только логических "0" - формирует управляющий сигнал на своем втором выходе.

Второй дешифратор 8.5 проверяет наличие байтов сообщения об ошибках и если на второй - четвертый входы второго дешифратора 8.5 поступили только логические "0", - формирует на своем выходе управляющий сигнал.

Третий дешифратор 8.6 при поступлении на его второй - девятый входы логических "0" формирует на своем выходе управляющий сигнал.

Суммирующий счетчик 8.7 предназначен для управления работой второго коммутатора 8.3. При поступлении на его третий вход двух логических "1" на его выходе формируется управляющий сигнал. Обнуление показания суммирующего счетчика 8.7 происходит при поступлении на его первый вход управляющего сигнала.

Элемент И 8.8, имеющий инвертирующий первый вход, предназначен для проверки последнего байта пакета "Ошибка". При одновременном поступлении на его первый вход логического "0", свидетельствующего о том, что последний байт пакета "Ошибка" не является нулевым, а на его третий вход сигнала, указывающего на то, что производится анализ последнего байта пакета, на выходе элемента И 8.8 формируется управляющий сигнал.

Тактирование работы первого 8.4, второго 8.5 и третьего 8.6 дешифраторов осуществляется импульсами, поступающими на их первые входы, а тактирование работы суммирующего счетчика 8.7 и элемента И 8.8 осуществляется импульсами, поступающими на их вторые входы.

Регистр 9 стратегии поиска (фиг.8) работает следующим образом.

Триггер 9.1 принимает состояние логической "1" при поступлении управляющего сигнала на его второй вход и принимает состояние логического "0" при поступлении управляющего сигнала на его третий вход. В дальнейшем триггер 9.1 меняет свое состояние на противоположное при каждом приходе управляющего сигнала на его первый вход.

У первого элемента И 9.2 информационными являются первый и третий входы, а тактирование работы осуществляется по его второму входу.

У второго элемента И 9.3 информационными являются первый инверсный и третий входы, а тактирование работы осуществляется по его второму входу.

У третьего элемента И 9.4 информационными являются второй и третий входы, а тактирование работы осуществляется по его первому входу.

У четвертого элемента И 9.5 информационными являются второй инверсный и третий входы, а тактирование работы осуществляется по его первому входу.

Линия 9.6 задержки обеспечивает задержку поступающего на ее вход управляющего сигнала на время задержки Tz = 4/Ft для недопущения возникновения переходных процессов при переходе триггера 9.1 из одного состояния в другое.

Таким образом, в целом устройство работает следующим образом: делитель 1 частоты обеспечивает побайтный анализ входной цифровой последовательности. При получении с первого выхода реверсивного счетчика 3 разрешения на запись (логическая "1") производится заполнение ячеек ОЗУ 2 байтами пакета, поступившими с демодулирующего устройства (канального контроллера). После того, как записаны все байты очередного пакета анализируемого протокола, в вычитающий счетчик 3 заносится общее количество записанных в ОЗУ 2 байтов, после чего на его первом выходе формируется разрешение на побайтное считывание информации (логический "0"). Через коммутатор 4 два первых байта пакета последовательно поступают в первый блок 5 селекции, где по значению поступивших байтов принимается предварительное решение о типе поступившего пакета, при этом второй 6, третий 7 и четвертый 8 блоки селекции отключены. Если принято решение о том, что данный пакет является "Запросом на чтение", тогда с помощью коммутатора 4 оставшиеся байты пакета, хранящиеся в ОЗУ 2, поступают во второй блок 6 селекции, при этом первый 5, третий 7 и четвертый 8 блоки селекции отключены. Если принято решение о том, что данный пакет является "Запросом на запись", тогда с помощью коммутатора 4 оставшиеся байты пакета, хранящиеся в ОЗУ 2, поступают в третий блок 7 селекции, при этом первый 5, второй 6 и четвертый 8 блоки селекции отключены. Если принято решение о том, что данный пакет является "Ошибкой", тогда с помощью коммутатора 4 оставшиеся байты пакета, хранящиеся в ОЗУ 2, поступают в четвертый блок 8 селекции, при этом первый 5, второй 6 и третий 7 блоки селекции отключены. Если принято решение о том, что данный пакет является "Данными" или "Квитанцией", тогда соответственно на третьем и четвертом выходах первого блока 5 селекции формируется управляющий сигнал.

Во втором 6, третьем 7 и четвертом 8 блоках селекции осуществляется проверка соответствия структуры анализируемого пакета априорно известной структуре соответственно пакетов "Запрос на чтение", "Запрос на запись" и "Ошибка".

Регистр 9 стратегии поиска предназначен для проверки соответствия порядка поступления пакетов сигнальной цифровой последовательности Fs правилам организации обмена данными протокола TFTP.

При принятии решения в первом 5, втором 6, третьем 7 или четвертом 8 блоках селекции о том, что анализируемый пакет не является "разрешенным" либо в случае нарушения допустимого порядка следования пакетов, выявленного регистром 9 стратегии поиска, путем обнуления вычитающего счетчика 3 прекращается анализ данного пакета и блоком 11 индикации об этом формируется сообщение.

Формирователь 10 временных интервалов предназначен для генерации сигнала, свидетельствующего о завершении сеанса связи, по тайм-ауту после приема последнего пакета "Квитанция". Он представляет собой таймер, формирующий на своем выходе управляющий сигнал по истечению промежутка времени, устанавливаемого в соответствии с принятыми в данном канале связи правилами обмена данными. Обнуление формирователя 10 временных интервалов происходит при поступлении на его вход управляющего сигнала.

При поступлении управляющего сигнала с выхода формирователя 10 временных интервалов либо с второго выхода четвертого блока 8 селекции на второй вход блока 11 индикации, он формирует сигнал, свидетельствующий об использовании в данном сеансе связи коммуникационного протокола TFTP.

После принятия как положительного, так и отрицательного решения об использовании в данной сети протокола TFTP, происходит обнуление вычитающего счетчика 3, и устройство поиска информации готово к ведению анализа вновь поступающей входной цифровой последовательности.

С позиций классификации по функциональному назначению следует отметить, что делитель 1 частоты, первый 2.2 и второй 2.3 суммирующие счетчики, суммирующие счетчики 6.8, 7.8 могут быть выполнены по схеме, изображенной на фиг. 1.66 (Шило В. Л. Популярные цифровые микросхемы: Справочник. -М.: Радио и связь, 1987, с. 352 (Массовая радиобиблиотека. Вып. 1111).) и в частности на К155ИЕ5; вычитающий счетчик 3 может быть выполнен по схеме, изображенной на фиг. 1.73 и в частности на К531ИЕ17; суммирующий счетчик 8.7 может быть выполнен по схеме, изображенной на фиг. 1.64 и, в частности, на К155ИЕ2; триггер 9.1 может быть реализован как счетчик на два с возможностью предварительной установки начального состояния и выполнен по схеме, изображенной на фиг. 1.64 и, в частности, на К155ИЕ2; первые дешифраторы 5.5, 6.1, 7.1, 8.4, вторые дешифраторы 5.6, 6.2, 7.2, 8.5, третие дешифраторы 5.7, 6.3, 7.3, 8.6, четвертые дешифраторы 5.8, 6.7, 7.7 могут быть выполнены по схеме, изображенной на фиг. 1.95 и, в частности, на К155ИДЗ; коммутатор 2.4, первые коммутаторы 5.2, 6.4, 7.4, 8.1, вторые коммутаторы 5.3, 6.6, 7.6, 8.3, третий коммутатор 5.4 могут быть выполнены по схеме, изображенной на фиг.3, для соответствующего числа входов и выходов; инвертор 2.1 может быть выполнен на К155ЛН1; элемент И 2.5 может быть выполнен по схеме, изображенной на фиг. 1.19 и, в частности, на К555ЛИ6; элементы И 5.11, 6.9, 7.9 могут быть выполнены по схеме, изображенной на фиг. 1.19 и, в частности, на К555ЛИ2; элемент И 8.8, первый элемент И 9.2, второй элемент И 9.3, третий элемент И 9.4 и четвертый элемент И 9.5 могут быть выполнены по схеме, изображенной на фиг. 1.19 и, в частности, на К555ЛИЗ; первый 4.1, второй 4.2, третий 4.3 и четвертый 4.4 триггеры могут быть выполнены по схеме RS-триггера, изображенной на фиг. 1.42 и, в частности, на К555ТР2; первый 4.5, второй 4.6, третий 4.7 и четвертый 4.8 буферные элементы могут быть выполнены по схеме, изображенной на фиг. 1.13 и, в частности, на К155ЛП10: первая линия 5.1 задержки, вторая линия 5.9 задержки, третья линия 5.10 задержки, линии 6.5, 7.5, 8.2, 9.6 задержки могут быть выполнены как последовательное соединение четного числа инверторов и, в частности, К155ЛН1; формирователь 10 временных интервалов может быть выполнен на К555ГГ, ИЕ, ИД; блок 11 индикации может быть реализован на светодиодах типа КЛ101 (Терещук Р.М. и др. Полупроводниковые приемно-усилительные устройства: Справ, радиолюбителя. -Киев: Наукова думка, 1987, с. 800); ОЗУ 2.7 может быть реализовано на микросхеме К537РУ8 (Лебедев О.Н. Микросхемы памяти и их применение. -М.: Радио и связь, 1990, с. 160) (Массовая радиобиблиотека. Вып. 1152).); дифференцирующая цепь 2.6 может быть выполнена по схеме, показанной на фиг. 11.2 (М.Мэндл. 200 избранных схем электроники. Пер. с англ. -М.:Мир, 1980, с. 344).

Таким образом, преимущества данного устройства состоят в возможности работы в режиме реального времени, нулевой вероятности пропуска (в случае наличия априорной достоверной информации о структуре пакета), простоте реализации и модификации под любые семейства коммуникационных протоколов диалогового типа. Вероятность ложных тревог зависит от устойчивости приема сигнала в канале связи и синхронизации по пакетам на уровне логического сетевого (и возможно транспортного) соединения передачи данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2094845C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2100839C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2130644C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2001 |

|

RU2199148C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

Изобретение относится к электросвязи и может быть использовано для поиска информации и идентификации применяемого в цифровых системах связи коммуникационного протокола TFTP. Целью изобретения является разработка устройства поиска информации, обеспечивающего повышение достоверности поиска, идентификации информации за счет получения однозначного решения. Для реализации этой цели в устройство введены делитель 1 частоты, вычитающий счетчик 3, коммутатор 4, обеспечивающие подключение входного сигнала к различным цепочкам логических элементов. Блок 2 памяти предназначен для хранения одного пакета исследуемого протокола. Первый блок 5 селекции осуществляет предварительную селекцию входного цифрового потока по байтам пакетов, содержащих код операции, а второй-четвертый блоки селекции 6-8 производят селекцию входного потока по структуре пакетов. Регистр 9 стратегии поиска осуществляет проверку соответствия порядка поступления пакетов анализируемого цифрового потока правилам обмена информацией. Формирователь 10 временных интервалов обеспечивает определение закрытия соединения. При прохождении сигнала по конкретным цепочкам логических элементов блок 11 индикации формирует информационные сообщения о результатах поиска. При таком построении устройства достигается возможность работы в режиме реального времени, нулевая вероятность пропуска (в случае наличия априорно достоверной информации о протоколе), простота реализации и модификации под любой коммуникационный протокол диалогового типа. 7 з.п. ф-лы, 11 ил.

| SU, авторское свидетельство, 1711185, G 06 F 15/40, 1989 | |||

| SU, авторское свидетельство, 1621049, G 06 F 15/40, 1989. |

Авторы

Даты

1998-07-20—Публикация

1996-02-13—Подача