Изобретение относится к электросвязи и может быть использовано для поиска информации и идентификации, применяемых в цифровых системах связи и, в частности, в сетях передачи данных (СПД) коммуникационных протоколов Frame Relay (FR) и High-Level Data Link Control (HDLC), стандартизованных Международным союзом электросвязи, а также контроля качества канала связи и выбора для работы в СПД, на основе контроля, протокола FR или HDLC.

Известно устройство поиска информации (см., например, а.с. 1621049 СССР, МПК G 06 F 15/40, 1989 г.) содержащее регистры границ, суммирующие и вычитающие счетчики, схемы сравнения, блоки памяти, блоки вычисления и ряд других элементов, позволяющих осуществлять поиск информации.

Известный аналог осуществляет поиск информации статистическим способом. Однако указанный аналог имеет недостаток - низкая вероятность правильного распознавания, что ограничивает область его применения.

Известно устройство поиска информации (см. , например, патент РФ N 2094845, МПК G 06 F 15/40, опубл. 27.10.97), содержащее коммутатор, формирователь сигналов сброса, блоки селекции, дешифраторы, суммирующие счетчики, регистр стратегии поиска, блок индикации, позволяющие осуществлять поиск информации.

Известный аналог осуществляет поиск информации только по протокольным правилам. Однако указанный аналог имеет недостаток. Известное устройство имеет низкую вероятность правильного распознавания, что ограничивает область его применения.

Известно устройство поиска информации (см. , например, патент РФ N 2100839, МПК G 06 F 15/40, опубл. 27.12.97), содержащее коммутатор, первый, второй и третий регистр, блок сравнения, блок коррекции, регистр стратегии поиска, блок дешифрации, позволяющие осуществлять поиск информации.

Известный аналог применяет синтаксический способ распознавания коммуникационных протоколов, что обеспечивает принятие решения в реальном масштабе времени.

Недостатком аналога является невысокая достоверность распознавания коммуникационных протоколов, так как распознавание протоколов производится только по одному элементу структуры блоков данных - управляющему байту.

Наиболее близким по технической сущности к заявленному является устройство поиска информации по патенту РФ N 2133500, МПК G 06 F 15/40, опубл. 20.07.98. Известное устройство поиска информации состоит из первого коммутатора, первого регистра, блока сравнения, блока коррекции, первого регистра стратегии поиска, второго регистра, третьего регистра, первого дешифратора, формирователя управляющих сигналов, второго регистра стратегии поиска, четвертого регистра, пятого регистра, второго дешифратора, шифратора, второго коммутатора, блока селекции, таймерного блока, третьего дешифратора, четвертого дешифратора, третьего регистра стратегии поиска, блока индикации.

Тактовый вход блока коррекции соединен с тактовыми входами первого регистра и блока сравнения и является тактовым входом устройства поиска информации. Информационный вход первого регистра соединен с информационными входами первого коммутатора и блока коррекции и является информационным входом устройства поиска информации. Выход первого коммутатора соединен с информационным входом третьего регистра.

Первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой информационные выходы первого регистра соединены с соответствующими информационными входами блока сравнения, выход блока сравнения соединен с управляющим входом первого регистра стратегии поиска. Выход блока коррекции соединен с тактовыми входами первого регистра стратегии поиска и третьего регистра. Выход первого регистра стратегии поиска соединен с входом второго регистра и управляющим входом первого дешифратора. Выход второго регистра соединен с управляющим входом третьего регистра.

Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый информационные выходы третьего регистра соединены с соответствующими информационными входами первого дешифратора, первый управляющий выход первого дешифратора соединен с шестым управляющим входом формирователя управляющих сигналов, а второй управляющий выход первого дешифратора соединен с четвертым информационным входом шифратора. Первый и второй управляющие входы формирователя управляющих сигналов соединены соответственно с выходом блока сравнения и выходом первого регистра стратегии поиска.

Первый и второй управляющие выходы формирователя управляющих сигналов соединены соответственно с первым и вторым управляющими входами первого коммутатора, а третий управляющий выход формирователя управляющих сигналов соединен с управляющим входом второго регистра стратегии поиска, тактовый вход которого соединен с выходом блока коррекции. Выход второго регистра стратегии поиска соединен с входом четвертого регистра, управляющим входом второго дешифратора и третьим управляющим входом формирователя управляющих сигналов. Выход четвертого регистра соединен с управляющим входом пятого регистра, информационный вход пятого регистра соединен с выходом первого коммутатора, а тактовый вход пятого регистра соединен с выходом блока коррекции.

Первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой информационные выходы пятого регистра соединены с соответствующими информационными входами второго дешифратора. Первый и второй информационные выходы второго дешифратора соединены соответственно с четвертым и пятым управляющими входами формирователя управляющих сигналов, третий, четвертый и пятый информационные выходы второго дешифратора соединены соответственно с первым, вторым и третьим информационными входами шифратора. Первый, второй и третий информационные выходы шифратора соединены с соответствующими информационными входами второго коммутатора.

Первый, второй и третий информационные выходы второго коммутатора соединены с соответствующими информационными входами блока селекции, четвертый, пятый и шестой информационные выходы второго коммутатора соединены соответственно с первым, вторым и третьим информационными входами четвертого дешифратора. Первый, второй и третий информационные выходы блока селекции соединены с соответствующими информационными входами третьего дешифратора и информационными выходами таймерного блока, вход которого подключен к управляющему выходу блока селекции.

Первый управляющий выход третьего дешифратора подключен ко второму управляющему выходу четвертого дешифратора, выходу блока индикации и к первому управляющему входу третьего регистра стратегии поиска. Второй управляющий выход третьего дешифратора соединен со вторым управляющим входом третьего регистра стратегии поиска. Третий управляющий выход третьего дешифратора соединен с третьим управляющим выходом четвертого дешифратора и вторым управляющим входом блока индикации. Первый управляющий выход четвертого дешифратора соединен с первым управляющим входом блока индикации. Первый и второй управляющие выходы третьего регистра стратегии поиска соединены соответственно с первым и вторым управляющими входами второго коммутатора.

Устройство поиска информации - прототип применяет в качестве признаков как структуру блоков данных (кадров) так и правил обмена ими (протокольных правил) в ходе сеанса передачи данных, обеспечивающих повышенную достоверность распознавания коммуникационного протокола FR.

Недостатком прототипа является узкая область применения, т.к. известное устройство позволяет идентифицировать только один тип протокола, в частности, коммуникационный протокол FR.

Целью изобретения является разработка устройства поиска информации, обеспечивающего возможность его применения в более широкой области, в частности, для распознавания коммуникационных протоколов FR и HDLC, контроля качества обмена данными, осуществляемому по протоколу FR или HDLC, а также для идентификации смены протокола удаленной станцией.

Поставленная цель достигается тем, что в известное устройство поиска информации, содержащее первый коммутатор, первый информационный выход которого подключен к информационному входу третьего регистра, управляющий вход которого подключен к выходу второго регистра, управляющий вход которого подключен к выходу регистра стратегии поиска и третьему управляющему входу первого коммутатора, информационный и тактовый входы первого регистра подключены соответственно к информационному и тактовому входам блока коррекции и являются одновременно информационным и тактовыми входами устройства, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой выходы первого регистра подключены к соответствующим информационным входам блока сравнения, тактовый вход которого подключен к тактовому входу блока коррекции, информационный вход которого подключен к информационному входу первого коммутатора, выход блока сравнения подключен к управляющему входу регистра стратегии поиска и второму управляющему входу первого коммутатора, тактовый вход третьего регистра подключен к тактовым входам регистра стратегии поиска, второго регистра и к выходу блока коррекции, дополнительно введены блок дешифрации, первый и второй блоки контроля качества канала, второй коммутатор.

Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый выходы третьего регистра подключены к соответствующим информационным входам блока дешифрации. Первый управляющий вход второго коммутатора подключен ко второму управляющему выходу блока дешифрации, четырнадцатый, десятый, девятый информационные входы которого подключены соответственно к первому, второму, третьему информационным входам второго коммутатора, второй управляющий вход которого подключен к выходу второго регистра. Управляющий вход блока дешифрации подключен к выходу регистра стратегии поиска.

Первый и второй управляющие выходы второго блока контроля качества канала подключены соответственно к первому и четвертому управляющим входам первого коммутатора. Управляющий вход второго блока контроля качества канала подключен к первому управляющему выходу блока дешифрации, первый и второй информационные выходы которого подключены соответственно к информационным выходам второго и первого блоков контроля качества канала и являются одновременно первым и вторым информационными выходами устройства. Первый, второй, третий выходы второго коммутатора подключены к соответствующим входам первого блока контроля качества канала. Второй информационный выход первого коммутатора подключен к информационному входу второго блока контроля качества канала, тактовый вход которого подключен к выходу блока коррекции.

Блок дешифрации состоит из первого дешифратора, первый и второй выходы которого подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к первому входу триггера. Второй вход триггера подключен к третьему выходу первого дешифратора, который является одновременно первым управляющим выходом блока. Управляющий вход первого дешифратора подключен к управляющему входу второго дешифратора и является одновременно управляющим входом блока. Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой входы первого дешифратора являются соответственно девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым, шестнадцатым информационными входами блока. Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой входы второго дешифратора являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым информационными входами блока. Выход второго дешифратора является вторым управляющим выходом блока. Первый и второй выходы триггера являются соответственно первым и вторым информационными выходами блока.

Первый блок контроля качества канала состоит из элемента И-НЕ, выход которого подключен к управляющему входу коммутатора, тактовому входу триггера, тактовому входу счетчика искаженных кадров, тактовому входу счетчика кадров. Выход счетчика кадров подключен ко второму информационному входу триггера и управляющему входу дешифратора, N информационных входов которого подключены к N выходам счетчика искаженных кадров. Информационный вход счетчика искаженных кадров подключен к выходу элемента исключающее  , управляющий вход счетчика искаженных кадров подключен ко второму выходу триггера. Первый выход триггера подключен к первому входу элемента исключающее

, управляющий вход счетчика искаженных кадров подключен ко второму выходу триггера. Первый выход триггера подключен к первому входу элемента исключающее  второй вход которого подключен к выходу коммутатора и первому информационному входу триггера. Информационный вход коммутатора является первым входом блока. Первый и второй входы элемента И-НЕ являются соответственно вторым и третьим входами блока. Выход дешифратора является информационным выходом блока.

второй вход которого подключен к выходу коммутатора и первому информационному входу триггера. Информационный вход коммутатора является первым входом блока. Первый и второй входы элемента И-НЕ являются соответственно вторым и третьим входами блока. Выход дешифратора является информационным выходом блока.

Второй блок контроля качества канала состоит из первого регистра стратегии поиска, первый выход которого подключен к первому выходу второго регистра стратегии поиска и является одновременно первым управляющим выходом блока. Второй выход первого регистра стратегии поиска подключен к управляющему входу первого регистра, второму выходу второго регистра стратегии поиска, управляющему входу дешифратора и является одновременно вторым управляющим выходом блока. Выход первого регистра подключен к управляющему входу второго регистра, выход которого подключен к информационному входу дешифратора, второй выход которого подключен к управляющему входу второго регистра стратегии поиска. Тактовый вход первого регистра стратегии поиска подключен к тактовым входам первого, второго регистров, второго регистра стратегии поиска и является одновременно тактовым входом блока. Информационный вход второго регистра и управляющий вход первого регистра стратегии поиска являются соответственно информационным и управляющим входом блока. Первый выход дешифратора является информационным выходом блока.

Благодаря новой совокупности существенных признаков за счет введения блока дешифрации, первого и второго блоков контроля качества канала, второго коммутатора обеспечивается распознавание протоколов FR и HDLC, контроль качества канала связи и выбор на основе контроля протокола FR или HDLC, а также идентификация смены протокола удаленной станцией. Этим достигается возможность применения заявленного устройства в более широкой области, в частности для работы в нестационарных каналах связи.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

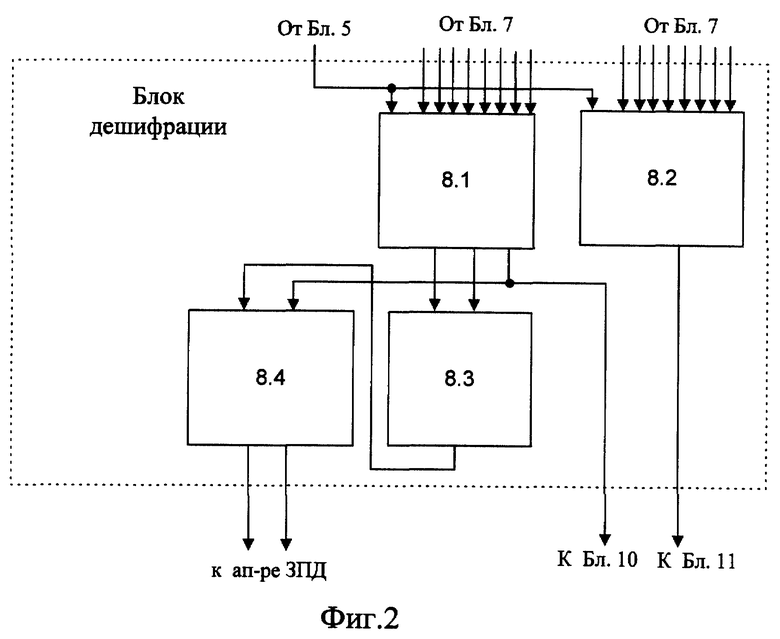

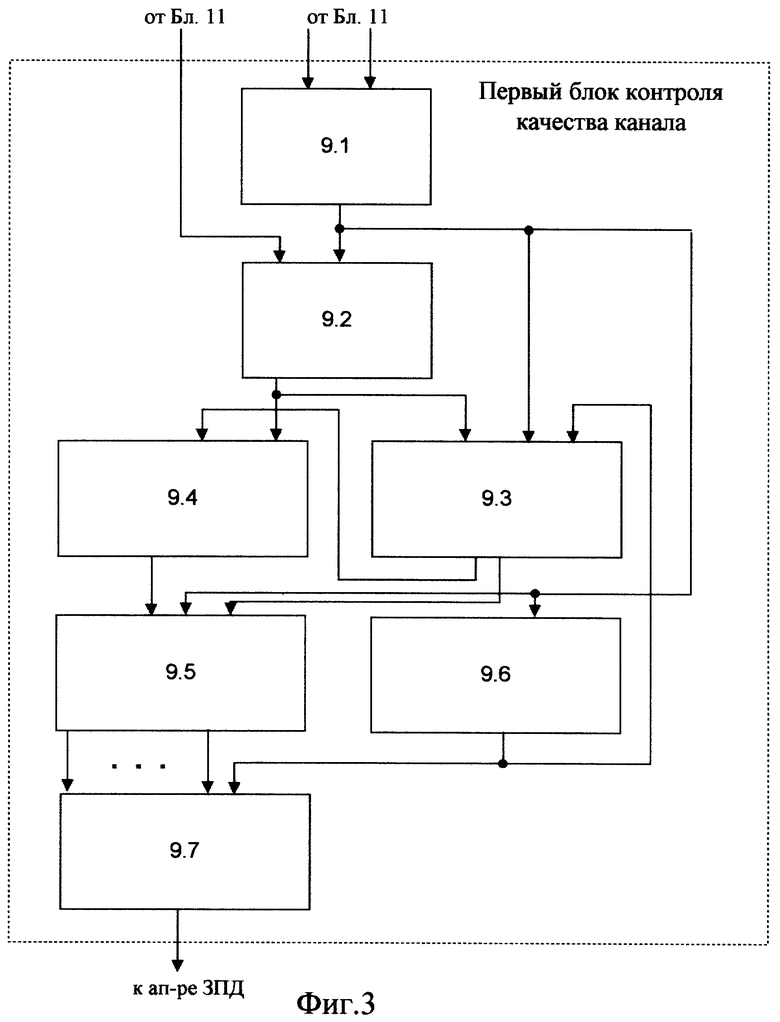

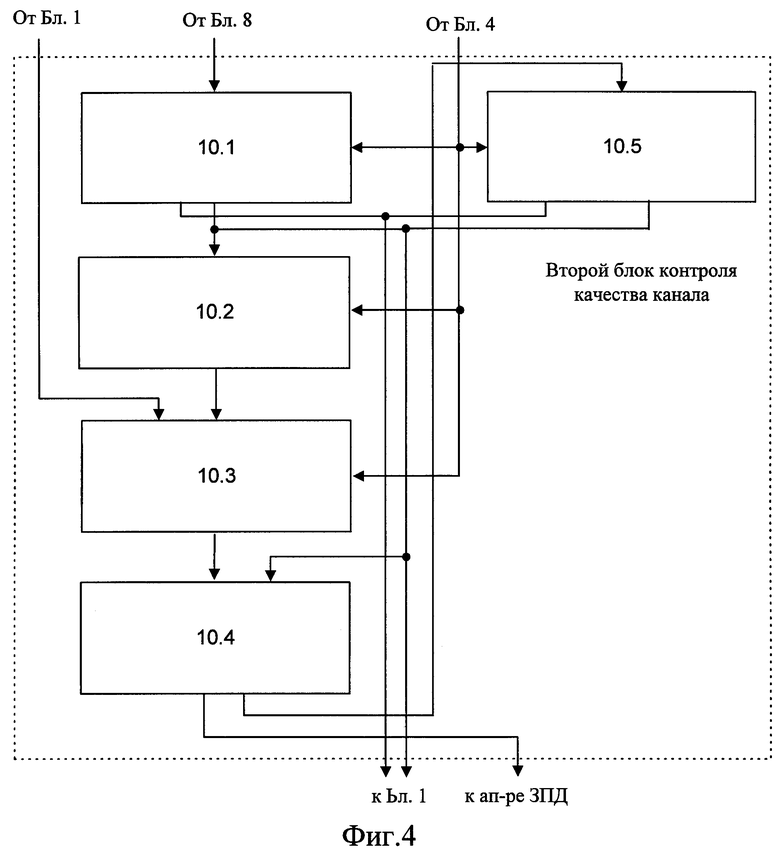

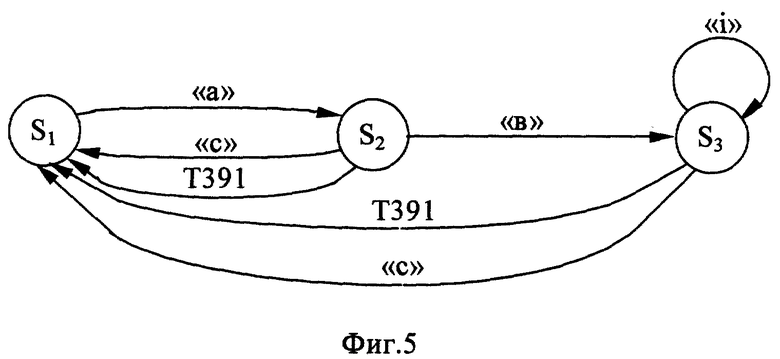

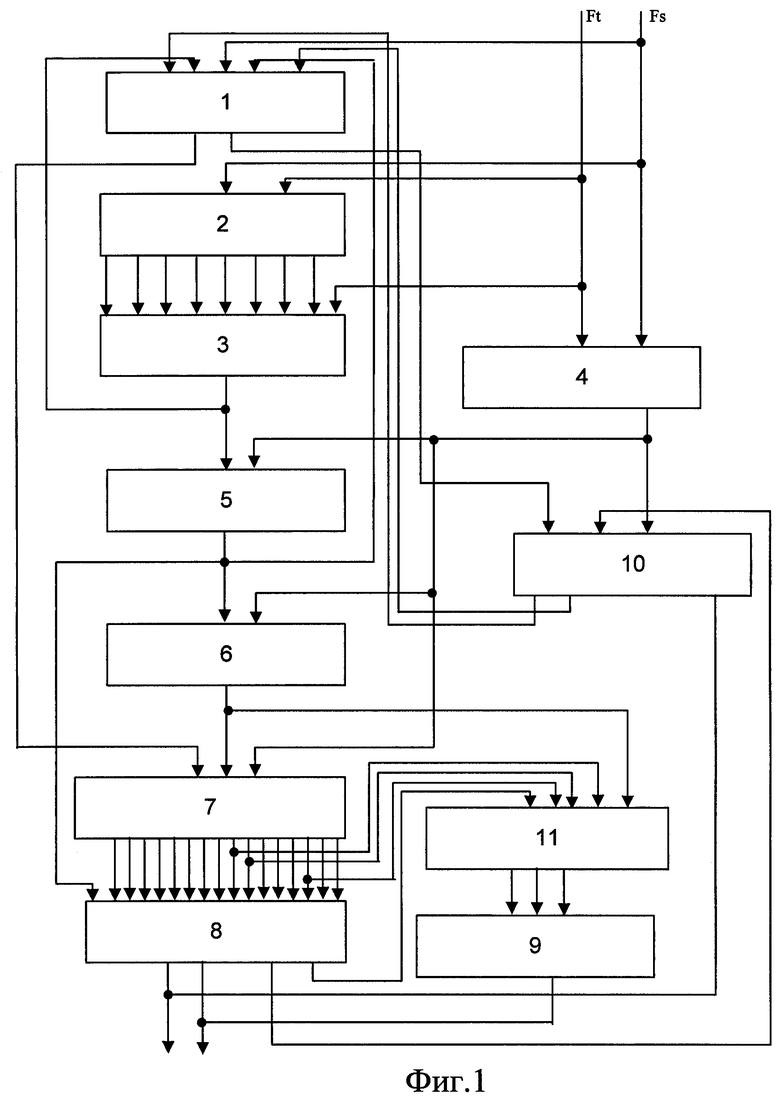

Заявленное устройство поясняется чертежами, на которых:

на фиг. 1 представлена электрическая функциональная схема предлагаемого устройства;

на фиг. 2 - электрическая функциональная схема блока дешифрации;

на фиг. 3 - электрическая функциональная схема первого блока контроля качества канала;

на фиг. 4 - электрическая функциональная схема второго блока контроля качества канала;

на фиг. 5 - алгоритм синтаксического распознавания интерфейса локального управления протокола FR с синхронно-симплексной стратегией управления по постоянному выделенному каналу;

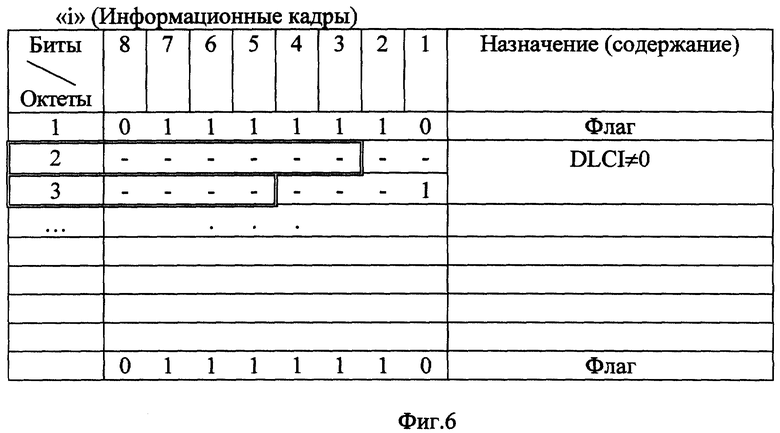

на фиг. 6 - формат информационного кадра протокола FR;

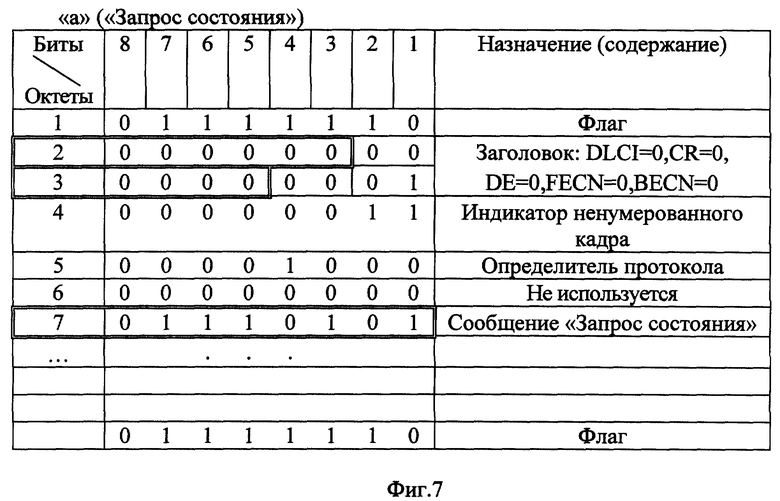

на фиг. 7 - формат управляющего кадра "Запрос состояния" протокола FR;

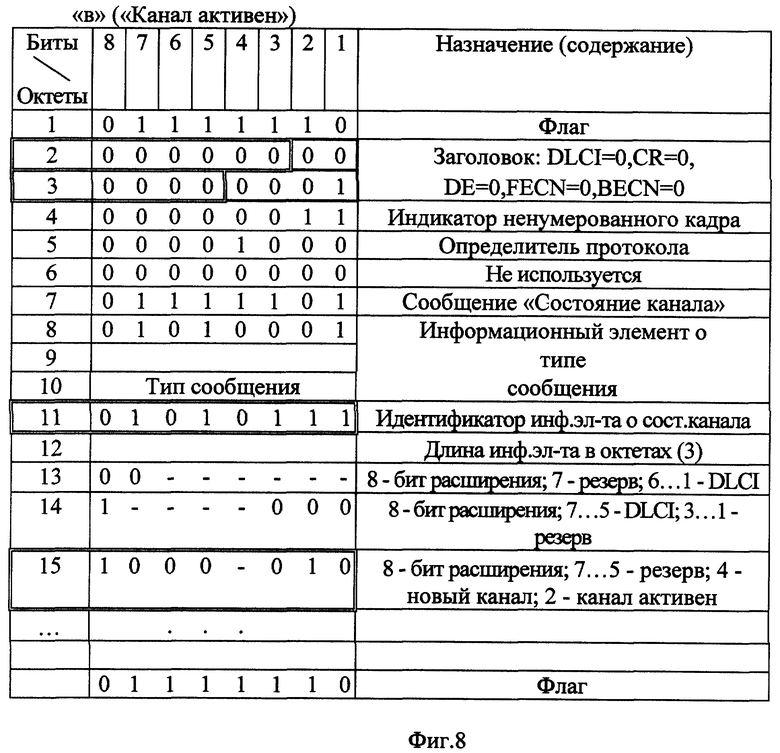

на фиг. 8 - формат управляющего кадра "Состояние канала, канал активен" протокола FR;

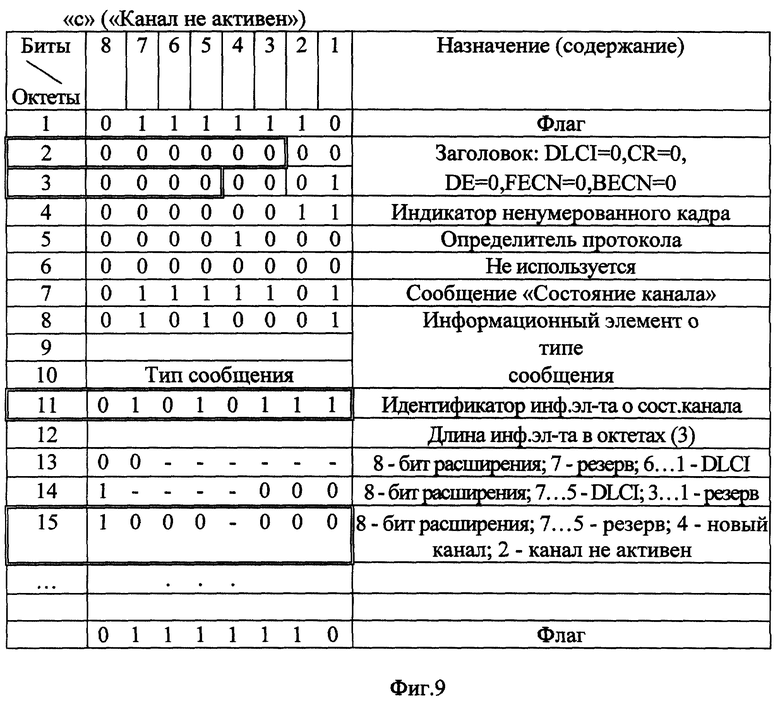

на фиг. 9 - формат управляющего кадра "Состояние канала, канал не активен" протокола FR;

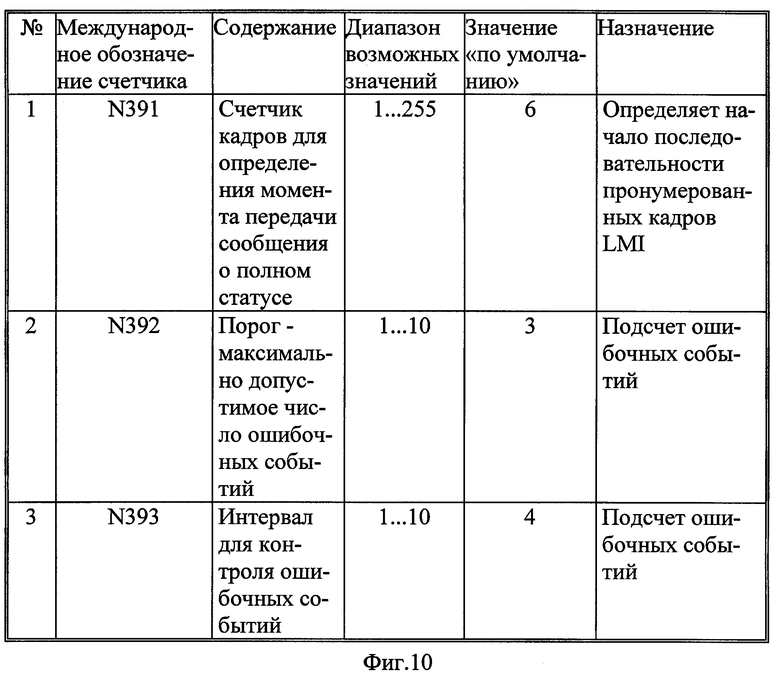

на фиг. 10 - счетчики событий, используемые для синхронизации процессов управления LMI протокола FR;

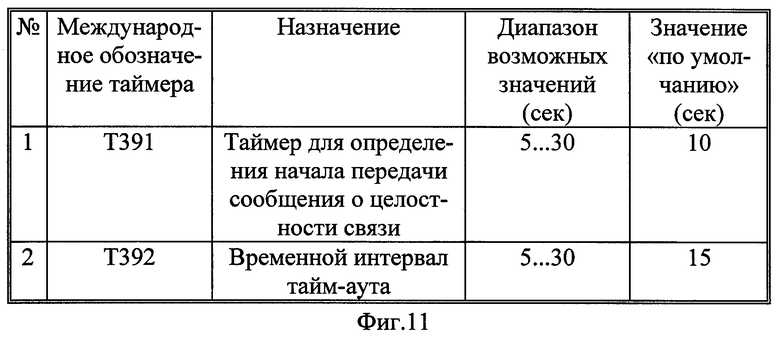

на фиг. 11 - счетчики времени, используемые для синхронизации процессов управления LMI протокола FR;

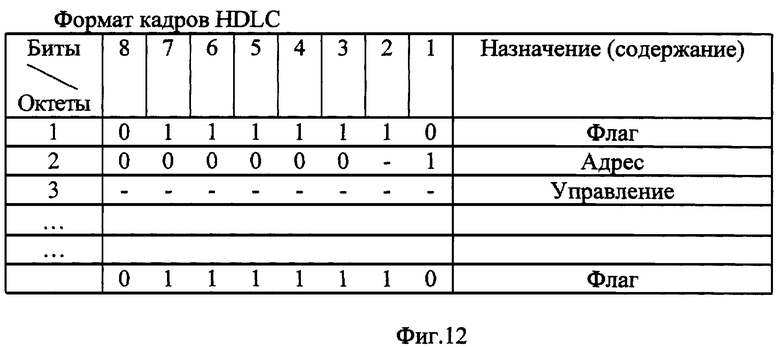

на фиг. 12 - формат кадров HDLC;

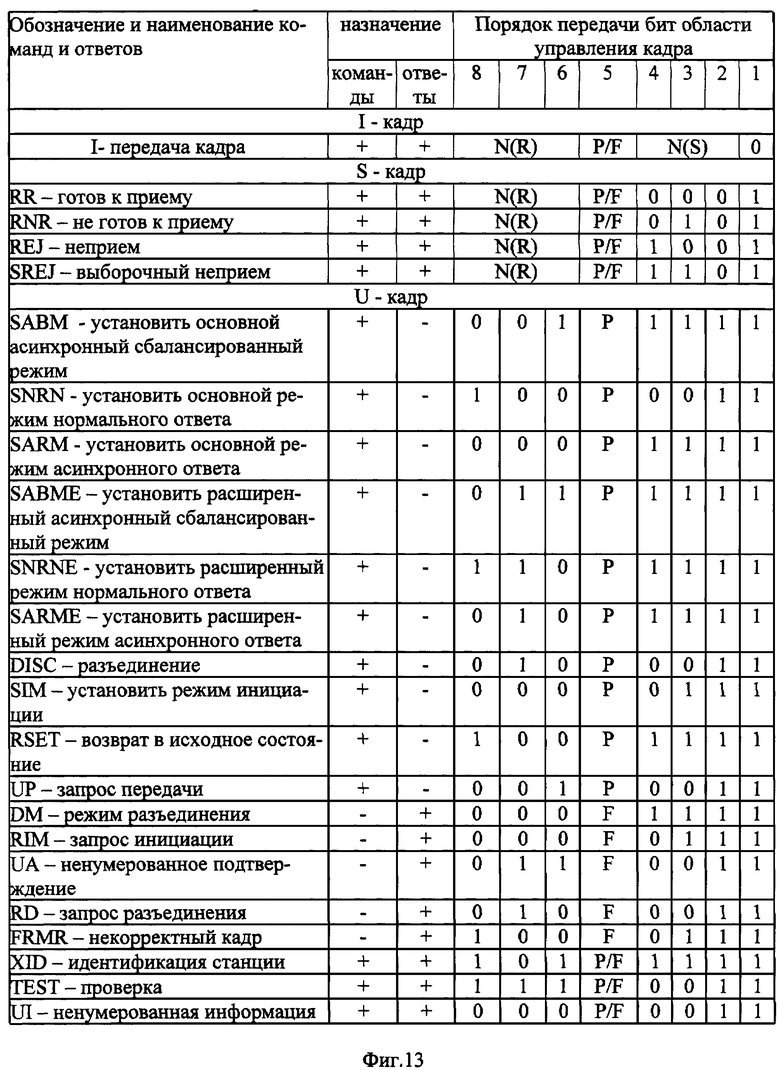

на фиг. 13 - структура области управления кадров основного формата коммуникационных протоколов подмножества HDLC.

Устройство поиска информации, показанное на фиг. 1, содержит первый коммутатор 1, первый регистр 2, блок сравнения 3, блок коррекции 4, регистр стратегии поиска 5, второй регистр 6, третий регистр 7, блок дешифрации 8, первый блок контроля качества канала 9, второй блок контроля качества канала 10, второй коммутатор 11. Первый информационный выход первого коммутатора 1 подключен к информационному входу третьего регистра 7, управляющий вход которого подключен к выходу второго регистра 6, управляющий вход которого подключен к выходу регистра стратегии поиска 5 и третьему управляющему входу первого коммутатора 1. Информационный и тактовый входы первого регистра 2 подключены соответственно к информационному и тактовому входам блока коррекции 4 и являются одновременно информационным и тактовыми входами устройства. Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой выходы первого регистра 2 подключены к соответствующим информационным входам блока сравнения 3. Тактовый вход блока сравнения 3 подключен к тактовому входу блока коррекции 4, информационный вход которого подключен к информационному входу первого коммутатора 1. Выход блока сравнения 3 подключен к управляющему входу регистра стратегии поиска 5 и второму управляющему входу первого коммутатора 1. Тактовый вход третьего регистра 7 подключен к тактовым входам регистра стратегии поиска 5, второго регистра 6 и к выходу блока коррекции 4.

Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый, четырнадцатый, пятнадцатый, шестнадцатый выходы третьего регистра 7 подключены к соответствующим информационным входам блока дешифрации 8. Первый управляющий вход второго коммутатора 11 подключен ко второму управляющему выходу блока дешифрации 8, четырнадцатый, десятый, девятый информационные входы которого подключены соответственно к первому, второму, третьему информационным входам второго коммутатора 11, второй управляющий вход которого подключен к выходу второго регистра 6. Управляющий вход блока дешифрации 8 подключен к выходу регистра стратегии поиска 5. Первый и второй управляющие выходы второго блока контроля качества канала 10 подключены соответственно к первому и четвертому управляющим входам первого коммутатора 1. Управляющий вход второго блока контроля качества канала 10 подключен к первому управляющему выходу блока дешифрации 8, первый и второй информационные выходы которого подключены соответственно к информационным выходам второго 10 и первого 9 блоков контроля качества канала и являются одновременно первым и вторым информационными выходами устройства. Первый, второй, третий выходы второго коммутатора 11 подключены к соответствующим входам первого блока контроля качества канала 9. Второй информационный выход первого коммутатора 1 подключен к информационному входу второго блока контроля качества канала 10, тактовый вход которого подключен к выходу блока коррекции 4.

Блок дешифрации 8, показанный на фиг. 4, предназначен для подключения к цифровому потоку первого 9 или второго 10 блока контроля качества канала при осуществлении обмена данными по протоколу HDLC или FR соответственно, а также выдачи сигнала в аппаратуру ЗПД местной станции на смену протокола при получении соответствующей команды от удаленной станции, состоит из первого дешифратора 8.1, второго дешифратора 8.2, элемента ИЛИ 8.3, триггера 8.4. Первый и второй выходы первого дешифратора 8.1 подключены соответственно к первому и второму входам элемента ИЛИ 8.3, выход которого подключен к первому входу триггера 8.4. Второй вход триггера 8.4 подключен к третьему выходу первого дешифратора 8.1 и является одновременно первым управляющим выходом блока 8. Управляющий вход первого дешифратора 8.1 подключен к управляющему входу второго дешифратора 8.2, который является одновременно управляющим входом блока 8.

Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой входы первого дешифратора 8.1 являются соответственно девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым, пятнадцатым, шестнадцатым информационными входами блока 8. Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой входы второго дешифратора 8.2 являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым информационными входами блока 8. Выход второго дешифратора 8.2 является вторым управляющим выходом блока 8. Первый и второй выходы триггера 8.4 являются соответственно первым и вторым информационными выходами блока 8.

Первый блок контроля качества канала 9, показанный на фиг. 3, предназначен для контроля качества канала связи при работе аппаратуры ЗПД по протоколу HDLC и выдачи сигнала в аппаратуру ЗПД местной станции на вхождение в связь по протоколу FR, при заданном качестве канала связи, состоит из элемента И-НЕ 9.1, коммутатора 9.2, триггера 9.3, элемента исключающее  9.4, счетчика искаженных кадров 9.5, счетчика кадров 9.6, схемы сравнения 9.7. Выход элемента И-НЕ 9.1 подключен к управляющему входу коммутатора 9.2, тактовому входу триггера 9.3, тактовому входу счетчика искаженных кадров 9.5, тактовому входу счетчика кадров 9.6. Выход счетчика кадров 9.6 подключен ко второму информационному входу триггера 9.3 и управляющему входу дешифратора 9.7, N информационных входов которого подключены к N выходам счетчика искаженных кадров 9.5.

9.4, счетчика искаженных кадров 9.5, счетчика кадров 9.6, схемы сравнения 9.7. Выход элемента И-НЕ 9.1 подключен к управляющему входу коммутатора 9.2, тактовому входу триггера 9.3, тактовому входу счетчика искаженных кадров 9.5, тактовому входу счетчика кадров 9.6. Выход счетчика кадров 9.6 подключен ко второму информационному входу триггера 9.3 и управляющему входу дешифратора 9.7, N информационных входов которого подключены к N выходам счетчика искаженных кадров 9.5.

Информационный вход счетчика искаженных кадров 9.5 подключен к выходу элемента исключающее  9.4, управляющий вход счетчика искаженных кадров 9.5 подключен ко второму выходу триггера 9.3. Первый выход триггера 9.3 подключен к первому входу элемента исключающей

9.4, управляющий вход счетчика искаженных кадров 9.5 подключен ко второму выходу триггера 9.3. Первый выход триггера 9.3 подключен к первому входу элемента исключающей  9.4, второй вход которого подключен к выходу коммутатора 9.2 и первому информационному входу триггера 9.3. Информационный вход коммутатора 9.2 является первым входом блока 9. Первый и второй входы элемента И-НЕ 9.1 являются соответственно вторым и третьим входами блока 9. Выход дешифратора 9.7 является информационным выходом блока 9.

9.4, второй вход которого подключен к выходу коммутатора 9.2 и первому информационному входу триггера 9.3. Информационный вход коммутатора 9.2 является первым входом блока 9. Первый и второй входы элемента И-НЕ 9.1 являются соответственно вторым и третьим входами блока 9. Выход дешифратора 9.7 является информационным выходом блока 9.

Второй блок контроля качества канала 10, показанный на фиг. 4, предназначен для контроля качества канала связи при работе аппаратуры ЗПД по протоколу FR и выдачи сигнала в аппаратуру ЗПД местной станции на вхождение в связь по протоколу HDLC при приеме кадра "Канал не активен", состоит из первого регистра стратегии поиска 10.1, первого регистра 10.2, второго регистра 10.3, дешифратора 10.4, второго регистра стратегии поиска 10.5. Первый выход первого регистра стратегии поиска 10.1 подключен к первому выходу второго регистра стратегии поиска 10.5 и является одновременно первым управляющим выходом блока 10. Второй выход первого регистра стратегии поиска 10.1 подключен к управляющему входу первого регистра 10.2, второму выходу второго регистра стратегии поиска 10.5, управляющему входу дешифратора 10.4 и является одновременно вторым управляющим выходом блока 10. Выход первого регистра 10.2 подключен к управляющему входу второго регистра 10.3, выход которого подключен к информационному входу дешифратора 10.4, второй выход которого подключен к управляющему входу второго регистра стратегии поиска 10.5. Тактовый вход первого регистра стратегии поиска 10.1 подключен к тактовым входам первого 10.2, второго 10.3 регистров, второго регистра стратегии поиска 10.5 и является одновременно тактовым входом блока 10. Информационный вход второго регистра 10.3 и управляющий вход первого регистра стратегии поиска 10.1 являются соответственно информационным и управляющим входом блока 10. Первый выход дешифратора 10.4 является информационным выходом блока 10.

Первый коммутатор 1 предназначен для коммутации входной цифровой последовательности на вход третьего регистра 7 и второго блока контроля качества канала 10. Второй коммутатор 11 предназначен для коммутации входной цифровой последовательности на вход первого блока контроля качества канала 9. Коммутатор 9.2 предназначен для коммутации входной цифровой последовательности на вход элементов исключающее  9.4 и триггера 9.3. Вариант построения коммутаторов представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М. : Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып. 1111) стр. 226, рис.2.27 и может быть реализован на микросхемах серии К555ИП7.

9.4 и триггера 9.3. Вариант построения коммутаторов представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М. : Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып. 1111) стр. 226, рис.2.27 и может быть реализован на микросхемах серии К555ИП7.

Первый регистр 2 предназначен для последовательного выделения восьми элементов входного цифрового потока, поступающего на его информационный вход, регистр стратегии поиска 5 предназначен для задержки управляющего сигнала, поступающего на его управляющий вход, на шестнадцать тактов, первый регистр стратегии поиска 10.1 предназначен для задержки управляющего сигнала, поступающего на его управляющий вход, на пятьдесят шесть и шестьдесят четыре такта, второй регистр стратегии поиска 10.5 предназначен для задержки управляющего сигнала, поступающего на его управляющий вход, на двадцать четыре и тридцать два такта, третий регистр 7 предназначен для последовательного выделения шестнадцати элементов входного цифрового потока, второй регистр 10.3 предназначен для последовательного выделения восьми элементов входного цифрового потока. Схемы регистров известны и описаны, например, в а. с. 1591072 СССР, МПК6 G 11 С 19/00, заявл. 23.11.88, опубл. 7.09.90 и могут быть реализованы на микросхемах серии К555ИР8.

Блок сравнения 3 предназначен для определения наличия на его первом-восьмом информационных входах кодовой комбинации 01111110, соответствующей "флагу". Вариант построения блока сравнения представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник.-М.: Радио и связь, 1987. - 352 с. : ил. - (Массовая радиобиблиотека. Вып.1111) стр. 273, рис. 2.68 и может быть реализован на микросхемах серии К555СП1.

Блок коррекции 4 предназначен для выявления и удаления бит "прозрачности", включаемых в цифровую последовательность и на передающей станции с целью исключения случайного появления комбинации, соответствующей "флагу". Вариант построения блока коррекции известен и представлен на фиг. 2 в Патенте РФ N 2100839 МПК G 06 F 15/40, опубл. 27.12.97. В частности, такая схема может быть реализована на микросхемах серии К555.

Второй 6, первый 10.2 регистры идентичны и предназначены для выработки управляющего импульса на обнуление содержания ячеек соответственно третьего 7 и второго 10.3 регистров после считывания с них информации. Вариант построения регистров представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник.-М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып.1111) стр. 78, рис. 1.57 и может быть реализован на микросхемах серии К555ТМ9.

Первый дешифратор 8.1 предназначен для преобразования октетов "SABM" и "DM" в пределах кадра HDLC (фиг. 13), третьего октета канала локального управления (LMI) в пределах кадра FR (фиг. 8,9), поступивших с третьего регистра 7, в информацию о наличии одного из трех сообщений протоколов HDLC или FR. Второй дешифратор 8.2 предназначен для преобразования второго октета в пределах кадра HDLC (фиг. 12), поступивших с третьего регистра 7 в информацию о работе аппаратуры ЗПД по протоколу HDLC. Вариант построения дешифраторов известны и описаны, например, в книге Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973, стр.146, рис.3.36 и может быть реализована на микросхемах серии К555ИД7.

Элемент ИЛИ 8.3, элемент И-НЕ 9.1 предназначены для логической развязки сигналов между входами и выходами микросхем. Варианты построения элементов ИЛИ, И-НЕ известны и описаны, например, в книге Тарабрин Б.В. Интегральные микросхемы: Справочник. - М.: Энергоатомиздат, 1985, стр.282 и могут быть реализованы соответственно на микросхемах серии К555ЛЛ1, К555ЛА3.

Триггер 8.4 предназначен для выработки управляющего сигнала на первом или втором выходе в зависимости от управляющего сигнала соответственно на его первом или втором входе. Вариант построения триггера представлен в книге Шило В. Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с. : ил. - (Массовая радиобиблиотека. Вып.1111) стр.63, рис. 1.42.

Триггер 9.3 предназначен для задержки входного сигнала на один такт. Вариант построения триггера представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М. : Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып. 1111) стр.78, рис.1.57 и может быть реализован на микросхемах серии К555ТМ9.

Элемент исключающее  9.4 предназначен для логической развязки сигналов между входами и выходами микросхем. Вариант построения элемента исключающее

9.4 предназначен для логической развязки сигналов между входами и выходами микросхем. Вариант построения элемента исключающее  представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып. 1111) стр.57, рис. 1.35. Счетчик искаженных кадров 9.5 предназначен для подсчета числа перезапросов от удаленной станции.

представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып. 1111) стр.57, рис. 1.35. Счетчик искаженных кадров 9.5 предназначен для подсчета числа перезапросов от удаленной станции.

Счетчик искаженных кадров представляет собой последовательный регистр. Схемы регистров известны и описаны, например, в а.с. 1591072 СССР, МПК6 G 11 С 19/00, заявл. 23.11.88, опубл. 7.09.90 и могут быть реализованы на микросхемах серии К555ИР8.

Счетчик кадров 9.6 предназначен для подсчета общего числа информационных и супервизорных кадров HDLC, т.е. интервала для контроля качества канала связи. Вариант построения счетчика представлен в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. - (Массовая радиобиблиотека. Вып.1111) стр.94, рис.1.69 и может быть реализован на микросхемах серии К155ИЕ8.

Дешифратор 9.7 предназначен для преобразования информации о количестве единиц на выходах счетчика искаженных кадров 9.5 в информацию о качестве канала связи. Вариант построения дешифраторов известны и описаны, например, в книге Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М. : Связь, 1973, стр. 146, рис.3.36 и может быть реализована на микросхемах серии К555ИД7.

Дешифратор 10.4 предназначен для преобразования октетов "Идентификатор информационного элемента о состоянии канала" и октета, указывающего на то, что данный канал "не активный" (фиг. 9), поступивших со второго регистра 10.3, соответственно в управляющий сигнал на управляющем входе второго регистра стратегии поиска 10.5 и управляющий сигнал на первом информационном выходе устройства поиска информации. Вариант построения дешифратора известны и описаны, например, в книге Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973, стр. 146, рис. 3.36 и может быть реализована на микросхемах серии К555ИД7.

Устройство работает следующим образом.

Устройство поиска информации, предназначено для распознавания коммуникационных протоколов FR и HDLC, контроля качества обмена данными, осуществляемому по протоколу FR или HDLC и выдачи сигнала в аппаратуру ЗПД местной и удаленной станции об использовании одного из двух типов протоколов в зависимости от сигнально-помеховой обстановки в канале связи.

Протокол FR был создан для замены протокола HDLC на высокоскоростных каналах связи. Как и HDLC, он обеспечивает множество независимых виртуальных каналов в одном физическом канале связи, но не имеет средств коррекции и восстановления при возникновении ошибок. Следовательно, при хорошем качестве канала связи целесообразнее работать по протоколу FR, обеспечивая высокую скорость передачи данных, а при качестве канала ниже заданного логичен переход на работу по протоколу HDLC. При отсутствии между местной и удаленной станцией резервных каналов связи, которые можно использовать при плохом качестве в рабочем канале, в составе станций должно быть предусмотрено устройство позволяющее определять переход взаимодействующей станции на работу по протоколу FR или HDLC, а также анализировать качество канала связи и инициировать работу по одному из протоколов в зависимости от состояния канала.

Первоначально вхождение в связь осуществляется по протоколу FR.

Протокол FR не предусматривает передачу сигнальных сообщений (нет командных (или супервизорных) кадров). Для передачи служебной информации используется специально выделенный канал управления (Local Management Interface - LMI), внутри которого передаются супервизорные кадры.

В распознаваемом протоколе, описанном в книге Мельников Д. А. Информационные процессы в компьютерных сетях. Протоколы, стандарты, интерфейсы, модели. - М: КУДИЦ-ОБРАЗ, 1999. - 256 с. на стр. 146- 165, используется три типа кадров, один из которых передается в направлении от пользователя к сети, а два от сети к пользователю.

Собственно алгоритм функционирования интерфейса локального управления протокола FR с синхронно-симплексной стратегией управления по постоянному выделенному каналу (ПВК) состоит в следующем (фиг. 5): установление пользователем режима соединения с сетью FR начинается с передачи в сеть сообщения типа "а" ("Запрос состояния") (фиг. 7), при этом пользователь из начального состояния S1 переходит в состояние S2, если сеть в течение времени Т391 (фиг. 11) не ответила пользователю, то пользователь возобновляет передачу сообщения типа "а", если сеть после передачи ей сообщения типа "а" пришлет сообщение типа "с" ("канал не активен) (фиг. 9), то пользователь через интервал времени Т391 повторяет передачу сообщения типа "а". Данный процесс будет повторяться до тех пор, пока не будет получено сообщение о доступности канала, либо не будет отменен пользователем.

Если канал оказывается доступным, то сетью передается сообщение типа "в" ("канал активен") (фиг. 8) и пользователь переходит в режим передачи информации (состояние S3), в котором передаются сообщения типа "i" ("Информационные кадры") (фиг. 6). Через определенный временной интервал (Т391) пользователь прекращает передачу информации, возвращается в состояние S1 и посылает в сеть сообщение типа "а" с целью подтверждения целостности связи, на что сеть отвечает сообщениями типа "в", содержащими требуемый элемент информации о целостности связи.

Интерфейсом LMI ведется подсчет числа опросов. После определенного числа переданных сообщений "а" (этот интервал имеет международное обозначение - N391 (фиг. 10)) абонент запрашивает у сети информацию о так называемом полном состоянии, используя также сообщение "а".

В случае возникновения ошибок сеть FR в сообщении "Состояние" устанавливает бит "активный ПВК" в "О", указывая тем самым временную неготовность канала (сообщение типа "в"). Когда ошибка устранена, сеть устанавливает бит "активный ПВК" в "1" (сообщение типа "с"). Однако данные действия сети происходят не сразу при возникновении ошибок, а только при превышении установленного "порога". Этот порог определяется протоколом FR и может изменяться пользователем. Сеть осуществляет подсчет ошибок (максимальное значение этого числа имеет международное обозначение - N392), возникающих в пределах установленного периода (это интервал имеет международное обозначение - N393). Если за интервал N393 порог N392 превышен, то сеть переводит канал в неактивное состояние. Выход из него - получение сетью безошибочного сообщения типа "а".

Однако стандарт FR не вводит процедур, на основе которых однозначно определяется, что ошибочная ситуация устранена и абонент может передать сообщения типа "а". Существует только одна возможность определения устранения ошибки, когда N392 событий происходят без ошибки.

В ряде случаев (преднамеренное воздействие помехами на канал связи) могут возникать тупиковые ситуации, когда канал продолжительное время будет находиться в неактивном состоянии. В связи с этим целесообразнее при получении от сети сообщения типа "с" не ожидать когда изменится сигнально-помеховая обстановка в канале связи, а сразу переходить на более помехоустойчивый протокол (например, HDLC), тем самым уменьшая время реакции аппаратуры на изменение внешних условий.

В то же время, при работе аппаратуры ЗПД по протоколу HDLC, описанному в книгах Протоколы информационно-вычислительных сетей. Справочник./ Аничкин.С. А, Белов С. А., Бернштейн А. А. и др. Под ред. И. А. Мизина, А. П. Кулешова. - М.: Радио и связь, 1990.- 504 с. на стр.96 -109; Мельников Д. А. Информационные процессы в компьютерных сетях. Протоколы, стандарты, интерфейсы, модели. - М: КУДИЦ-ОБРАЗ, 1999.- 256 с. на стр.47-51, 226-239, контролируя состояние канала связи, можно при качестве канала выше заданного (количество ошибок за определенный интервал) переходить на более высокоскоростной протокол FR.

Таким образом, в составе аппаратуры должны быть устройства позволяющие:

- идентифицировать цифровой поток на его принадлежность к протоколу FR или HDLC (блок дешифрации 8);

- контролировать качество канала связи при работе по протоколу FR или HDLC (первый 9 и второй 10 блоки контроля качества канала);

- по результатам контроля (первый 9 и второй 10 блоки контроля качества канала), а также в случае получения соответствующей команды от удаленной станции (блок дешифрации 8), выдавать команду в аппаратуру ЗПД на перевод аппаратуры для работы по протоколу FR или HDLC.

Идентификация коммуникационных протоколов в устройстве осуществляется на основе анализа структуры блоков данных (кадров). Для идентификации протокола HDLC можно использовать второй октет входной цифровой последовательности. Ели второй октет соответствует октету, показанному на фиг. 12, то принимается решении о принадлежности принимаемого кадра протоколу HDLC, т. к. второй октет ни одного из типов сообщений протокола FR (фиг. 6,7,8,9) не имеет идентичной структуры.

Контролировать качество канала связи при работе по протоколу HDLC можно по количеству перезапросов от удаленной станции, передаваемых в составе информационных и супервизорных кадров HDLC (фиг. 13). Для этой цели достаточно сравнить шестой бит третьего октета кадра HDLC N-1 и N-го кадра. Появление подряд значений 0 или 1 в сравниваемых битах свидетельствует о перезапросе от удаленной станции.

Контроль качества канала связи при работе по протоколу FR реализуется на основе ряда счетчиков (фиг. 10). Поэтому блоку контроля качества канала FR достаточно в принимаемом цифровом потоке выявить сообщение LMI типа "с" (фиг. 9).

Подключение кадров HDLC к первому блоку контроля качества канала 9, а также канала LMI ко второму блоку контроля качества канала 10 обеспечивается блоком дешифрации 8.

Идентификация смены протокола удаленной станцией обеспечивается по принимаемым сообщениям о вхождении в связь по протоколу отличному от текущего. Вхождение в связь по протоколу HDLC для дуплексного ЗПД, работающего в режиме АВМ (наиболее часто применяемого на практике), осуществляется с помощью команды SABM, и в ряде случаев командой DM и затем SABM (фиг. 13). Вхождение в связь по протоколу FR осуществляется с помощью канала LMI.

В случае приема кадра не соответствующего используемому в данный момент протоколу аппаратурой ЗПД производится стирание кадра, однако, блок дешифрации 8 идентифицирует данные сообщения и выдает команду о переходе аппаратуры ЗПД на другой протокол.

Входными сигналами для устройства поиска информации (фиг. 1) являются сигнальная цифровая последовательность Fs и сигнал тактовой частоты Ft, поступающие с модема.

Первый коммутатор 1 предназначен для коммутации входной цифровой последовательности на вход третьего регистра 7 и второго блока контроля качества канала 10. При поступлении на второй управляющий вход первого коммутатора 1 управляющего сигнала осуществляется коммутация входного потока, поступающего на информационный вход первого коммутатора 1, к его первому информационному выходу. При приходе управляющего сигнала на третий управляющий вход первого коммутатора 1 происходит отключение информационного входа первого коммутатора 1 от его первого информационного выхода. При поступлении на первый управляющий вход первого коммутатора 1 управляющего сигнала осуществляется коммутация входного потока, поступающего на информационный вход первого коммутатора 1, к его второму информационному выходу. При приходе управляющего сигнала на четвертый управляющий вход первого коммутатора 1 происходит отключение информационного входа первого коммутатора 1 от его второго информационного выхода.

Первый регистр 2 предназначен для последовательного выделения восьми элементов входного цифрового потока, поступающего на его информационный вход.

Блок сравнения 3 предназначен для определения наличия на его первом-восьмом информационных входах кодовой комбинации 01111110, соответствующей "флагу". В случае получения положительного решения на выходе блока сравнения 3 формируется управляющий сигнал. Тактовая синхронизация работы первого регистра 2 и блока сравнения 3 обеспечивается с помощью Ft.

Блок коррекции 4 предназначен для выявления и удаления бит "прозрачности", включаемых в цифровую последовательность и на передающей станции с целью исключения случайного появления комбинации, соответствующей "флагу". Данная цель достигается путем удаления из Ft тактового импульса, соответствующего биту "прозрачности". Скорректированная Fti, поступающая с выхода блока коррекции 4, обеспечивает тактовую синхронизацию работы первого регистра стратегии поиска 5, второго 6 и третьего 7 регистров, а также второго блока контроля качества канала 10.

Регистр стратегии поиска 5 предназначен для определения момента времени, в течение которого на ячейках третьего регистра 7 находятся биты входного цифрового потока, соответствующие второму и третьему октета в пределах кадра FR или HDLC и обеспечения кадровой синхронизации работы блока дешифрации 8. Регистр стратегии поиска 5 представляет собой шестнадцатиразрядный последовательный регистр в котором при поступлении на его управляющий вход управляющего импульса производится запись 1 в первую ячейку и обнуление содержания других ячеек. Перемещение управляющего импульса, поступившего с блока сравнения 3, осуществляется под воздействием Fti. После прохождения шестнадцати тактовых импульсов Fti управляющий импульс появляется на выходе первого регистра стратегии поиска 5.

Второй регистр 6 предназначен для выработки управляющего импульса на обнуление содержания ячеек третьего регистра 7 после считывания с него информации. Он представляет собой D-триггер, с выхода которого управляющий сигнал поступает на управляющий вход третьего регистра 7.

Третий регистр 7 предназначен для последовательного выделения шестнадцати элементов входного цифрового потока, поступающего на его информационный вход. При наличии управляющего импульса на управляющем входе происходит обнуление содержания ячеек третьего регистра 7.

Блок дешифрации 8 предназначен для подключения к цифровому потоку первого 9 или второго 10 блока контроля качества канала при осуществлении обмена данными по протоколу HDLC или FR соответственно, а также выдачи сигнала в аппаратуру ЗПД местной станции на смену протокола при получении соответствующей команды от удаленной станции.

Первый блок контроля качества канала 9 предназначен для контроля качества канала связи при работе аппаратуры ЗПД по протоколу HDLC и выдачи сигнала в аппаратуру ЗПД местной станции на вхождение в связь по протоколу FR, при заданном качестве канала связи.

Второй блок контроля качества канала 10 предназначен для контроля качества канала связи при работе аппаратуры ЗПД по протоколу FR и выдачи сигнала в аппаратуру ЗПД местной станции на вхождение в связь по протоколу HDLC при приеме кадра "Канал не активен".

Второй коммутатор 11 предназначен для коммутации четырнадцатого, десятого, девятого бита третьего октета входной цифровой последовательности на вход первого блока контроля качества канала 9. При поступлении на первый управляющий вход второго коммутатора 11 управляющего сигнала (работа по протоколу HDLC) осуществляется коммутация входного потока, поступающего на первый, второй и третий информационные входы второго коммутатора 11 соответственно к его первому, второму и третьему выходу. При приходе управляющего сигнала на второй управляющий вход второго коммутатора 11 происходит отключение информационных входов второго коммутатора 11 от его информационных выходов.

Блок дешифрации 8 (фиг. 2) работает следующим образом.

Первый дешифратор 8.1 предназначен для преобразования октетов "SABM" и "DM" в пределах кадра HDLC (фиг. 13), третьего октета канала локального управления (LMI) в пределах кадра FR (фиг. 8,9), поступивших с третьего регистра 7, в информацию о наличии одного из трех сообщений протоколов HDLC или FR. Управляющий сигнал появляется на первом выходе первого дешифратора 8.1 в том случае, если принятая последовательность соответствует сообщению "SABM" (00111111), на втором выходе, если принятая последовательность соответствует сообщению "DM" (00011111), на третьем выходе, если принятая последовательность соответствует каналу LMI (00000001). Срабатывание первого дешифратора 8.1 осуществляется в момент прихода управляющего сигнала с выхода регистра стратегии поиска 5.

Второй дешифратор 8.2 предназначен для идентификации работы аппаратуры ЗПД по протоколу HDLC, путем определения принадлежности второго октета принимаемого кадра сообщению "Адрес" в пределах кадра HDLC (фиг. 12). Управляющий сигнал на выходе второго дешифратора 8.2 появится, если принятая последовательность соответствует сообщению "Адрес" (00000001). Срабатывание второго дешифратора 8.2 осуществляется в момент прихода управляющего сигнала с выхода регистра стратегии поиска 5.

Управляющий сигнал на выходе элемента ИЛИ 8.3 появится в случае управляющего сигнала на его первом или втором входе.

Триггер 8.4 предназначен для идентификации смены протокола аппаратурой ЗПД удаленной станции. Триггер 8.4 первоначально имеет высокий уровень на втором выходе (работа по протоколу FR). При приходе управляющего сигнала на первый вход триггера 8.4, происходит срабатывание последнего, и высокий уровень появится на его первом выходе (команда от удаленной станции на работу аппаратуры ЗПД по протоколу HDLC.). При приходе управляющего сигнала на второй вход триггера 8.4, происходит его срабатывание, и высокий уровень появится на его втором выходе (команда от удаленной станции на работу аппаратуры ЗПД по протоколу FR).

Первый блок контроля качества канала 9 (фиг. 3) работает следующим образом.

Элемент И-НЕ 9.1 исключает из дальнейшего анализа служебные (ненумерованные) кадры HDLC (фиг. 13), не содержащие информации о необходимости повторной передачи кадров.

Коммутатор 9.2 предназначен для коммутации шестого бита третьего октета кадра HDLC на вход триггера 9.3 и элемента исключающее  9.4. При поступлении на управляющий вход коммутатора 9.2 управляющего сигнала осуществляется коммутация шестого бита третьего октета, поступающего на информационный вход коммутатора 9.2 к его выходу.

9.4. При поступлении на управляющий вход коммутатора 9.2 управляющего сигнала осуществляется коммутация шестого бита третьего октета, поступающего на информационный вход коммутатора 9.2 к его выходу.

Триггер 9.3 предназначен для задержки входной цифровой последовательности на один такт. Он представляет собой D- триггер, с первого выхода которого управляющий сигнал поступает на первый вход элемента 9.4. Со второго выхода триггера 9.3 управляющий сигнал поступает на управляющий вход счетчика искаженных кадров 9.5 для обнуления содержания его ячеек после считывания информации со счетчика.

Элемент исключающее  9.4 предназначен для сравнения значения шестого бита третьего октета предыдущего и принимаемого кадра HDLC. При совпадении уровня сигнала с коммутатора 9.2 и триггера 9.3 (запрос от удаленной станции на повторную передачу кадра) на выходе элемента исключающее

9.4 предназначен для сравнения значения шестого бита третьего октета предыдущего и принимаемого кадра HDLC. При совпадении уровня сигнала с коммутатора 9.2 и триггера 9.3 (запрос от удаленной станции на повторную передачу кадра) на выходе элемента исключающее  19.4 появится управляющий сигнал.

19.4 появится управляющий сигнал.

Счетчик искаженных кадров 9.5 предназначен для подсчета числа перезапросов от удаленной станции (количество управляющих сигналов на выходе элемента исключающее  9.4).

9.4).

Счетчик кадров 9.6 предназначен для подсчета общего числа информационных и супервизорных кадров HDLC, т.е. интервала для контроля качества канала связи.

Дешифратор 9.7 предназначен для преобразования информации о количестве единиц на выходах счетчика искаженных кадров 9.5 в информацию о качестве канала связи. Если количество единиц (ошибок) не превысит выбранного порога, то на выходе дешифратора появляется управляющий сигнал в аппаратуру ЗПД местной станции на переключения для работы по протоколу FR. Срабатывание дешифратора 9.7 осуществляется в момент прихода управляющего сигнала со второго выхода триггера 9.3.

Второй блок контроля качества канала 10 (фиг. 4) работает следующим образом.

Первый регистр стратегии поиска 10.1 предназначен для определения момента времени, в течение которого на ячейках второго регистра 10.3 находятся биты входного цифрового потока, соответствующие одиннадцатому октету (фиг. 11, 12) в пределах кадра FR и обеспечения кадровой синхронизации работы дешифратора 10.4. Первый регистр стратегии поиска 10.1 представляет собой шестидесятичетырехразрядный последовательный регистр, в котором при поступлении на его управляющий вход управляющего импульса производится запись 1 в первую ячейку и обнуление содержания других ячеек. Перемещение управляющего импульса, поступившего с блока дешифрации 8, осуществляется под воздействием Fti. После прохождения пятидесяти шести тактовых импульсов Fti управляющий импульс появляется на первом выходе первого регистра стратегии поиска 10.1. После прохождения шестидесяти четырех тактовых импульсов Fti управляющий импульс появляется на втором выходе второго регистра стратегии поиска 10.1.

Первый регистр 10.2 предназначен для выработки управляющего импульса на обнуление содержания ячеек второго регистра 10.3 после считывания с него информации. Он представляет собой D-триггер, с выхода которого управляющий сигнал поступает на управляющий вход второго регистра 10.3.

Второй регистр 10.3 предназначен для последовательного выделения восьми элементов входного цифрового потока, поступающего на его информационный вход. При наличии управляющего импульса на управляющем входе происходит обнуление содержания ячеек второго регистра 10.3.

Дешифратор 10.4 предназначен для преобразования октета "Идентификатор информационного элемента о состоянии канала" и октета, указывающего на то, является данный канал активным или нет (фиг. 8,9). Управляющий сигнал появляется на первом выходе дешифратора 10.4 в том случае, если принятая последовательность соответствует сообщению "канал не активен" (1000-000) (фиг. 9), на втором управляющем выходе, если принятая последовательность соответствует сообщению "Идентификатор информационного элемента о состоянии канала" (01010111) (фиг. 8,9). Срабатывание дешифратора 10.4 осуществляется в момент прихода управляющего сигнала со вторых выходов первого 10.1 или второго 10.5 регистра стратегии поиска.

Второй регистр стратегии поиска 10.5 предназначен для определения момента времени, в течение которого на ячейках второго регистра 10.3 находятся биты входного цифрового потока, соответствующие пятнадцатому октету (фиг. 11, 12) в пределах кадра FR и обеспечения кадровой синхронизации работы дешифратора 10.4. Второй регистр стратегии поиска 10.5 представляет собой тридцатидвухразрядный последовательный регистр в котором при поступлении на его управляющий вход управляющего импульса производится запись 1 в первую ячейку и обнуление содержания других ячеек. Перемещение управляющего импульса, поступившего с дешифратора 10.4, осуществляется под воздействием Fti. После прохождения двадцати четырех тактовых импульсов Fti управляющий импульс появляется на первом выходе второго регистра стратегии поиска 10.5. После прохождения тридцати двух тактовых импульсов Fti управляющий импульс появляется на втором выходе второго регистра стратегии поиска 10.5.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2001 |

|

RU2199148C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ИСКАЖЕНИЯ ИНФОРМАЦИОННОГО ЦИФРОВОГО ПОТОКА | 2004 |

|

RU2273045C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2100839C1 |

| УСТРОЙСТВО МОНИТОРИНГА БЕЗОПАСНОСТИ АВТОМАТИЗИРОВАННЫХ СИСТЕМ | 2004 |

|

RU2270478C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2001 |

|

RU2207729C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

Изобретение относится к электросвязи и может быть использовано для поиска информации и идентификации, применяемых в цифровых системах связи и, в частности, в сетях передачи данных (СПД) коммуникационных протоколов Frame Relay (FR) и High-Level Data Link Control (HDLC), стандартизованных Международным союзом электросвязи, а также контроля качества канала связи и выбора для работы в СПД, на основе контроля, протокола FR или HDLC. Техническим результатом является разработка устройства поиска информации (УПИ), обеспечивающего возможность его применения в более широкой области, в частности, для распознавания коммуникационных протоколов FR и HDLC, контроля качества обмена данными, осуществляемого по протоколу FR или HDLC, а также для идентификации смены протокола удаленной станцией. Для этого заявленное устройство содержит коммутаторы, регистры, блок сравнения, блок коррекции, регистр стратегии поиска, блок дешифрации, блоки контроля качества канала. 3 з.п. ф-лы, 13 ил.

управляющий вход счетчика искаженных кадров подключен ко второму выходу триггера, первый выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ

управляющий вход счетчика искаженных кадров подключен ко второму выходу триггера, первый выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ  второй вход которого подключен к выходу коммутатора и первому информационному входу триггера, информационный вход коммутатора является первым входом блока, первый и второй входы элементы И-НЕ являются соответственно вторым и третьим входами блока, выход дешифратора является информационным выходом блока.

второй вход которого подключен к выходу коммутатора и первому информационному входу триггера, информационный вход коммутатора является первым входом блока, первый и второй входы элементы И-НЕ являются соответственно вторым и третьим входами блока, выход дешифратора является информационным выходом блока.

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2094845C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| US 4611298 A, 09.09.1986. | |||

Авторы

Даты

2002-02-10—Публикация

2000-12-25—Подача