Изобретение относится к технике связи и вычислительной технике и может быть использовано в системах передачи дискретной информации по каналам низкого качества, в частности для телеметрии.

Известны устройства для защиты от ошибок, в которых повышение достоверности передаваемой информации достигается за счет многократных повторений сообщений, см., например, а.с. N 677123, N 1345357. В известных устройствах использовано мажоритарное декодирование двоичных кодов при трехкратном повторении сообщений.

Недостатком известных устройств является относительно высокая вероятность ошибочного восстановления символа (комбинации), что в ряде случаев крайне не желательно.

Наиболее близким техническим решением к заявляемому является "Устройство защиты от ошибок ", по А.с. N 1644392, МПК H 03 M 13/00, опубликованное в Б. И. N 15 от 23.04.91 г.

Известное устройство защиты от ошибок содержит последовательно соединенные первый и второй регистры сдвига, параллельные выходы которых подключены к информационным входам блока коммутации. Выходы блока коммутации подключены к информационным входам блока декодирования, информационный выход которого является выходом устройства. Известное устройство содержит также делитель частоты и счетчик импульсов, счетные входы которых объединены и подключены к прямому выходу ошибки блока декодирования. Кроме того, имеется логический элемент ИЛИ и блок постоянной памяти, который служит для управления работой блока коммутации и подключен входами к счетчику импульсов, а выходами - к управляющим входам блока коммутации. Входы логического элемента ИЛИ подключены к выходу делителя частоты и к инверсному выходу блока декодирования, выход элемента ИЛИ соединен с входами сброса регистров сдвига, делителя частоты и счетчика импульсов. Работой устройства управляют тактовые импульсы, воздействующие на регистры сдвига и блок декодирования.

Известное устройство имеет недостатки: высокую вероятность появления ошибки декодирования, особенно при ограничении времени, отводимого для него, и узкую область применения устройства.

Первый недостаток обусловлен тем, что для получения нужной вероятности правильного декодирования необходимо на приеме обработать большое число повторов комбинации. Например, при вероятности ошибки в канале 5•10-2 необходимо на приеме обработать 6 повторов комбинации, при меньшем числе обрабатываемых повторов комбинации возрастает вероятность ошибочного декодирования. В известном устройстве в процессе декодирования последовательно предпринимаются попытки декодировать первоначально поступающие на прием комбинации, а затем комбинации, формируемые путем суперпозиции сегментов из разных повторений комбинации. Декодирование на основе суперпозиции сегментов разных повторов требует синхронного положения тактовых импульсов и циклового фазирования. Известное устройство не решает задачи синхронизации, предполагается, что это делается вне его, что сужает область применения устройства.

Целью изобретения является создание устройства защиты от ошибок, обеспечивающего малую вероятности ошибки декодирования, при ограниченном времени декодирования, а также расширение области применения устройства за счет реализации в нем цикловой и тактовой синхронизации.

Поставленная цель достигается тем, что в известное устройство защиты от ошибок, содержащее регистр сдвига, информационный и тактовый входы которого являются соответственно информационным и тактовым входами устройства, делитель частоты, вход которого подключен к тактовому входу устройства и тактовому входу блока управления коммутацией, первый управляющий вход которого подключен к выходу первого счетчика импульсов, а выход - к управляющему входу блока коммутации, r информационных входов которого подключены к соответствующим r выходам первой группы информационных выходов регистра сдвига (где r ≥ 5), а тактовый вход соединен с тактовым входом устройства, дополнительно введены логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенный выходом к входу "Совпадение" блока управления счетом, второй и третий счетчики импульсов, выходы которых соединены соответственно с вторым и третьим управляющими входами блока управления коммутацией, дешифратор ключа, подключенный s входами элементов ключа к соответствующим s выходам второй группы информационных выходов регистра сдвига (где s=1, 2, 3, ...), выход дешифратора ключа соединен с четвертым управляющим входом блока управления коммутацией, пятый и шестой входы которого объединены соответственно с седьмым и восьмым входами блока управления счетом и подключены к первому и второму выходам делителя частоты, первый, второй и третий выходы блока управления счетом соединены со счетными входами соответственно первого, второго и третьего счетчиков импульсов, к входам сброса каждого из которых подключены соответственно четвертый, пятый и шестой выходы блока управления счетом, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом устройства, а второй вход - с последовательным выходом регистра сдвига, r выходов блока коммутации являются информационными выходами устройства.

Существо предложения по уменьшению вероятности ошибки декодирования основывается на обязательном выполнении следующих условий: безошибочной дешифрации ключевой части комбинации и проверки правильности приема каждого элемента в комбинациях, при уменьшенном (по сравнению с прототипом) числе обрабатываемых повторов кодовой комбинации. В случае выявления хотя бы одной ошибки в обрабатываемых комбинациях информация не выдается получателю. Такое решение технической задачи целесообразно для применений, при которых прием ошибочной комбинации опаснее, чем пропуск ее, как это имеет место, например, при приеме информации от измерителя глубины фарватера на движущемся объекте.

Существо предложения по расширению области применения устройства в сравнении с прототипом основано на совместном выполнении функций фазирования и декодирования принимаемых сообщений.

Формируемые на передающей стороне кодовые комбинации длиной n элементов содержат s бит, образующих ключевую комбинацию, и r бит (r = n-s) для передачи основной информации. Передача каждой комбинации повторяется m раз.

На приемной стороне после демодуляции принимаемый сигнал поступает на вход регистра сдвига, число разрядов которого (3n второе превышает длину кодовой комбинации n, а тактовая частота сдвигов в 3 раза выше информационной скорости. В результате в регистре сдвига всегда хранится три копии последних n бит информации, поступивших на устройство, причем копии сдвинуты друг относительно друга на 1/3 длительности информационного элемента. Сигнал на последовательном выходе регистра сдвига задержан на длину кодовой комбинации, поэтому входной сигнал является повтором сигнала на выходе регистра сдвига.

Каждая из трех копий сигнала, поступающая с последовательного выхода регистра, обрабатывается отдельно путем поэлементного сопоставления с входным сигналом и подсчета числа совпадений элементов во входном сообщении и исследуемой копии. Объемы счетчиков совпадений равны и выбраны с учетом длины кодовой комбинации n и задаваемого числа принятых повторов комбинации.

При несовпадении на каком-либо сдвигающем такте элемента входного сигнала с соответствующим элементом копии задержанного сигнала происходит сбрасывание в нулевое положение того из счетчиков, который участвует в обработке соответствующей копии. При наличии на входе устройства помех и возможных краевых искажениях демодулированного сигнала с наибольшей вероятностью быстрее будет заполняться счетчик, подсчитывающий совпадения входного сигнала с той из трех копий, положение элементов которой в наибольшей степени совпадают с элементами входного сигнала.

Заполнение объема какого-либо из счетчиков является выполнением одного из условий для выдачи информации получателю. Другим условием является дешифрация ключевой комбинации. Если выполнены оба условия, то соответствующая кодовая комбинация пропускается получателю. Таким образом, в заявляемом устройстве одновременно с декодированием кодовой комбинации решается задача эквивалентная установлению тактового синхронизма, а также циклового фазирования.

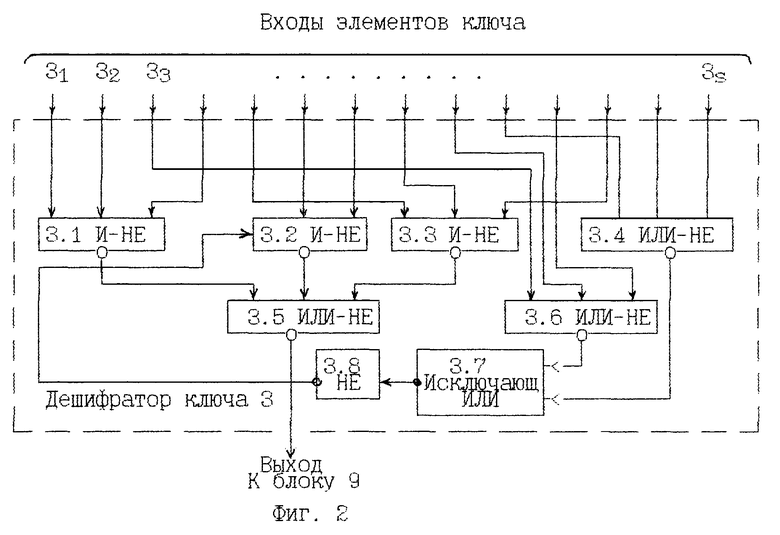

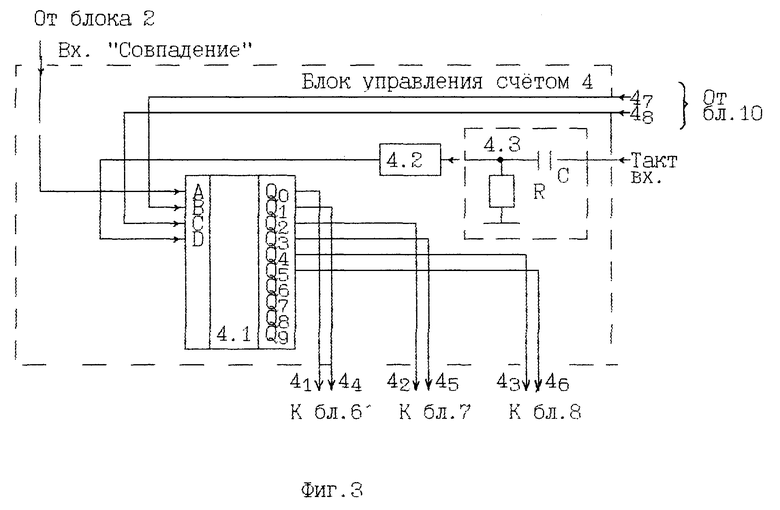

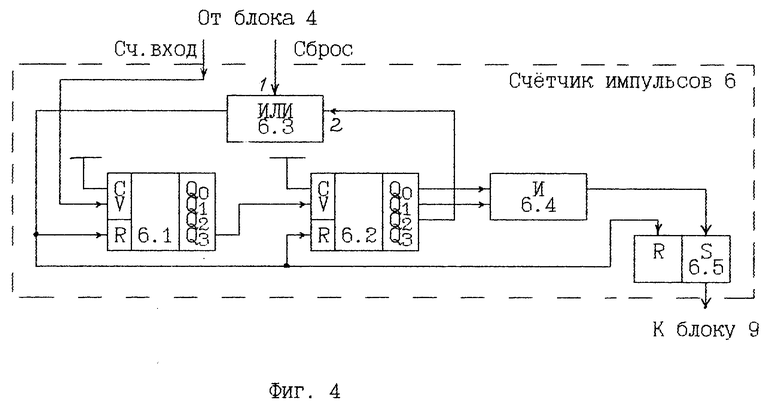

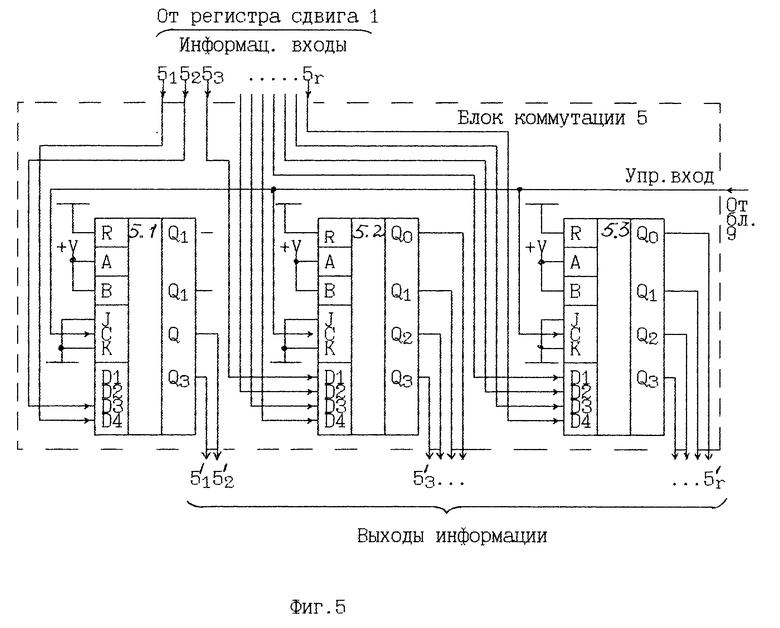

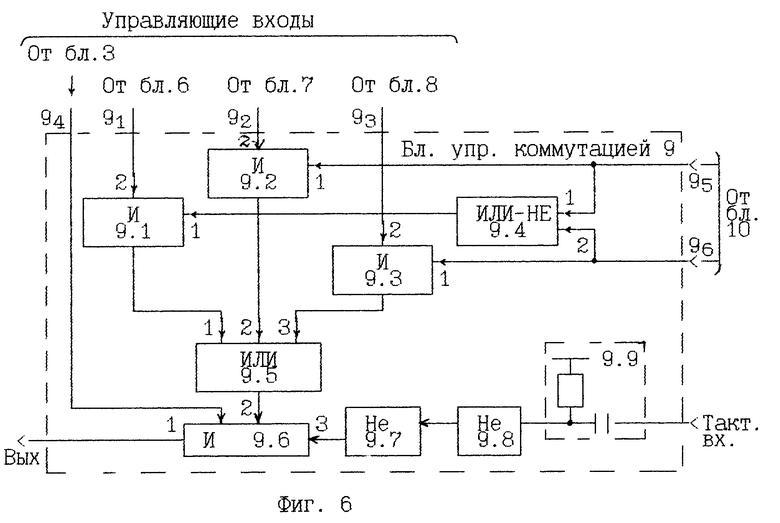

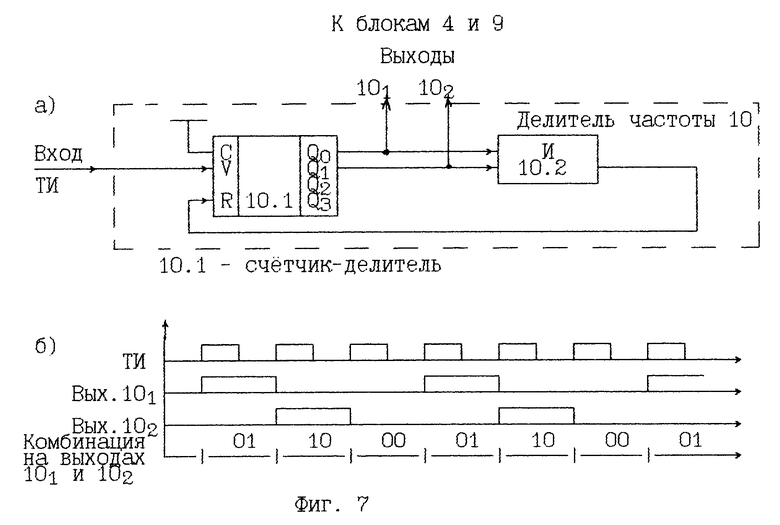

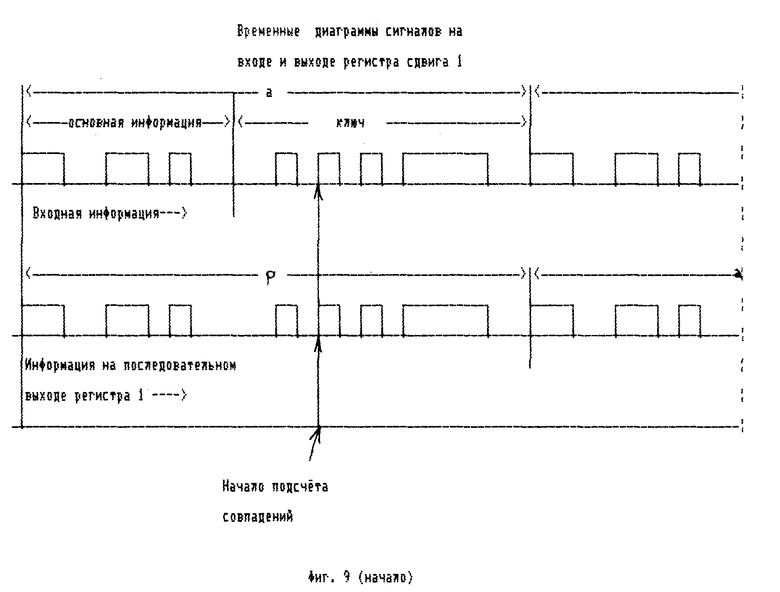

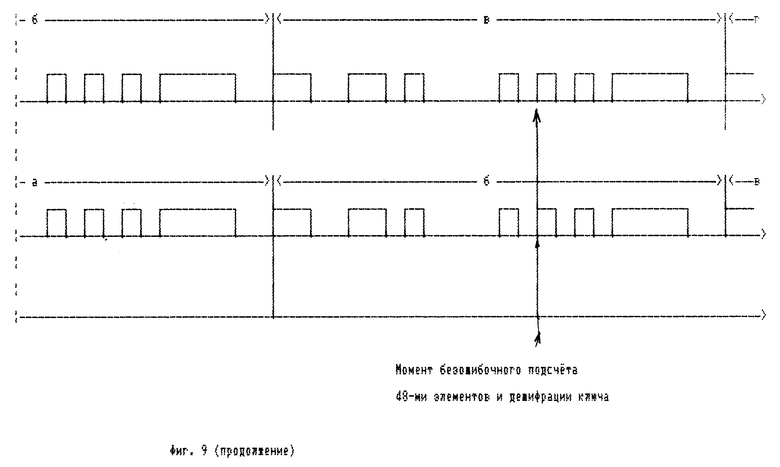

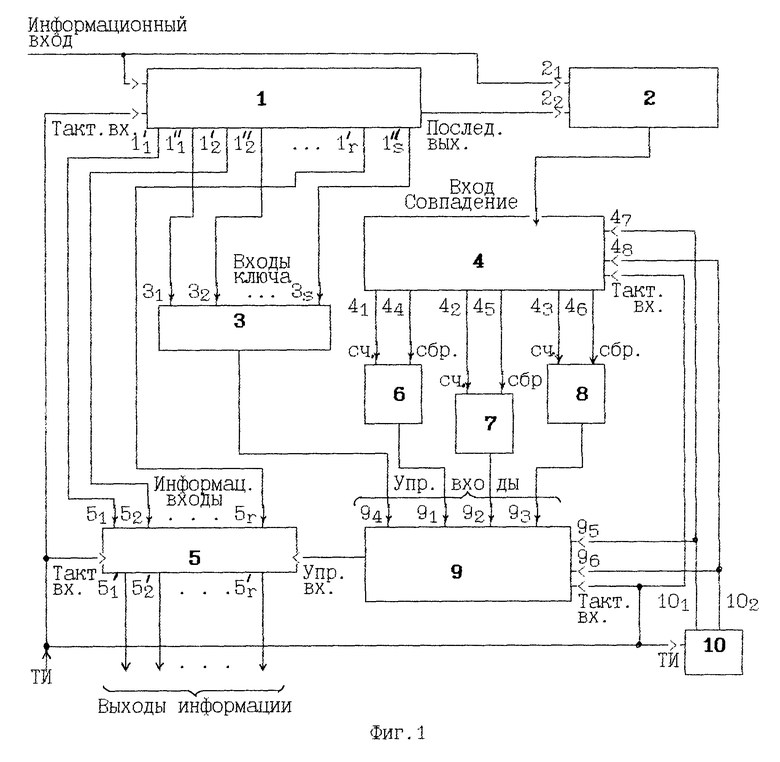

Заявляемое устройство поясняется следующим чертежами, на которых представлены на фиг. 1 - устройство защиты от ошибок; на фиг. 2 - дешифратор ключа 3; на фиг. 3 - блок управления счетом 4; на фиг. 4 - счетчик импульсов 6, (по схеме на фиг. 4 выполнены счетчики импульсов: первый 6, второй 7 и третий 8); на фиг. 5 - блок коммутации 5; на фиг. 6 - блок управления коммутацией 9; на фиг. 7 - делитель частоты 10; на фиг. 8 и 9 - временные диаграммы.

Устройство защиты от ошибок, показанное на фиг. 1, состоит из регистра сдвига 1, логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, дешифратора ключа 3, блока управления счетом 4, блока коммутации 5, первого 6, второго 7 и третьего 8 счетчиков импульсов, блока управления коммутацией 9, делителя частоты 10. Информационный вход устройства соединен с информационным входом регистра сдвига 1 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2. Информационные выходы устройства являются выходами  блока коммутации 5. Тактовый вход устройства соединен с тактовым выходом регистра сдвига 1, тактовым входом блока коммутации 5, входом ТИ делителя частоты 10 и тактовыми входами блока управления счетом 4 и блока управления коммутацией 9. Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 соединен с последовательным выходом регистра сдвига 1, а выход соединен с входом "Совпадение" блока управления счетом 4. Седьмой вход 47 блока управления счетом 4 объединен с пятым входом 95 блока управления коммутацией 9 и подключен к первому выходу 101 делителя частоты 10. Соответственно восьмой вход 48 блока управления счетом 4 объединен с шестым входом 96 блока управления коммутацией 9 и подключен ко второму входу 102 делителя частоты 10. Первый 41, второй 42 и третий 43 выходы блока управления счетом 4 подключены к счетным входам соответственно первого 6, второго 7 и третьего 8 счетчиков импульсов. Четвертый 44, пятый 45 и шестой 46 выходы блока управления счетом 4 подключены к входам "сброс" первого 6, второго 7 и третьего 8 счетчиков импульсов. Выходы счетчиков импульсов 6, 7, и 8 подключены к первому 91, второму 92 и третьему 93 управляющим входам блока управления коммутацией 9 соответственно. Первая группа r информационных выходов

блока коммутации 5. Тактовый вход устройства соединен с тактовым выходом регистра сдвига 1, тактовым входом блока коммутации 5, входом ТИ делителя частоты 10 и тактовыми входами блока управления счетом 4 и блока управления коммутацией 9. Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 соединен с последовательным выходом регистра сдвига 1, а выход соединен с входом "Совпадение" блока управления счетом 4. Седьмой вход 47 блока управления счетом 4 объединен с пятым входом 95 блока управления коммутацией 9 и подключен к первому выходу 101 делителя частоты 10. Соответственно восьмой вход 48 блока управления счетом 4 объединен с шестым входом 96 блока управления коммутацией 9 и подключен ко второму входу 102 делителя частоты 10. Первый 41, второй 42 и третий 43 выходы блока управления счетом 4 подключены к счетным входам соответственно первого 6, второго 7 и третьего 8 счетчиков импульсов. Четвертый 44, пятый 45 и шестой 46 выходы блока управления счетом 4 подключены к входам "сброс" первого 6, второго 7 и третьего 8 счетчиков импульсов. Выходы счетчиков импульсов 6, 7, и 8 подключены к первому 91, второму 92 и третьему 93 управляющим входам блока управления коммутацией 9 соответственно. Первая группа r информационных выходов  регистра сдвига 1 соединена с r информационными входами 51 ... 5r блока коммутации 5, вторая группа s информационных выходов

регистра сдвига 1 соединена с r информационными входами 51 ... 5r блока коммутации 5, вторая группа s информационных выходов  регистра сдвига 1 соединена с s входами элементов ключа 31 ... 3s дешифратора 3. Выход дешифратора 3 подключен к четвертому управляющему входу 94 блока управления коммутацией 9, выход которого соединен с управляющим входом блока коммутации 5.

регистра сдвига 1 соединена с s входами элементов ключа 31 ... 3s дешифратора 3. Выход дешифратора 3 подключен к четвертому управляющему входу 94 блока управления коммутацией 9, выход которого соединен с управляющим входом блока коммутации 5.

Регистр сдвига 1 выполнен по известной схеме, описанной, например, в книге В. Л. Шило "Популярные цифровые микросхемы": Справочник. -М.: Радио и связь, 1981 - 352 с., на стр. 248-250. В этой же книге на стр. 216 описаны логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

На фиг. 2 показана схема дешифратора ключа 3, предназначенного для дешифрации ключевой комбинации. Схема содержит три логических элемента И-НЕ 3.1, 3.2 и 3.3, три элемента ИЛИ-НЕ 3.4, 3.5 и 3.6, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3.7 и инвертор 3.8. На входы 31 ... 3s дешифратора ключа 3 поступают сигналы со второй группы информационных выходов 11 ... 1s регистра сдвига 1, на которых при синхронном положении обрабатываемой копии присутствуют элементы ключевой комбинации.

Сигнал на выходе дешифратора 3 формируется при безошибочной дешифрации всех s элементов ключевой комбинации.

Все логические элементы, образующие схему дешифратора 3, известны и описаны, например, в книге В. Л. Шило "Популярные цифровые микросхемы": Справочник. -М. : Радио и связь, 1981 - 352 с. (на стр. 204 - 208 описаны схемы И-НЕ, ИЛИ-НЕ, на стр. 216 - схемы ИСКЛЮЧАЮЩЕЕ ИЛИ, на стр. 212 - инверторы).

На фиг. 3 показана схема блока управления счетом 4, предназначенного для управления работой счетчиков импульсов: первого - 6, второго - 7 и третьего - 8. Блок управления счетом 4 содержит дешифратор 4.1, инвертор 4.2 и дифференцирующую цепь 4.3.

На тактовый вход блока управления счетом 4 поступают тактовые импульсы с тактового входа устройства. На седьмой 47 и восьмой 48 входы блока 4 поступают сигналы с первого 101 и второго 102 выходов делителя частоты 10 соответственно, на вход "Совпадение" поступает сигнал с выхода логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2.

Через первый 41, второй 42 и третий 43 выходы блока управления счетом 4 поступают счетные импульсы к счетным входам первого 6, второго 7 и третьего 8 счетчиков импульсов соответственно. Через четвертый 44, пятый 45 и шестой 46 выходы блока 4 поступают импульсы для сброса счетчиков 6, 7 и 8 соответственно.

Тактовый вход блока 4 через дифференцирующую цепь 4.3 подключен к входу инвертора 4.2 выход которого соединен с входом D дешифратора 4.1 (старший разряд дешифратора 4.1). Седьмой 47 и восьмой 48 входы блока управления счетом 4 соединены с входами B и C дешифратора 4.1 (средние разряды), вход "Совпадение" соединен с входом A дешифратора 4.1 (младший разряд). Дешифратор 4.1 выполняет преобразование четырехразрядного двоичного кода, поступающего на входы, в октальный код.

Первый 41 и четвертый 44 выходы блока управления счетом 4 подключены к выходам Q0, Q1, дешифратора 4.1, на которых формируются младшие разряды выходного октального кода. Второй 42 и пятый 45 выходы блока 4 подключены к выходам Q2, Q3 дешифратора 4.1 (средние разряды выходного октального кода), и третий 43 и шестой 46 выходы блока 4 - к выходам Q4, Q5 (старшие разряды выходного кода).

Дешифратор 4.1 известен, описан, например, в книге В.Л.Шило "Популярные цифровые микросхемы": Справочник. -М.: Радио и связь, 1981 - 352 с. на стр. 261-263. В этой же книге описаны инверторы на стр. 212.

Схемы дифференцирующих цепей известны и описаны, см., например, книгу И. С.Гоноровского "Радиотехнические цепи и сигналы" -М.: Советское радио, 1971, -671 с, параграф 6.5 стр. 215-216.

На фиг. 4 показана схема первого счетчика импульсов 6, по такой же схеме выполнены второй счетчик импульсов 7 и третий счетчик - 8. Каждый счетчик импульсов предназначен для подсчета безошибочно принятых элементов обрабатываемых копий сигнала.

Счетчик импульсов содержит счетчики-делители 6.1 и 6.2, логический элемент И 6.4 и RS - триггер 6.5. Счетный вход счетчика импульсов 6 соединен с тактовым входом V счетчика-делителя 6.1, выход "Сброс" соединен с первым входом логического элемента ИЛИ 6.3. Выход счетчика импульсов 6 является выходом RS-триггера 6.5. Выход элемента ИЛИ 6.3 подключен к установочным входам R счетчиков-делителей 6.1 и 6.2, а также RS-триггера 6.5. Входы C счетчиков-делителей 6.1 и 6.2, которые задают фронт срабатывания, заземлены. Выход старшего разряда Q3 счетчика-делителя 6.1 соединен с тактовым входом V счетчика-делителя 6.2. Выходы двух младших разрядов Q0 и Q1 счетчика-делителя 6.2 подключены к выходам элемента И 6.4, выход которого соединен с выходом S RS-триггера 6.5. Выход среднего разряда Q2 счетчика-делителя 6.2 подключен к второму входу элемента ИЛИ 6.3.

Все элементы, на которых выполнен первый счетчик импульсов 6 известны, описаны в уже упомянутой книге В.Л.Шило "Популярные цифровые микросхемы", на стр. 241 см. счетчика (рис. 2.42) и таблицу на стр. 219 - состояния счетчика; на стр. 230 см. RS-триггер, на стр. 204-208 - логические элементы ИЛИ, И.

На фиг. 5 показана схема блока коммутации 5, предназначенного для выдачи принятой кодовой комбинации получателю. Схема блока коммутации 5 выполнена на основе последовательно-параллельного регистра. На входы 51 ... 5r блока коммутации 5 поступают сигналы с r выходов первой группы информационных выходов  регистра сдвига 1, входы 51 ... 5r блока коммутации подключены к D - входам регистров 5.1, 5.2, 5.3. Управляющий вход блока коммутации 5, на который поступает сигнал от блока управления коммутацией 9, подключен к тактовым входам C регистров 5.1, 5.2, 5.3. Выходы Q регистров 5.1, 5.2, 5.3 образуют r выходов

регистра сдвига 1, входы 51 ... 5r блока коммутации подключены к D - входам регистров 5.1, 5.2, 5.3. Управляющий вход блока коммутации 5, на который поступает сигнал от блока управления коммутацией 9, подключен к тактовым входам C регистров 5.1, 5.2, 5.3. Выходы Q регистров 5.1, 5.2, 5.3 образуют r выходов  блока коммутации 5.

блока коммутации 5.

Последовательно-параллельные регистры известны, описаны, см., например, упомянутую книгу В.Л.Шило на стр. 254-255.

На фиг. 6 изображен блок управления коммутацией 9, предназначенный для формирования управляющих воздействий для блока коммутации 5. Блок 9 содержит логические элементы И 9.1, 9.2, 9.3, 9.6, ИЛИ 9.5, ИЛИ-НЕ 9.4, инверторы 9.7, 9.8 и дифференцирующую цепочку 9.9.

На тактовый вход блока 9 поступают тактовые импульсы с тактового входа устройства. На первый управляющий вход 91 блока 9 поступает сигнал с выхода первого счетчика импульсов 6, на второй управляющий вход 92 поступает сигнал с выхода второго счетчика 7, на третий управляющий вход 93 - с выхода третьего счетчика 8, а на четвертый управляющий вход 94 поступает сигнал с выхода дешифратора 3. На пятый 95 и шестой 96 входы блока управления коммутацией 9 поступают сигналы с первого 101 и второго 102 выходом делителя частоты 10 соответственно. Выход блока управления коммутацией 9 является выходом логического элемента И 9.6.

Тактовый вход блока управления коммутацией 9 через дифференцирующую цепь 9.9 и два последовательно соединенных инвертора 9.7, 9.8 подключен к третьему входу элемента И 9.6. Пятый вход 95 блока 9 соединен с первыми входами логического элемента И 9.2 и элемента ИЛИ - НЕ 9.4, шестой вход 96 соединен с первым входом элемента И 9.3 и вторым входом элемента ИЛИ - НЕ 9.4. Первый 91, второй 92 и третий 93 управляющие входы блока 9 соединены с вторыми входами логических элементов И 9.1, 9.2 и 9.3 соответственно. Четвертый управляющий вход 94 соединен с первым входом элемента И 9.6. Выходы элементов И 9.1, 9.2 и 9.3 через логический элемент ИЛИ 9.5 соединены с вторым входом элемента И 9.6, выход которого является выходом блока управления коммутацией 9.

На фиг. 7а) показана схема делителя частоты 10, построенного по схеме счетчика по модулю 3, который содержит счетчик-делитель 10.1 и логический элемент И 10.2. На вход делителя частоты 10 поступают тактовые импульсы, на выходах 101 и 102 делителя частоты 10 формируются последовательно двухразрядные комбинации 00, 01, 10 (см. временные диаграммы на фиг. 7б)). Счетчик-делитель 10.1 и элемент И 10.2 описаны в упоминавшейся уже книге В.Л.Шило на стр. 241-242 и 204-208 соответственно.

Вход делителя частоты 10 соединен с тактовым входом V счетчика-делителя 10.1, выход C которого заземлен. Выход делителя 10 являются выходами Q0 и Q1 счетчика-делителя 10.1, и они соединены также с входами элемента И 10.2, выход которого подключен к входу сброса R счетчика-делителя 10.1.

На фиг. 8 показана временная диаграмма кодовой комбинации, на фиг. 9 - временные диаграммы на входе устройства защиты от ошибок (т.е. на входе регистра сдвига 1) и на последовательном выходе регистра сдвига 1.

Заявляемое устройство работает следующим образом. Для передачи информации использованы кодовые комбинации, структура которых показана на фиг. 8. Длина кодовой комбинации n элементов (при реализации устройства n=24), s из этих элементов (s= 14) используются в качестве ключевой части, r элементов (r= n-s= 10) использовано для передачи основной информации. При этом сначала передается 10 элементов ключевой части, затем - 10 элементов основной информации и после этого - еще 4 элемента оставшейся ключевой части.

Цикловое фазирование и тактовая синхронизация устанавливаются в процессе декодирования. Выдача сообщения получателю осуществляется только при безошибочном приеме установленного числа повторов сообщения и одновременной правильной дешифрации всей ключевой части кодовой комбинации, как в начальной части комбинации, так и в ее конце, что возможно только при правильном фазовом положении. Структура кодовой комбинации, при которой ключевая часть передается частично перед основной информацией, а частично вслед за ней, повышает вероятность правильного приема основной информации в заявляемом устройстве.

Входной сигнал поступает на информационный вход регистра сдвига 1, длина которого 72 разряда (3 • n), что второе превышает длину кодовой комбинации (24 разряда). Тактовые импульсы, продвигающие информацию по регистру сдвига 1, имеют частоту, в 3 раза превышающую скорость передачи информации. В результате в регистре сдвига 1 всегда хранится 3 копии последних 24-х бит информации, а сигнал на последовательном выходе регистра 1 задержан относительно входного на длительность кодовой комбинации. (См. временные диаграммы на фиг. 9).

Входной сигнал и сигнал с последовательного выхода регистра сдвига 1, т. е. незадержанный и задержанный сигналы, поступают соответственно на 1-й и 2-й входы логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2. При совпадении сигналов на входе (обе "единицы" или оба "нуля") на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 вырабатывается сигнал логического нуля, в противном случае вырабатывается логическая единица.

Выходной сигнал логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 поступает через вход "Совпадение" в блок управления счетом 4, а в нем - на вход младшего разряда дешифратора 4.1 (вход A дешифратора 4.1 на фиг. 3, где изображена схема блока управления счетом 4). На вход старшего разряда D дешифратора 4.1 поступает сигнал, сформированный по переднему фронту тактового импульса (с помощью дифференцирующей цепи 4.3 и инвертора 4.2). На входы средних двух разрядов дешифратора 4.1 поступают сигналы с выходов делителя частоты 10, через седьмой 47 и восьмой 48 входы блока управления счетом 4.

Сигналы на выходах делителя частоты 10 представляют собой результаты деления частоты входных тактовых импульсов на три и являются повторяющимися двухразрядными комбинациями 00, 01, 10 и опять 00, 01, 10 и т.д. (см. диаграмму напряжения на фиг. 7б)). Совокупность сигналов, поступающих с выхода логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, с выходов делителя частоты 10, а также продифференцированные передние фронты тактовых импульсов, формирует управляющее входное кодовое слово для дешифратора 4.1 в блоке управления счетом 4. Входные кодовые слова сменяются с частотой следования тактовых импульсов. При совпадении элементов входного сигнала с элементами копии, поступающей с последовательного выхода регистра сдвига 1, управляющие слова в младшем разряде имеют нуль: 0000, 0010, 0100, 0010, 0100, 0000 и т.д.

Каждому управляющему слову на входе дешифратора 4.1 соответствует определенный выходной сигнал дешифратора 4.1. Таблица состояний дешифратора, использованного в блоке управления счетом 4, показана на стр. 262 в книге В. Л. Шило "Популярные цифровые микросхемы": Справочник. -М.: Радио и связь, 1987.

При совпадении элементов входного сигнала и элементов обрабатываемой копии с выхода регистра сдвига 1 в дешифраторе 4.1 формируется сигнал, который используется затем как счетный импульс в соответствующем счетчике импульсов 6, 7 или 8.

Например, при управляющем слове 0000 на входах дешифратора 4.1 вырабатывается импульс на выходе Q0 дешифратора 4.1, этот импульс через первый выход 41 блока управления счетом 4 поступает на счетный вход первого счетчика импульсов 6. При управляющем слове 0010 импульс формируется на выходе Q2 дешифратора 4.1 и через второй выход 42 блока управления счетом 4 поступает на счетный вход второго счетчика импульсов 7. При управляющем слове 0100 вырабатывается импульс на выходе Q4, который поступает через третий выход 43 блока управления счетом 4 на счетный вход третьего счетчика импульсов 8.

Если на каком-то из тактовых импульсов, продвигающих информацию по регистру сдвига 1, элемент входного сигнала и элемент обрабатываемой копии не совпадают, то на выходе логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2 вырабатывается логическая единица, которая в комбинации слова, управляющего дешифратором 4.1, стоит в младшем разряде. При этом в дешифраторе 4.1 будут формироваться сигналы на тех выходах, которые через четвертый 44, пятый 45 и шестой 46 выходы блока управления счетом 4 подключены к входам сброса соответственно первого 6, второго 7 и третьего 8 счетчиков импульсов.

Например, если при подобном несовпадении элементов входного сигнала и копии формируется управляющее слово 0001, то сигнал в дешифраторе 4.1 вырабатывается на выходе Q1, который через четвертый выход 44 блока 4 подключен к выходу сброса первого счетчика импульсов 6. При управляющей комбинации 0011 сигнал вырабатывается на выходе Q3 и через пятый 45 выход блока 4 воздействует на сброс второго счетчика импульсов 7. При управляющей комбинации 0101 сигнал формируется на выходе Q5 дешифратора 4.1 и через шестой 46 выход блока управления счетом 4 поступает на вход сброса третьего счетчика импульсов 8.

Для уверенного приема сообщения в заявляемом устройстве требуется принять без ошибок три повтора кодовой комбинации. Счетчик импульсов, который первым зарегистрирует этот факт, заполнится при этом до 48. Очевидно, что число повторов комбинации m на передаче должно быть в таком случае более трех. Число возможных повторов кодовой комбинации при передаче, например, телеметрической информации зависит от разнообразных факторов: от величины отрезка времени, которое может быть выделено для одного замера и передачи результатов замера, от свойств канала, используемого для передачи информации, от скорости перемещения, если объект движется, и т.д.

Итак, если в процессе обработки принимаемого сигнала подряд произошло 48 совпадений элементов входной информации с элементами одной из 3-х копий, на выходе счетчика импульсов, подсчитывающего совпадения при обработке этой копии, появится выходной сигнал, который формируется (см. схему счетчика импульсов на фиг. 4) с помощью логического элемента И 6.4 и RS-триггера 6.5.

Сигнал с выхода любого из счетчиков импульсов 6, 7 или 8, поступает в блок управления коммутацией 9 (см. фиг. 6) через первый 91, второй 92 и третий 93 управляющие входы соответственно. В блоке управления коммутацией 9 сигнал с выхода первого счетчика импульсов 6 поступает на второй вход логического элемента И 9.1 (см. схему блока управления коммутацией 9 на фиг. 6), сигнал от второго счетчика импульсов 7 поступает на второй вход логического элемента И 9.2, сигнал третьего счетчика 8 - на второй вход И 9.3. На первые входы логических элементов И 9.2 и 9.3 поступают сигналы с выходов делителя частоты 10 через пятый 95 и шестой 96 входы блока управления коммутацией 9.

Элемент И 9.1 открыт только при наличии на пятом 95 и шестом 96 входах блока управления коммутацией 9 комбинации 00 за счет сигнала, формируемого на выходе логического элемента ИЛИ-НЕ 9.4. При входной комбинации 01 (на пятом 95 и шестом 96 входах) открыт элемент И 9.2, при комбинации 10 - элемент И 9.3.

Выходные сигналы логических элементов И 9.1, 9.2 и 9.3 поступают через элемент ИЛИ 9.5, на второй вход логического элемента И 9.6, на третий вход которого поступают импульсы, сформированные по переднему фронту тактовых импульсов (см. на фиг. 6 дифференцирующую цепь 9.9 и инверторы 9.7 и 9.8). На первый вход элемента И 9.6 поступает сигнал от дешифратора ключа 3 (через четвертый управляющий вход 94 блока управления коммутацией 9).

Таким образом, сигнал на выходе блока управления коммутацией 9 формируется при условии, что произошло подряд 48 совпадений входного и задержанного сигналов, правильно расшифрована ключевая часть кодовой комбинации и, кроме того, действует передний фронт тактового импульса. В результате на выходе блока управления коммутацией 9 вырабатывается управляющий сигнал для блока коммутации 5.

В блоке коммутации 5 (см. схему 5 на фиг. 5), по управляющему сигналу от блока управления коммутацией 9 информационные разряды кодовой комбинации, поступающие через входы 51 ... 5r блока на информационные D-входы регистров 5.1, 5.2 и 5.3 переносятся на выходы этих регистров. Выходы регистров 5.1, 5.2 и 5.3 образуют r выходов  блока коммутации 5, являющихся выходами всего устройства.

блока коммутации 5, являющихся выходами всего устройства.

Возможны ситуации, когда при заполнении до 48 какого-либо из счетчиков импульсов (6, 7 и 8), дешифратор ключа 3 не сработал, скажем, из-за отсутствия циклового совпадения тогда дешифрация ключа может произойти несколько позднее по мере последующего продвижения информации по регистру сдвига 1. При этом происходит дальнейшее заполнение счетчиков. Выходной сигнал заполнившегося ранее до 48 счетчика импульсов будет сохраняться, пока счетчик не заполнится до числа 64. Если счетчик импульсов заполняется до 64-х, в данном счетчике импульсов на выходе Q2 счетчика-делителя 6.2 (см. фиг. 4) появится сигнал, который через логический элемент ИЛИ 6.3 воздействует на сброс счетчика, заполнившегося до 64.

Малая вероятность ошибочного декодирования достигается за счет обязательно выполнения одновременно двух требований: безошибочного приема кодовой комбинации при условии безошибочной дешифрации ключевой комбинации.

Вероятность правильного декодирования кодовой комбинации с N-го повтора определяется выражением

PПД = 1 - (1 - PПД1)N,

где PПД1 - вероятность правильного декодирования с первого повтора

PПД1= (1 - P

где n - длина кодовой комбинации;

P0 - вероятность ошибки в канале связи.

При P0 = 5 • 10-2, длине кодовой комбинации n = 24 и приеме с третьего повтора получим вероятность правильного декодирования не менее 0,999, что существенно выше, чем в прототипе.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1996 |

|

RU2115952C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1997 |

|

RU2115246C1 |

| УСТРОЙСТВО СТАТИСТИЧЕСКОГО УПЛОТНЕНИЯ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1997 |

|

RU2110897C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1995 |

|

RU2100839C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1995 |

|

RU2099889C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

Изобретение относится к технике связи и вычислительной технике и может быть использовано в системах передачи дискретной информации по каналам низкого качества. Технический результат - обеспечение малой вероятности ошибки декодирования, при ограниченном времени декодирования, расширение области применения устройства за счет обеспечения цикловой и тактовой синхронизации. Сущность изобретения заключается в безошибочной дешифрации ключевой части комбинации и проверке правильности приема каждого элемента в комбинациях при уменьшенном числе обрабатываемых повторов кодовой комбинации, а также на совместном выполнении функций фазирования и декодирования принимаемых сообщений. 9 ил.

Устройство защиты от ошибок, содержащее регистр сдвига, информационный и тактовый входы которого являются соответственно информационным и тактовым входами устройства, делитель частоты, вход которого подключен к тактовому входу устройства и тактовому входу блока управления коммутацией, первый управляющий вход которого подключен к выходу первого счетчика импульса, а выход - к управляющему входу блока коммутации, r информационных входов которого подключены к соответствующим r выходам первой группы информационных выходов регистра сдвига (где r ≥ 5), а тактовый вход соединен с тактовым входом устройства, отличающееся тем, что дополнительно введены логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенный выходом к входу "Совпадение" блока управления счетом, второй и третий счетчики импульсов, выходы которых соединены, соответственно, с вторым и третьим управляющими входами блока управления коммутацией, дешифратор ключа, подключенный S входами элементов ключа к соответствующим S выходам второй группы информационных выходов регистра сдвига (где S = 1, 2, 3 ...), выход дешифратора ключа соединен с четвертым управляющим входом блока управления коммутацией, пятый и шестой входы которого объединены соответственно с седьмым и восьмым входами блока управления счетом и подключены к первому и второму выходам делителя частоты, первый, второй и третий выходы блока управления счетом соединены со счетными входами соответственно первого, второго и третьего счетчиков импульсов, к входам сброса каждого из которых подключены соответственно четвертый, пятый и шестой выходы блока управления счетом, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом устройства, а второй вход - с последовательным выходом регистра сдвига, r выходов блока коммутации являются информационными выходами устройства.

| Устройство защиты от ошибок | 1989 |

|

SU1644392A1 |

| Устройство для декодирования двоичных кодов при трехкратном повторении сообщений | 1990 |

|

SU1743003A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для мажоритарного декодирования имитостойких циклических кодов при трехкратном повторении комбинации | 1990 |

|

SU1709538A1 |

| Устройство для декодирования двоичных кодов при трехкратном повторении сообщений | 1986 |

|

SU1345357A2 |

| Устройство для декодирования двоичных кодов при трехкратном повторении сообщений | 1980 |

|

SU944129A1 |

| Устройство защиты от ошибок | 1989 |

|

SU1683180A1 |

| Устройство для мажоритарного деко-диРОВАНия дВОичНыХ КОдОВ пРи TPEX-KPATHOM дублиРОВАНии СООбщЕНий | 1979 |

|

SU799135A2 |

| Способ нейтрализации электростатических зарядов на нити | 1975 |

|

SU677135A1 |

| US 5633880 A1, 20.05.97 | |||

| ПРИМЕНЕНИЕ КОМПОЗИЦИЙ, СОДЕРЖАЩИХ BIFIDOBACTERIUM ANIMALIS SSP. LACTIS LMG P-28149 | 2015 |

|

RU2673341C2 |

| DE 4117726 A1, 06.08.92 | |||

| Устройство для регистрации грозовых разрядов | 1960 |

|

SU138078A1 |

| СПОСОБ ХИРУРГИЧЕСКОГО ЛЕЧЕНИЯ ОСЛОЖНЕННЫХ ЯЗВ ЖЕЛУДКА | 2004 |

|

RU2261666C1 |

Авторы

Даты

1999-03-20—Публикация

1998-02-18—Подача