Изобретение относится к полупроводниковой микроэлектронике и наноэлектронике и может быть использовано при создании интегральных схем с элементами субмикронных и нанометровых размеров, а также в тех случаях, когда целесообразно минимизировать количество литографических операций.

Известны конструкции МОП-транзисторов, при изготовлении которых используется небольшое количество две три литографические операции [1] Однако они плохо пригодны для построения интегральных схем, в которых необходимо использовать МОП транзисторы двух типов и сложную систему соединяющих их проводников.

Известны интегральные схемы с двумя типами МОП транзисторов [2] Они содержат полупроводниковую подложку, частично покрытую маскирующим изолирующим слоем, в непокрытой части которой сформированы два типа транзисторов, содержат два слоя проводников, изолированных слоев диэлектрика, и необходимые соединения между этими слоями межсоединения. Существенным недостатком таких интегральных схем является конструктивно топологическая сложность, характеризуемая количеством литографических операций при их изготовлении. Дело в том, что процессы литографии сопровождаются передачей массива информации о формируемом рисунке, чем значительно отличаются от остальных технологических процессов. Это существенно усложняет технологический процесс изготовления интегральных схем и препятствует его автоматизации. В случае прототипа при формировании рисунка изолирующего слоя-маски, затворов МОП-транзисторов, проводников и межсоединений необходимы литографические операции. В современных интегральных схемах общее количество литографии составляет от 10 до 20 и более. С переходом к интегральным схемам с элементами нанометровых размеров из-за сложности операции литографии и, в первую очередь, из-за необходимости многократных совмещений рисунков, применение подобных конструкций становится практически неприемлимым.

Для минимизации количества операции литографии предлагается в известной конструкции схем, содержащей полупроводниковую подложку, частично покрытую маскирующим слоем, в непокрытой части которой сформированы два типа МОП-транзисторов, содержащей два слоя проводников, изолированных слоем диэлектрика, и межсоединения, выполнить маскирующий слой в виде локальных областей, отделенных определенной ширины зазорами, протяженными вдоль двух взаимно перпендикулярных направлений, а выше указанные элементы и слои сформировать в зазорах между указанными областями, причем маскирующий слой сформировать с толщиной, превышающей ширину проводников.

Для задания рисунка локальных изолирующих областей потребуется естественно выполнение операции литографии, но формирование пассивных элементов интегральной схемы (двух слоев проводников, межсоединений) можно будет проводить без использования операции литографии. Это обеспечивается тем, что маскирующие области сохраняются свободными от проводников (чем предлагаемая конструкция принципиально отливается от прототипа), а толстая маска позволяет известными способами, используя лучевые технологические методы (включая нанесение, удаление и модификацию слоев ), формировать два взаимно перпендикулярных слоя проводников.

В дополнение к этому предлагается для интегральных схем на транзисторах с одинаковой шириной канала выполнить все зазоры одинаковой ширины, МОП-транзисторы первого типа сформировать в тройниковом зазоре определенной ориентации, а МОП-транзисторы второго типа в зеркально симметричном зазоре. Для интегральных схем на транзисторах с различной канала предлагается сформировать МОП-транзисторы в зазорах, представляющих собой прямоугольники с шириной, в три раза превращающей ширину проводника, и типы транзисторов задать ориентацией прямоугольника. Наличие в толстой маске зазоров сложной формы и различной ориентации позволяет формировать вышеперечисленными лучевыми методами без использования дополнительных литографий два типа МОП - транзисторов.

Таким образом, в интегральной схеме с двумя типами МОП-транзисторов введение толстого маскирующего слоя, представляющего собой локальные области, отделенные определенной ширины зазорами, протяженными вдоль двух взаимно перпендикулярных направлений, и выполнение МОП транзисторов и межсоединений и слоев проводников в зазорах между указанными областями обеспечивают достижение нового технического результата возможность создания интегральных схем с использованием всего одной операции литографии. Это расширяет возможности перехода к интегральным схемам с нанометровыми размерами и впервые позволяет реализовать технологию их изготовления без использования такой сложной процедуры, как совмещение слоев в процессе литографии.

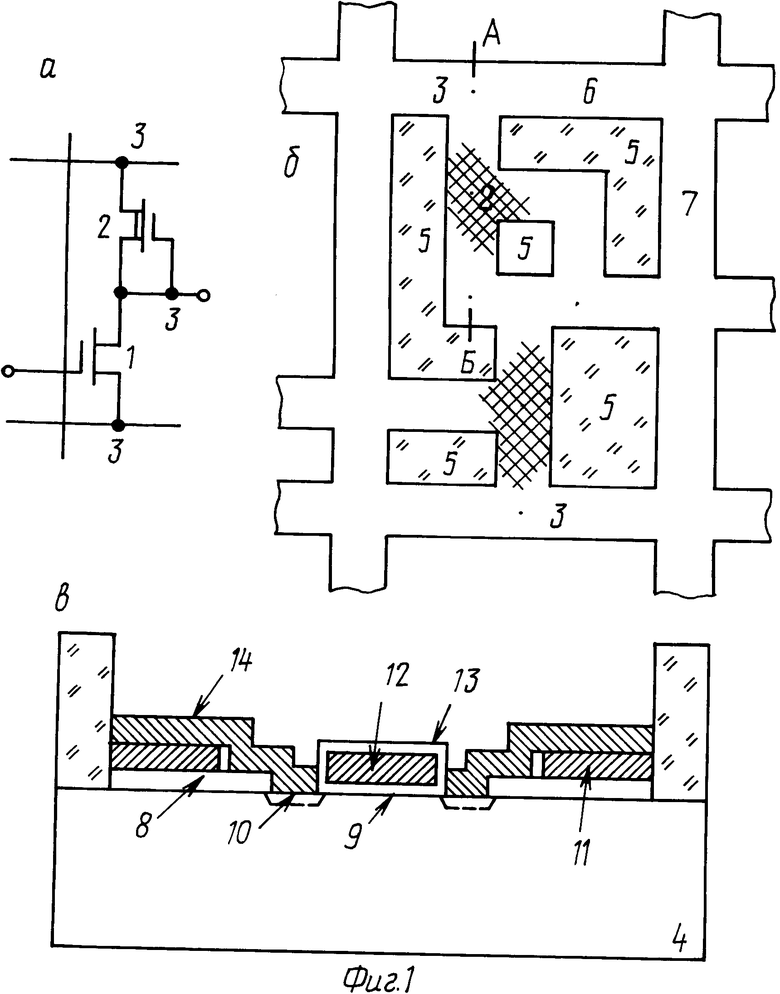

На фиг. 1,а изображена электрическая схема п-МОП инвертора; на фиг. 1,б

его однослойная топология с указанием размещения элементов; на фиг. 1,в - разрез структуры МОП-транзистора и межсоединения (разрез по линии А-Б); на фиг. 2,а изображена электрическая схема КМОП инвертора; на фиг. 2,б его однослойная топология на транзисторах с различной шириной канала.

Инвертор содержит активный транзистор 1 и нагрузочный транзистор 2, проводники и межсоединения 3. Интегральная схема выполнена на полупроводниковой подложке 4 с размещенными на ней локальными изолирующими областями 5, толщиной, например, 1,5 мкм, раздельными зазорами определенной ширины (например 1,0 мкм), протяженными в двух взаимно перпендикулярных направлениях, горизонтальном 6 и вертикальном 7, образующими односвязную область. Зазор покрыт слоем полевого диэлектрика 8 за исключением вертикальных тройников 1 и 2 (фиг. 1, б), где подзатворный диэлектрик 9 окаймлен по вертикали окнами к стоку/истоку 10. По горизонтальным зазорам сверху лежит первый проводящий слой 11, например из тугоплавкого металла W, Mo, Ti, который для транзисторов одновременно служит и затвором 12. Слой 11 покрыт межслойным диэлектриком 13 за исключением угловых зазоров и вертикальных тройниковых зазоров 3. Сверху по вертикальным зазорам лежит второй слой металла 14, например Al. Транзисторы двух типов отличаются топологически ориентацией вертикальных тройников 1 и 2 и в данном конструктиве имеют одинаковую ширину канала, определяемую шириной проводников. Их различная ориентация позволяет независимо изменять концентрацию примеси в канале, например путем наклонного легирования через маску 5.

В варианте интегральных схем на транзисторах с разной шириной каналов (фиг. 2) последовательность слоев в зазорах аналогична вышерассмотренной. Транзисторы разного типа проводимости 1 и 2 топологически отличаются ориентацией прямоугольных зазоров, что позволяет осуществлять их формирование независимо с помощью известных лучевых методов.

Источники информации

1. Зи.С. Физика полупроводниковых приборов. Кн. 2 -М. Мир, 1984, с. 70 - 78, рис. 53, 54, 58, 59.

2. Технология СБИС. /Под ред. С. Зи. КН. 2. -М. Мир, 1986, с. 207 212, рис. 11, 12.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ НА МОП-ТРАНЗИСТОРАХ | 1994 |

|

RU2100873C1 |

| ДВУХЗАТВОРНАЯ МДП-СТРУКТУРА С ВЕРТИКАЛЬНЫМ КАНАЛОМ | 1995 |

|

RU2106721C1 |

| РЕГИСТР СДВИГА | 1989 |

|

RU2066886C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДИНАМИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2029995C1 |

| СПОСОБ ФОРМИРОВАНИЯ МЕЖСОЕДИНЕНИЙ В МАТРИЦЕ ТРЕХМЕРНЫХ ПОЛУПРОВОДНИКОВЫХ ЭЛЕМЕНТОВ | 1991 |

|

RU2012090C1 |

| ПОЛУПРОВОДНИКОВЫЙ ПРИБОР | 1980 |

|

SU1840207A1 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1998 |

|

RU2166220C2 |

| СПОСОБ ПОЛУЧЕНИЯ ПЛЕНКИ ДИОКСИДА КРЕМНИЯ НА ПОДЛОЖКЕ | 1996 |

|

RU2116686C1 |

| ГАЗОЧУВСТВИТЕЛЬНЫЙ ДАТЧИК НА ОСНОВЕ ПОЛЕВОГО ТРАНЗИСТОРА | 1993 |

|

RU2061233C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЭЛЕКТРИЧЕСКИМ ЗОНДОВЫМ СЧИТЫВАНИЕМ | 2000 |

|

RU2198435C2 |

Использование:изобретение относится к полупроводниковой микро- и наноэлектронике и может быть использовано при создании интегральных схем с элементами субмикронных и нанометровых размеров. Сущность изобретения: предлагается в конструкции интегральных схем на полупроводниковой подложке, частично покрытой маскирующим слоем, последний выполнять в виде локальных областей, отделенных друг от друга определенной ширины зазорами, протяженными вдоль взаимно перпендикулярных направлений, которые в результате образуют односвязную область. В непокрытой маскирующим слоем части подложки - в зазорах между маскирующими областями - формируются все элементы интегральной схемы. Маскирующие области остаются свободными от проводников. Выбором толщины маски, большей ширины проводников, обеспечивается возможность независимого формирования двух взаимно перпендикулярных слоев проводников. 2 з. п. ф-лы, 2 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Зи С | |||

| Физика полупроводниковых приборов | |||

| Кн | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - М.: Мир, 1984, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Технология СБИС /Под ред | |||

| С.Зи | |||

| Кн | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - М.: Мир, 1986, с | |||

| Станок для изготовления из дерева круглых палочек | 1915 |

|

SU207A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1997-12-27—Публикация

1994-09-27—Подача