Изобретение относится к электронной технике и может быть использовано при изготовлении интегральных схем, особенно при необходимости минимизации количества операций литографии.

Известен способ изготовления интегральных схем на МОП-транзисторах, при котором на полупроводниковой подложке формируют изолирующий слой, затем его локально удаляют и в непокрытой части подложки формируют два типа транзисторов, включая формирование карманов, затворов, стоков/истоков и электродов, затем формируют необходимую систему проводников и межсоединений - разводку [1] Существенным недостатком такого способа изготовления интегральных схем является большое количество операций литографии, которая является одной из самых критичных технологических операций, а необходимость совмещения слоев при литографии требует сложного дорогостоящего оборудования.

Известен способ изготовления интегральных схем на МОП-транзисторах, включающий нанесение маскирующего слоя на поверхность пластины, вскрытие в нем одинаково ориентированных окон и формирование в них областей стоков/истоков и затворов транзисторов одного типа методами нанесения, удаления и модификации слоев направленными пучками частиц, а также формирование проводников. Он позволяет сформировать области стока/истока, а также электроды МОП-транзистора с помощью единственной литографии [2] Однако он непригоден для изготовления интегральных схем со сложной разводкой и тем более интегральных схем на комплементарных МОП-транзисторах.

Предлагается в известном способе изготовления интегральных схем на МОП-транзисторах, включающем нанесение маскирующего слоя на поверхность пластины, вскрытие в нем одинаково ориентированных окон и формирование в них транзисторов методами нанесения, удаления и модификации слоев направленными пучками частиц, а также формирование проводников, одновременно вскрывать окна, ориентированные во взаимно-перпендикулярном направлении под транзисторы другого типа и окна под проводники с той же ориентацией, что и под транзисторы, затем наносить защитный слой, который облучают пучками вдоль первого направления под углами ± А к нормали к пластине и удаляют его в незатененных стенкой маскирующего слоя местах, где вышеуказанными методами формировать транзисторы одного типа проводимости, затем удалять защитный слой в местах, незатененных при облучении пучками вдоль второго направления под теми же углами, где формируют вышеуказанными методами транзисторы другого типа проводимости, далее в местах, незатененных при облучении вдоль первого направления под углами ± В к нормали, формировать первый слой проводников, после чего в местах, незатененных при облучении вдоль обоих направлений под углами ±В, формировать межслойную изоляцию, и в местах, незатененных при облучении под углами ± В вдоль второго направления, формировать второй слой проводников, причем ширину проводников, затворов и областей стоков/истоков выбрать одинаковой и углы А и В выбирать исходя из соотношений

4W/H > tg A > 3W/H, 3W/2H > tg B > W/H,

где W- вышеуказанная ширина;

Н высота маскирующего слоя.

Принципиальным отличием предлагаемого способа от прототипа является то, что маскирующий слой, являющийся экраном при облучении пучками, удаляется и в местах размещения транзисторов, и в местах размещения проводников, а затворы транзисторов разных типов и проводники в двух слоях разводки сориентированы в взаимоперпендикулярных направлениях. Это позволяет сделать исходную топологию интегральной схемы однослойной и при использовании всего одной литографии осуществить их независимое последовательное формирование в незатененных местах, подвергаемых облучению.

Как следует из вышеописанного, при облучении пластины под углом А вдоль первого направления оно проникает в область транзистора первого типа проводимости, где защитный слой подлежит удалению, для этого тангенс угла к нормали к пластине выбирается меньше отношения минимальной полудлины транзистора к высоте маски. Вместе с тем оно не должно проникнуть в область транзистора второго типа проводимости, где защитный слой должен быть сохранен, для чего тангенс угла должен быть больше отношения ширины транзистора к высоте маски. Поскольку ширина транзистора равна сумме ширины стока, затвора и истока, т.е. втрое превышает ширину проводников, а длина транзистора предполагается втрое превышает ширину, то должно выполняться первое из вышеприведенных систем неравенств.

При формировании слоя разводки облучение вдоль его направления не должно проникать в области шин другого направления, откуда следует второе из вышеприведенных систем неравенств.

В качестве пучков могут использоваться электронные пучки с различной энергией, пучки ионов, атомов и молекулярные пучки, а также пучки фотонов различной энергии, т.е. световые потоки видимого, ультрафиолетового или рентгеновского диапазона. При формировании транзисторов в зависимости от типа защитного слоя он либо удаляется самим пучком, либо происходит его экспозиция и он локально удаляется при последующей обработке. Во вскрытых таким образом окнах известными методами формируют МОП-транзисторы разных типов проводимости. При формировании проводников формирование происходит либо непосредственно нанесением из пучка напылением, либо проводящий слой наносят тотально, покрывают слоем чувствительным к облучению, а затем после экспозиции пучком удаляют в неэкспонированных местах известными методами.

Таким образом, предлагаемый способ изготовления интегральных схем на МОП-транзисторах обеспечивает достижение нового технического результата - замену технологии с многими литографиями на технологию с одной литографией. Это расширяет возможности реализации новых технологий, в частности перехода к нанотехнологии, и облегчает переход к автоматизированной технологии и впервые позволяет реализовать технологию изготовления интегральных схем на МОП-транзисторах без использования такой сложной процедуры, как совмещение слоев в процессе литографии.

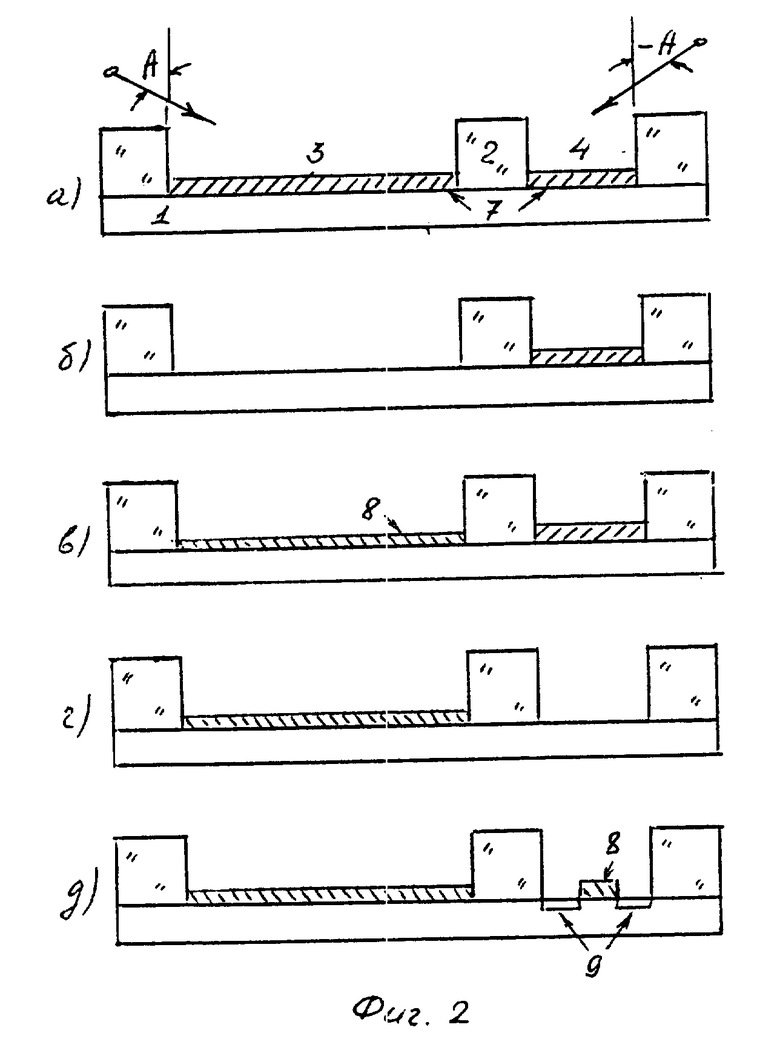

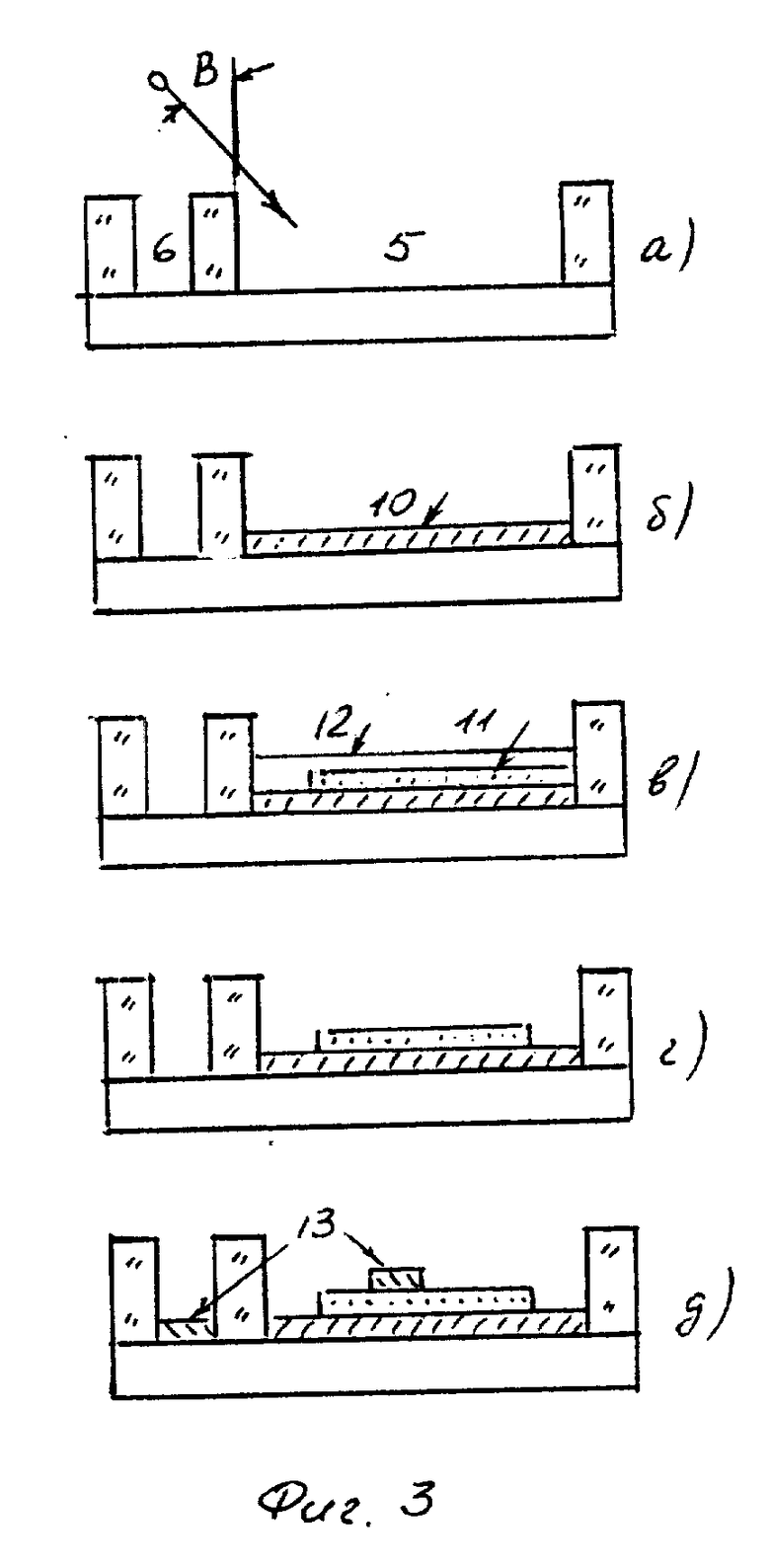

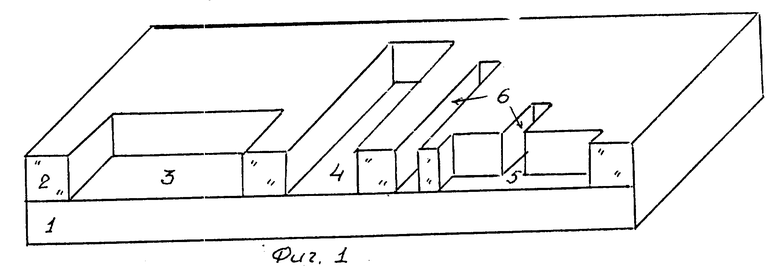

На фиг. 1 изображен разрез фрагмента маскированной пластины с окнами под элементы интегральной схемы; на фиг. 2 последовательность формирования двух типов МОП-транзисторов; на фиг. 3 -последовательность формирования двух слоев разводки с межсоединениями.

На кремниевой подложке 1 n-типа проводимости выращивают маскирующий слой 2, например из окиси кремния толщиной 2 мкм. В нем формируют окна 3 и 4 под транзисторы первого типа проводимости и второго типа, соответственно. Эти окна ориентированы во взаимоперпендикулярных направлениях и имеют ширину 3 мкм и ширину не менее 8 мкм. Одновременно в нем формируют окна 5 и 6 шириной в один мкм под проводники первого и второго слоя, соответственно, ориентированные во взаимоперпендикулярных направлениях (фиг. 1).

Затем наносят защитный слой 7, например из термического оксида толщиной 0,1 мкм, покрытого позитивным фоторезистом. Проводят наклонное экспонирование под углами ± А к нормали к пластине (56o < А < 63o) вдоль первого направления (фиг. 2,а). Проявляют фоторезист и удаляют его в проэкспонированных местах, удаляют тонкий слой оксида, незащищенного фоторезистом (фиг. 2,б). В результате в окнах 3 оксид отсутствует, и в них стандартными методами, с использованием наклонного облучения вдоль второго направления, формируют транзисторы первого типа проводимости, включая затворы 8 и сток/исток 9 (фиг. 2, в). Затем защитный слой 7 удаляется в окнах 4 (фиг. 2,г), и в них формируются транзисторы второго типа проводимости (фиг. 2,д).

Далее наклонным напылением вдоль первого направления под углами ±В к нормали к пластине (26o < B < 36o) (фиг. 3,а), формируют первый слой проводников 10, например из вольфрама толщиной 0,1 мкм (фиг. 3,б). Затем наклонным напылением под углом В к нормали к пластине вдоль первого направления наносят межслойную изоляцию 11, например нитрид кремния толщиной 0,1 мкм, и наносят слой негативного фоторезиста 12 (фиг. 3,в). Проводят наклонное экспонирование фоторезиста 12 вдоль первого направления под углом - В к нормали к пластине, проявляют и удаляют необлученный фоторезист, а через вскрытые в фоторезисте окна удаляют межслойную изоляцию и затем фоторезист (фиг. 3,г). В завершение наклонным напылением вдоль второго направления под углами ± В формируют второй слой проводников 13, например из алюминия толщиной 0,2 мкм (фиг. 3,д).

Предлагаемый способ позволяет за счет перехода к однолитографическому технологическому маршруту устранить проблему совмещения, которая ограничивает возможности автоматизации технологии и препятствует переходу к интегральным схемам нанометрового диапазона.

Литература

1. Технология СБИС, под ред. С. Зи, Кн. 2, Москва, Мир, 1986, с. 237-241, рис. 11.29.

2.Я. Таруи, Основы технологии СБИС, с. 389-393, 1985г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНАЯ СХЕМА С ДВУМЯ ТИПАМИ МОП-ТРАНЗИСТОРОВ | 1994 |

|

RU2100874C1 |

| ДВУХЗАТВОРНАЯ МДП-СТРУКТУРА С ВЕРТИКАЛЬНЫМ КАНАЛОМ | 1995 |

|

RU2106721C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДИНАМИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2029995C1 |

| Способ изготовления датчиков водорода на МОП-транзисторах | 1990 |

|

SU1785049A1 |

| ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ | 1991 |

|

RU2025831C1 |

| ГАЗОЧУВСТВИТЕЛЬНЫЙ ДАТЧИК НА ОСНОВЕ ПОЛЕВОГО ТРАНЗИСТОРА | 1993 |

|

RU2061233C1 |

| АССОЦИАТИВНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1991 |

|

RU2006964C1 |

| СПОСОБ ФОРМИРОВАНИЯ МЕЖСОЕДИНЕНИЙ В МАТРИЦЕ ТРЕХМЕРНЫХ ПОЛУПРОВОДНИКОВЫХ ЭЛЕМЕНТОВ | 1991 |

|

RU2012090C1 |

| Способ изготовления МОП-транзистора | 1991 |

|

SU1824656A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП-ТРАНЗИСТОРОВ | 1987 |

|

SU1554686A1 |

Использование: в электронной технике, при изготовлении интегральных схем, особенно при необходимости минимизации количества операций литографии. Сущность изобретения: в способе изготовления КМОП интегральных схем со взаимоперпендикулярным направлением затворов комплементарных транзисторов, размещенных в окнах в маскирующем слое на поверхности пластины, включающем нанесение, удаление и модификацию слоев направленными пучками в вышеуказанных окнах, маскирующий слой удаляют также и в местах размещения проводников, затем наносят защитный слой, который сначала удаляют в местах, подвергаемых облучению пучками вдоль первого направления под углами ± А к нормали к пластине, где и формируют транзисторы первого типа проводимости, затем защитный слой удаляют в местах, подвергаемых облучению пучками вдоль второго направления под теми же углами, где формируют транзисторы второго типа проводимости, далее в местах, подвергаемых облучению вдоль первого направления под углами ± В к нормали формируют первый проводящий слой, затем в местах, доступных облучению вдоль обоих направлений под углами ± В, формируют межслойную изоляцию и в местах, подвергаемых облучению под углами ± В вдоль второго направления, формируют второй проводящий слой, причем углы А и В выбирают, исходя из соотношения: 4W/H > tg A > 3W /H, 3W/2H > tg B > W/H, где W - ширина проводника, шины затвора, области стока и истока, Н - высота маскирующего покрытия. 3 ил.

Способ изготовления интегральных схем на МОП-транзисторах, включающий нанесение маскирующего слоя на поверхность пластины, вскрытие в нем одинаково ориентированных окон и формирование в них областей стоков/истоков и затворов транзисторов одного типа методами нанесения, удаления и модификации слоев направленными пучками частиц, а также формирование проводников, отличающийся тем, что одновременно вскрывают окна, ориентированные во взаимно перпендикулярном направлении под транзисторы другого типа и окна под проводники с той же ориентацией, что и под транзисторы, затем наносят защитный слой, который облучают пучками вдоль первого направления под углами ± A к нормали к пластине и удаляют его в не затененных стенкой маскирующего слоя местах, где указанными методами формируют транзисторы одного типа проводимости, затем защитный слой удаляют в местах, незатененных при облучении пучками вдоль второго направления под теми же углами, где формируют вышеуказанными методами транзисторы другого типа проводимости, далее в местах, незатененных при облучении вдоль первого направления под углами ± B к нормали, формируют первый слой проводников, после чего в местах, не затененных при облучении вдоль обоих направлениq под углами ± B, формируют межслойную изоляцию, и в местах, не затененных при облучении под углами ± B вдоль второго направления, формируют второй слой проводников, причем ширина проводников, затворов и областей стоков/истоков одинакова и углы A и B выбирают исходя из соотношений

4W/H > tgA > 3W/H,

3W/2H > tgB > W/H,

где W ширина проводников;

Н высота маскирующего слоя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Технология СБИС /Под ред | |||

| С.Зи, Книга 2 | |||

| - М.: Мир, 1986, с | |||

| Прибор для корчевания пней | 1921 |

|

SU237A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Таруи Я | |||

| Основы технологии СБИС | |||

| - М.: Мир, 1985, с | |||

| Гидравлический подъемник | 1922 |

|

SU389A1 |

Авторы

Даты

1997-12-27—Публикация

1994-09-27—Подача