Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны реляторные коммутаторы (см. например рис. 60а на с. 97 в книге Волгин Л. И. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. - Таллинн: Валгус, 1989, 179 с.; А.с. СССР 1693614, кл. G 06 G 7/25, 1991), каждый из которых определяет на какой из трех его управляющих входов воздействует медианный сигнал.

Недостатком известных реляторных коммутаторов является низкая нагрузочная способность, так как их выходное сопротивление равно сумме сопротивления нескольких замкнутых аналоговых ключей, и большая погрешность коэффициента передачи, которая обусловлена нестабильностью сопротивлений нескольких замкнутых аналоговых ключей.

Наиболее близким по технической сущности к заявляемому изобретению является выбранный в качестве прототипа реляторный коммутатор (А.с. СССР 1674168, кл. G 06 G 7/25, 1991), который определяет, на какой из трех его управляющих входов воздействует медианный сигнал, и содержит реляторы, состоящие из дифференциальных компараторов напряжения и аналоговых переключателей.

Прототип обладает тем же недостатком, т.е. его выходное сопротивление равно сумме сопротивлений двух замкнутых аналоговых ключей, а погрешность коэффициента передачи обусловлена нестабильностью сопротивлений двух замкнутых аналоговых ключей.

Целью изобретения является повышение нагрузочной способности и уменьшение погрешности коэффициента передачи.

Поставленная цель достигается тем, что в реляторный коммутатор, содержащий три дифференциальных компаратора напряжения, причем неинвертирующие входы второго и третьего компараторов подключены к второму управляющему входу коммутатора, инвертирующие входы первого и третьего компараторов подключены к третьему управляющему входу комутатора, а неинвертирующий вход первого и инвертирующий вход второго компараторов подключены к первому управляющему входу коммутатора, введены аналоговый размыкающий ключ, два аналоговых замыкающих ключа и три булевых логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу первого компаратора, вторые входы второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу третьего компаратора, второй вход первого и первый вход второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу второго компаратора, выходы второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к управляющим входам первого и второго замыкающих ключей соответственно, а выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к управляющему входу размыкающего ключа, вход которого является первым информационным входом коммутатора, а выход - первым выходом коммутатора, входы первого и второго замыкающих ключей являются соответственно вторым и третьим информационными входами коммутатора, а выходы - соответственно вторым и третьим выходам коммутатора.

По имеющимся у авторов сведениям совокупность существенных признаков, характеризующих сущность заявляемого изобретения, неизвестна из уровня техники, что позволяет сделать вывод о соответствии изобретения критерию "новизна".

По мнению авторов сущность заявляемого изобретения не следует для специалиста явным образом из известного уровня техники, так как из него не выявляется вышеуказанное влияние на получаемый технический результат (новое свойство объекта) - совокупности признаков, которые отличают от прототипа заявляемое изобретение, что позволяет сделать вывод о его соответствии критерию "изобретательский уровень".

Совокупность существенных признаков, характеризующих сущность изобретения, может быть многократно использована в автоматике и аналоговой вычислительной технике для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др. с получением технического результата, заключающегося в том, что выходное сопротивление реляторного коммутатора равно сопротивлению замкнутого аналогового ключа, а также в том, что погрешность коэффициента передачи коммутатора обусловлена нестабильностью сопротивления замкнутого аналогового ключа, обуславливающего обеспечение достижения поставленной цели - повышение нагрузочной способности и уменьшение погрешности коэффициента передачи, что позволяет сделать вывод о соответствии изобретения критерию "промышленная применимость".

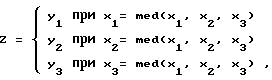

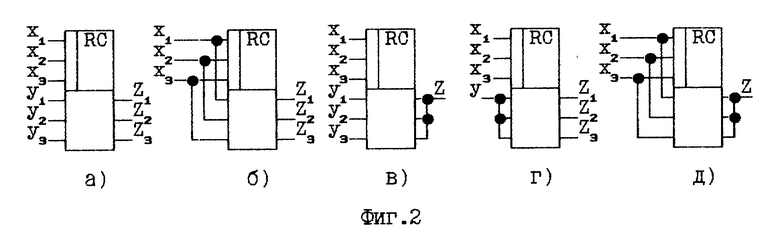

На фиг. 1 приведена схема предлагаемого реляторного коммутатора; на фиг. 2 - условное обозначение коммутатора и несколько вариантов схем его включения.

Схема предлагаемого реляторного коммутатора (фиг. 1) содержит три дифференциальных компаратора напряжения 1 - 3; три булевых логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 - 6; размыкающий 7 и два замыкающих 8 и 9 аналоговых ключа. Неинвертирующий вход компаратора 1 и инвертирующий вход компаратора 2 объединены и образуют первый управляющий вход компаратора, неинвертирующие входы компараторов 2 и 3 подключены к второму управляющему входу коммутатора, а инвертирующие входы компараторов 1 и 3 - к третьему управляющему входу коммутатора, выходы компараторов 1 и 3 подключены соответственно к первым входам элементов 4 и 6 и к вторым входам элементов 5 и 6, а выход компаратора 2 подключен к второму входу элемента 4 и к первому входу элемента 5, выход которого подключен к управляющему входу ключа 8, выходы элементов 4 и 6 подключены к управляющим входам ключей 7 и 9 соответственно, выходы ключей 7 - 9 являются выходами (z1-z3), а входы - информационными входами коммутатора, x1-x3 и y1-y3 - аналоговые сигналы соответственно на управляющих и информационных входах коммутатора.

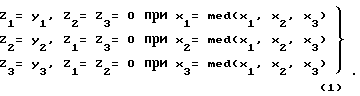

Работа предлагаемого релятора коммутатора (фиг.1) осуществляется следующим образом. Воспроизводимая коммутатором операция определяется выражением: .

.

При x1 = med(x1, x2, x3) на входах элементов 4, 5, 6 будут одинаковые логические сигналы, на их выходах будет логический "0", ключ 7 будет замкнут, ключи 8 и 9 - разомкнуты, т.е. Z1 = y1, Z2 = Z3 = 0. При x2=med(x1, x2, x3) на входах элемента 6 будут одинаковые логические сигналы, на его выходе будет логический "0", на входах элементов 4 и 5 будут разные логические сигналы, на их выходах будет логическая "1", ключ 8 будет замкнут, ключи 7 и 9 - разомкнуты, т.е. z2=y2, z1=z3=0. При x3=med(x1, x2, x3) на входах элементов 4 и 6 будут разные логические сигналы, на их выходах будет логическая "1", на входах элемента 5 будут одинаковые логические сигналы, на его выходе будет логический "0", ключ 9 будет замкнут, ключи 7 и 8 - разомкнуты, т.е. z3=y3, z1=z2=0.

Таким образом, реляторный коммутатор определяет на какой из трех его управляющих входов воздействует медианный сигнал, при этом выходное сопротивление коммутатора по сравнению с прототипом уменьшено в два раза и равно сопротивлению замкнутого аналогового ключа, нестабильность этого сопротивления будет определять погрешность коэффициента передачи, т.е. достигнуто повышение нагрузочной способности и уменьшение погрешности коэффициента передачи коммутатора.

При соединении управляющих и информационных входов в соответствии с фиг. 2б коммутатор (RC) будет воспроизводить операцию выделения медианы с идентификацией номера входа i, на который воздействует медианный сигнал xi (номер выхода для которого zi=xi совпадает с номером входа, на который воздействует медианный сигнал xi), т.е. операцию (1) при y1=x1, y2=x2, y3=x3. При объединении выходов коммутатор является медианным мультиплексором (фиг. 2в) и воспроизводит операцию: ,

,

а при объединении информационных входов - медианным демультиплексором (фиг. 2г) и воспроизводит операцию (1) при y1=y2=y3=y. Медианный мультиплексор (фиг. 2в) при соединении его входов в соответствии с фиг. 2д является медианным селектором, а при других заданных комбинациях соединений его входов может быть использован в качестве формирователя некоторых типовых нелинейных функций: функции двустороннего параллельного или одностороннего ограничения, режекторной или селективной фильтрации уровней сигнала, функции допускового контроля и др.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАНГОВЫЙ ФИЛЬТР | 1996 |

|

RU2124754C1 |

| РЕЛЯТОРНЫЙ ПОЗИЦИОННЫЙ ИДЕНТИФИКАТОР | 1996 |

|

RU2117330C1 |

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2001 |

|

RU2192043C1 |

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2001 |

|

RU2192044C1 |

| РЕЛЯТОРНЫЙ ИДЕНТИФИКАТОР | 1996 |

|

RU2117329C1 |

| РЕЛЯТОРНЫЙ МОДУЛЬ | 2001 |

|

RU2195701C1 |

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2000 |

|

RU2181502C2 |

| РЕЛЯТОРНЫЙ АМПЛИТУДНЫЙ СЕЛЕКТОР | 1996 |

|

RU2112276C1 |

| РАНГОВЫЙ ФИЛЬТР | 2000 |

|

RU2172516C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2000 |

|

RU2177643C1 |

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др. Технический результат заключается в повышении нагрузочной способности и уменьшении погрешности коэффициента передачи, который достигается за счет того, что в реляторный коммутатор, содержащий три дифференциальных компаратора напряжения, введены аналоговый размыкающий ключ, два аналоговых замыкающих ключа и три булевых логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. 2 ил.

Реляторный коммутатор, содержащий три дифференциальных компаратора напряжения, причем неинвертирующие входы второго и третьего компараторов подключены к второму управляющему входу коммутатора, инвертирующие входы первого и третьего компараторов подключены к третьему управляющему входу коммутатора, а неинвертирующий вход первого и инвертирующий вход второго компараторов подключены к первому управляющему входу коммутатора, отличающийся тем, что в него введены аналоговый размыкающий ключ, два аналоговых замыкающих ключа и три булевых логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первые входы первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу первого компаратора, вторые входы второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу третьего компаратора, второй вход первого и первый вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу второго компаратора, выходы второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к управляющим входам первого и второго замыкающих ключей соответственно, а выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к управляющему входу размыкающего ключа, вход которого является первым информационным входом коммутатора, а выход первым выходом коммутатора, входы первого и второго замыкающих ключей являются соответственно вторым и третьим информационными входами коммутатора, а выходы - соответственно вторым и третьим выходами коммутатора.

| Устройство для воспроизведения функции медианы | 1989 |

|

SU1674168A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-01-27—Публикация

1996-04-23—Подача