Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин и аналоговых процессоров, использующих операцию выделения из совокупности аналоговых сигналов заданной порядковой статистики (сигнала заданного ранга).

Известны ранговые фильтры (см. например авт. св. СССР 1478233, кл. G 06 G 7/25, 1989. ; авт. св. 1674168, кл. G 06 G 7/25, 1991; авт. св. СССР 1693614, кл. G 06 G 7/25, 1991), которые выполняют операцию выбора медианного из трех сигналов y=med(x1, x2, x3).

Недостатком известных ранговых фильтров являются ограниченные функциональные возможности, так как они не выполняют операции выбора максимального из трех сигналов y=max(x1, x2, x3) и минимального из трех сигналов y=min(x1, x2, x3).

Наиболее близким по технической сущности к заявляемому изобретению является выбранный в качестве прототипа ранговый фильтр (авт. св. СССР 1278902, кл. G 06 G 7/25, 1986), содержащий блок выделения экстремальных сигналов, блок выделения максимального сигнала и блок выделения минимального сигнала и выполняющий операцию y=med(x1, x2, x3).

Прототип обладает тем же недостатком, то есть не выполняет операции y= max(x1x2, x3 и y=min(x1, x2, x3).

Целью изобретения является расширение функциональных возможностей за счет обеспечения выполнения операций y=max(x1, x2, x3), y=min(x1, x2, x3), y=med(x1, x2, x3).

Поставленная цель достигается тем, что в ранговый фильтр, содержащий блок выделения экстремальных сигналов, первый и второй входы которого являются соответственно первым и вторым информационным входами рангового фильтра, введены первый и второй реляторные амплитудные селекторы, каждый из которых выполнен в виде дифференциального компаратора напряжения, выход которого соединен с первым входом булевого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного своим выходом к входам управления замыкающего и размыкающего ключей, входы которых соединены соответственно с неинвертирующим и инвертирующим входами дифференциального компаратора напряжения и являются соответственно первым и вторым входами каждого из реляторных амплитудных селекторов, второй вход булевого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является управляющим входом, а объединенные выходы замыкающего и размыкающего ключей - выходом каждого из реляторных амплитудных селекторов, первый вход первого реляторного амплитудного селектора является третьим информационным входом рангового фильтра, а второй вход соединен с выходом "Максимум" блока выделения экстремальных сигналов, первый вход второго реляторного амплитудного селектора соединен с выходом первого реляторного селектора, а второй вход - с выходом "Минимум" блока выделения экстремальных сигналов, выход второго реляторного амплитудного селектора является выходом рангового фильтра, первым и вторым управляющим входом которого являются соответственно управляющий вход первого и управляющий вход второго реляторных амплитудных селекторов.

По имеющимся у авторов сведениям совокупность существенных признаков, характеризующих сущность заявляемого изобретения неизвестна из уровня техники, что позволяет сделать вывод о соответствии изобретения критерию "новизна".

По мнению авторов, сущность заявляемого изобретения не следует для специалиста явным образом из известного уровня техники, так как из него не выделяется вышеуказанное влияние на получаемый технический результат - новое свойство объекта - совокупности признаков, которые отличают от прототипа заявляемое изобретение, что позволяет сделать вывод о его соответствии критерию "изобретательский уровень".

Совокупность существенных признаков, характеризующих сущность изобретения, в принципе, может быть многократно использована в автоматике и аналоговой вычислительной технике для построения функциональных узлов аналоговых вычислительных машин и аналоговых процессоров, использующих операцию выделения из совокупности аналоговых сигналов заданной порядковой статистики (сигнала заданного ранга), с получением технического результата, заключающегося в том, что ранговый фильтр, в зависимости от логических сигналов, поданных на его управляющие входы, наряду с выполнением операции y=med(x1, x2, x3), выполняет операции y=max(x1, x2, x3) и y=min(x1, x2, x3, обуславливающего обеспечение поставленной цели - расширение функциональных возможностей, что позволяет сделать вывод о соответствии изобретения критерию "промышленная применимость".

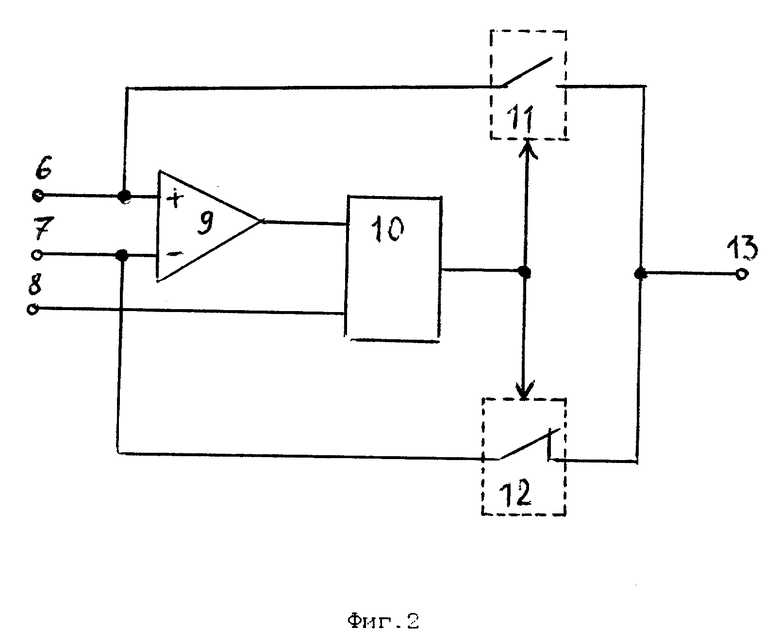

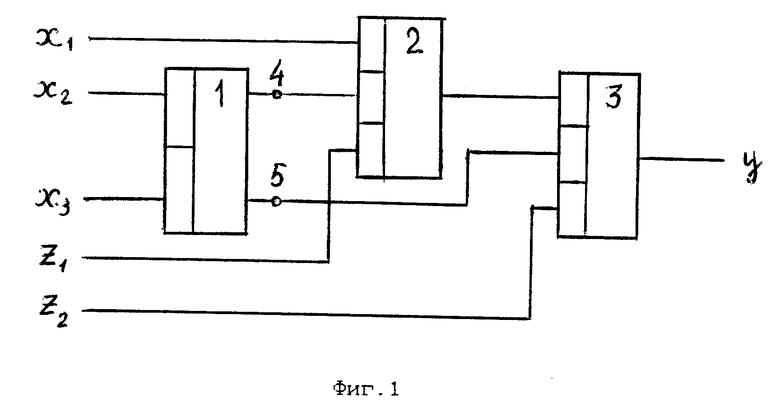

На фиг. 1 и фиг. 2 представлены соответственно схема предлагаемого рангового фильтра и схема реляторного амплитудного селектора, который использован при построении фильтра.

Ранговый фильтр (фиг. 1) содержит блок выделения экстремальных сигналов 1, первый реляторный амплитудный селектор 2, второй реляторный амплитудный селектор 3, выход "Максимум" 4 и выход "Минимум" 5 блока выделения экстремальных сигналов 1. Первый, второй входы блока 1 и первый вход селектора 2 являются соответственно первым, вторым и третьим информационными входами рангового фильтра, второй вход селектора 2 соединен с выходом 4 блока 1, первый вход селектора 3 соединен с выходом селектора 2, а второй вход - с выходом 5 блока 1, выход селектора 3 является выходом рангового фильтра, первым и вторым управляющими входами которого являются соответственно управляющий вход селектора 2 и управляющий вход селектора 3.

Каждый из селекторов 2 и 3 (фиг. 2) содержит первый 6 и второй 7 входы, управляющий вход 8, дифференциальный компаратор напряжения 9, булевый логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, замыкающий 11 и размыкающий 12 ключи, выход 13. Выход компаратора 9 соединен с первым входом элемента 10, подсоединенного своим выходом к входам управления замыкающего 11 и размыкающего 12 ключей, входы которых соединены соответственно с неинвертирующим и инвертирующим входами компаратора 9 и являются соответственно первым 6 и вторым 7 входами реляторного амплитудного селектора, управляющим входом 8 которого является второй вход элемента 10, а выходом 13 - объединенные выходы ключей 11 и 12.

Ранговый фильтр работает следующим образом. x1, x2, x3 - аналоговые сигналы соответственно на третьем, первом и втором информационных входах рангового фильтра, z1, z2 - логические сигналы соответственно на первом и втором управляющих входах рангового фильтра, y - сигнал на выходе рангового фильтра. На выходе 4 блока 1 выделяется максимальный сигнал из x2 и x3 (max(x2, x3), а на выходе 5 - минимальный сигнал из x2 и x3 (mib(x2, x3)). Пусть z1= 0 - логический (лог.) "0". При x1>max(x2, x3) на входах элемента 10, входящего в состав селектора 2, будут разные логические сигналы, на выходе элемента 10 будет лог. "1", ключ 11 будет замкнут, ключ 12 - разомкнут, на выходе селектора 2 выделится сигнал x1. При x1<max(x2, x3) на входах элемента 10, входящего в состав селектора 2, будут одинаковые логические сигналы, на выходе элемента 10 будет лог. "0", ключ 11 будет разомкнут, ключ 12 - замкнут, на выходе селектора 2 выделится сигнал max(x2, x3). Таким образом, на выходе селектора 2 при z1=0 выделяется максимальный сигнал из двух сигналов, действующих на его входах (max[x1, max(x2, x3)]). Пусть z1=1 - лог. "1". При x1<max(x2, x3) на входах элемента 10, входящего в состав селектора 2, будут разные логические сигналы, на выходе элемента 10 будет лог. "1", ключ 11 будет замкнут, ключ 12 - разомкнут, на выходе селектора 2 выделится сигнал x1. При x1>max(x2, x3) на входах элемента 10, входящего в состав селектора 2, будут одинаковые логические сигналы, на выходе элемента 10 будет лог. "0", ключ 11 будет разомкнут, ключ 12 - замкнут, на выходе селектора 2 выделится сигнал max(x2, x3). Таким образом, на выходе селектора 2 при z1= 1 выделяется минимальный сигнал из двух сигналов, действующих на его входах (min[x1, max(x2, x3)]). Аналогично, при z2=0 на выходе селектора 3, являющемся выходом рангового фильтра, выделяется максимальный сигнал из сигнала на выходе 5 блока 1 и сигнала на выходе селектора 2, а при z2=1 - минимальный из тех двух сигналов. То есть при z1=z2=0 ранговый фильтр выполняет операцию

y=max [min(x2, x3), max[x1, max(x2, x3)]] = max(x1, x2, x3); при z1=z2=1 ранговый фильтр выполняет операцию

y= min [min(x2, x3), min[x1, max(x2, x3)]] = min(x1, x2, x3); при z1=1, z2=0 ранговый фильтр выполняет операцию

y= max [min(x2, x3), min [x1, max(x2, x3)]] = med(x1, x2, x3). Кроме того, при z1=0, z2=1 ранговый фильтр выполняет операцию

y=min [min(x2, x3), max[x1, max(x2, x3)]] = min(x2, x3).

Таким образом, в отличие от прототипа предлагаемый ранговый фильтр, в зависимости от логических сигналов, поданных на его управляющие входы, наряду с выполнением операции y=med(x1, x2, x3), выполняет операции y=max(x1, x2, x3) и y=min(x1, x2, x3), что расширяет его функциональные возможности. При этом в отличие от прототипа предлагаемый ранговый фильтр, в зависимости от логических сигналов, поданных на его управляющие входы, выполняет операцию выделения минимального из сигналов, поступающих на его первый и второй информационные входы, не зависимо от сигнала на его третьем информационном входе, что также расширяет функциональные возможногсти рангового фильтра.

Изобретение относится к области аналоговой вычислительной техники и может быть использовано для реализации операции выделения из совокупности аналоговых сигналов заданной порядковой статистики. Техническим результатом является расширение функциональных возможностей за счет обеспечения выделения медианы. Фильтр содержит блок выделения экстремальных сигналов и реляторные амплитудные селекторы, каждый из селекторов состоит из дифференциального компаратора напряжения, ключей и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. 2 ил.

Ранговый фильтр, содержащий блок выделения экстремальных сигналов, первый и второй входы которого являются информационными входами рангового фильтра, отличающийся тем, что в него введены первый и второй реляторные амплитудные селекторы, каждый из которых выполнен в виде дифференциального компаратора напряжения, выход которого соединен с первым входом булевого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, подсоединенного своим выходом к входам управления замыкающего и размыкающего ключей, входы которых соединены соответственно с неинвертирующим и инвертирующим входами дифференциального компаратора напряжения и являются соответственно первым и вторым входами каждого из реляторных амплитудных селекторов, второй вход булевого логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является управляющим входом, а объединенные выходы замыкающего и размыкающего ключей - выходом каждого из реляторных амплитудных селекторов, первый вход первого реляторного амплитудного селектора также является информационным входом рангового фильтра, а второй вход соединен с выходом "Максимум" блока выделения экстремальных сигналов, первый вход второго реляторного амплитудного селектора соединен с выходом первого реляторного амплитудного селектора, а второй вход - с выходом "Минимум" блока выделения экстремальных сигналов, выход второго реляторного амплитудного селектора является выходом рангового фильтра, первым и вторым управляющими входами которого являются соответственно управляющие входы первого и второго реляторных амплитудных селекторов.

| Устройство для воспроизведения функции медианы (его варианты) | 1985 |

|

SU1278902A1 |

| Аналоговый мультиплексор-демультиплексор | 1987 |

|

SU1478233A1 |

| Устройство для воспроизведения функции медианы | 1989 |

|

SU1674168A1 |

| Медианный мультиплексор-демультиплексор | 1989 |

|

SU1693614A1 |

Авторы

Даты

1999-01-10—Публикация

1996-02-15—Подача