Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления и др.

Известны аналоговые процессоры (см. например рис.72а в книге Волгин Л.И. Синтез устройств для обработки и преобразования информации в элементном базисе реляторов. - Таллинн: Валгус, 1989. - 179 с.), которые обеспечивают выбор медианного из пяти входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных аналоговых процессоров, относится ограниченные функциональные возможности, обусловленные тем, что не обеспечивается выбор минимального, супраминимального, субмаксимального или максимального сигнала.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, аналоговый процессор (фиг. 1 в описании изобретения к патенту РФ 2124754, кл. G 06 G 7/52, 1999 г.), который содержит два релятора и обеспечивает выбор минимального, медианного или максимального из трех входных аналоговых сигналов.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится ограниченные функциональные возможности, обусловленные тем, что не допускается обработка пяти входных аналоговых сигналов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения выбора минимального, супраминимального, медианного, субмаксимального или максимального из пяти входных аналоговых сигналов.

Указанный технический результат при осуществлении изобретения достигается тем, что в аналоговом процессоре, содержащем два релятора, каждый из которых выполнен в виде компаратора, подключенного выходом к первому входу булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, особенность заключается в том, что в аналоговый процессор дополнительно введены n (n= 37) реляторов, причем все реляторы сгруппированы в одиннадцать групп так, что i-ая  и одиннадцатая группы содержат соответственно три и девять реляторов, первые входы первых реляторов первой,..., десятой групп объединены и образуют первый управляющий вход аналогового процессора, второй и третий управляющие входы которого образованы соответственно объединенными входами управления первых и объединенными входами управления вторых, третьих реляторов каждой i-ой

и одиннадцатая группы содержат соответственно три и девять реляторов, первые входы первых реляторов первой,..., десятой групп объединены и образуют первый управляющий вход аналогового процессора, второй и третий управляющие входы которого образованы соответственно объединенными входами управления первых и объединенными входами управления вторых, третьих реляторов каждой i-ой  группы, а четвертый управляющий вход подключен к входам управления первого,. . . , девятого реляторов одиннадцатой группы, в i-ои

группы, а четвертый управляющий вход подключен к входам управления первого,. . . , девятого реляторов одиннадцатой группы, в i-ои  группе выход первого и выход второго реляторов соединены соответственно с первым входом второго и первым входом третьего реляторов, выход третьего релятора первой группы и выходы третьих реляторов второй,..., десятой групп подключены соответственно к первому входу первого и вторым входам первого,..., девятого реляторов одиннадцатой группы, в которой выход предыдущего релятора соединен с первым входом последующего релятора, а выход девятого релятора является выходом аналогового процессора.

группе выход первого и выход второго реляторов соединены соответственно с первым входом второго и первым входом третьего реляторов, выход третьего релятора первой группы и выходы третьих реляторов второй,..., десятой групп подключены соответственно к первому входу первого и вторым входам первого,..., девятого реляторов одиннадцатой группы, в которой выход предыдущего релятора соединен с первым входом последующего релятора, а выход девятого релятора является выходом аналогового процессора.

Проведенный заявителем анализ уровня техники, включающий поиск по патентным и научно-техническим источникам информации, и выявление источников, содержащих сведения об аналогах заявленного изобретения, позволил установить, что заявитель не обнаружил аналог, характеризующийся признаками, тождественными всем существенным признакам заявленного изобретения. Определение из перечня выявленных аналогов прототипа, как наиболее близкого по совокупности существенных признаков аналога, позволил выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном устройстве, изложенных в формуле изобретения. Следовательно, заявляемое изобретение соответствует условию "новизна".

Для проверки соответствия заявленного изобретения условию "изобретательский уровень" заявитель провел дополнительный поиск известных решений, чтобы выявить признаки, совпадающие с отличительными от прототипа признаками заявленного устройства. Результаты поиска показали, что заявленное изобретение не вытекает для специалиста явным образом из известного уровня техники, поскольку из уровня техники, определенного заявителем, не выявлено влияние предусматриваемых существенными признаками заявленного изобретения преобразований на достижение технического результата, в частности, заявленным изобретением не предусматриваются следующие преобразования:

- дополнение известного средства какой-либо известной частью (частями), присоединяемой (присоединяемыми) к нему по известным правилам для достижения технического результата, в отношении которого установлено влияние именно таких дополнений;

- замена какой-либо части (частей) известного средства другой известной частью для достижения технического результата, в отношении которого установлено влияние именно такой замены;

- исключение какой-либо части (элемента) средства с одновременным исключением обусловленной ее наличием функции и достижением при этом обычного для такого исключения результата;

- увеличение количества однотипных элементов для усиления технического результата, обусловленного наличием в средстве именно таких элементов;

- выполнение известного средства или его части (частей) из известного материала для достижения технического результата, обусловленного известными свойствами этого материала;

- создание средства, состоящего из известных частей, выбор которых и связь между которыми осуществлены на основании известных правил, рекомендаций, и достигаемый при этом технический результат обусловлен только известными свойствами частей этого средства и связей между ними.

Описываемое изобретение не основано на изменении количественного признака (признаков), представлении таких признаков во взаимосвязи, либо изменении ее вида. Имеется в виду случай, когда известен факт влияния каждого из указанных признаков на технический результат, и новые значения этих признаков или их взаимосвязь могли быть получены исходя из известных зависимостей, закономерностей. Следовательно, заявленное изобретение соответствует условию "изобретательский уровень".

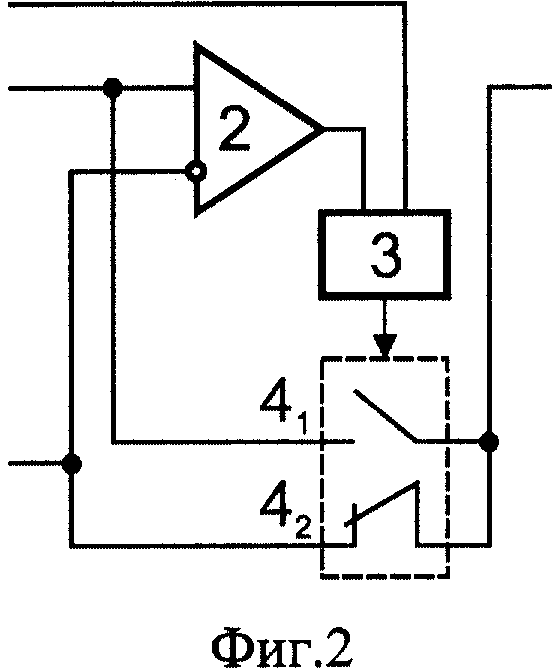

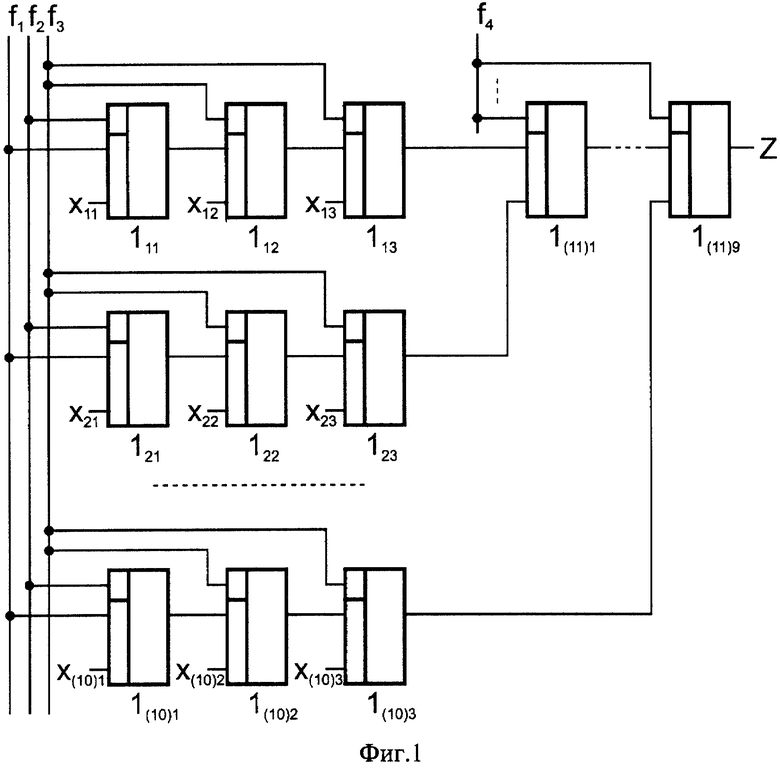

На фиг. 1 и 2 представлены соответственно схема предлагаемого аналогового процессора и схема релятора, использованного при построении указанного процессора. Аналоговый процессор содержит реляторы 111,...,1(11)9. Каждый релятор выполнен в виде компаратора 2, подключенного выходом к первому входу булевого элемента ИСКЛЮЧАЮШЕЕ ИЛИ 3, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей 41 и 42, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора 2, присоединенные соответственно к входам ключей 41 и 42. Все реляторы сгруппированы в одиннадцать групп так, что i-ая  и одиннадцатая группы содержат соответственно реляторы 1i1, 1i2, 1i3, и 1(11)1, ...,1(11)9, первые входы реляторов 111,...,1(10)1 объединены и образуют первый управляющий вход аналогового процессора, второй и третий управляющие входы которого образованы соответственно объединенными входами управления реляторов 111,...,1(10)1 и объединенными входами управления реляторов 1i1, 1i3

и одиннадцатая группы содержат соответственно реляторы 1i1, 1i2, 1i3, и 1(11)1, ...,1(11)9, первые входы реляторов 111,...,1(10)1 объединены и образуют первый управляющий вход аналогового процессора, второй и третий управляющие входы которого образованы соответственно объединенными входами управления реляторов 111,...,1(10)1 и объединенными входами управления реляторов 1i1, 1i3 , а четвертый управляющий вход подключен к входам управления реляторов 111)1,..., 1(11)9, выходы реляторов 1i1 и 1i2 соединены соответственно с первыми входами реляторов 1i2 и 1i3

, а четвертый управляющий вход подключен к входам управления реляторов 111)1,..., 1(11)9, выходы реляторов 1i1 и 1i2 соединены соответственно с первыми входами реляторов 1i2 и 1i3 выход релятора 113 и выходы реляторов 123,...,1(10)3 подключены соответственно к первому входу релятора 1(11)1 и вторым входам реляторов 1(11)1,..., 1(11)9, выходы реляторов 1(11)1,..., 1(11)8 соединены соответственно с первыми входами реляторов 1(11)2,..., 1(11)9, а выход релятора 1(11)9 является выходом аналогового процессора.

выход релятора 113 и выходы реляторов 123,...,1(10)3 подключены соответственно к первому входу релятора 1(11)1 и вторым входам реляторов 1(11)1,..., 1(11)9, выходы реляторов 1(11)1,..., 1(11)8 соединены соответственно с первыми входами реляторов 1(11)2,..., 1(11)9, а выход релятора 1(11)9 является выходом аналогового процессора.

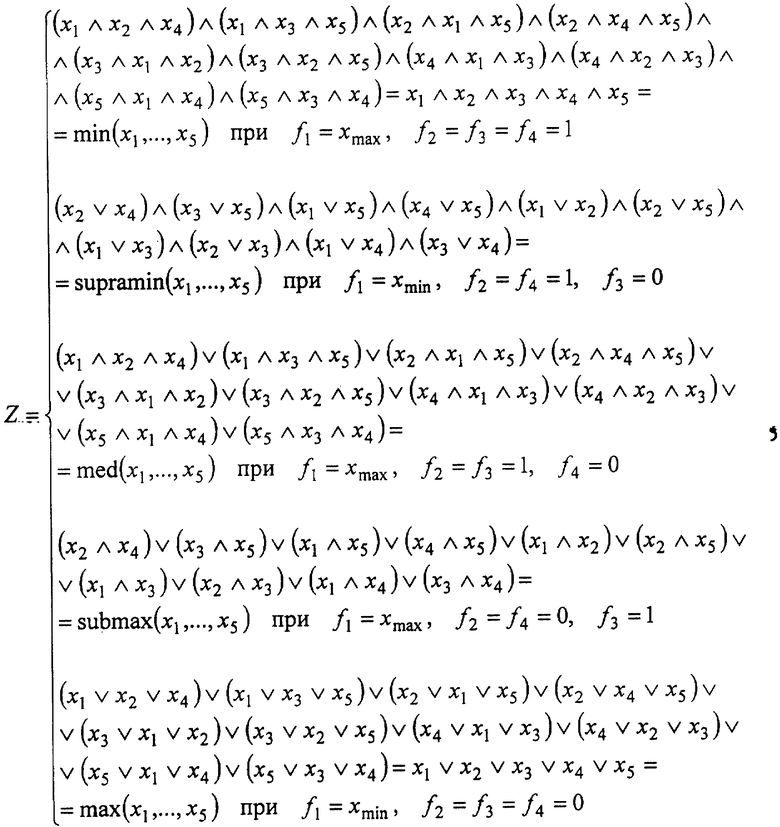

Работа предлагаемого аналогового процессора осуществляется следующим образом. На вторые входы реляторов 1i1, 1i2, 1i3 i-ой  группы подается соответственно неповторяющийся набор xi1, xi2, xi3, образованный тремя неповторяющимися сигналами из входного кортежа аналоговых сигналов x1, . . . x5 ∈ (xmin, xmax), причем x11=x21=x1, x31=x41=x2, x51=x61=x3, x71=x81= x4, x91=x(10)1=x5; на втором, третьем, четвертом и первом управляющих входах процессора фиксируются соответственно необходимые управляющие сигналы f2, f3, f4 ∈ {0,1} и f1 ∈ {xmin, xmax}. Если на входе управления релятора присутствует логический "0" (логическая "1") и сигнал на его первом входе больше либо меньше сигнала на его втором входе, то ключ 41 соответственно замкнут (разомкнут) либо разомкнут (замкнут), а ключ 42 соответственно разомкнут (замкнут) либо замкнут (разомкнут). Следовательно, если на входе управления релятора присутствует логический "0" (логическая "1"), то этот релятор будет выделять на своем выходе наибольший (наименьший) из сигналов, действующих на его первом и втором входах. Таким образом, операция воспроизводимая предлагаемым процессором определяется выражением, приведенным в конце описания, где символами

группы подается соответственно неповторяющийся набор xi1, xi2, xi3, образованный тремя неповторяющимися сигналами из входного кортежа аналоговых сигналов x1, . . . x5 ∈ (xmin, xmax), причем x11=x21=x1, x31=x41=x2, x51=x61=x3, x71=x81= x4, x91=x(10)1=x5; на втором, третьем, четвертом и первом управляющих входах процессора фиксируются соответственно необходимые управляющие сигналы f2, f3, f4 ∈ {0,1} и f1 ∈ {xmin, xmax}. Если на входе управления релятора присутствует логический "0" (логическая "1") и сигнал на его первом входе больше либо меньше сигнала на его втором входе, то ключ 41 соответственно замкнут (разомкнут) либо разомкнут (замкнут), а ключ 42 соответственно разомкнут (замкнут) либо замкнут (разомкнут). Следовательно, если на входе управления релятора присутствует логический "0" (логическая "1"), то этот релятор будет выделять на своем выходе наибольший (наименьший) из сигналов, действующих на его первом и втором входах. Таким образом, операция воспроизводимая предлагаемым процессором определяется выражением, приведенным в конце описания, где символами  и

и  обозначены соответственно операции max и min.

обозначены соответственно операции max и min.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый аналоговый процессор обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает выбор минимального, супраминимального, медианного, субмаксимального или максимального из пяти входных аналоговых сигналов.

Таким образом, вышеизложенные сведения свидетельствуют о выполнении при использовании заявленного устройства следующей совокупности условий:

- средство, воплощающее заявленное устройство при его осуществлении, предназначено для использования в промышленности, а именно в области автоматики и аналоговой вычислительной техники в качестве функционального узла аналоговых вычислительных машин, систем автоматического регулирования и управления и др.;

- для заявленного устройства в том виде, как оно охарактеризовано в независимом пункте изложенной формулы изобретения, подтверждена возможность его осуществления с помощью описанных в заявке или известных до даты приоритета средств и методов;

- средство, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Следовательно, заявленное изобретение соответствует условию "промышленная применимость".

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2005 |

|

RU2281550C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2011 |

|

RU2446462C1 |

| РАНГОВЫЙ ФИЛЬТР | 2001 |

|

RU2192045C1 |

| АНАЛОГОВЫЙ ПРОЦЕССОР | 2005 |

|

RU2281551C1 |

| РАНГОВЫЙ ФИЛЬТР | 2000 |

|

RU2171496C1 |

| РАНГОВЫЙ ПРЕДИКАТОР | 2001 |

|

RU2204861C1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ РАНГОВОЙ ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ | 1999 |

|

RU2143739C1 |

| РАНГОВЫЙ ФИЛЬТР | 2003 |

|

RU2230360C1 |

| РАНГОВЫЙ ФИЛЬТР | 2003 |

|

RU2229159C1 |

| РАНГОВЫЙ ПРЕДИКАТОР | 2001 |

|

RU2204862C1 |

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления. Техническим результатом является расширение функциональных возможностей за счет обеспечения выбора минимального, супраминимального, медианного, субмаксимального или максимального из пяти входных аналоговых сигналов. Устройство содержит регуляторы, каждый из которых состоит их компаратора, булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, замыкающего и размыкающего ключей. 2 ил.

Аналоговый процессор, содержащий два релятора, каждый из которых выполнен в виде компаратора, подключенного выходом к первому входу булевого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является входом управления релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей, выходы которых объединены и образуют выход релятора, первым и вторым входами которого являются соответственно неинвертирующий и инвертирующий входы компаратора, присоединенные соответственно к входам замыкающего и размыкающего ключей, отличающийся тем, что в него дополнительно введены n (n= 37) реляторов, причем все реляторы сгруппированы в одиннадцать групп так, что i-ая  и одиннадцатая группы содержат соответственно три и девять реляторов, первые входы первых реляторов первой,..., десятой групп объединены и образуют первый управляющий вход аналогового процессора, второй и третий управляющие входы которого образованы соответственно объединенными входами управления первых и объединенными входами управления вторых, третьих реляторов каждой i-ой

и одиннадцатая группы содержат соответственно три и девять реляторов, первые входы первых реляторов первой,..., десятой групп объединены и образуют первый управляющий вход аналогового процессора, второй и третий управляющие входы которого образованы соответственно объединенными входами управления первых и объединенными входами управления вторых, третьих реляторов каждой i-ой  группы, а четвертый управляющий вход подключен к входам управления первого,..., девятого реляторов одиннадцатой группы, в i-ой

группы, а четвертый управляющий вход подключен к входам управления первого,..., девятого реляторов одиннадцатой группы, в i-ой  группе выход первого и выход второго реляторов соединены соответственно с первым входом второго и первым входом третьего реляторов, выход третьего релятора первой группы и выходы третьих реляторов второй, ..., десятой групп подключены соответственно к первому входу первого и вторым входам первого,..., девятого реляторов одиннадцатой группы, в которой выход предыдущего релятора соединен с первым входом последующего релятора, а выход девятого релятора является выходом аналогового процессора.

группе выход первого и выход второго реляторов соединены соответственно с первым входом второго и первым входом третьего реляторов, выход третьего релятора первой группы и выходы третьих реляторов второй, ..., десятой групп подключены соответственно к первому входу первого и вторым входам первого,..., девятого реляторов одиннадцатой группы, в которой выход предыдущего релятора соединен с первым входом последующего релятора, а выход девятого релятора является выходом аналогового процессора.

| РАНГОВЫЙ ФИЛЬТР | 1996 |

|

RU2124754C1 |

| Устройство для ранжирования аналоговых сигналов | 1988 |

|

SU1541636A1 |

| Многопороговый функциональный преобразователь | 1988 |

|

SU1566378A2 |

| SU 1568061 A1, 30.05.1990 | |||

| ПОЗИЦИОННЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2149452C1 |

| ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ РАНГОВОЙ ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ | 1999 |

|

RU2143739C1 |

| US 5642070 А, 24.06.1997 | |||

| ВОЛГИН Л.И | |||

| Синтез устройств для обработки и преобразования информации в элементном базисе реляторов | |||

| - Таллинн: Валгус , 1989, с | |||

| Светоэлектрический измеритель длин и площадей | 1919 |

|

SU106A1 |

Авторы

Даты

2001-12-27—Публикация

2000-11-14—Подача