Изобретение относится к полупроводниковым интегральным микросхемам, нашедшим применение в аналоговых системах.

Известные аналоговые микросхемы, например, графические эквалайзеры, музыкальные синтезаторы, фильтры специального назначения, анализаторы спектра и т.п. используют конструкцию и техническое исполнение, включающие применение дискретных компонентов, размещенных на печатных платах. Такие схемы обычно громоздки, трудоемки в производстве, ненадежны и, как следствие, относительно дороги.

Аналоговые микросхемы вышеописанного типа изготавливаются в полупроводниковом интегральном исполнении, однако существуют трудности при использовании поточного промышленного производства при изготовлении интегральных микросхем с точными значениями резисторов и большими значениями емкостей. Тем не менее, интегральные микросхемы, такие как операционные усилители, генераторы и цепи фазовой автоподстройки существуют, но эти схемы имеют тот недостаток, что их надо специально изготавливать для каждого отдельного случая, что крайне дорого.

Известна также полупроводниковая интегральная схема, описанная в заявке Великобритании и опубликованная по классу G 06 G 7/06, N 2016767,1982 г., которая содержит множество аналоговых ячеек, соединенных друг с другом посредством внутренних цепей и образующих сеть, причем каждая ячейка выполнена с множеством внутренних схемных элементов; схему выборки и обращения ячеек, выполненную со схемой управления и средством генерирования сигнала выборки, причем средство генерирования сигнала выборки ячеек соединено с внутренними цепями. Известной полупроводниковой интегральной схеме присущи недостатки, указанные выше.

Задачей данного изобретения является преодоление указанных недостатков и проблем путем обеспечения относительно недорогих стандартных полупроводниковых интегральных микросхем, которые подходят для широкого применения, не требуя изменения в процессе изготовления таких интегральных микросхем.

Техническая задача согласно этому изобретению решается за счет того, что в известной полупроводниковой интегральной микросхеме каждая ячейка выполнена с переключающей схемой, соединенной с внутренними схемными элементами, а внутренние цепи соединяют ячейки и вход, на который поступают данные о состоянии (конфигурации) ячеек; сеть имеет первые информационные каналы (DD), выполненные с цепями переключающего воздействия (DD), присоединенными в каждой ячейке, а внутренние цепи выполнены с соединенными переключающими схемами (ISI, IS2, IS3, IS0) в каждой ячейке; каждая переключающая схема (ISI, IS2, IS3, IS0) выполнена со средством хранения конфигурационных данных (SRAM) и взаимосвязывающим транзисторным переключателем (TP); внутренние цепи содержат глобальную систему взаимной связи (HB, YB) и локальную систему взаимной связи между выходом каждой ячейки (OP) и входами (IPI, IP2) соседних ячеек; аналоговые ячейки (CL) имеют усилитель (OA), программируемые аналоговые компоненты (P/res, P/cap), переключающее средство (PT), два входа и один выход; аналоговые ячейки (CL) имеют форму сетки (A) и соединены в ряды горизонтальными шинами и в столбцы вертикальными шинами; средство генерирования сигнала (PSRH, PSRY) имеет два программирующих сдвиговых регистра, присоединенных к схеме управления (CC) и соединенных с горизонтальной и вертикальной шинами соответственно; глобальная система взаимной связи имеет горизонтальные глобальные шины (HB), идущие горизонтально между рядами аналоговых ячеек, и вертикальные глобальные шины (YB), идущие вертикально между столбцами аналоговых ячеек; вертикальные и горизонтальные глобальные шины (YB, HB) по краям сети присоединены к переключающим блокам (ES); по крайней мере один из программируемых аналоговых компонентов аналоговой ячейки представляет собой программируемый резисторный компонент (P/res) и представлен в виде пары согласованных характерных полевых транзисторов (M3, M4, M12, M13) с существенно идентичными электрофизическими параметрами, причем первый транзистор (M4-M13) является транзистором сравнения, а второй обеспечивает фактическую величину резистора; имеется дифференциальный усилитель (N/CC, P/CC), при этом регулируемый источник постоянного тока (CCS) присоединен в виде нагрузки к транзистору сравнения (M4-M13) с первым (1,5 В) и вторым (2,5 В) опорными потенциалами, причем транзистор сравнения (M4-M13) присоединен с образованием цепи отрицательной обратной связи у дифференциального усилителя (N/CC, P/СС); линейный резистор выполнен в виде дополнительной пары согласованных полевых транзисторов, причем вторые транзисторы каждой пары соединены параллельно; каждый программируемый резистор имеет резисторную сеть (R/BLK), включающую в себя совокупность пар (N-REI, P-REI...N/PE6, P/RE6) полевых транзисторов противоположной полярности и запоминающее средство (RAMB); сеть включает в себя вторые информационные каналы, связанные с аналоговыми ячейками (CL), и средство цифроаналогового преобразования, присоединенное к хранилищу конфигурационных данных и вторым информационным каналом (AD); регулируемый источник постоянного тока присоединен к вторым информационным каналам (AD); имеются программируемые конденсаторные компоненты (P/cap), выполненные по крайней мере с одной конденсаторной умножительной схемой (M1, M2); каждый транзистор противоположной полярности имеет присоединенную емкостную аналоговую схему (N/STR, P/STR), а внешний резистор (EPRI) и внешний конденсатор (ERCI) выполнены с возможностью их подключения к упомянутым аналоговым компонентам.

Согласно введению вышеперечисленных конструктивных особенностей в полупроводниковую интегральную схему обеспечивается достижениt технического результата в предложенном изобретении.

Изобретение будет более понятно из нижеследующего описания нескольких вариантов, вместе с прилагаемыми чертежами.

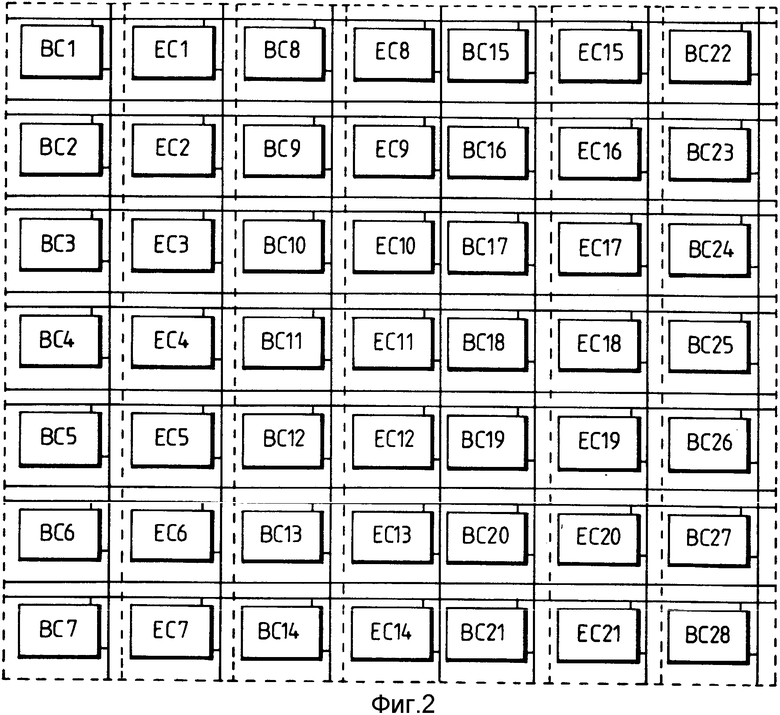

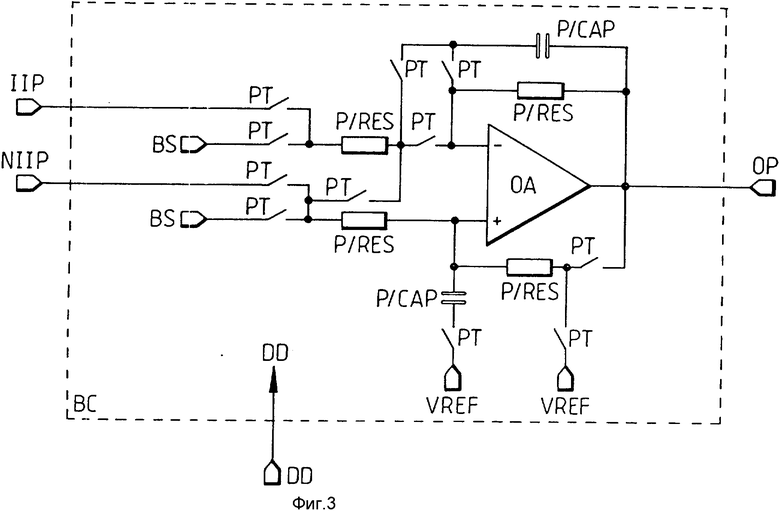

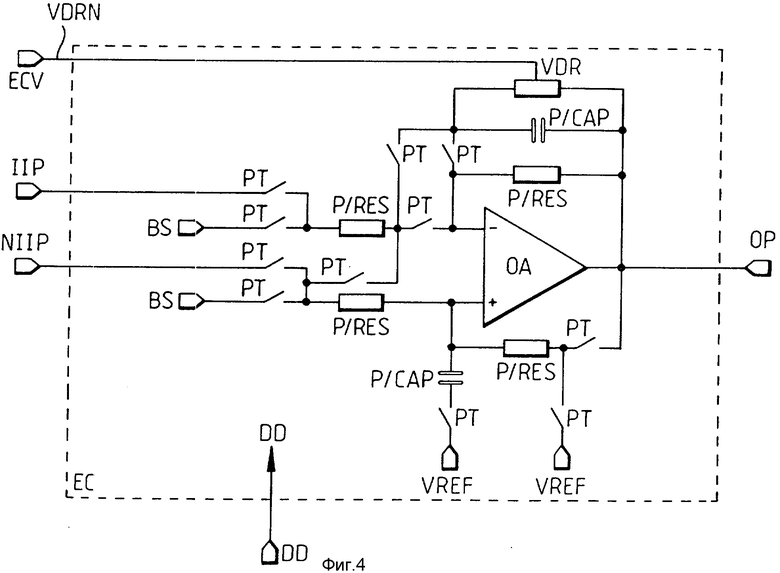

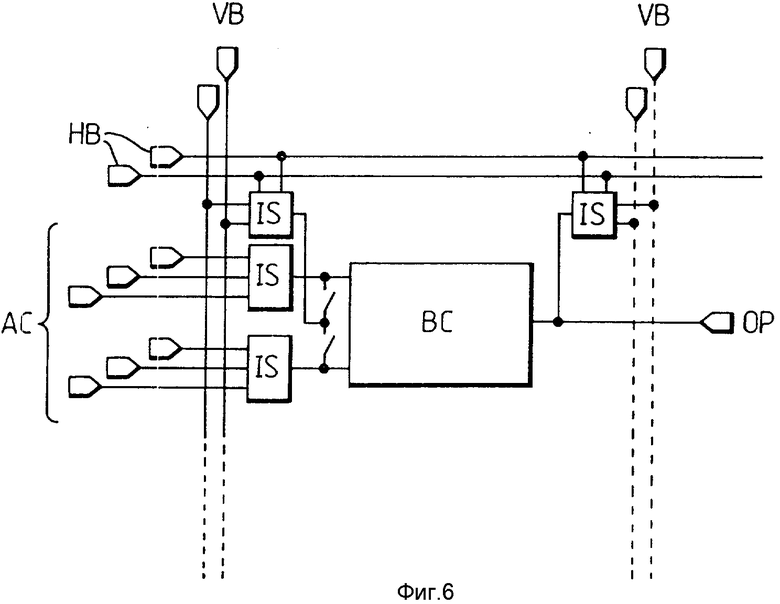

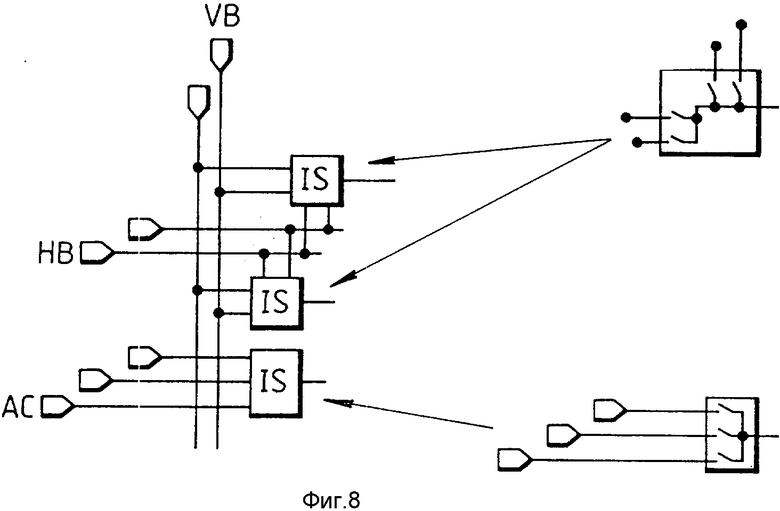

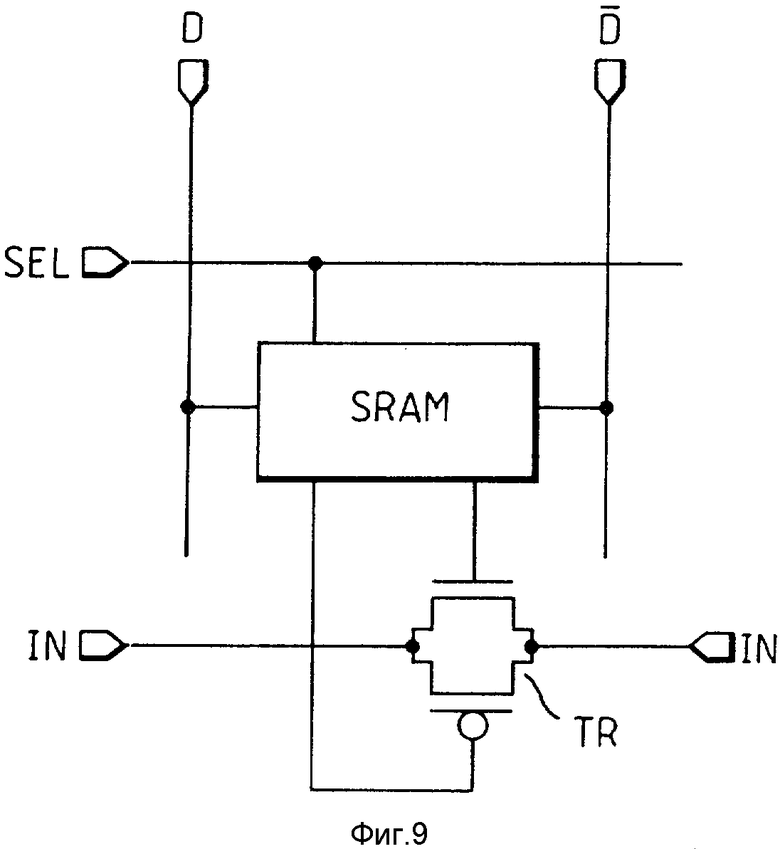

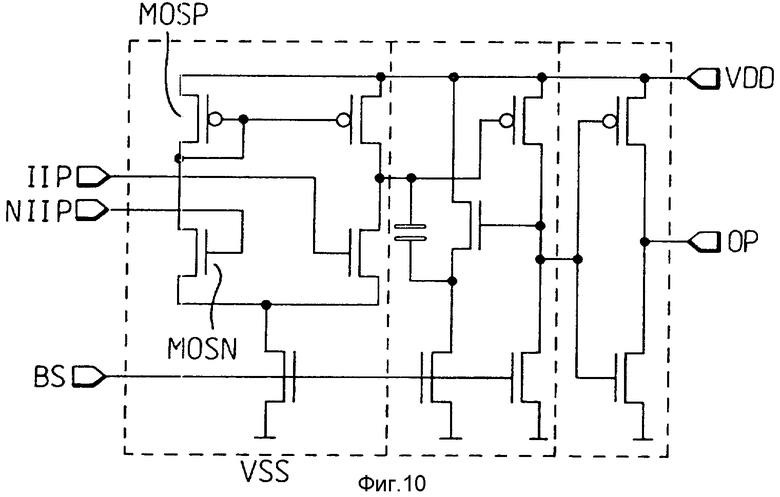

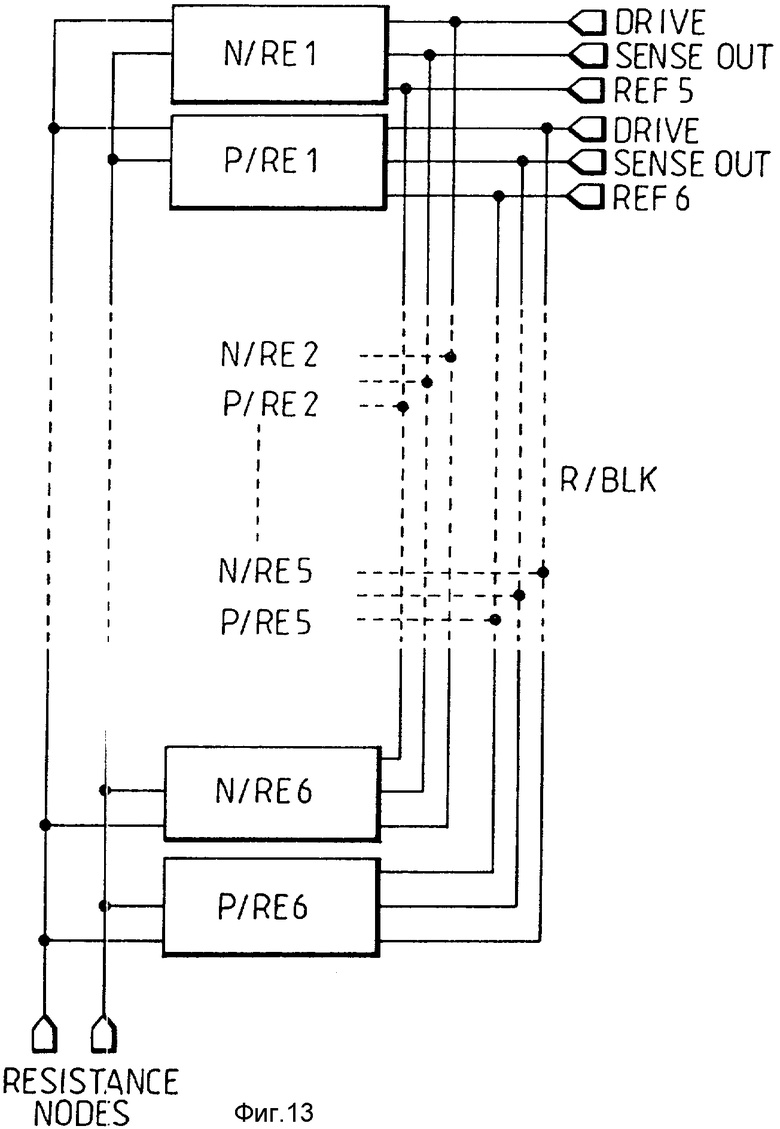

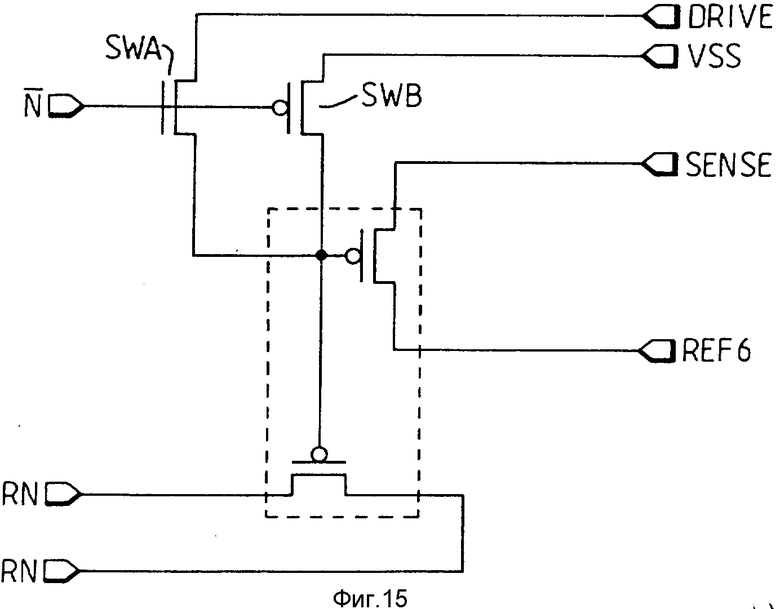

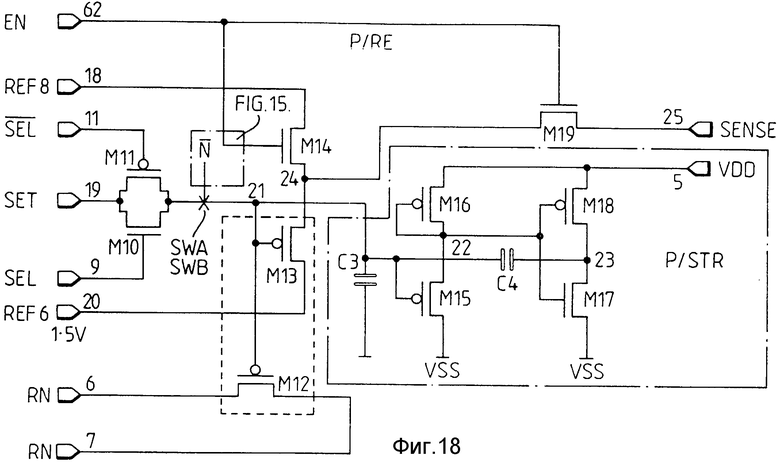

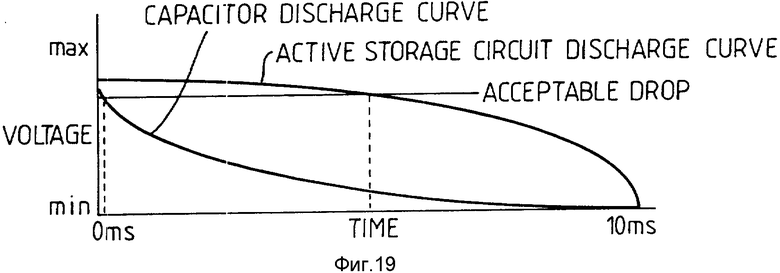

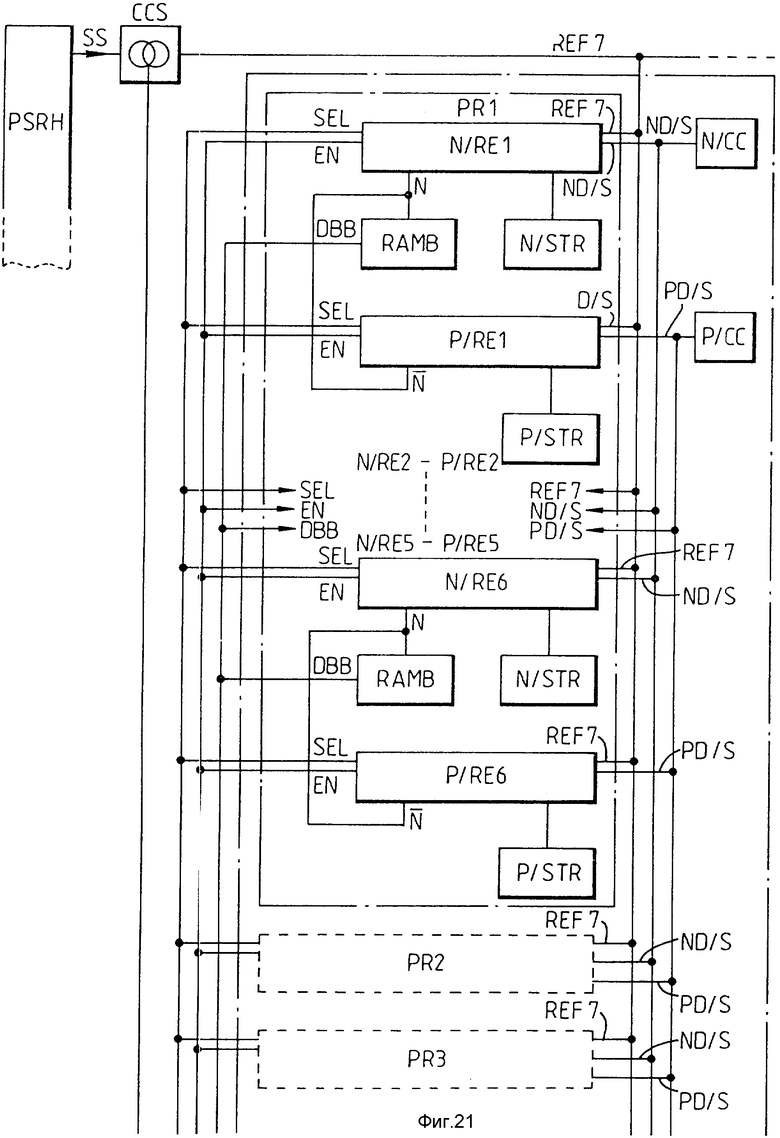

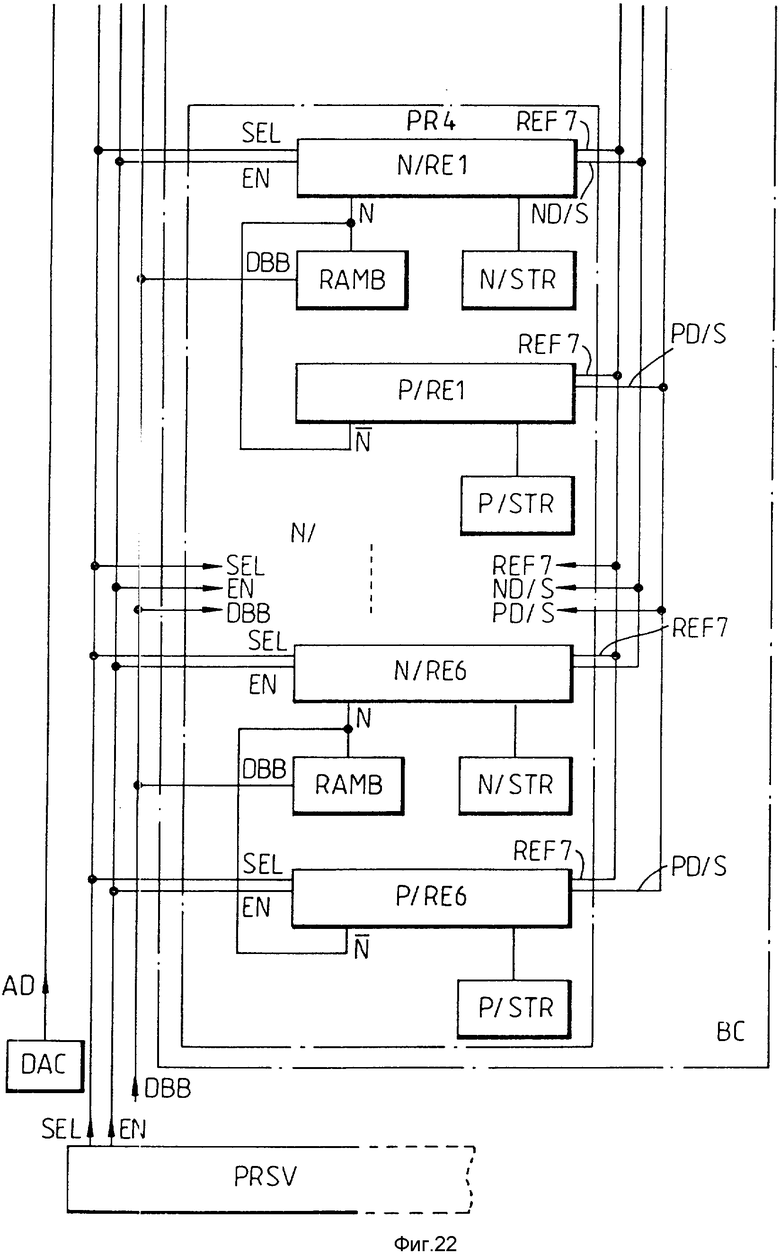

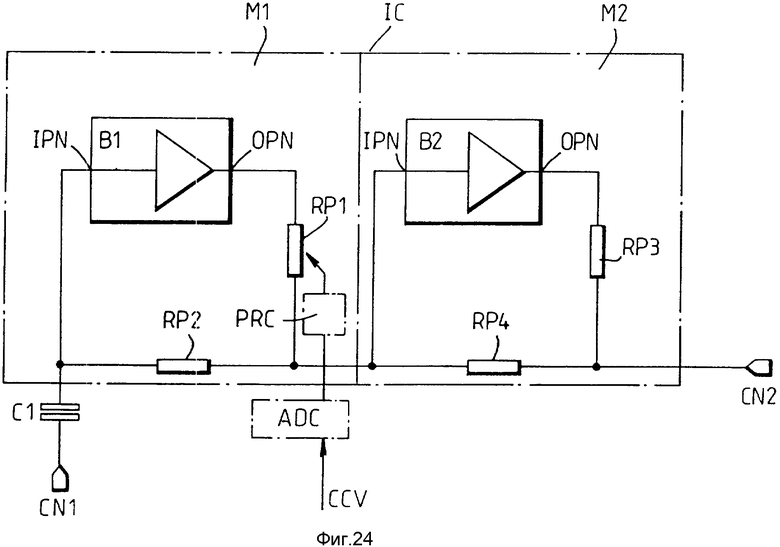

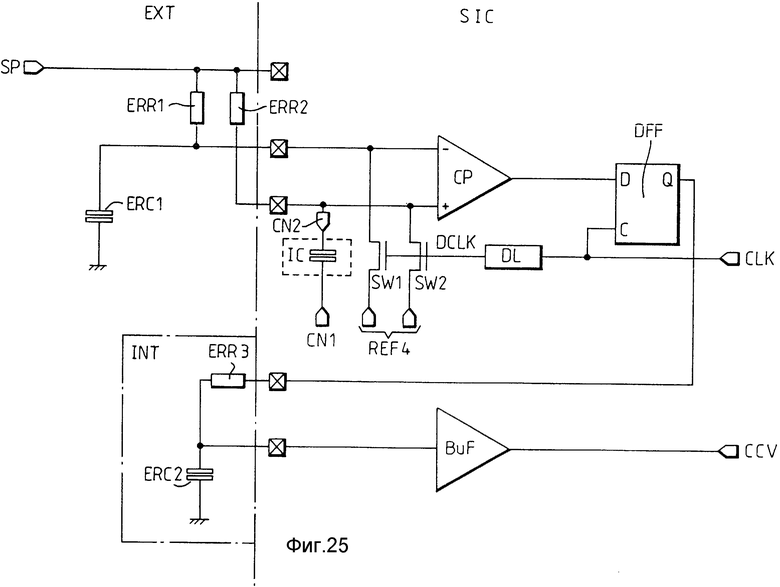

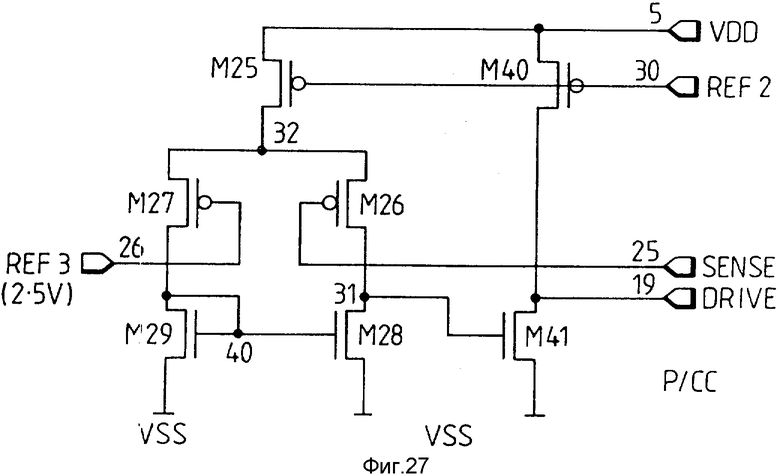

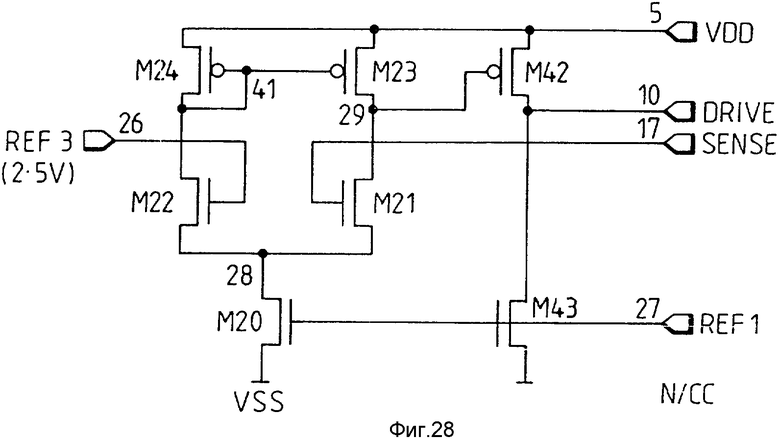

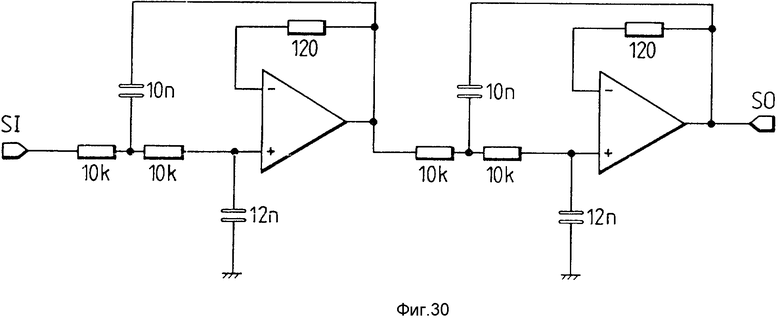

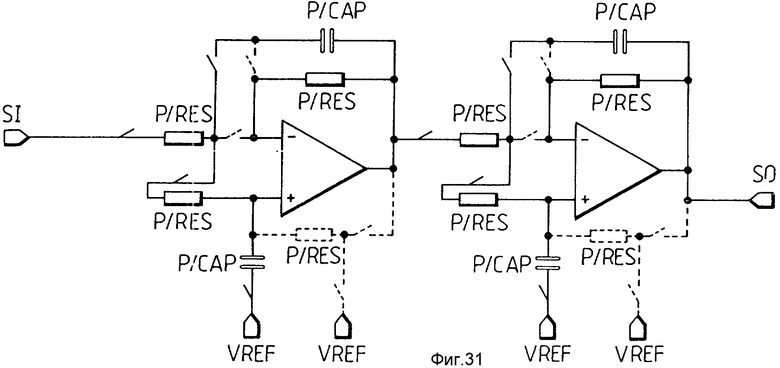

На фиг. 1 представлено схематическое изображение полупроводниковой интегральной микросхемы в форме линейной решетки согласно данному изобретению; на фиг. 2 - схема основной ячейки и увеличенных ячеек в линейной решетке; на фиг. 3 - схема основной ячейки; на фиг. 4 - схема увеличения ячейки; на фиг. 5 - часть решетки, где более подробно изображена общая схема соединения; на фиг. 6 - схема соединений вокруг основной ячейки; на фиг. 7 - схема соединений вокруг увеличенной ячейки; на фиг. 8 - в деталях переключатели соединений; на фиг. 9 - программируемая схема переключения с пропускным транзистором, управляемым ячейкой памяти оперативного запоминающего устройства; на фиг. 10 - ячейка схемы операционного усилителя; на фиг. 11 - схема цепи программируемого резистора; на фиг. 12 - схема программируемого резистора; на фиг. 13 - схема блока программируемого резистора; на фиг. 14 - программируемый резистор канала "п-типа" устройства переключения; на фиг. 15 - программируемый резистор канала "р-типа" устройства переключения; на фиг. 16 - схема программируемого резистора; на фиг. 17 - подробная схема программируемого резистора с каналом "n-типа"; на фиг. 18 - подробная схема программируемого резистора с каналом "p-типа"; на фиг. 19 - семейство кривых разряда; на фиг. 20 - принципиальная схема аналоговой программирующей схемы; на фиг. 21 и 22 - составляющие фиг. 23 показывают более подробно принципиальную схему типовой основной ячейки и ее схему программирования; на фиг. 24 - принципиальная схема многоконденсаторной цепи; на фиг. 25 - принципиальная схема конденсаторной цепи компенсации; на фиг. 26 - детальная схема аналогового буфера, используемого в цепи на фиг. 24; на фиг. 27 - подробная схема "p-канальной" управляющей цепи/дифференциальный усилитель; на фиг. 28 - подробная схема "n-канальной" управляющей цепи/дифференциальный усилитель; на фиг. 29 - принципиальная схема периферийного устройства ввода/вывода с программируемым коэффициентом передачи; на фиг. 30 - принципиальная схема фильтра низких частот, и на фиг. 31 - схема с фиг. 30, выполненная внутри решетки.

Согласно фиг. 1-31 полупроводниковая интегральная схема содержит множество аналоговых ячеек, соединенных друг с другом посредством внутренних цепей и образующих сеть, причем каждая ячейка выполнена с множеством внутренних схемных элементов; схему выборки и обращения ячеек, выполненную со схемой управления и средством генерирования сигнала выборки ячеек, причем средство генерирования сигнала выборки ячеек соединено с внутренними цепями, каждая ячейка выполнена с переключающей схемой, соединенной с внутренними схемными элементами, а внутренние цепи соединяют ячейки и вход, на который поступают данные о состоянии (конфигурации) ячеек; сеть имеет первые информационные каналы (DD), выполненные с цепями переключающего воздействия (DD), присоединенными к каждой ячейке, а внутренние цепи выполнены с соединенными переключающими схемами (ISI, IS2, IS3, IS0) в каждой ячейке; каждая переключающая схема (ISI, IS2, IS3, IS0) выполнена со средством хранения конфигурационных данных (SRAM) и взаимосвязывающим транзисторным переключателем (TR);

внутренние цепи содержат глобальную систему взаимной связи (HB, YB) и локальную систему взаимной связи между выходом каждой ячейки (OP) и входами (IPI, IP2) соседних ячеек; аналоговые ячейки (CL) имеют усилитель (OA), программируемые аналоговые компоненты (P/res, P/cap), переключающее средство (PT), два входа и один выход; аналоговые ячейки (CL) имеют форму сетки (A) и соединены в ряды горизонтальными шинами и в столбцы вертикальными шинами; средство генерирования сигнала (PSRH, PSRY) имеет два программирующих сдвиговых регистра, присоединенных к схеме управления (CC) и соединенных с горизонтальной и вертикальной шинами соответственно; глобальная система взаимной связи имеет горизонтальные глобальные шины (HB), идущие горизонтально между рядами аналоговых ячеек, и вертикальные глобальные шины (YB), идущие вертикально между столбцами аналоговых ячеек; вертикальные и горизонтальные глобальные шины (YB, HB) по краям сети присоединены к переключающим блокам (ES); по крайней мере один из программируемых аналоговых компонентов аналоговой ячейки представляет собой программируемый резисторный компонент (P/res) и представлен в виде пары согласованных характерных полевых транзисторов (M3, M4-M12, M13) с существенно идентичными электрофизическими параметрами, причем первый транзистор (M4-M13) является транзистором сравнения, а второй обеспечивает фактическую величину резистора; имеет дифференциальный усилитель (N/CC, P/CC), при этом регулируемый источник постоянного тока (CCS) присоединен в виде нагрузки к транзистору сравнения (M4-M13) с первым (1,5 В) и вторым (2,5 В) опорными потенциалами, причем транзистор сравнения (M4-M13) присоединен с образованием цепи отрицательной обратной связи у дифференциального усилителя (N/CC, P/CC); линейный резистор выполнен в виде дополняющей пары согласованных полевых транзисторов, причем вторые транзисторы каждой пары соединены параллельно;

каждый программируемый резистор имеет резисторную сеть (R/BLK), включающую в себя совокупность пар (N-REL, P-REI...N/RE6, P/RE6) полевых транзисторов противоположной полярности и запоминающее средство (RAMB); сеть включает в себя вторые информационные каналы, связанные с аналоговыми ячейками (CL), и средство цифроаналогового преобразования, присоединенное к хранилищу конфигурационных данных и вторым информационным каналом (AD); регулируемый источник постоянного тока присоединен к вторым информационным каналам (AD); имеет программируемые конденсаторные компоненты (P/cap), выполненные по крайней мере с одной конденсаторной умножительной схемой (M1, M2); каждый полевой транзистор противоположной полярности имеет присоединенную емкостную аналоговую запоминающую схему (N/STR, P/STR), а внешний резистор (EPRI) и внешний конденсатор (ERCI) выполнены с возможностью их подключения к упомянутым аналоговым компонентам.

Это изобретение обеспечивает типичное построение программируемой линейной решетки, содержащей операционные усилители, использующие полупроводниковые МОП-полевые транзисторы, конденсаторы, резисторы, резисторы зависящие от напряжения, и переключателя, выполненные в полупроводниковой интегральной форме. Решетка содержит сорок девять ячеек (28 основных и 21 увеличенных), включающих операционные усилители с изменяемым подсоединением, позволяющим пользователю реализовать сложные аналоговые функциональные схемы. Программируемые резисторы и конденсаторы служат для обеспечения разработчиками возможности создания различных аналоговых схем.

Из чертежей становится понятно, что все буквенные обозначения RN на чертежах соответствуют двум узлам программируемого резистора. На фиг. 1 видно, что ячейки CL составлены в столбцы, образуя решетку семь на семь, и эти ячейки соединяются при помощи цепи соединения. Цепь соединения содержит линии шин, идущих вертикально и горизонтально между рядами и столбцами ячеек. Четыре общие линии шин VB (фиг. 5) идут вертикально между столбцами ячеек, и две общие линии шин HB (фиг. 5) проходят горизонтально между рядами. Ячейки могут быть прямо подсоединены к каждой из этих шин при помощи переключающих элементов IS1, IS2, IS3 и IS0. Кроме того, на краях решетки блоки переключения (обозначенные ES на фиг. 5) позволяют прямо подключать горизонтальные и вертикальные шины.

Более ста 5-нанофарадных конденсаторов может быть выполнено при использовании многоконденсаторной технологии, и более двухсот резисторов может быть запрограммировано в диапазоне значений между 10 и 640 килоомами. Функции умножителя могут быть выполнены, используя комбинации резисторов, зависящих от напряжения и операционных усилителей.

Допустимые отклонения при производстве компонентов могут автоматически компенсироваться для надежной работы. Все внутренние программируемые резисторы и конденсаторы компенсируются одним внешним резистором и конденсатором.

Устройство является подходящим для использования в широком диапазоне аналоговых функций, включая замещение большинства существующих низкочастотных аналоговых интегральных микросхем (IC), и обеспечивает высокий уровень интеграции, используя новую схемотехнику.

Аналоговые интегральные микросхемы, требующие высоких значений емкостей и сопротивлений, имеют ограниченную степень интеграции вследствие того, что очень большая площадь кремния требуется для изготовления этих пассивных компонентов (элементов). Например, один однонанофарадный конденсатор обычно занимает всю площадь кристалла.

Поэтому программируемые резисторы обычно выполняются с использованием метода переключаемых конденсаторов. Однако этот подход имеет ограниченное применение для программируемых устройств, так как каждый резистор требует отдельного источника импульсов для получения подходящего сопротивления. Более того, метод переключаемых конденсаторов снижает широкополосность устройства.

Ниже перечислены некоторые типичные аналоговые функциональные устройства, использующие эту схему:

Графические эквалайзеры

Звуковые музыкальные синтезаторы

Звуковые микшерские пульты

Фильтры специального назначения

Анализаторы спектра

Генераторы сигналов

Макетирование

Автоматическая телефонная связь

Замещение НЧ линейных интегральных микросхем

Образование

На фиг. 1 показано устройство в плане. Устройство содержит решетку A из программируемых аналоговых ячеек CL, каждая из которых содержит динамическую аналоговую схемотехнику, что требует регенерации для поддержания конфигурации схемы и значения компонентов. Данные конфигурации содержатся в оперативном запоминающем устройстве (ОЗУ) емкостью 4800 бит на кристаллах. Этот источник данных конфигурации постоянно считывается для обеспечения регенерации.

Данные конфигурации, которые записываются в оперативное запоминающее устройство ОЗУ, могут изменяться от внешнего источника для получения новой схемы, которая требуется, внутри решетки.

Если потребуется, после отключения питания питание оперативного запоминающего устройства ОЗУ для хранения данных конфигурации схемы может осуществляться от батареи. Миниатюрная батарея питания может быть размещена внутри интегральной микросхемы.

Данные конфигурации схемы определяют последовательность выбора внутренних соединений ячеек CL при помощи программирующих регистров сдвига PSRH и PSRV под управлением устройства управления CC. Эти данные конфигурации подаются к соединяющим элементам и программируемым элементам и программируемым элементам в цифровой форме по первым каналам передачи данных DD. Значения компонентов, записанные в цифровой форме в оперативное запоминающее устройство ОЗУ, подаются к программируемым элементам по вторым каналам передачи данных AD в аналоговой форме, полученной через цифроаналоговый преобразователь ЦАП. Каждый программируемый элемент имеет отдельную адресуемую схему выборки и хранения, например, переключателя M1 и M2, вместе с аналоговой схемой записи N/STR и P/STR, и данные конфигурации записываются в каждую схему выборки и хранения последовательно.

Хотя в настоящем варианте изобретения программирующие регистры сдвига PSRH и PSRV, цифроаналоговый преобразователь ЦАП, оперативное запоминающее устройство ОЗУ и схема управления CC выполнены в полупроводниковой интегральной микросхеме в виде решетки из ячеек, возможно, если потребуется, включить эти компоненты в отдельную интегральную микросхему.

Схема выборки и хранения /N/STR, P/STR/ управляет программируемым резистором, зависящим от напряжения, и каждый резистор отдельно компенсируется, делая поправку на отклонения при производстве и температурные изменения. Каждый программируемый резистор выполняется как пара (комплементарная пара) МОП-транзисторов. Каждый транзистор пары имеет второй согласованный транзистор, образуя часть схемы, фазовой автоподстройки, управляемой напряжением.

Конденсаторы выполняются со значениями 5 пикофарад. Значение этих конденсаторов затем умножаются в каждом случае двумя преобразователями сопротивления до конечного значения в 5 нанофарад. Каждая стадия (х33) содержит буфер и два программируемых резистора.

В решетке находятся двадцать восемь основных ячеек от BCI до BC28 и двадцать одна расширенная ячейка от ECI до EC21 (фиг. 2). Каждая основная ячейка BC (фиг. 3) содержит один операционный усилитель общего назначения ОУ (OA), четыре программируемых резистора п/рез и два программируемых конденсатора а/кон. Каждая расширенная ячейка EC (фиг. 4) содержит один быстродействующий операционный усилитель ОУ, четыре программируемых резистора п/рез, два программируемых конденсатора п/кон, и один резистор, зависящий от напряжения VDR, который может служить в качестве аналогового переключателя. Как основные ячейки BC, так и расширенные ячейки EC инвертирующий вход NP и неинвертирующий вход NIIP, и каждая объединяет напряжение смещения BS вместе с источником опорного напряжения VPEF. Выход OP осуществляется из каждой ячейки с помощью операционного усилителя OA. Каждый операционный усилитель OA расширенной ячейки может также использоваться как компаратор, линейный интегратор, или как умножитель, когда он применяется вместе с резистором, зависящим от напряжения, или с аналоговым переключателем. Это особенно полезно при сжатии, управления усилением и модуляции. Фиг. 10 показывает схему операционного усилителя ячейки стандартного типа, включающего полевые транзисторы МОП-типа, как с n-, так и с p-проводимостью, и имеющего не инвертирующий вход NIIP, инвертирующий вход NP и выход OP. VSS и VDD представляют собой источники напряжения, а BS является напряжением смещения.

Используя резисторы, зависящие от напряжения, VDR в расширенных ячейках EC, внешние напряжения EC могут прикладываться к узлу резистора, зависящего от напряжения VDRN (фиг. 7) для управления характеристиками внутренней схемы в пределах ячейки EC. Например, при использовании решетки для выполнения двадцатиканального графического эквалайзера внешние потенциометры не будут нести аудиосигналы к и от решетки, а только управляющие напряжения.

Схема соединений.

В то время, как каждая ячейка может быть сформирована для требуемого функционального использования схемы путем программирования внутренних резисторов и конденсаторов и соединения источников через каналы передачи сигналов с использованием пропускных транзисторов PT, в пределах решетки существует общая система соединений, состоящая из металлизированных соединительных дорожек, которые используются для соединения ячеек на всех расстояниях внутри решетки, т. е. не соседних ячеек. Местные соединения организованы через местную систему соединений, где выход каждой ячейки соединяется с входом каждой соседней ячейки в пределах решетки. Фиг. 5, фиг. 6 и 7 показывают общую систему соединений и местную систему соединений для основной BC и расширенной EC ячеек соответственно. Фиг. 8 подробно показывает схему переключения соединения IS.

Каждое соединение физически связано с каждой ячейкой, используя пару пропускных транзисторов n- и p-проводимости, управляемых с помощью переключающего запоминающего устройства в форме статического оперативного запоминающего устройства SRAM. Фиг. 9 показывает пропускной транзистор TP и связанное с ним оперативное запоминающее устройство SRAM, образующих программируемую схему переключений. Шины данных или тракты управления переключением, образующие часть вышеупомянутых первых каналов передачи данных, для управления этой схемой переключения, обозначены буквами D и  (фиг. 5). Каждое переключение может быть выбрано с помощью линии SEL. Соединения IN представляют собой узлы соединений.

(фиг. 5). Каждое переключение может быть выбрано с помощью линии SEL. Соединения IN представляют собой узлы соединений.

Ячейки в пределах устройства размещены вместе со средствами соединений и блоками переключений. Каждая ячейка ВС (фиг. 5) ассоциирует с двумя входами сигналов IP1 и IP2, тремя блоками переключений IS1, IS2 и IS3, причем IS1 и IS2 могут локально соединяться с другими ячейками (прилегающими ячейками AC), а IS3 может соединяться с общей шиной HB и VB. Выход каждой ячейки OP напрямую соединяется с блоками переключения прилегающей ячейки и, кроме того, соединяется с блоком переключений 1 0, способным направлять выходные сигналы на общую шину HB и VB.

Программируемые резисторы.

Программируемый резистор состоит из программируемых резисторных элементов, зависящих от напряжения, причем каждый элемент состоит из пары комплементарных МОП-транзисторов.

Фиг. 11 и 12 показывают общее устройство для программирования каждого элемента. Следует отметить, что на фиг. 12 части схемы с фиг. 17 и 18 обозначены так же, как и на вышеупомянутых фигурах.

На фиг. 11 N/CC и P/CC дифференциальными усилителями, в то время, как PR1, PR2, PR3 ... составляют цепь программируемых резисторов R/BLK, фиг. 12, 13. Каждая цепь программируемого резистора имеет ассоциирующие с ней два узла аналоговой записи N/TP и P/STR (фиг. 12). Каждая ячейка (BC, EC) содержит два дифференциальных усилителя, которые последовательно устанавливают нужное управляющее напряжение возбуждения для программируемых резисторов, зависящих от напряжения. Узлы аналоговой записи N/STP и P/STR хранят управляющее напряжение возбуждения для программируемого резистора, что дает возможность дифференциальным усилителям N/CC и P/CC устанавливать другие программируемые элементы. Детали схемы дифференциальных усилителей показаны на фиг.27 и 28.

Фиг. 14 и 15 показывают программируемые резисторные элементы основного p- и n-типа соответственно. Каждый резисторный элемент способен обеспечивать тридцать два значения сопротивлений в диапазоне 2:1, например, от десяти до двадцати килоом с шагом 32, например, 10 к 10.31к 10.62к и т.д.

Каждый программируемый резистор выполняется ( фиг. 13) как шесть пар резисторных элементов p- и n-типа N/RE1, P/RE1 до N/RE6, P/RE6, лежащими в диапазоне значений от 10 до 640 кОм. Каждый элемент соединяется параллельно с предыдущим элементом и удваивает его величину, например, от 10 до 20 кОм, от 20 до 40 кОм и т.д.

На фиг. 20 показаны основные требования для выбора определенной ячейки CL в решетке A. Во-первых, соответствующий ряд выбирается, и соответственно определенный постоянный ток CCS, с помощью сигналов выбора от регистра сдвига PSRH, после чего определенный уровень тока, относящийся к определенному желаемому сопротивлению внутри определенного диапазона значений, программируется выбранным источником постоянного тока CCS с помощью вторых каналов передачи данных AD при помощи цифроаналогового преобразователя DAC, который в свою очередь программируется с помощью оперативного запоминающего устройства RAM (фиг. 1). Таким способом определяется координатный опорный сигнал внутри решетки. Во-вторых, регистр сдвига PRSV обеспечивает сигнал подготовки EN и сигнал выбора SEL, который служит в качестве координатного опорного сигнала внутри решетки. Определенный сигнал подготовки EN вместе с сигналом выбора SEL/SEL /EN/ служат для выбора одного из резисторов (от PRI до PR4), программируемых с помощью тока от источника постоянного тока CCS. Это достигается в течение процесса программирования, в котором одна пара резисторов из шести пар резисторов в резисторной цепи выбранного резистора выбирается с помощью данных конфигурации ячейки, снимаемых с шины данных DBB, образующей часть первых каналов передачи данных, и которая записывается в оперативное запоминающее устройство RAMB ( фиг. 14, фиг. 21, фиг. 22). Не выбранные резистивные элементы отключаются от схемы.

На фиг. 21 и 22, которые следует расположить, как показано на фиг. 23, показано основное (общее) устройство основной ячейки BC с четырьмя программируемыми резисторами от PR1 до PR4 (P/рез, фиг. 3), каждый из которых принимает форму цепи R/BLK, как показано на фиг. 13.

Каждый резистор содержит шесть пар резистивных элементов, вышеупомянутых N/RE1, P/RE1 до N/RE6, P/RE6, причем каждый имеет связанную с ним аналоговую запись N/STR, P/STR, как было указано выше. Любая пара резисторов и, следовательно, определенный диапазон значений резистора могут быть выбраны данными с шины данных DBB, которые записаны в оперативное запоминающее устройство RAMB. Переключатели SWA и SWB (фиг. 14 и 15) служат для включения соответствующей пары. Эффект этого включения схематично показан на фиг. 17 и 18, где вход возбуждения DRIVE (10, 16; фиг. 16) и вход установки SET (10, 19; фиг. 17, 18) могут управляться переключающими переключателями SWA и SWB.

На фиг. 21 и 22 показаны горизонтальный (CC S, REF 7) координатный опорный сигнал и вертикальный (EN, EI) координатный опорный сигнал вместе с вышеупомянутыми дифференциальными усилителями N/CC и P/CC, которые обслуживают всю ячейку и обеспечивают необходимые сигналы возбуждения и считывания (ND/S, PD/S) для установки резистивного элемента на желаемое значение в выбранном диапазоне.

При постепенном перемещении регистров сдвига PSPH и PSPV различные компоненты во всех ячейках могут быть программированы и установлены последовательно. Например, сперва устанавливается (выбирается) первый ряд, затем второй и так далее для всех последовательных рядов; затем следует последовательный выбор каждого столбца, причем каждый компонент программируется и устанавливается в выбранных ячейках последовательно, удваивая свою величину, например, от 10 до 20 кОм, от 20 до 40 кОм и т.д.

Во время программирования одна пара из шести выбирается с помощью данных, записанных в оперативное запоминающее устройство RAMB. Невыбранные резистивные элементы отключаются.

Дальнейшая работа схемы программируемого резистора изображена на фиг. 16. N/CC и P/CC - дифференциальные усилители, в то время, как N/PE и P/EE - два программируемых резистивных элемента в цепи. На фиг. 16 и фиг. 17 видно, что выход дифференциального усилителя N/CC служит для возбуждения (SET, 10) затвора транзистора n-типа M4 через переключатель, образованный транзисторами M1 и M2. Соединение истока транзистора M4 имеет опорный потенциал в 1,5 В (REF5), а сток M4 подсоединен к транзистору M5, который в свою очередь соединен с источником постоянного тока на выходе (REF 7). Узел M4 и M5 соединяется с неинвертирующим входом (17, SEN SE - фиг. 28) дифференциального усилителя N/CC через транзистор M33 (фиг. 17), а инвертирующий вход (26, REF 3 - фиг. 28) дифференциального усилителя соединен с опорным потенциалом в 2,5 В.

Программируемый резистор выполнен вместе с транзистором M3. Возбуждение затвора M3 определяется потенциалом затвора M4, который является частью цепи отрицательной обратной связи дифференциального усилителя N/CC (фиг. 17, 28).

Для программирования резистора на требуемое значение источник постоянного тока CCS (фиг. 20) перестраивается до соответствующей установки тока (0,1 мА для 10 кОм, 0,01 мА для 100 кОм и т.д.), до тех пор, пока не произойдет стабилизация цепи отрицательной обратной связи. Стабильное состояние дифференциального усилителя достигается при установлении на обоих его входах одного и того же потенциала (2,5 В). В этот момент падение напряжения в транзисторе M4 равно 1 В (2,5-1,5, REF 5). Транзистор M4 будет тогда иметь ток стока, равный току постоянного источника тока. Потенциал на затворе транзистора M4 теперь находится на уровне требуемой проводимости транзистора M4. Поскольку потенциал затвора транзистора M4 также приложен к транзистору M3, транзистор M3 будет также программирован или установлен на требуемое сопротивление.

На фиг. 13,17 и 18 видно, что транзистор p-типа M12 параллельно соединен с транзистором M3 n-типа. Транзистор M12 со своей схемой выполняет сходную функцию по отношению к транзистору M3, и ассоциирующая схема (кроме самого транзистора M12) будет иметь обратные характеристики относительно транзистора M3. Для выполнения программируемого резистора оба транзистора должны обеспечивать линейную функцию передачи.

Режим аналоговой записи.

Когда установлено требуемое возбуждение для транзистора M4, транзисторы M1 и M2 отключаются, а потенциал затвора M4 поддерживается на конденсаторах C1 (200 фФ) и C2 (400 фФ) до тех пор, пока он не регенерируется несколькими секундами позже. Требуется два транзистора для переключения возбуждения затвора на M4 для избежания разрушения напряжения, накопленного на C1 и C2 благодаря емкостной связи возбуждающих сигналов на затворах переключающих транзисторов M1 и M2.

Потенциал, приложенный к затвору транзистора M4, также прикладывается к конденсаторной записывающей схеме, образованной транзисторами от M6 до M9 и конденсаторами C1 и C2.

N/STR, P/STR показывают схемы записи (фиг. 17 и 18). Транзисторы M8 и M9 образуют инвертирующий усилитель. Обычный усилитель способен работать только с половинным уровнем мощности, транзисторы M6 и M7 обеспечивают преобразование уровня напряжения, для того чтобы запоминающая схема могла работать при напряжениях, приближающихся к VDD. Для программируемого резистивного элемента p-типа требуется записывающая схема, работающая с напряжением около VSS.

Фиг. 19 показывает характеристику разряда записывающей схемы по сравнению с обычной конденсаторной схемой одинаковой емкости, а также ясно видно, что наблюдается улучшение в периоде сохранности записи при сохранении приемлемого напряжения.

Записывающая схема требуется для поддержания этого аналогичного потенциала, в то время как программирующая схема устанавливает другие резисторы в решетке. Активная записывающая схема формирует инверсную нормальную экспоненциальную характеристику разряда конденсатора и резистора. Запоминающая схема также препятствует модуляции напряжения затвора, вызываемой емкостной связью между затвором и истоком или стоком транзистора M3 или M12.

Конденсатор, используемый для запоминания напряжения возбуждения затвора транзисторов M3 и M4, должен удерживать заряд без заметного снижения до следующего периода регенерации (1 мс). Любые изменения заряда конденсатора будет вызывать изменение сопротивления транзистора M4, и что более важно, транзистора M3. Это ведет к полной неработоспособности схемы. Если схема применяется в качестве фильтра, то соответствующие характеристики могут быть изменены, например, изменяется усиление или фаза. Если схема имеет высокий коэффициент усиления, она может быть применена как генератор.

Влияние изменения сопротивления в транзисторе M4 не такое же, как постоянное отклонение сопротивления, поскольку сопротивление будет динамично изменяться вместе с частотой регенерации. Это обеспечит частоту 1 кГц в точке подсоединения его к схеме.

Программирование.

Вернемся к фиг. 20, которая показывает общую программирующую схему. Цифроаналоговый преобразователь DAC вырабатывает напряжение, пропорциональное требуемому сопротивлению или емкости для каждого элемента ячейки. Выход цифроаналогового преобразователя DAS преобразуется в источник постоянного тока CCS, с которого ток поступает на общую нагрузку (REF 7) для обеспечения выбранной ячейки подходящим током программирования. Цифроаналоговый преобразователь DAC управляется оперативным запоминающим устройством RAM на кристаллах (фиг. 1), которое содержит данные конфигурации и значения компонентов в цифровой форме. Следует отметить, что все программируемые элементы в решетке последовательно регенерируются для поддержания правильных значений отдельных компонентов.

Программируемые конденсаторы.

На чертежах, особенно на фиг. 24, которая изображает схему программируемого конденсатора, показано, что конденсаторы выполняются с помощью конденсаторной умножительной технологии. Программируемые конденсаторы содержат в основном три элемента, конденсатор C1 и один или два конденсаторных умножителя M1 и M2. Они подсоединены между узлами CN1 и CN2.

Поскольку невозможно изготовить одну сотню пятинанофарадных конденсаторов, маленький конденсатор C1 (пятипикофарадный) изготовляется, а эквивалент желаемой емкости получается с помощью процесса преобразования сопротивления.

Пятипикофарадный конденсатор C1 подключается к выходу первого буфера B1. Программируемые резисторы RP1 и RP2 (резисторы, чьи значения могут изменяться, как потребуется) соединяются в ряд между входом и выходом первого буфера B1, причем выход снимается между первым и вторым программируемым резисторами. При таком построении компонентов отношение установленных значений двух программируемых резисторов RP2 и RP1 определяет число, на которое умножается значение емкости C1.

Установленное значение сопротивления RP2 выше, чем установленное значение сопротивления RPI, поэтому соединение резисторов RP1 и RP2 приводит к умножению, и общая величина эффективной емкости равна (RP2/RP1)xC1. Эффективная емкость от соединения резисторов RP1 и RP2 далее умножается на второй стадии умножителем M2, включающим программируемые резисторы RP3 и RP4 и буфер B2. Таким образом, конечная эффективная емкость от соединения резисторов RP3 и PR4 приблизительно равняется (RP2/RP1)x(RP4/RP3)xC1. Эта вторая стадия умножения необходима, если требуются более высокие значения емкостей для того, чтобы избежать явления паразитной емкости, наблюдаемого в программируемых резисторах с более высокими значениями сопротивлений, требуемых для производства конденсаторов с высокими значениями емкости.

Программируемые резисторы RP2 и RP4 применяются для программирования конечной емкости, в то время как резистор RP1 управлятся опорным сигналом CCV (фиг. 24 и 25) для компенсации отклонений при производстве/установке конденсатора C1.

Главным недостатком схемы такого типа является то, что не могут быть получены высокодобротные конденсаторы. Однако для большинства случаев применения конденсаторов, произведенных таким способом, это не является главным недостатком, так как конденсаторный умножитель имеет последовательное сопротивление, которое приблизительно равно величине резистора RP3.

Конденсаторная цепь компенсации, показанная на фиг. 25 и включающая внешнюю секцию EXT и секцию полупроводниковой интегральной микросхемы SIC, обеспечивает опорное управляющее напряжение CCV конденсаторного умножителя, который управляет программируемым резистором RP1. Таким образом, разброс значений толщины оксидной пленки пятипикофарадного конденсатора C1 автоматически компенсируется.

Питающее напряжение прикладывается к точке SP, и при работе оно используется для схемы синхронизации, чтобы сравнить постоянные времени двух отдельных, но в основном одинаковых емкостей/резистивных схем. Схема с одной постоянной времени использует точный внешний пятинанофарадный конденсатор ERC1 вместе с внешним резистором ERP1 известной величины, а схема с другой постоянной времени использует внутренний конденсатор IC (типа показанного на фиг. 24) со значением, равным 5 нанофарадам (получаемого умножением значения внутреннего конденсатора в 5 пикофарад) вместе с внешним резистором ERP2.

Два конденсатора IC и ERC1 заряжаются и разряжаются неоднократно путем переключения переключателей SW1 и SW2 под управлением сигналов синхронизации DCLK, которые являются сигналами синхронизации CLK, задержанными с помощью линий задержки DL. Соединители REF4 на переключателях SW1 и SW2 подсоединяются к нулевому напряжению.

Во время действия задержанных сигналов синхронизации DCLK компаратор CP неоднократно сравнивает напряжения на конденсаторах IC и ERC1 для определения, конденсатора, заряжающегося быстрее, и результирующий выход компаратора задерживается/запоминается триггером D-типа.

Во время действия сигналов синхронизации CLK выход Q триггера DFF (предыдущей выход сигнала сравнения, соответствующий времени, непосредственно предшествующему сигналу синхронизации CLK) является выходом к интегратору INT, содержащему внешний конденсатор ERC2 и внешний резистор ERR3, который интегрирует последовательные выходные сигналы с Q. Выход интегратора IC проходит через второй буфер ВИГ для обеспечения опорного сигнала CCV (аналоговый сигнал), который в свою очередь обеспечивает управление изменением значений резистора RP1 в умножителе M1, и таким образом изменяет отношение RP2/RP1, а следовательно, и эффективное значение емкости IC.

Следует понимать, что аналогичный сигнал CCV требует преобразования в эквивалентную цифровую форму для воздействия на схему для изменения величины резистора RP1. Это может быть достигнуто с помощью подходящего аналого-цифрового преобразователя ADC, подключенного между входом второго буфера BUF и входом схемы PRC для управления программируемым резистором RP1.

Так, в работе этот процесс имеет место, когда интегратор постоянно воздействует на аналоговый сигнал CCV, который в свою очередь изменяет величину резистора RP1 и величину конденсатора IC. Данный процесс продолжается до тех пор, пока не достигается откорректированное значение емкости.

Далее, если внутренний конденсатор IC заряжается быстрее, чем внешний конденсатор ERC1, то опорное напряжение CCV уменьшается. Это приводит к увеличению значения внутреннего конденсатора IC из-за изменения отношения сопротивлений RP1 и RP2 в умножителе M1.

Напротив, если внешний конденсатор ERC1 заряжается быстрее, чем внутренний конденсатор IC, то опорное напряжение CCV увеличивается. Это приводит к уменьшению величины внутреннего конденсатора IC из-за изменения отношения сопротивления RP1 и RP2 умножителя M1.

Фиг. 26 показывает подробную принципиальную схему, изображающую вход с высоким входным сопротивлением, выход с низким выходным сопротивлением буферного каскада с единичным коэффициентом усиления, используемого в умножителях M1 и M2, как первых буферов B1 и B2, причем вход обозначен IPN, а выход - OPN. Эти узлы обозначены одинаково как на фиг. 24, так и на фиг. 25.

Буфер включает три МОП-транзистора p-типа, TR1, TR2 и TR3 и три МОП-транзистора n-типа TR4, TR5, TR6 и TR7.

VSS и VDD представляют собой питающее напряжение для схемы, в то время как REF1 представляет собой подходящее опорное напряжение смещения.

Фиг. 29 показывает детали периферийной программируемой усилительной схемы входа/выхода 10C (фиг. 1). Каждая ячейка использует операционные усилители OA1, оперативное запоминающее устройство RAM1, программируемый резистор P/PES и транзисторный переключатель TR1, служащий как пропускной транзистор. ECN представляет контактную площадку, а IPA представляет вход в решетку, в то время как OPA - выход из решетки. REFV представляет собой опорное напряжение.

Пример схемы НЧ фильтра.

Низкочастотный фильтр второго порядка показан на фиг. 30. Такая же схема, выполненная в решетке, показана на фиг. 31. На фиг. 31 те элементы и части схемы, которые не используются, например, включены, показаны пунктиром.

Использование: в аналоговых системах. Сущность: интегральная микросхема содержит решетку (А) из аналоговых ячеек с изменяемой конфигурацией (CL), каждая из которых может соединяться с другими ячейками решетки при помощи цепей соединения (HB, VB). Каждая из ячеек может быть выборочно и отдельно отобрана с помощью сигналов отбора (SS) и (DD), поступающих с регистров сдвига (DSR, PSRV). После отбора ячейка (CL) формируется данными конфигурации (DD, AD), которые устанавливают ячейку к принятию конкретной электрической конфигурации, определяемой цифровыми данными (DD), и определяют различные программируемые резисторы и конденсаторы (P/res, P/cap) в ячейках с определенными параметрами при помощи аналоговых сигналов (AD). Данные конфигурации хранятся в оперативном запоминающем устройстве (RAM). Часть этих данных преобразовывается в цифровую форму с помощью цифроаналогового преобразователя (DAC). Схема управляется центральным устройством управления (CC) и способна принимать конфигурацию для определенного аналогового функционального назначения из всего множества возможных. Применение в схемотехнике делает возможным автоматическую компенсацию отклонений (допусков) изготовленных компонентов. 17 з.п. ф-лы, 31 ил.

15. Схема по пп. 11, 12, или 13 и 14, отличающаяся тем, что регулируемый источник постоянного тока присоединен к вторым информационным каналам (AD).

| GB, заявка, 2016767, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-02-10—Публикация

1991-04-02—Подача