Изобретение относится к электронной технике и может быть использовано при конструировании интегральных схем.

Известен накопитель электрически программируемого ПЗУ, включающий матрицу МДП транзисторов, в стоковую цепь каждого p-канального транзистора включена плавкая поликремниевая перемычка, соединенная через разрядную шину с дешифратором столбцов, поликремниевые затворы каждого транзистора соединены с адресной шиной данной строки, которая, в свою очередь, подключена к дешифратору строки.

Известная конструкция обладает следующими недостатками: - сложность режима программирования, требуются большие импульсы напряжения с амплитудой примерно 30 В для получения тока, достаточного для пережигания перемычки, - низкое быстродействие, обусловленное большой емкостью адресных и разрядных шин.

Известен накопитель электрически программируемого ПЗУ, включающий матрицу вертикальных биполярных транзисторов, в эмиттерную цепь каждого биполярного транзистора включена плавкая поликремниевая перемычка, соединенная через разрядную шину с дешифратором столбцов, базовые области каждого биполярного транзистора соединены поликремниевой адресной шиной с дешифратором строк.

Известная конструкция обладает следующими недостатками: - сложность режима программирования, для расплавления пережигания поликремниевой перемычки требуются большие величины напряжений и токов, - низкая скорость программирования, ограниченная временем пережигания плавких перемычек, - низкое быстродействие, обусловленное большой емкостью адресных и разрядных шин.

Наиболее близким техническим решением к предлагаемому изобретению является накопитель электрически программируемого ПЗУ, основанный на пробое диэлектрика, включающий матрицу из m строк и n столбцов МДП транзисторов, в стоковую область каждого из которых последовательно подключен программируемый пробоем конденсатор, m адресных шин, подключенных к дешифратору строк, и n разрядных шин, подключенных к дешифратору столбцов, причем затворы транзисторов, расположенных в каждой строке, соединены с адресной шиной данной строки, стоки МПД транзисторов подключены к одной из обкладок конденсатора, вторые обкладки конденсатора подключены к соответствующим столбцам.

Известная конструкция обладает следующими недостатками: - низкое быстродействие, обусловленное емкостью p-n-перехода стока под разрядной шиной; все разрядные шины находятся под высоким потенциалом; - сложность в программировании, все схемы управления программированием должны работать при напряжении ≥ 12 В, при рабочем напряжении схемы 5 В, что существенно усложняет конструкцию схемы.

Целью изобретения является упрощение программирования и повышение быстродействия за счет уменьшения емкости разрядных шин.

Поставленная цель достигается тем, что в накопителе электрически программируемого ПЗУ, включающем матрицу из m строк и n столбцов МДП транзисторов, к каждому из которых последовательно подключен программируемый пробоем конденсатор, m адресных шин, подключенных к дешифратору строк, и n разрядных шин, подключенных к дешифратору столбцов, причем затворы транзисторов, расположенных в каждой строке, соединены с адресной шиной данной строки, стоки транзисторов каждого столбца подключены к разрядной шине этого столбца, одна из обкладок каждого конденсатора подключена к истоку соответствующего транзистора, а вторые обкладки конденсаторов объединены и подключены к дополнительной шине, соединенной с источником программирующего напряжения.

Сопоставительный анализ предлагаемого технического решения с прототипом показывает, что предлагаемая конструкция отличается от известной тем, что стоки транзисторов каждого столбца подключены к разрядной шине этого столбца, одна из обкладок каждого конденсатора подключена к истоку соответствующего транзистора, а вторые обкладки конденсаторов объединены и подключены к дополнительной шине, соединенной с источником программирующего напряжения. Таким образом, предлагаемая конструкция соответствует критеpию "Новизна".

Из литературных источников неизвестен накопитель электрически программируемого ПЗУ с конструкцией, аналогичной предлагаемой.

В предлагаемой конструкции стоки транзисторов каждого столбца подключены к разрядной шине этого столбца, а в известной конструкции в цепь стока транзистора включен программирующий конденсатор. В предлагаемой конструкции используется одна разрядная шина на две ячейки, т.е. две соседние ячейки имеют общий сток, в то время, как в извествной конструкции на каждую ячейку используется своя разрядная шина.

В предлагаемой конструкции одна из обкладок каждого конденсатора подключена к источнику соответствующего транзистора, а в известном решении одна из обкладок каждого конденсатора подключена к стоку соответствующего транзистора. В предлагаемом решении вторые обкладки конденсаторов объединены и подключены к дополнительной шине, соединенной с источником программирующего напряжения. А в известном решении вторые обкладки конденсаторов объединены и подключены к разрядной шине, а источник МДП-транзисторов подключены к шине "земля". Использование одной разрядной шины на две ячейки накопителя позволяет уменьшить в 2 раза емкость разрядной шины за счет уменьшения диффузионной емкости p-n-перехода и повысить быстродействие схемы. В известном решении программируемый конденсатор включен в цепь стока МДП-транзистора, для выбора ячейки при программировании на каждую ячейку используется своя разрядная шина, емкость которой определяется диффузионной емкостью p-n-перехода и емкостью вышележащих диэлектрических слоев.

В предлагаемой конструкции для упрощения режима программирования используется отдельный источник программирующего напряжения, к которому через дополнительную шину подключены вторые обкладки конденсаторов, а все цепи схемы работают при стандартном напряжении питания +5 В, высокий потенциал (≥12 В) подается только на дополнительные шины. В известной конструкции все схемы управления программированием в момент программирования должны работать при повышенном напряжении, большем напряжения программирования (≥12 В). В известной конструкции напряжение программирования подается на разрядную шину, соединенную со стоками транзисторов. А в предлагаемой конструкции в момент программирования на всех разрядных шинах и схемах обрамления стандартное напряжение питания (+5 В). Таким образом, предлагаемая конструкция соответствует критерию "Существенные отличия".

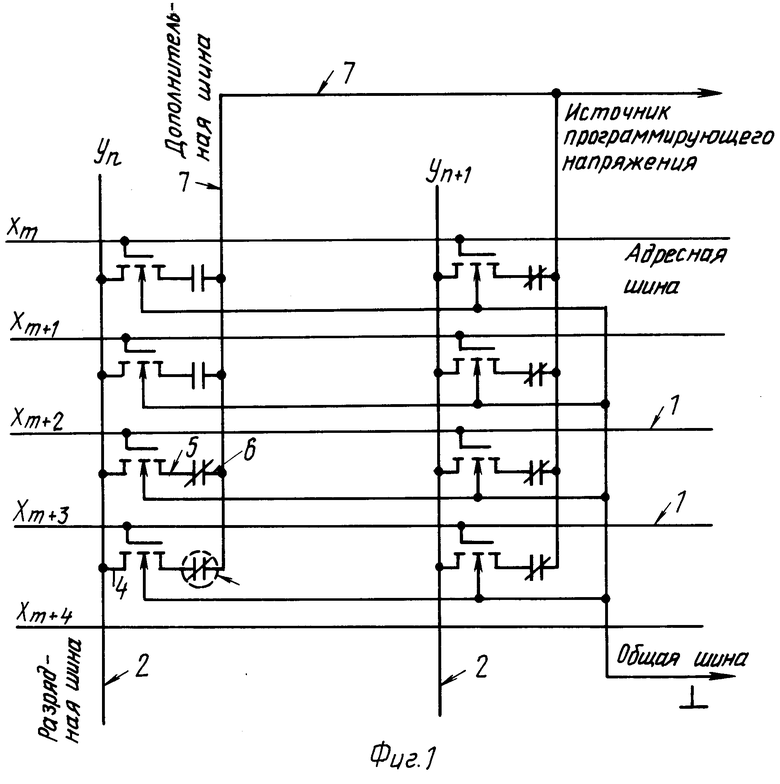

На фиг. 1 изображена электрическая схема построения накопителя электрически программируемого ПЗУ; на фиг. 2 - электрическая схема организации накопителя ППЗУ емкостью 4К х 1 бит. Предлагаемый накопитель (фиг. 1) включает матрицу из m строк 1 и n столбцов 2 МДП транзисторов, к каждому из которых последовательно подключен программируемый пробоем конденсатор 3, m адресных шин, подключенных к дешифратору строк, и n разрядных шин, подключенных к дешифратору столбцов, затворы транзисторов, расположенных в каждой строке, соединены с адресной шиной данной строки 1. Стоки транзисторов каждого столбца 4 подключены к разрядной шине 2 этого столбца, одни из обкладок каждого конденсатора 5 подключены к истоку соответствующего транзистора, а вторые обкладки конденсаторов 6 объединены и подключены к дополнительной шине 7, соединенной с источником программирующего напряжения.

В состоянии до программирования поликремниевый электрод 6 (вторая обкладка конденсаторов) изолирован от диффузионного слоя МДП транзистора в области истока транзистора тонким слоем диэлектрика. В процессе программирования ячейки к поликремниевому электроду прилагаем импульс напряжения, происходит пробой изолятора, и поликремниевый электрод соединяется с диффузионным слоем, ячейка запрограммирована.

В предлагаемом накопителе для выбора ячейки при программиpовании используются три шины: адресная, разрядная и дополнительная шина. Адресная шина объединяет затворы транзисторов, расположенных в каждой строке, и подключает их к дешифратору строк. Разрядная шина объединяет стоки транзисторов, расположенных в каждом столбце, и подключает их к дешифратору столбцов. Причем на два соседних столбца транзисторов используется одна разрядная шина. Дополнительная шина объединяет вторые обкладки программируемых конденсаторов и подключает их к дополнительному источнику питания. В режиме программирования на выбранную с помощью адресной и разрядной шин ячейку подают по дополнительной шине высокое программирующее напряжение от отдельного источника питания, достаточное для пробоя конденсаторного диэлектрика в цепи истока транзистора. Все остальные схемы управления программированием работают при стандартном напряжении питания. Это дает возможность упростить схему управления программированием. А также снижает еще больше емкость разрядных шин и повышает быстродействие, так как в режиме программирования на разрядных шинах не бывает высокого потенциала (меньше диффузионные емкости p-n-переходов) в отличие от прототипа, где на разрядных шинах в режиме программирования имеется высокий потенциал. Использование программируемого конденсатора в цепи истока транзистора позволяет значительно упростить режим программирования схемы, так как только на дополнительных шинах будет высокий потенциал ≥12 В, необходимый для пробоя конденсаторного диэлектрика. Этот потенциал формируется дополнительным источником. А на всей остальной схеме будет стандартное напряжение питания.

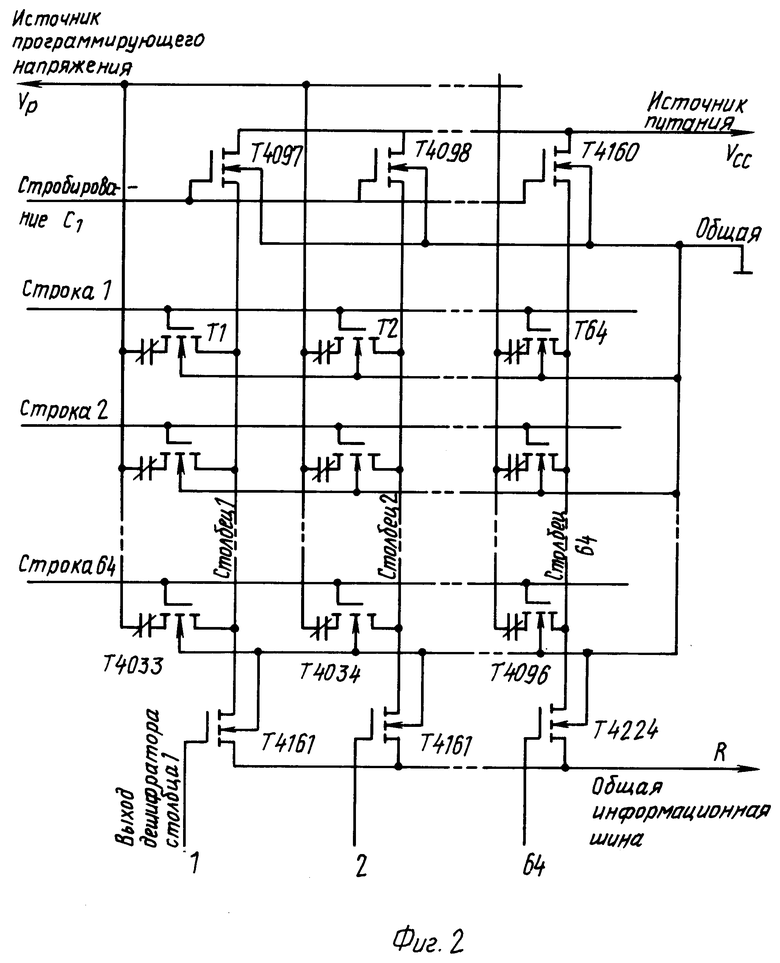

Рассмотрим для примера организацию накопителя ППЗУ емкостью 4К х 1бит (фиг. 2).

Накопитель состоит их 4096 запоминающих МДП транзисторов, исток каждого из которых соединен с запоминающим конденсатором, а вторые обкладки всех запоминающих конденсаторов объединены и выведены на отдельную площадку Vр. 64 строки накопителя подключены к выходам дешифратора строк, работающего при напряжении питания Vсс = 5 В, 64 выхода дешифратора столбцов (работающего при Vсс = 5 В) управляют ключевыми транзисторами Т 4161 - Т 4224, которые осуществляют связь столбцовых шин с общей информационной шиной R. Транзисторы Т 4097 - Т 4160 используются в качестве стробируемой сигналом С1 нагрузки. При считывании информации площадка Vр закорачивается с шиной земли. При подаче адресного сигнала дешифраторы строки и столбца осуществляют выборку запоминающей ячейки, то есть на одном из выходов дешифраторов строки и столбца устанавливается высокий уровень +5 В. Все транзисторы выбранной строки переводятся в проводящее состояние. В том случае, если запоминающий конденсатор, включенный последовательно с транзистором, запрограммирован (пробит конденсаторный диэлектрик), то открыта цепь разряда емкости столбцовой разрядной шины на землю и на ней будет устанавливаться низкий уровень. В том случае, если запоминающий конденсатор не запрограммирован, то последовательная цепь транзистор-конденсатор закрыта, и на столбцовой шине сохранится высокий потенциал, который будет поддерживаться соответствующими транзисторами Т 4097 - Т 4160, используемыми в качестве высокоомной нагрузки.

Информация, установившаяся на столбце через один из транзисторов Т 4161 - 4224, на который подается из дешифратора столбцов отпирающий потенциал, поступает на общую информационную шину и подается через усилитель считывания на выходной буфер.

В режиме программирования в начале на площадку Vр подается уровень питания микросхемы 5 В. При подаче адресного сигнала дешифраторы строки и столбца осуществляют выборку строки и столбца. Записываемая информация подается от входной площадки на общую информационную шину R и через выбранный дешифратором столбцов один из транзисторов Т 4161 - 4224 на выбранный столбец. Затем проводится импульсное повышение напряжения на площадке Vр до уровня 12-14 В, превосходящего напряжение пробоя диэлектрика запоминающего конденсатора.

В том случае, когда на столбцовой шине задан низкий потенциал, на обкладках запоминающего конденсатора выбранной ячейки памяти создается разность потенциалов 12-14 В, необходимая для пробоя запоминающего диэлектрика. В том случае, когда на столбцовой шине задается высокий потенциал, транзистор выбранной запоминающей ячейки запирается, и при повышении напряжения на площадке Vр на обкладках запоминающего конденсатора выбранной ячейки устанавливается разность потенциалов, не достаточная для пробоя запоминающего диэлектрика.

Таким образом, предлагаемый накопитель электрически программируемого ПЗУ позволяет повысить быстродействие ППЗУ за счет уменьшения емкости разрядных шин в 2 раза, так как в конструкции используется одна разрядная шина на две ячейки, стоки двух соседних ячеек объединены. Кроме того, предлагаемая конструкция позволяет упростить программирование, так как в режиме программирования на выбранную ячейку подают высокое программирующее напряжение по дополнительной шине от отдельного источника напряжения. Все остальные схемы обрамления и управления программированием работают при стандартном напряжении питания. Это дает возможность упростить схему управления программированием. А также, снижает еще больше емкость разрядных шин и повышает быстродействие, так как в режиме программирования на разрядных шинах не бывает высокого потенциала (уменьшаются диффузионные емкости p-n-переходов).

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| Матричный накопитель для электрорепрограммируемого запоминающего устройства | 1980 |

|

SU1336110A1 |

| НАКОПИТЕЛЬ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1995 |

|

RU2106022C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Способ изготовления матричного накопителя для постоянного запоминающего устройства | 1989 |

|

SU1628735A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1980 |

|

SU888731A1 |

Изобретение относится к электронной технике и может быть использовано при конструировании интегральных схем высокой степени интеграции. Цель изобретения - упрощение программирования и повышения быстродействия за счет уменьшения емкости разрядных шин. Это достигается тем, что в накопителе электрически программируемого ПЗУ, включающем матрицу из m строк и n столбцов МДП-транзисторов, к каждому из которых последовательно подключен программируемый пробоем конденсатор, m адресных шин, подключенных к дешифратору строк, и n разрядных шин, подключенных к дешифратору столбцов, причем затворы транзисторов, расположенных в каждой строке, соединены с адресной шиной данной строки, строки транзисторов каждого столбца подключены к разрядной шине этого столбца, одна из обкладок каждого конденсатора подключена к истоку соответствующего транзистора, а вторые обкладки конденсаторов объединены и подключены к дополнительной шине, соединенной с источником программирующего напряжения. 2 ил.

НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, содержащий запоминающие ячейки, расположенные в виде матрицы, каждая из которых содержит МДП-транзистор и конденсатор с изолирующим слоем, затворы транзисторов соединены с адресной шиной данной строки, отличающийся тем, что стоки транзисторов подключены к разрядной шине данного столбца, одна из обкладок каждого конденсатора соединена с истоком соответствующего транзистора, другие обкладки конденсаторов объединены и подключены к шине программирующего напряжения.

| 0 |

|

SU213638A1 | |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1995-02-09—Публикация

1991-05-30—Подача