Предлагаемое изобретение относится к области вычислительной техники, в частности к схемам матриц ячеек памяти «MRAM» («Magnetic Random Access Memory»), использующей технологию магниторезистивной оперативной памяти с передачей спинового вращения («STT-MRAM») так называемым спин-вентильным запоминающим устройствам. «STT-MRAM» также известна как «RAM» («Random Access Memory») с передачей спинового вращательного момента («Spin Transfer Torque RAM», «STT-RAM»), «RAM» с переключением намагничивания и передачей спинового вращательного момента («Spin Torque Transfer Magnetization Switching RAM», или «Spin-RAM»), «RAM» с передачей спинового момента («SMT-RAM»).

Известна программируемая в жестких условиях эксплуатации вентильная матрица, которая является полупроводниковым устройством, включающая в себя компоненты программируемых логических схем (ПЛИС), называемых «логическими блоками», и программируемые межсоединения, или интерфейсы. Логические блоки могут быть запрограммированы для выполнения функции элементарных логических вентилей, например «AND» и «XOR» или более сложных комбинационных функций, например декодеров или простых математических функций. В большинстве матриц «FPGA» («Field Programmable Gate Arrey») логические блоки также включают в себя элементы памяти, которые могут быть простыми триггерами или более полными блоками памяти. Иерархия программируемых интерфейсов обеспечивает возможность соединения логических блоков так, как это необходимо разработчику систем. После того как матрица «FPGA» изготовлена, разработчик - схемотехник может использовать программирование для реализации многих различных логических функций, тем самым, конструируя «программируемое в условиях эксплуатации» устройство. Матрица «PLA» («Programmable Logic Arrey») аналогична «FPGA», за исключением того, что «PLA» модифицируется, или «программируется», на этапе изготовления интегральных микросхем (ИМС) посредством изменений в одной или двух масках. Так «PLA», имеющая элементы флэш-памяти «EPROM», как правило, формируется из двух логических матриц, матрицы ввода и матрицы вывода /1/. Каждая матрица имеет входы, которые присоединяются к выводам затвора транзисторов в пределах логической матрицы, и обеспечивает выходы в узлы вывода. Входы матрицы ввода являются входами программируемой логической матрицы. Выходы матрицы ввода являются промежуточными узлами. Входы матрицы вывода соединены с промежуточными узлами. Выходы матрицы вывода являются выходами «PLA». Матрица ввода может обеспечивать функцию «AND», а матрица вывода может обеспечивать функцию «OR». В качестве альтернативы, обе матрицы могут обеспечивать функцию «NOR». Эти функции определяются типом и возможностью подключения используемых транзисторов и сигналами, применяемыми к их затворам. Конфигурация «NOR-NOR» имеет конкретные преимущества за счет того, что ее проще всего реализовать в логической схеме технологии КМОП. При реализации функции «NOR» существует некоторое количество транзисторов, равное количеству входов, соединенных параллельно. Подключение дополнительных параллельных транзисторов для размещения дополнительных входов не влияет на скорость функционирования этапа.

Известна матрица «FPGA» с запоминающими магнитными элементами или ячейками памяти «MRAM» /2/. Информация о соединении записывается в запоминающие магнитные элементы. Информация о соединении последовательно вводится и сохраняется в сдвиговых регистрах, которые соответствуют запоминающим магнитным элементам. При включении электропитания информация о соединении, хранящаяся в запоминающих магнитных элементах, фиксируется посредством элементов-триггеров и выводится в переключающие схемы для соединения логических блоков «FPGA».

Магниторезистивная оперативная память («MRAM») является технологией энергонезависимой памяти, время отклика (чтение/запись) которой сопоставимо с энергозависимой памятью. В отличие от технологий общепринятой «RAM», в которой данные хранятся как электрические заряды или электрические токи, «MRAM» использует магнитные элементы.

Объединить магнитный элемент памяти и магниторезистивный элемент считывания удалось в памяти «CRAM» («Crosstie Random Access Memory»). При этом измерялись небольшие различия в сопротивлении ячеек в узловых точках, что позволяло различать «0» и «1». Разница сопротивлений не превышала 0,1%, что было достаточно для демонстрации эффекта, но крайне мало для его практического использования.

В 1982 году было предложено располагать ячейки магнитной памяти непосредственно на кремниевой пластине. Тогда же были предприняты попытки изготовить магнитную память в едином технологическом процессе с электронной схемой управления. Этот принцип сохранен в «MRAM» до сих пор, поскольку связи между матрицей ячеек памяти и схемой управления достаточно сложны.

Ячейки памяти располагаются на поверхности кремниевого кристалла и соединяются сверху и снизу системой проводников, через которые селективно управляют их состоянием (производят запись или считывание).

«MRAM» можно разместить непосредственно на кристалле процессора, при этом максимально сокращается длина соединительных проводников и повышается скорость ее работы. Считается, что по сравнению с существующими приборами памяти, при использовании «MRAM» может быть достигнуто 1000-кратное увеличения плотности записи /3/.

Физической основой «MRAM» являются субмикронные многослойные структуры из магнитных и немагнитных материалов, изменяющие свое магнитное состояние и электропроводность под действием внешнего магнитного поля. Два противоположных направления намагниченности одного из магнитных слоев соответствуют записи логических «1» и «0». На кристалле располагается множество ячеек, способных сохранять цифровую информацию без питания. Рабочие характеристики «MRAM» улучшаются при снижении размеров ячеек памяти.

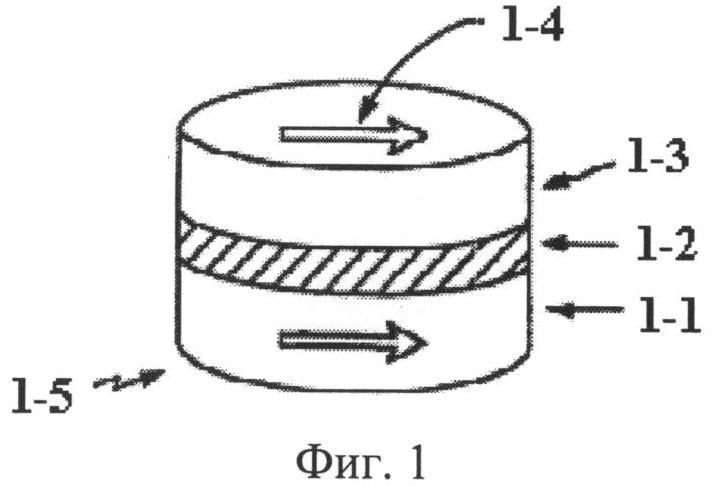

Ячейка состоит из двух сверхтонких ферромагнитных пленок, разделенных слоем материала с низкой проводимостью (например, TaN), а также пленок сложного состава, вытравленных в виде плоских проводников (полосок, шин) (Фиг.1).

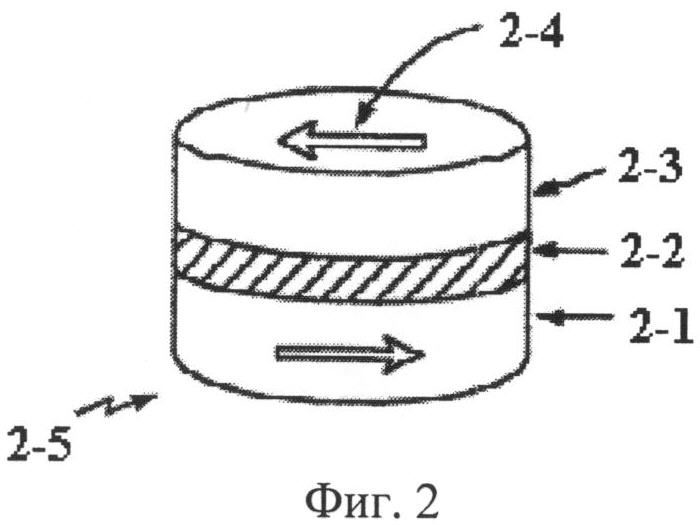

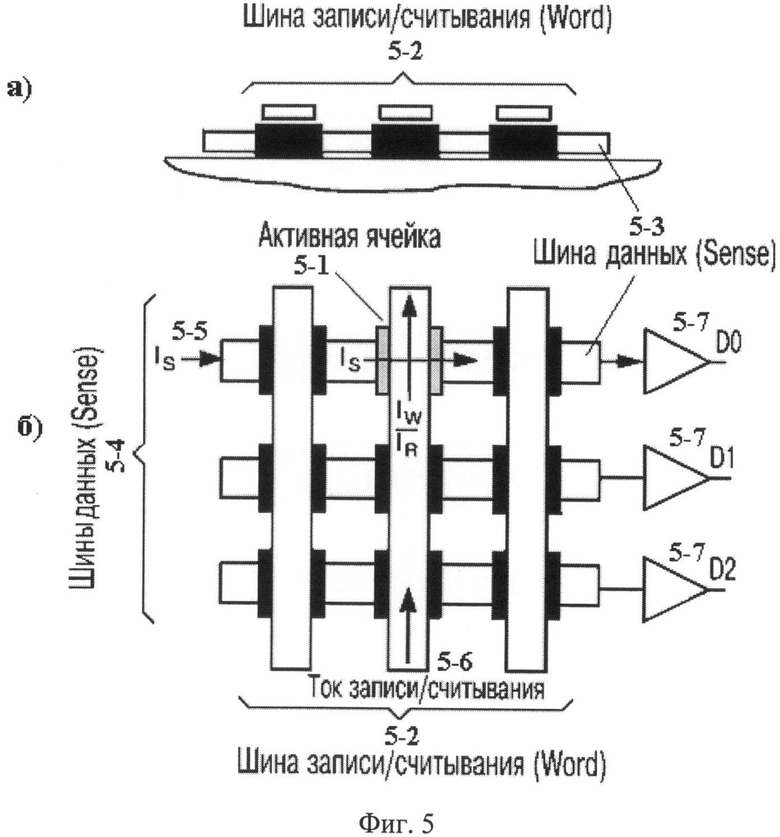

Запись информации производится пропусканием тока, который намагничивает верхний слой NiFeCo в прямом (параллельном) (Фиг.1) или обратном (антипараллельном) направлении (Фиг.2) одновременно по двум линиям - записи («word» - шина записи/считывания слов («ШЗС») и данных («sense» - шина данных «ШД»), на пересечении которых находится данная ячейка (Фиг.3). Величина токов подбирается таким образом, что изменение состояния ячейки происходит только при совместном их действии. Напряженность магнитного поля, создаваемого токами в других ячейках, недостаточна для изменения их состояния. При считывании состояние ячейки («0» или «1») определяют по изменению сопротивления ячейки при пропускании тока, постоянного по «ШД» через все включенные последовательно ячейки (Фиг.4), и тока считывания по «ШЗС». Ток считывания «iч» создает магнитное поле, совпадающее или противоположное полю магнитных слоев, при этом угол поворота магнитного вектора различен для «0» или «1».

Сплав «никель-пермаллой» имеет нормальное анизотропное магнитосопротивление (ARM) около 2%. При современных методах считывания максимальная разница в напряжениях для состояний «0» или «1» составляет 0,5%. В реальной ячейке для приемлемых токов считывания разность напряжений составляет 0,5…1 мВ. При таких уровнях сигнала работает 256 Кбайт «MRAM» фирмы «Honeywell», обеспечивая скорость считывания 250 нс. Время записи составляет 100 мс и может быть улучшено /4/.

Открытое в 1988 году при исследовании свойств сверхтонких многослойных структур, состоящих из чередующих слоев ферромагнитного (Fe, Co) и немагнитного (Cu, Ag) или антиферромагнитного (Cr, Mn) металлов гигантское магнитосопротивление (GMR) позволило значительно повысить скорость считывания и записи информации в запоминающих ячейках «MRAM». Толщина каждого слоя составляла несколько десятков ангстрем. Минимально возможное число слоев, при котором наблюдается эффект, это три - два ферромагнитных слоя, разделенных немагнитной прослойкой.

В 1991 году была разработана многослойная ячейка памяти с магнитосопротивлением 6%, состоящая из магнитных пленок и медного промежуточного слоя. В новую конструкцию были внесены некоторые изменения. Поскольку время считывания сокращается пропорционально квадрату амплитуды сигнала, трехкратное увеличение магнитосопротивления ведет к 9-кратному сокращению времени считывания. При использовании магнитных материалов для реализации GMR были разработаны «MRAM» со временем считывания до 50 нс.

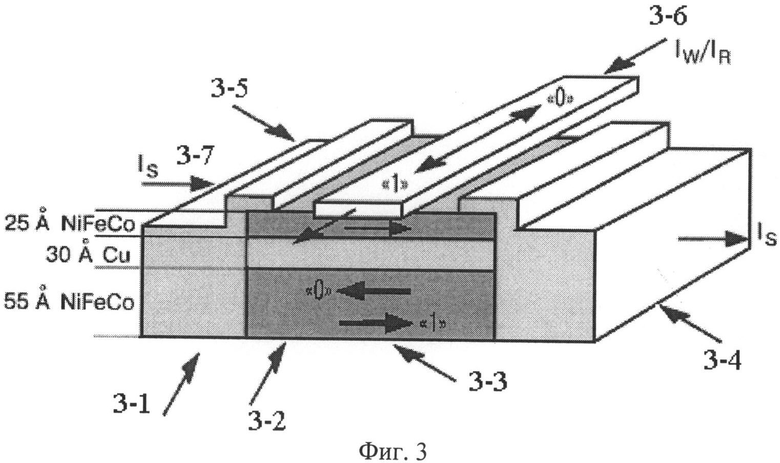

В настоящее время наиболее перспективными считаются два основных элемента - псевдоспиновый вентиль («PSV» - «Psevdo Spin Valve») и ячейки на основе туннельного эффекта («SDT» - «Spin Depending Tunneling» или MTJ - «Magnetic Tunnel Junction»). Конструкция ячейки памяти в виде вентиля «PSV» позволила значительно повысить уровень сигналов считывания в «MRAM», в 8 раз сократить время считывания и по быстродействию поставить «MRAM» в один ряд с полупроводниковой памятью. В приборах магнитной памяти для хранения цифровой информации используется явление гистерезиса. На Фиг.3 показана упрощенная схема памяти на магнитных элементах. Малая величина полезного сигнала обуславливает требования, предъявляемые к процедуре записи и считывания в ячейку памяти.

Варианты структуры запоминающей ячейки «MRAM» приведены в Приложении «А».

В ПЛИС, использующей технологию «STT-MRAM», принятой за прототип /4/, вариант осуществления изобретения может включать в себя программируемую логическую матрицу, содержащую: множество устройств на «MTJ» с передачей спинового вращения, организованных в матрицу, и множество программируемых источников, соединенных с соответствующими устройствами «MTJ», для изменения полярности свободного слоя каждого устройства «MTJ», причем первая группа устройств «MTJ» организована в матрицу ввода, вторая группа устройств «MTJ» организована в матрицу вывода, и матрица ввода и матрица вывода объединены для формирования логической функции на основе относительных полярностей свободного слоя каждого устройства «MTJ».

Другой вариант осуществления может включать в себя способ реализации логической схемы в матрице, содержащий: программирование каждого из множества устройств «MTJ», организованных в матрицу, в состояние высокого или низкого сопротивления, причем каждое устройство «MTJ» программируется первым программируемым источником, соединенным со стороной свободного слоя (СС) выбранного устройства «MTJ», и программируемым источником, соединенным со стороной фиксированного слоя (ФС) выбранного устройства «MTJ», организацию первой группы устройств «MTJ» в столбцы и строки матрицы ввода, организацию второй группы устройств «MTJ», по меньшей мере, в один столбец в матрице вывода, причем выходы каждой строки соединены с устройствами «MTJ», по меньшей мере, в одном столбце, и определение логической функции на основе относительных сопротивлений каждого устройства «MTJ».

Недостатком такой схемы организации устройства «PLA» является демонстрация принципов программирования СС и ФС элементов «MTJ» для суперпозиции определенной заданной логической функции на выходе «PLA». Могут быть разработаны альтернативные варианты осуществления, не отступая от содержания и объема изобретения /4/. Кроме того, известные элементы изобретения не были подробно описаны или были опущены для исключения затруднения в понимании соответствующих деталей вариантов реализации изобретения. Слово «иллюстративный» там использовано в значении «служащий в качестве примера, образца или иллюстрации». Любой вариант реализации, приведенный в описании /4/ как «иллюстративный», не должен обязательно рассматриваться как предпочтительный или имеющий преимущества перед другими вариантами осуществления. Таким же образом, термин «варианты осуществления изобретения» не требует, чтобы все варианты осуществления изобретения включали в себя рассматриваемый признак, преимущество или режим функционирования.

Варианты осуществления изобретения используют элементы магниторезистивной оперативной памяти «STT-MRAM», составляющих часть матрицы запоминающего устройства. «STT-MRAM» использует электроны, которые становятся спин-поляризованными, так как электроны проходят через тонкую пленку (спиновый фильтр). Во время операции записи спин-поляризованные электроны влияют вращающим моментом на СС, который может переключать полярность намагниченности СС. Операция чтения аналогична общепринятой в «MRAM» в том смысле, что ток используется для идентификации сопротивления логического состояния запоминающего элемента «MTJ», как обсуждалось выше.

На Фиг.3 приведена одноразрядная ячейка памяти технологии «PSV-MRAM» для лучшего понимания процесса программирования элемента «PSV». Логическое состояние элемента «PSV» в «PSV-MRAM» записывается электрически, в противоположность магнитной записи в общепринятой «MRAM».

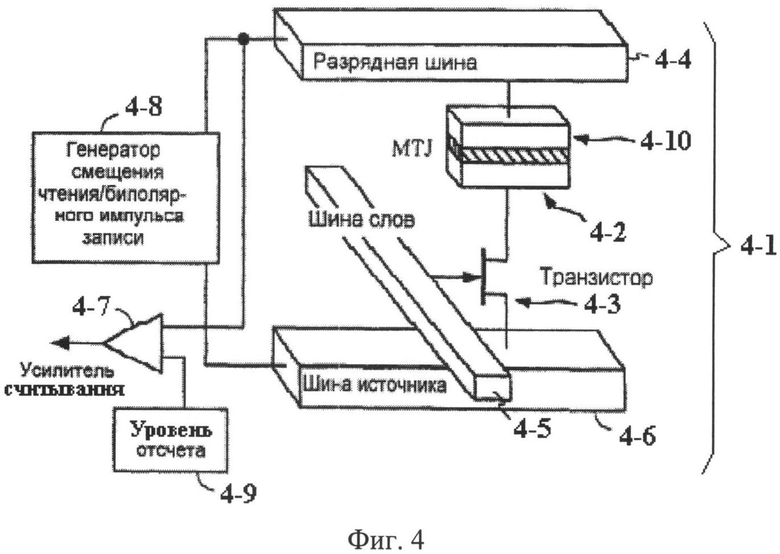

На Фиг.4 приведена более подробная схема ячейки «STT-MRAM» для дальнейшего обсуждения операций чтения/записи. В отличие от «MRAM», операция записи в «STT-MRAM» является электрической. Цепи чтения/записи формируют напряжение записи между разрядной шиной и шиной источника. В зависимости от полярности напряжения между разрядной шиной и шиной источника может быть изменена полярность магнитного СС элемента «MTJ», и, соответственно, в ячейку «STT-MRAM» может быть записано определенное логическое состояние. Таким же образом, во время операции чтения формируется ток чтения, который протекает между разрядной шиной и шиной источника через элемент «MTJ». Когда току дают возможность протекать через транзистор, сопротивление (логическое состояние) элемента «MTJ» может быть определено на основе разности напряжений между разрядной шиной и шиной источника, которое сравнивается с началом отсчета и затем усиливается усилителем считывания. Это функционирование и конструкция ячейки памяти известны в данной области техники. Дополнительные подробности представлены, например, в /5/ и в Приложении «А».

Практически отсутствуют публикации о патентоохраняемых технических решений устройств «STT-MRAM».

Техническим результатом заявляемого устройства является интегрированная в СБИС технологии КМОП/КНИ с n+- и p+-поликремниевыми затворами матрица памяти «STT-MRAM».

Технический результат достигается тем, что решением задачи создания матрицы памяти «STT-MRAM» является устройство матричного типа, управляемое внешними сигналами записи/чтения информации и ввода/вывода данных, содержащее:

множество устройств на магнитных туннельных переходах («MTJ») с передачей спинового вращения, организованных в матрицу запоминающих ячеек;

устройство организации записи/чтения информации для конкретного устройства «MTJ», включающее:

блок ввода/вывода данных,

блок дешифратора адресного кода,

блок управления ключами шин записи слова,

блок ключей шин записи слова,

блок управления ключами разрядных шин,

блок ключей разрядных шин,

блок управления записью/чтением данных,

блок формирователя тока записи/чтения,

источники тока записи слова, тока записи разряда, тока чтения в составе блока формирователя тока записи/чтения,

шины разрядные, шины записи слова, шины чтения слова, двунаправленную шину ввода/вывода данных,

соединенные с соответствующими устройствами «MTJ» для изменения полярности намагниченности свободного слоя каждого устройства «MTJ», причем блоки устройства организации записи/чтения информации объединены соответствующими шинами для формирования логического состояния на основе относительных полярностей свободного слоя и фиксированного слоя каждого устройства «MTJ»,

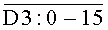

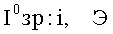

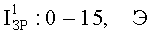

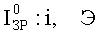

блок усилителя чтения данных на выходе матрицы запоминающих ячеек, соединенный с двунаправленной шиной ввода/вывода данных по цепям «UP:0-15, Э» и «DЧ:0-15», выполненный с возможностью обнаруживать уровень сигнала на конце «А» в шине разрядной и формировать двоичный выходной сигнал «DЧ:0-15» на основе сравнения уровня сигнала в разряде матрицы запоминающих ячеек в компараторе, включенным в состав блока усилителя чтения данных, с эталонным пороговым уровнем сигнала («UЭ»),

С целью придания исходной анизотропии намагниченности свободного и фиксированного ферромагнитного слоев каждой запоминающей ячейки матрицы памяти «STT-MRAM» при формировании топологи устройства «MTJ» оно выполнено в виде эллипса с осью легкого намагничивания, направленной по его большой оси,

С целью изменения полярности намагниченности верхнего свободного слоя устройства «MTJ» внешнее управляющее матрицей памяти «STT-MRAM» устройство соединено по цепям сигнала разрешения записи информации (

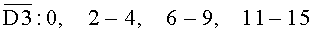

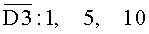

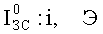

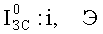

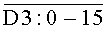

Для исключения статистического разброса величины магнитного момента нижнего закрепленного ферромагнитного слоя в каждом устройстве «MTJ», концы «А» разрядной шины «ШР-А:0-15, Э» этого устройства в режиме чтения данных соединены с одним из входов компаратора, а второй вход компаратора соединен с шиной записи/чтения, в которой генерируется выходной сигнал «UЭ» эталонного устройства «MTJ», расположенного в центре каждого слова матрицы запоминающих ячеек («МЗЯ») (Фиг.34).

Для организации постоянного запоминающего устройства (ПЗУ) емкостью 64 кбит с 16-и разрядной двунаправленной шиной ввода/вывода данных «DIO:0-15», она содержит множество запоминающих ячеек («ЗЯ») на основе устройств «MTJ», которые могут быть электрически приведены в состояние высокого сопротивления «RB» или низкого сопротивления « RH».

Для обеспечения обращения к выбранному слову «МЗЯ», выходы «C:i» блока дешифратора адреса («Дш.А»), где i=0…4095 равно численному значению кода адреса, соединены с входом блока управления ключами шины записи слова («БУК ШЗС») и одновременно, через блок ключей записи слова («БК ШЗС»), с шиной записи слова («ШЗС:i») «МЗЯ», где i=0…4095 равно численному значению кода адреса устройства «MTJ», с возможностью выработки на одном из выходов «C:i» сигнала с уровнем логической «1» при поступлении на вход «Дш.А» по шине «A:0-11» от внешнего устройства параллельного адресного кода (Фиг.16).

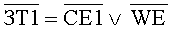

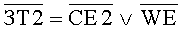

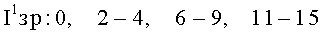

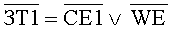

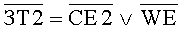

С целью обеспечения формирования сигналов 1-го и 2-го цикла записи («

С целью генерации сигналов управления ключами «БУК ШЗС» в зависимости от состояния входных сигналов «C:i», где i=0…4095, «

С целью управления «БК ШР» выходы «б:0-15, Э» блока «БУК ШР» присоединены с одной стороны к «БК ШР» с логическим состоянием, определяемым состоянием входных сигналов внешнего устройства «

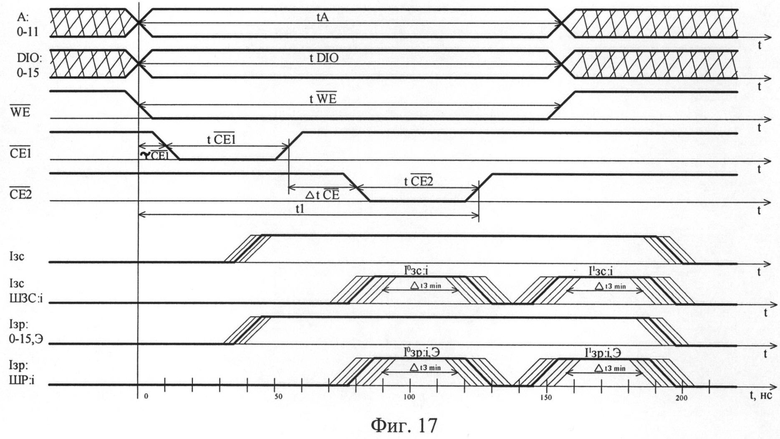

Для обеспечения соединения концов «ШЗС», выбранных для записи слова, к источнику тока «IЗС» и «ШО» в режиме записи и отключения шин «ШЗС», входы «a:i», «б:i» «БК ШЗС» соединены с соответствующими выходами «БУК ШЗС» с возможностью реализации алгоритма работы «БК ШЗС», а выходы «ШЗС-А:i» и «ШЗС-Б:i» (i=0…4095) «БК ШЗС» соединены с соответствующими шинами «МЗЯ» (Фиг.17).

Для формирования стабильных токов записи слова «IЗС» и разрядных токов записи «IЗР:0-15, Э», входы «З» и «Ч» блока «ФТЗЧ» соединены с соответствующими выходами «БУЗЧ», а выход «IЗС» «ФТЗЧ» при уровне «1» сигнала «З» соединен с входом «БК ШЗС», и «

С целью частичной компенсации технологических отклонений сопротивлений «RH» и «RB» устройств «MTJ» в словах энергонезависимой «МЗЯ», она организована в виде 4096 шестнадцатиразрядных слов, каждая «ЗЯ» содержит «MTJ», транзистор МОП и систему шин для обеспечения записи и чтения данных по словам, а каждое слово содержит 17 «ЗЯ», одна из которых эталонная, исходно заранее установленная в состояние «0» с возможностью выработки эталонного напряжения «UЭ» при чтении информации из данного слова.

Для организации управления работой «МЗЯ» все шины записи/чтения «МЗЯ» соединены с соответствующими выходами «ШЗС-А:i», «ШЗС-Б:i» «БК ШЗС» (i=0…4095), шины «ШР-A:i, Э,», «ШР-Б:i, Э» (i=0-15) с соответствующими выходами «БК ШР», шина «ШЧС:i» с соответствующим выходом блока «Дш.А», а в режиме чтения шина «ШР-А:i, Э» соединена с входами «UP:0-15, Э» «БУЧ» и с выбранной «ЗЯ» (Фиг.18).

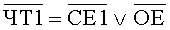

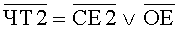

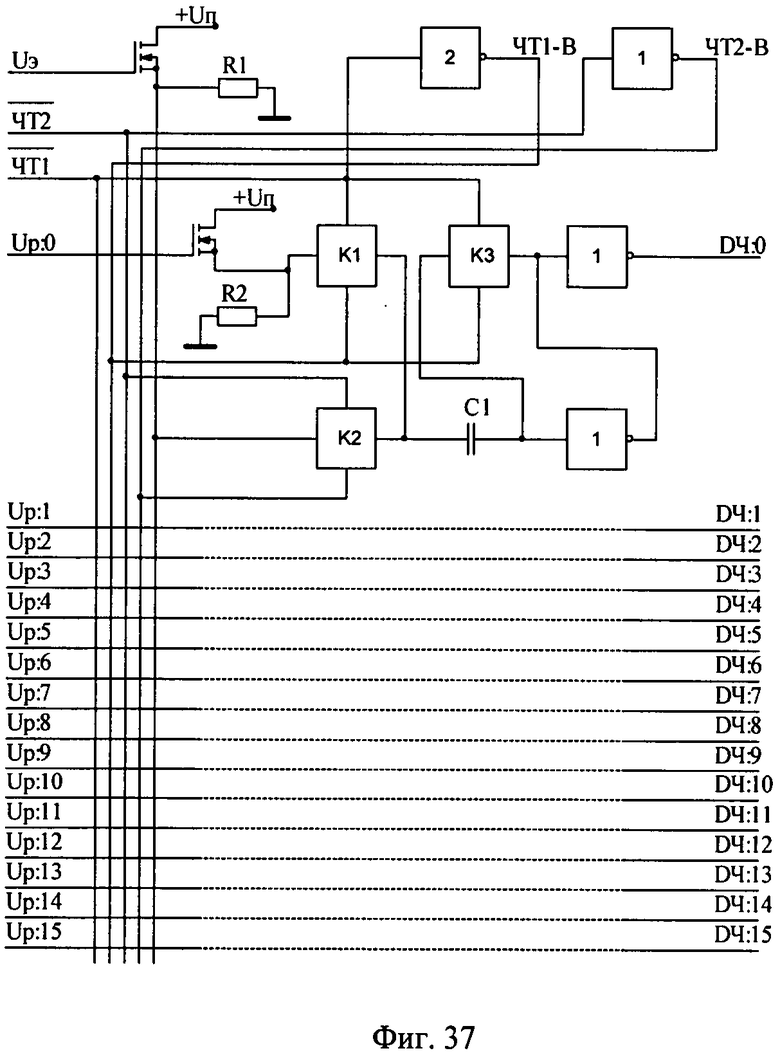

С целью обеспечения усиления считанных с шины «ШР-A:i, Э» «БК ШР» сигналов «UP:0-15, Э» и выработки нормированных сигналов «DЧ:0-15», в режиме чтения вход «

Приведенное описание заявляемого устройства может быть дополнено следующими иллюстрациями, приведенными ниже.

На Фиг.1 показана процедура записи информации пропусканием тока, который намагничивает верхний свободный слой (СС) в прямом (параллельном) направлении: (1-1) - нижний фиксированный слой ФС; (1-2) - переход MTJ; (1-3) - СС; (1-4) - вектор намагниченности; (1-5) - элемент «MTJ».

На Фиг.2 показана процедура записи информации пропусканием тока, который намагничивает верхний СС в инверсном (антипараллельном) направлении: (2-1) - элемент «MTJ»; (2-1) - ФС; (2-2) - переход «MTJ»; (2-3) - СС; (2-4) - вектор намагниченности; (2-5) - элемент «MTJ».

На Фиг.3 приведена конструкция одноразрядной ячейки памяти (3-1) «PSV-MRAM», включающей в себя: элемент (3-2) «PSV», направление намагниченности (3-3) («1»∞→), («0»∞→) ФС, шину данных (3-4) («IS» «Sence») и шину записи/чтения (3-5) слов («Word»), ток записи/чтения (3-6) («IW/IR»), измерительный ток (3-7) IS.

На Фиг.4 показана ячейка памяти (4-1) «STT-MRAM», включающая в себя: элемент (4-2) «MTJ», транзистор МОП (4-3), шину разряда («ШР») (4-4), шину слов («ШС») (4-5), шину источника тока («ШИ») (4-6), усилитель считывания («УСч») (4-7), цепи записи/чтения (4-8), уровень отсчета (4-9) на «ШР», СС (4-10) элемента «MTJ».

На Фиг.5 показана организация шин записи/чтения матрицы «STT-MRAM»: а) поперечное сечение; б) вид сверху; (5-1) активная ячейка; (5-2) - шина записи/считывания (Word); (5-3) - линия данных (Sense); (5-4) - шина данных (Sense); (5-5) - ток измерительный IS; (5-6) - ток записи (IW)/считывания (IR); (5-7) - усилители считывания.

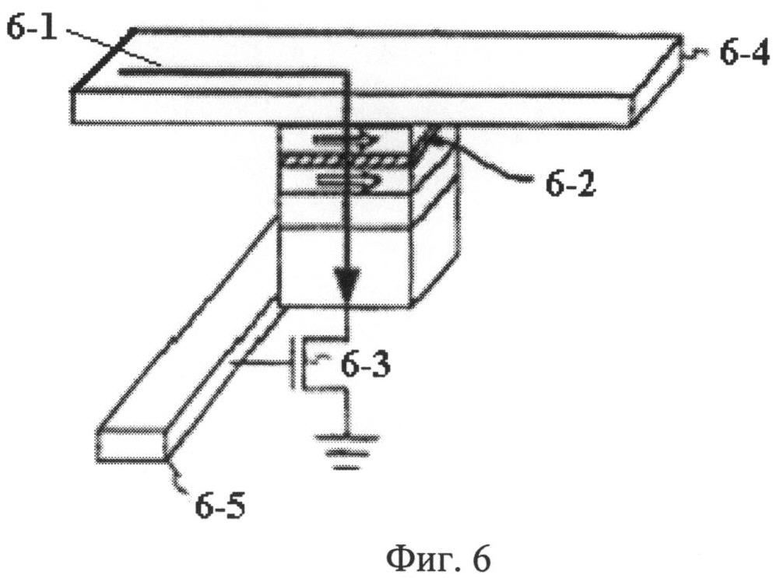

На Фиг.6 показана 3-D ячейка «MRAM» технического решения, принятого за прототип: (6-1) - ток записи; (6-2) - элемент «MTJ»; (6-3) - транзистор МОП; (6-4) - шина записи/разрядная (чтения); (6-5) - шина ввода данных.

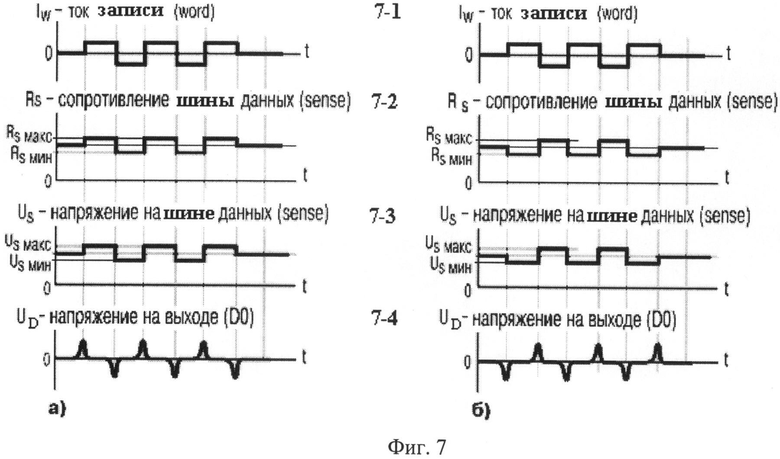

На Фиг.7 показаны эпюры протекания токов записи/чтения в ячейке «STT-MRAM» для случая хранения а) логического «0» и б) логической «1»: (7-1) - IW - ток записи (word); (7-2) - RS - сопротивление шины данных (sense); (7-3) - US - напряжение на шине данных (sense); (7-4) - UD - напряжение на выходе данных.

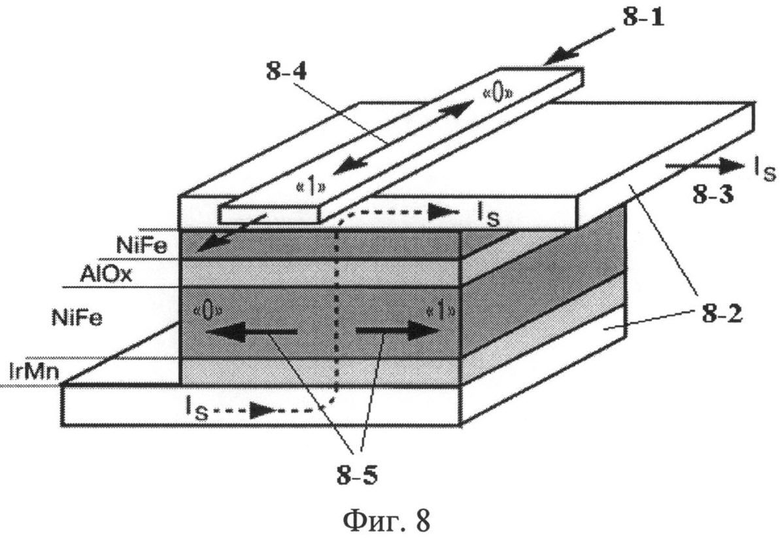

На Фиг.8 показана структура ячейки памяти ИМС 1T1MTJ «MRAM»: (8-1) - шина записи/чтения (Word); (8-2) - шина данных (Sense); (8-3) - IS - ток чтения данных; (8-4) - «0»↔«1» - полярность тока записи/чтения; (8-5) - «0»∞←; →∞«1» - полярность вектора намагниченности.

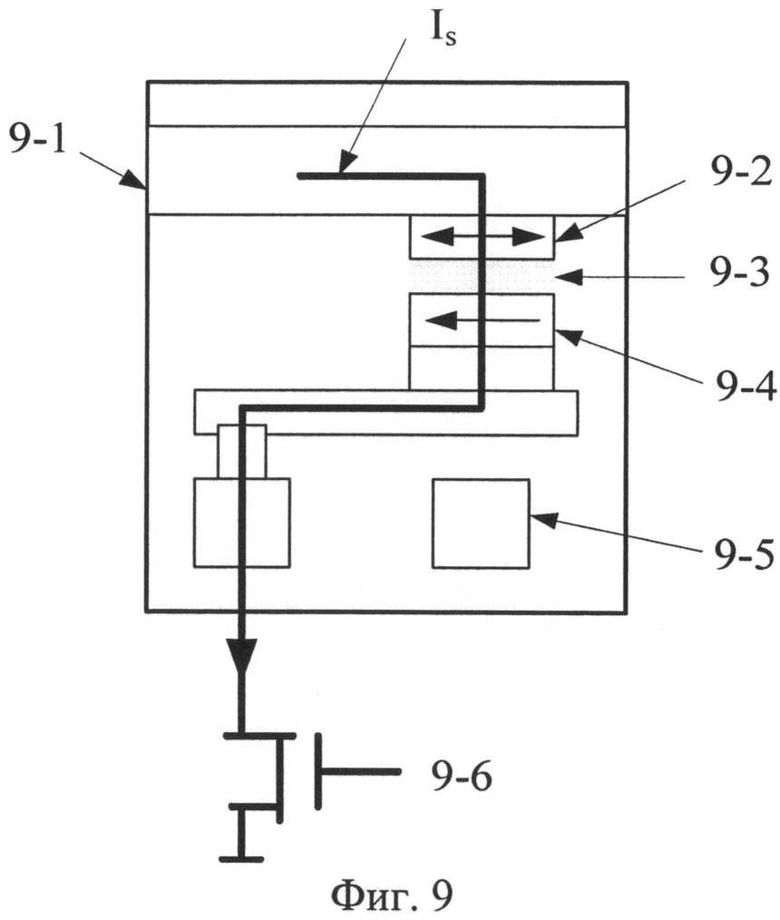

На Фиг.9. показано поперечное сечение ячейки «STT-MRAM» со структурой «MTJ»: (9-1) - шина данных; (9-2) - СС; (9-3) туннельный барьер; (9-4) - ФС; (9-5) - шина разряда; (9-6) - изолирующий транзистор («ВКЛ» при чтении).

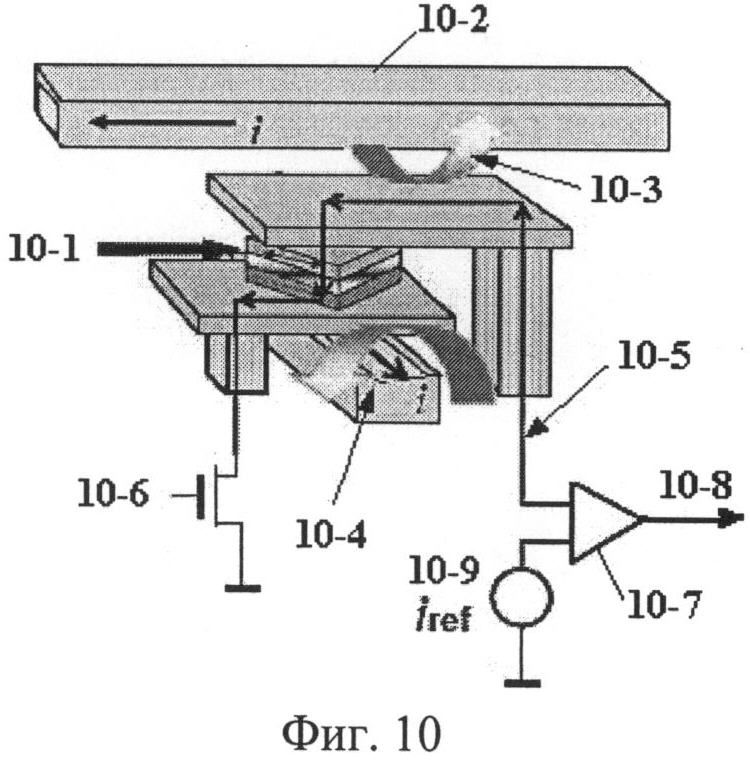

На Фиг.10 показана 3-D ячейка «STT-MRAM» конструкции Савченко: (10-1) - ячейка «MTJ»; (10-2) - шина разряда; (10-3) - магнитное поле; (10-4) шина слов; (10-5) - ток чтения; (10-6) - транзистор МОП («ВКЛ» при считывании, «ОТКЛ» при записи); (10-7) - компаратор; (10-8) - выходные данные; (10-9) - IREF - опорный источник.

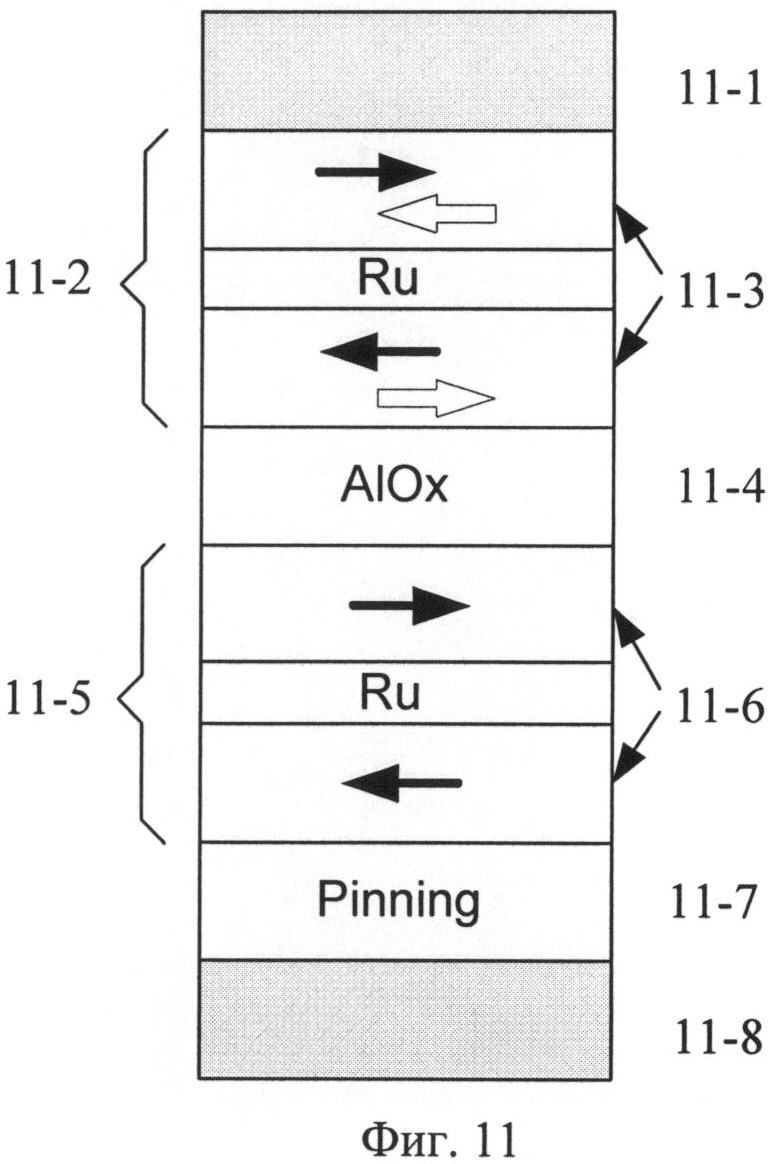

На Фиг.11 показано поперечное сечение элемента «MTJ» с эффектом «пиннинга»: (11-1) - верхний электрод; (11-2) - составной магнитный слой; (11-3) - сенсорный слой; (11-4) - магнитный барьер; (11-5) - магнитный слой; (11-6) - эталонный слой; (11-7) - «Pinning»; (11-8) - базовый электрод.

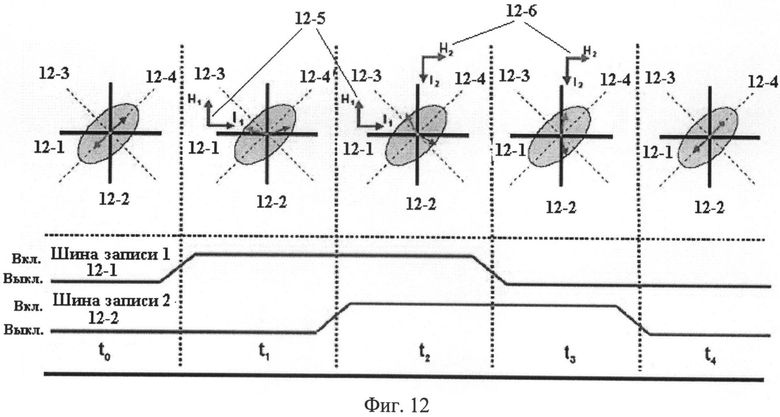

На Фиг.12 показана временная диаграмма сигналов записи и соответствующие ей повороты магнитных осей в составном сенсорном слое ячейки «MRAM» («Freescale»): (12-1) - шина «1» записи; (12-2) - шина «2» записи; (12-3) ось трудного намагничивания; (12-4) - ось легкого намагничивания; (12-5) - расположение векторов поля

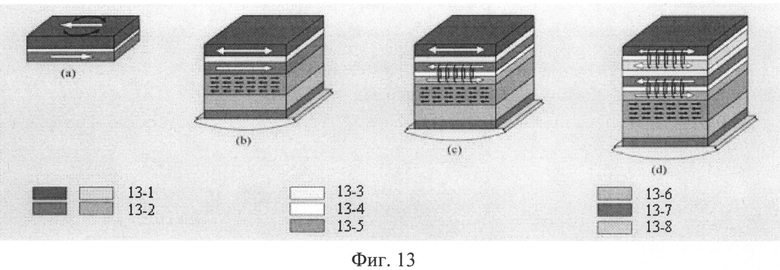

На Фиг.13 показана эволюция архитектуры «MTJ», конструированная под «MRAM» (а) базисная структура «MTJ»; (b) структура «MTJ» с ферромагнитным слоем, запинингованным на антиферромагнетике;(с) структура «MTJ» с ферромагнитным слоем, запинингованным на искусственном антиферромагнетике; (d) структура «MTJ», в котором оба электрода содержат пары слоев: (13-1) - магнитный СС; (13-2) - пиннингуемый магнитный слой; (13-3) - пленка туннельного барьера; (13-4) - пленка, содержащая Ru; (13-5) - антиферромагнитная пленка со смещением; (13-6) - прослойки; (13-7) - засеянные пленки; (13-8) - подложка.

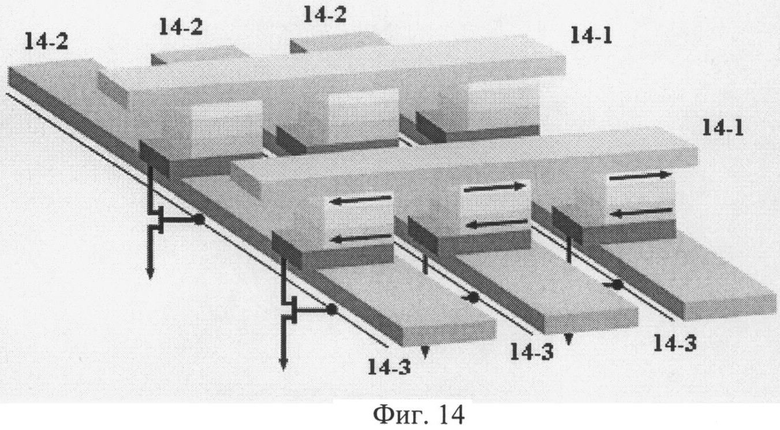

На Фиг.14 приведена 3-D схема расположения шин разряда («ШР»), записи слова («ШЗС»), чтения («ШЧ») и транзисторов МОП в элементе матрицы «STT-MRAM»: (14-1) - разрядная шина; (14-2) - шина данных; (14-3) - шина записи/чтения.

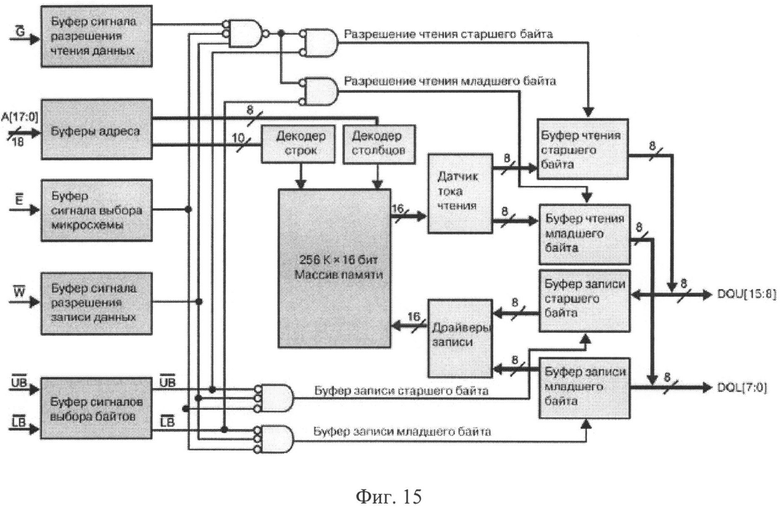

На Фиг.15 приведена блок-схема микросхемы MR2A16A.

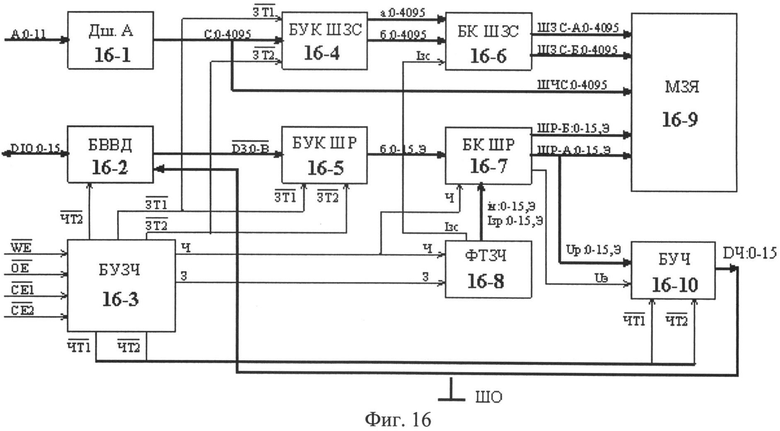

На Фиг.16 приведена блок-схема матрицы памяти «STT-MRAM»: (16-1) - блок дешифратора адреса («Дш.А»); (16-2) - блок управления вводом/выводом данных («БВВД»); (16-3) - блок управления записью/чтением («БУЗЧ»); (16-4) - блок управления ключами шины записи слова («БУК ШЗС»); (16-5) - блок управления ключами шины разряда («БУК ШР»); (16-6) - блок ключей шины записи слова («БК ШЗС»); (16-7) - блок ключей шины разряда («БК ШР»); (16-8) - блок формирователя токов записи/чтения («ФТЗЧ»); (16-9) - матрица запоминающих ячеек («МЗЯ»); (16-10) - блок усилителей чтения данных («БУЧ»),

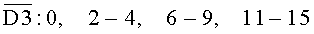

На Фиг.17 приведены эпюры изменения сигналов в режиме записи данных.

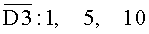

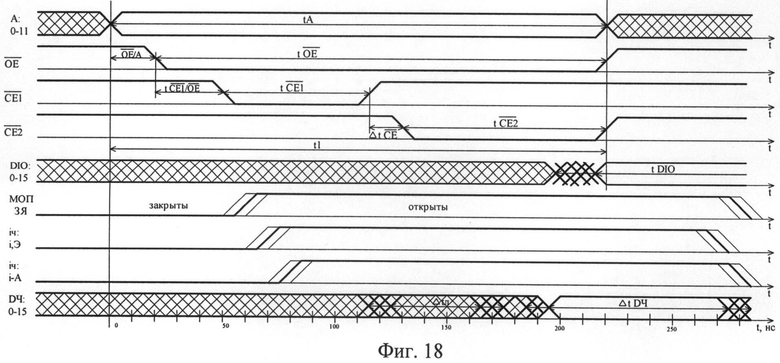

На Фиг.18 приведены эпюры изменения сигналов в режиме чтения данных.

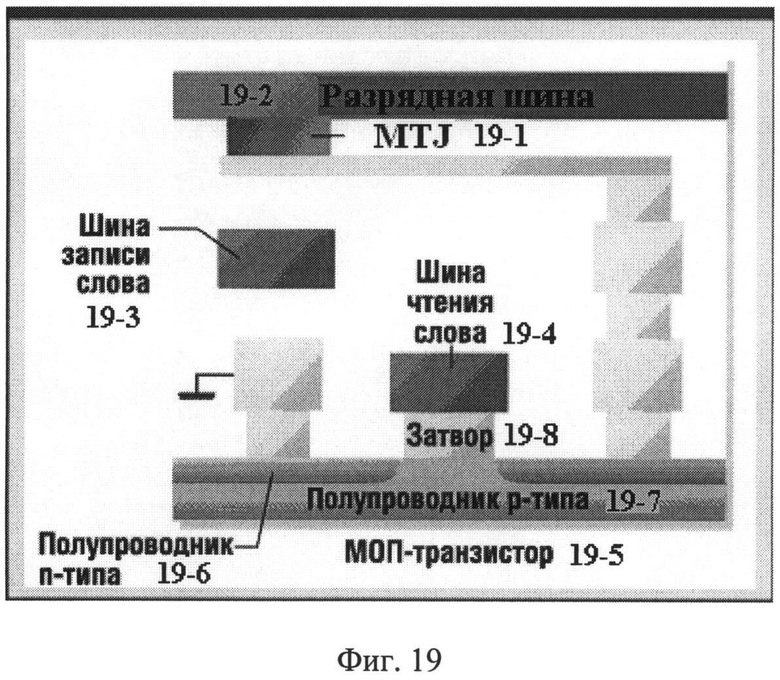

На Фиг.19 приведено поперечное сечение запоминающей ячейки «МЗЯ» устройства «STT-MRAM»: (19-1) - элемент «MTJ»; (19-2) - шина разряда; (19-3) - шина записи слова; (19-4) - шина чтения слова; (19-5) - транзистор МОП; (19-6) - n-Si; (19-7) - p-Si; (19-8) - затвор транзистора МОП.

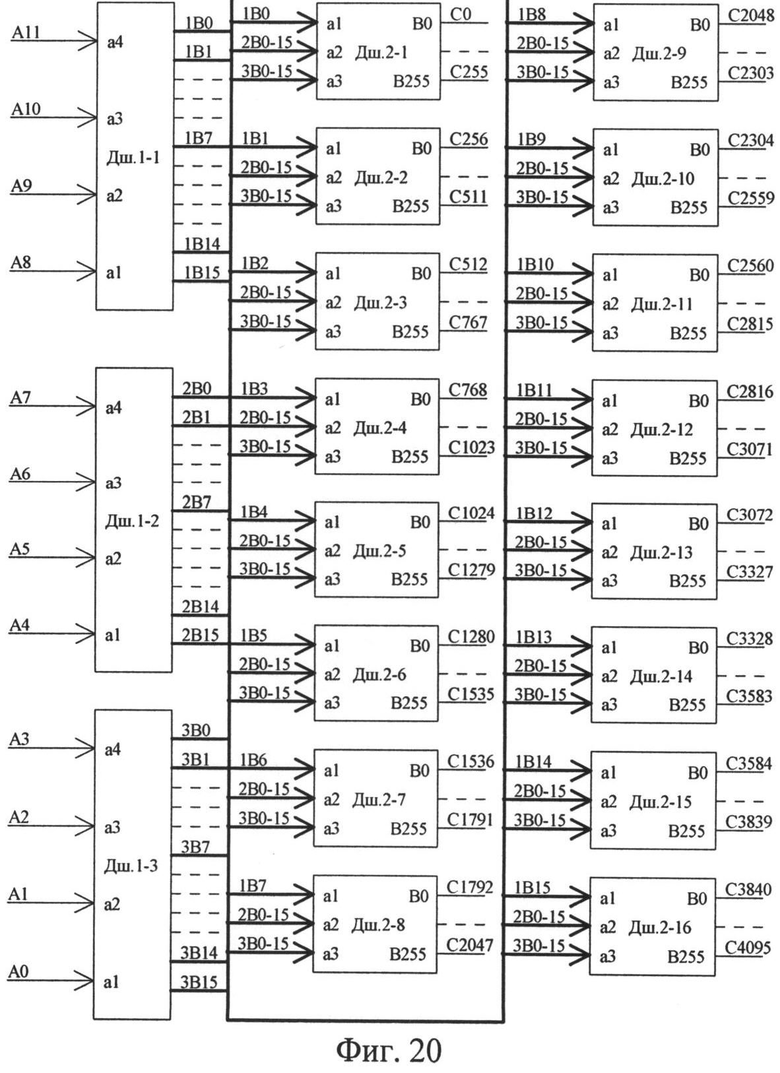

На Фиг.20 приведена принципиальная электрическая схема блока дешифратора адреса («Дш.А»): «Дш1-i» - дешифратор адреса 1-го типа; «Дш2-i» - дешифратор адреса 2-го типа; «Bi» - выход дешифратора 1-го типа; «ai» - входы дешифратора 1-го; «ЧТ2-В» - сигнал второго цикла чтения высокого уровня; Ai - входные сигналы дешифратора; Ci - выходные сигналы дешифратора, i=0-4095.

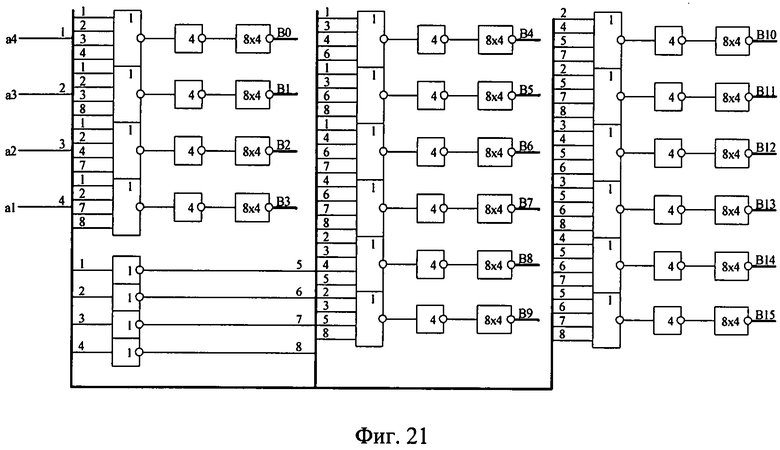

На Фиг.21 приведена принципиальная электрическая схема канала «Дш.А» первого типа.

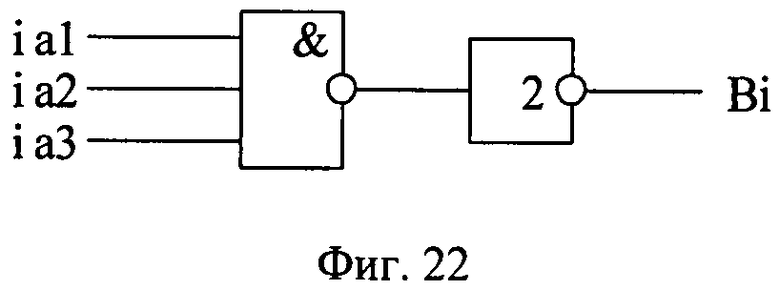

На Фиг.22 приведена принципиальная электрическая схема канала «Дш.А» второго типа.

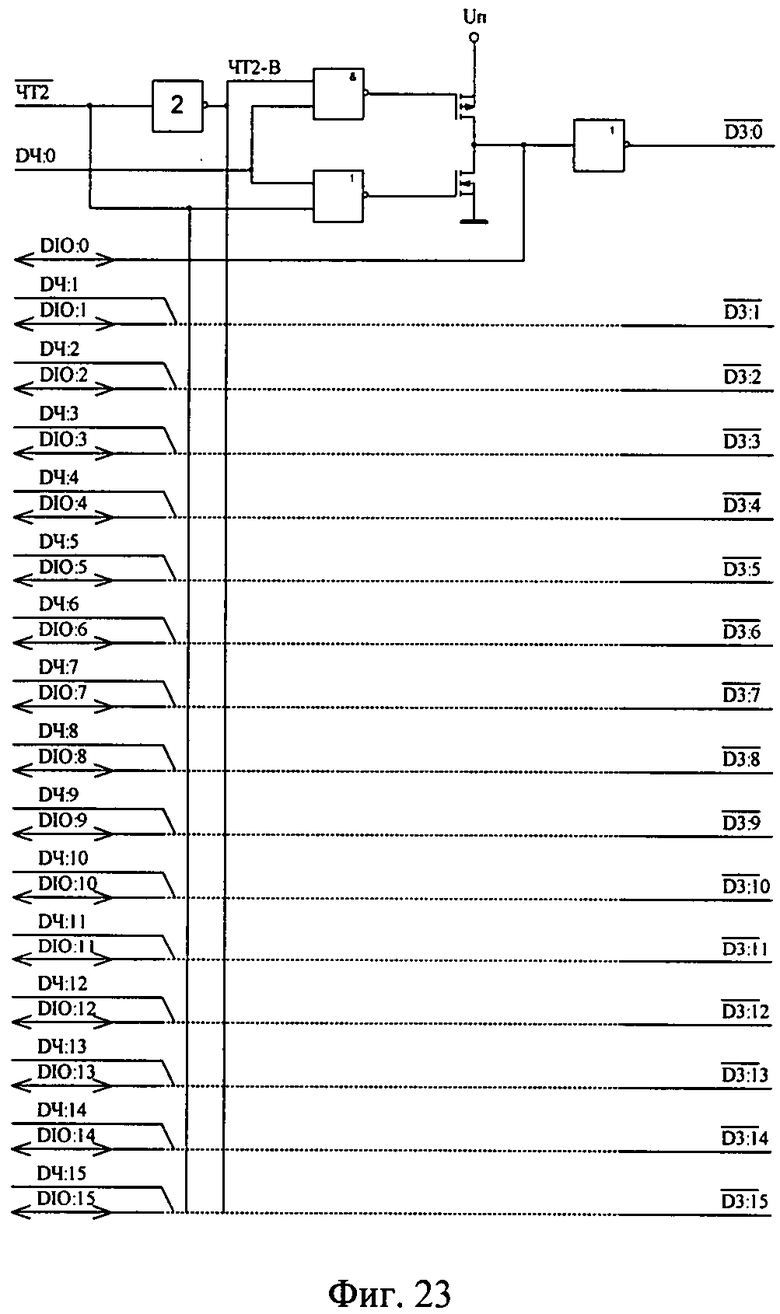

На Фиг.23 приведена принципиальная электрическая схема «БВВД».

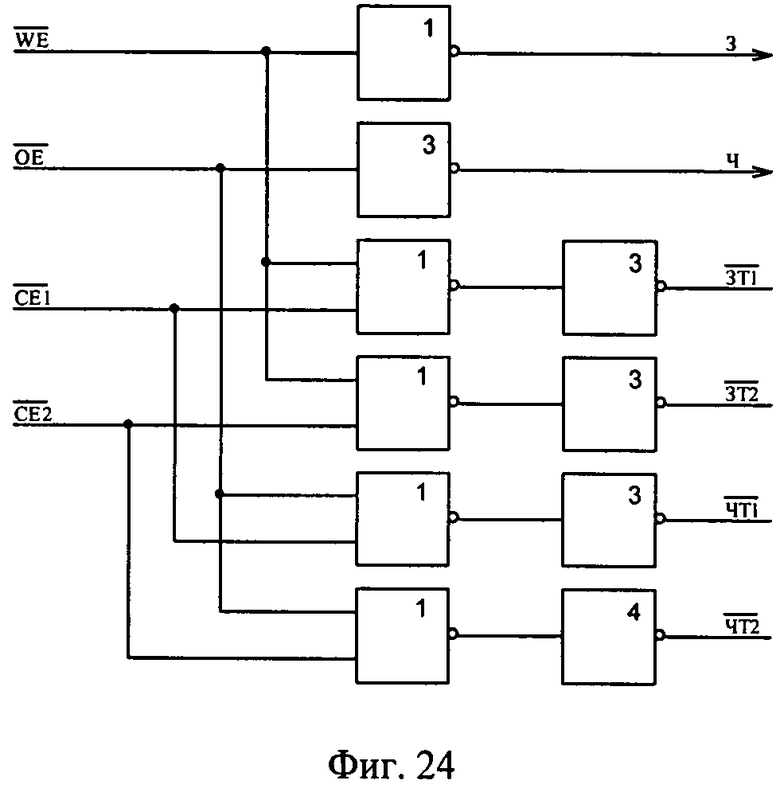

На Фиг.24 приведена принципиальная электрическая схема «БУЗЧ».

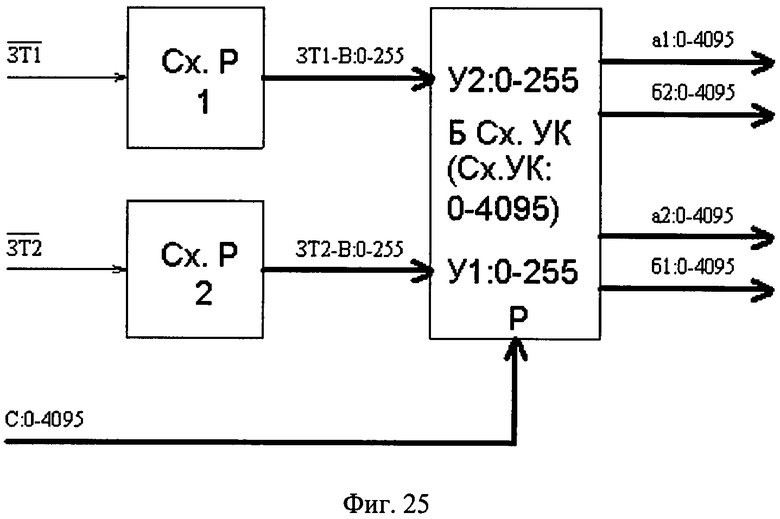

На Фиг.25 приведена функциональная схема «БУК ШЗС»: «Cx.P1», «Cx.P2» - схемы разветвления; «БСх.УК» - схема управления ключами; «Сх.УК:0-4095» - схемы управления ключами; «P» - вход схемы управления ключами; «У1:0-255» - входы «1» схемы управления ключами; «У2:0-255» - входы «2» схемы управления ключами; «ЗТ2-В:0-255» - сигнал записи 2-го цикла; «ЗТ1-В:0-255». - сигнал записи 1-го цикла.

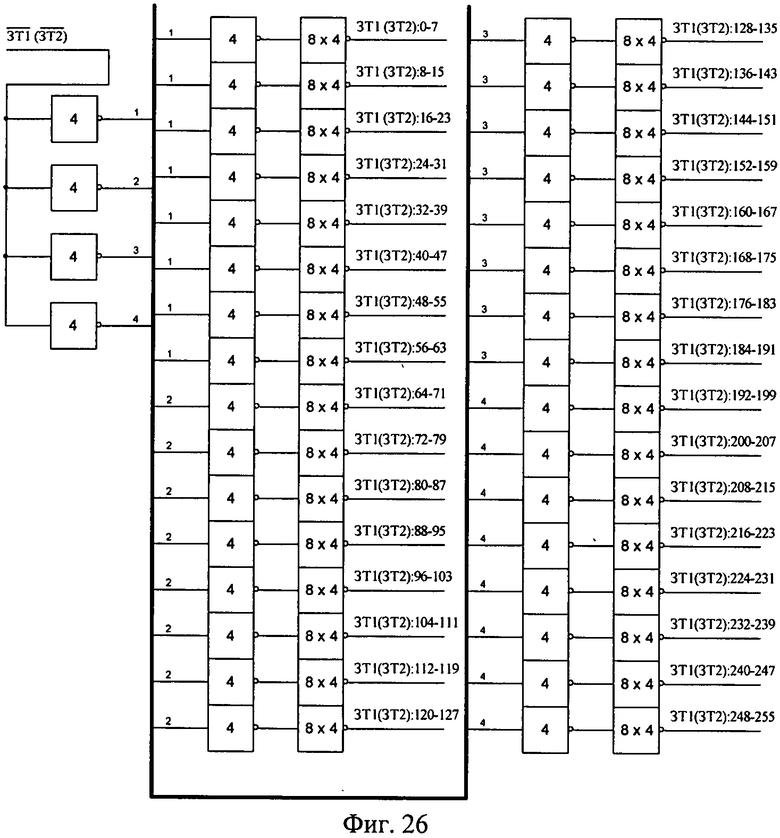

На Фиг.26 приведена принципиальная электрическая схема разветвления «Сх.Р».

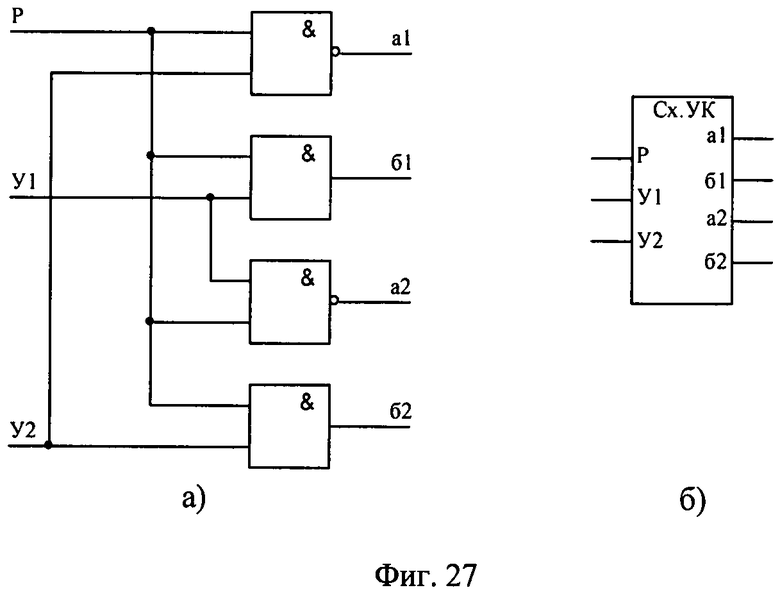

На Фиг.27 приведена принципиальная электрическая схема управления ключами: а) внутренняя структура; б) условное обозначение.

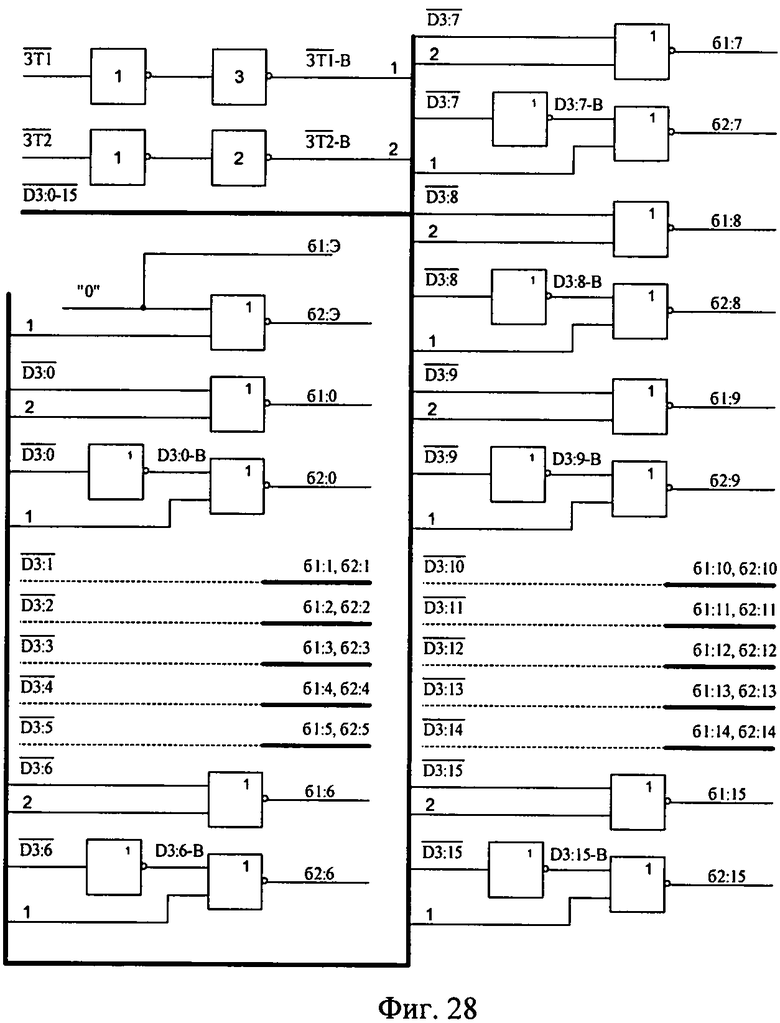

На Фиг.28 приведена принципиальная электрическая схема «БУК ШР»: «б1:Э» - сигналы; «б2:Э» - сигналы; «б1:0-15» - сигналы; «a2:i» - сигналы; UЭ - эталонный сигнал.

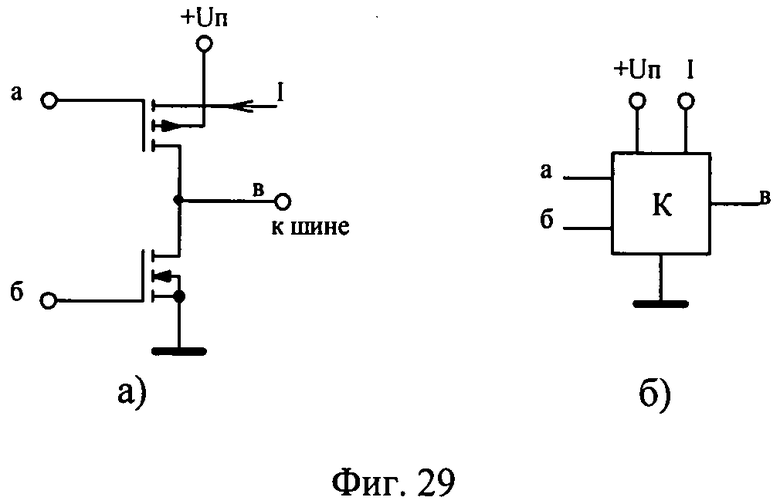

На Фиг.29 приведена а) электрическая схема ключа коммутации тока и б) его условное обозначение.

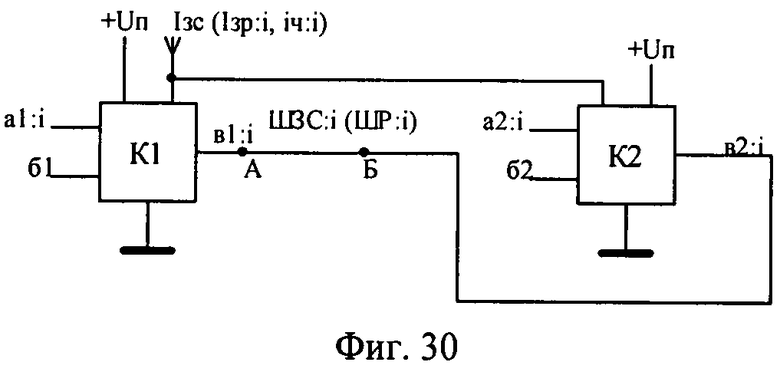

На Фиг.30 приведена принципиальная электрическая схема канала «БК ШЗС»: «К1» - 1-й ключ; «К2» - 2-й ключ; «Bl-i» - 1-й выход; «B2-i» - 2-й выход.

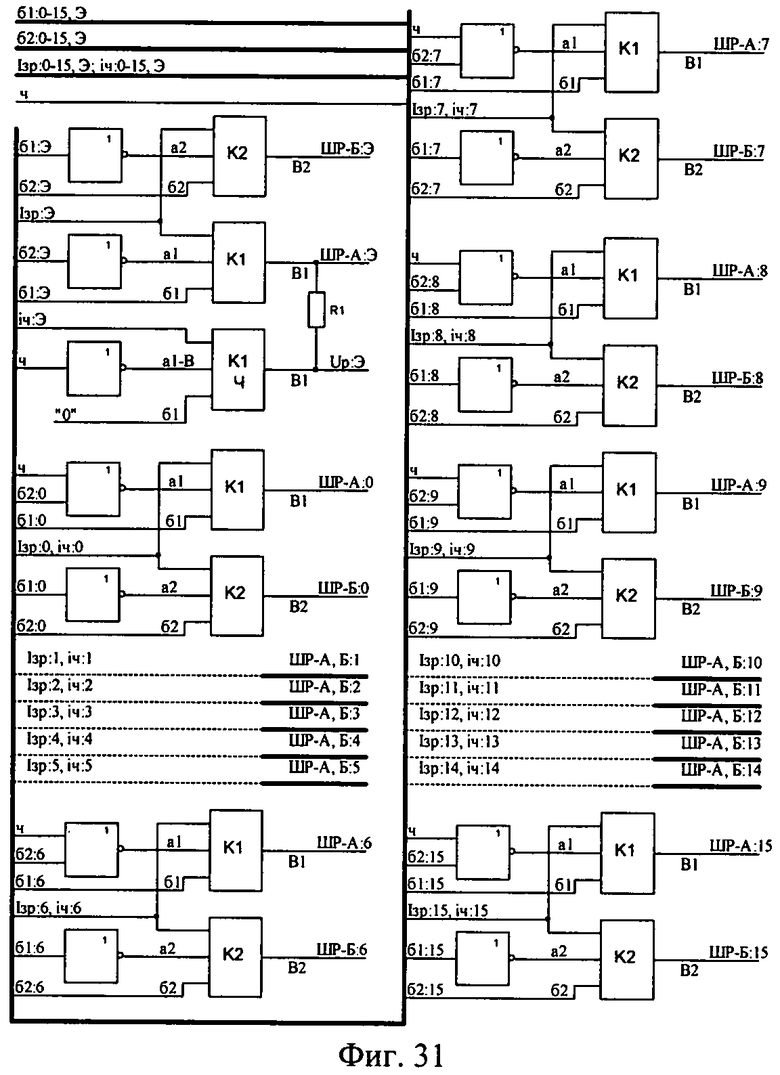

На Фиг.31 приведена принципиальная электрическая схема «БК ШР»: «K1» - 1-й ключ; «К2» - 2-й ключ; «R1» - резистор; «a1:i» - сигналы; «a2:i» - сигналы; UЭ - эталонный сигнал.

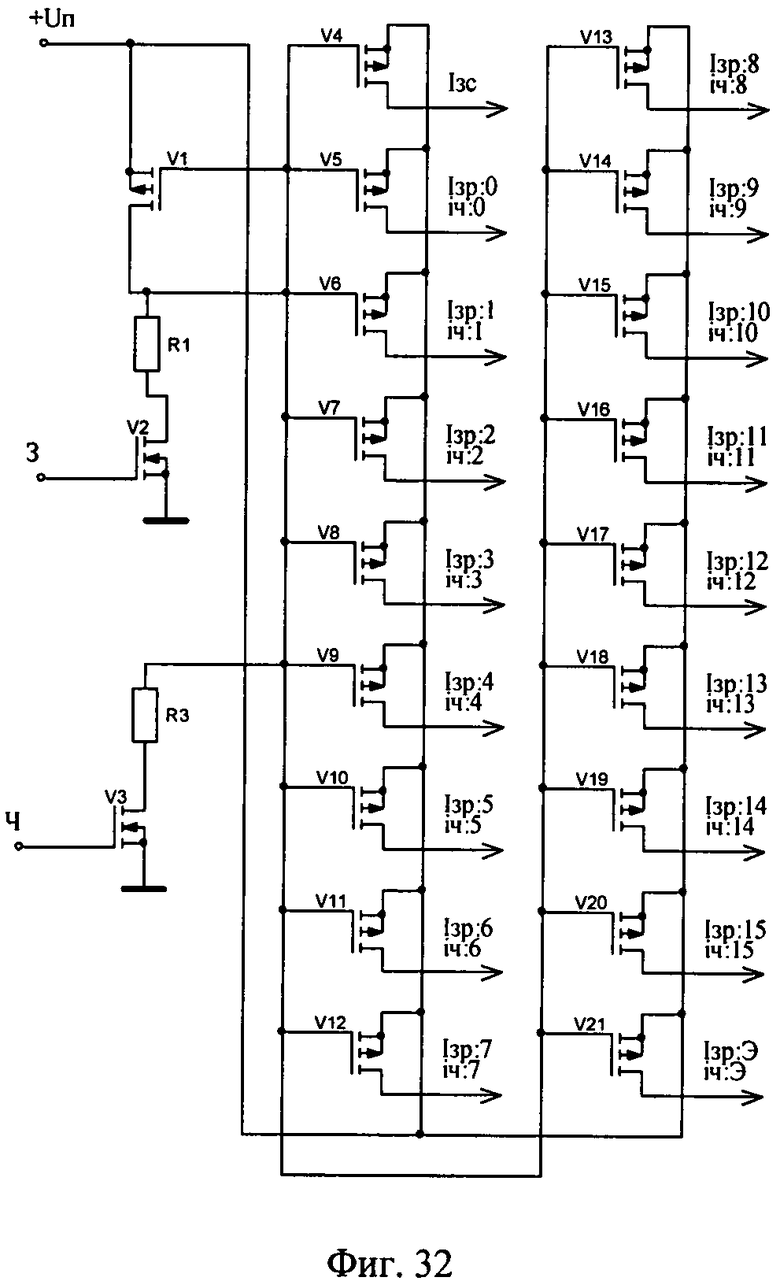

На Фиг.32 приведена принципиальная электрическая схема «ФТЗЧ»: V1 - транзистор МОП; V2-V24 - транзисторы МОП; «IЗ» - ток записи; «IЧ» ток чтения через резистор R2; R2 - резистор.

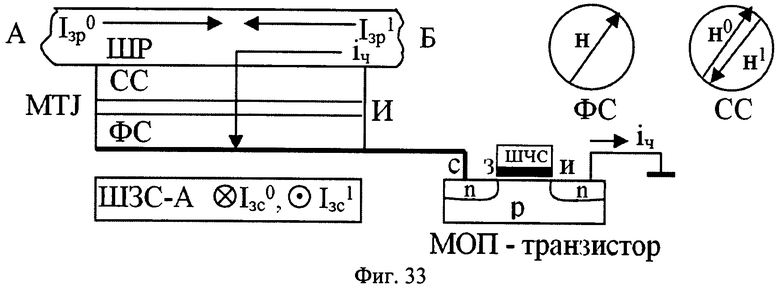

На Фиг.33 приведена запоминающая ячейка («ЗЯ») с системой шин: «ШР-А» - конец «А» шины разряда; «ШР-Б» - конец «Б» шины разряда;

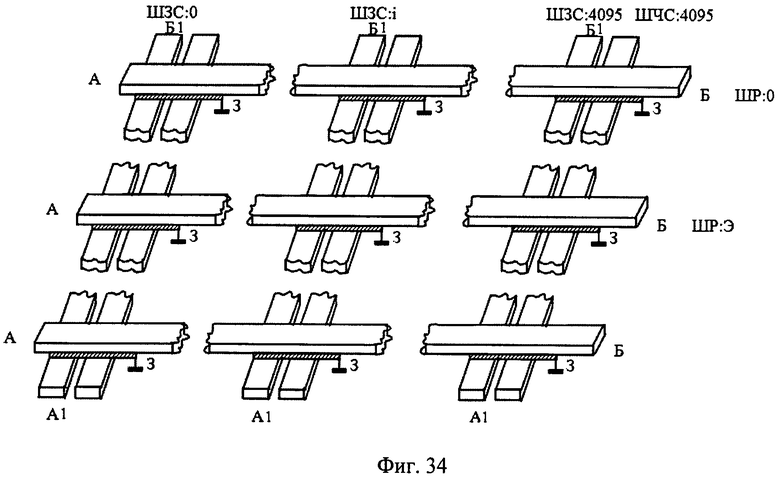

На Фиг.34 приведена принципиальная электрическая схема матрицы «ЗЯ»: А - конец «А» ШР; Б - конец «Б» ШР; ШР:0 - шина разряда «1»; ШР:Э - шина разряда «Э»; Б1 - конец «Б1» ШЗС; ШЗС:0 - шина «0»-я записи слова; ШЗС:i - шина «i» записи слова; ШЗС:4095; ШЧС:4095 - шина «4096» записи/чтения слова; «ШО» - общая шина.

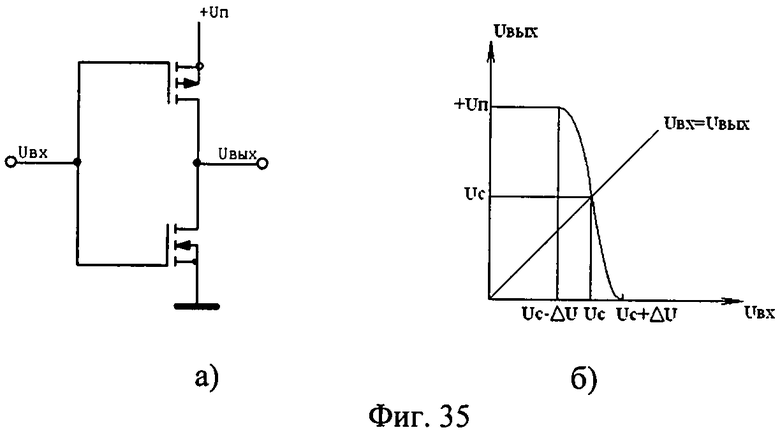

На Фиг.35 приведены: а) инвертор КМОП; б) его передаточная характеристика.

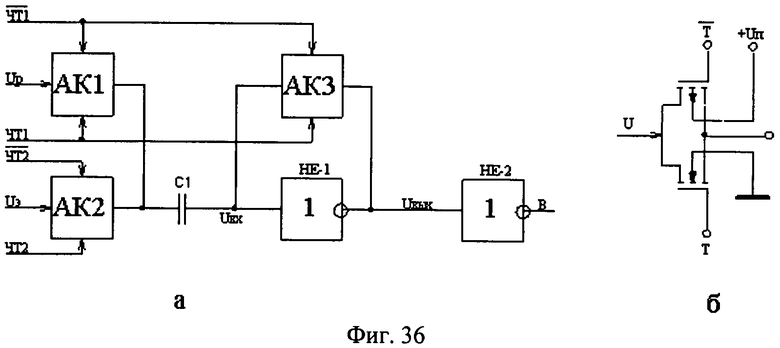

На Фиг.36 приведены: а) принципиальная электрическая схема компаратора напряжения: «НЕ-1» - инвертор КМОП; «НЕ-2» - инвертор КМОП; «АК1» - аналоговый ключ двунаправленный; «АК2» - то же самое; «АКЗ» - то же самое; «В» - напряжение на выходе компаратора; «ЧТ1» - сигнал чтения высокого уровня 1-го цикла; «ЧТ2» - сигнал чтения высокого уровня 2-го цикла; Cl - разделительный конденсатор, б) аналогового ключа.

На Фиг.37 приведена принципиальная электрическая схема «БУЧ».

Пример конкретной реализации.

Технический результат достигается тем, что решением задачи создания матрицы памяти «STT-MRAM» является устройство матричного типа, управляемое внешними сигналами записи/чтения информации и ввода/вывода данных, содержащее: множество устройств на магнитных туннельных переходах «MTJ» с передачей спинового вращения, организованных в матрицу, и устройства выборки конкретного элемента «MTJ» для организации записи/чтения информации, ввода/вывода данных, источников тока, соединенных с соответствующими устройствами «MTJ», для изменения полярности намагниченности свободного слоя каждого устройства «MTJ».

Для придания исходной анизотропии намагниченности свободного и фиксированного ферромагнитного слоев каждой запоминающей ячейки «STT-MRAM», при формировании топологии устройства «MTJ» оно выполнено в виде эллипса с осью легкого намагничивания, направленной по его большой оси.

Зависимость магнитосопротивления одного из магнитных элементов эллиптической формы двухслойной магнитной структуры CoFe/TaOx/CoFe от магнитного поля R(H), приложенного вдоль длинной оси магнитного элемента, эллиптической формы (размер 300×200 нм) позволила определить изменения величины магнитосопротивления порядка 3% при падении напряжения на структуре «MTJ» 10-500 мВ при пропускании тока ~1-50 мкА. Сопротивление структуры составляло ~10 кОм. Величина магнитосопротивления составила ~ 3% при падении напряжения 10 мВ и плавно уменьшалась с ростом измерительного тока. При приложении внешнего магнитного поля порядка 500 Э намагниченности слоев становились коллениарными. При уменьшении величины магнитного поля, намагниченности слоев начинали разворачиваться относительно друг друга, т.е. возникало угловое состояние. Этот разворот происходил до величины магнитного поля величины порядка ноля эрстед. При изменении направления внешнего магнитного поля на зависимости сопротивления от величины магнитного поля R(H) наблюдался скачок - частица переходила в антиферромагнитное состояние, намагниченности слоев были б) аналогового ключа противоположно направлены. Это состояние являлось устойчивым до полей порядка 500 Э, при увеличении величины поля R(H) скачком уменьшается, что соответствует переходу частицы в состояние с ферромагнитным упорядочиванием слоев.

С уменьшением размера магниторезистивного элемента до 200×100 нм удалось добиться, чтобы существовало только два устойчивых состояния во внешнем магнитном поле. Величина изменения магнитосопротивления составила порядка 2%. Фактически этот элемент позволяет хранить информацию при выключении внешнего поля.

Проведены измерения зависимости сопротивления от магнитного поля, направленного вдоль короткой оси частицы. Эти измерения показали, что сопротивление системы пропорционально косинусу угла между магнитными моментами слоев.

Таким образом, продемонстрирована возможность наблюдения магнитосопротивления в двухслойной магнитной структуре CoFe/TaOx/CoFe. Полученные результаты открывают возможность начала разработки конструкции магниторезистивных элементов запоминающих устройств на основе эффекта туннельного магнитосопротивления. Этот результат был достигнут благодаря разработке и освоению методов изготовления магниторезистивных элементов с размерами 100×200 нм, помещенных между подводящими электродами.

Блоки устройства организации записи/чтения информации объединены для формирования информационного бита на основе относительных полярностей свободного слоя каждого устройства «MTJ», и блок усилителя чтения данных, соединенный с шиной ввода/вывода, выполнен с возможностью обнаруживать уровень сигнала в шине ввода/вывода разряда и формировать двоичный выходной сигнал на основе сравнения уровня сигнала в разряде матрицы с пороговым уровнем сигнала. С целью изменения полярности намагниченности верхнего свободного ферромагнитного слоя устройства «MTJ» процедура записи/чтения проводится в два цикла под управлением внешних разрешающих сигналов «

При этом по заднем фронту "0"→"1" сигнала разрешения записи первого цикла «

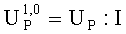

На Фиг.16 приведена блок-схема ИМС матрицы памяти «STT-MRAM» емкостью 64 кбит (16 К×16) с 16-разрядной двунаправленной шиной данных. На входы микросхемы поступают из внешнего по отношению к микросхеме устройства сигналы управления ее работой: «

По шине адреса «А:0-11» на микросхему поступают сигналы адреса, код которых определяет слово памяти, к которому производится обращение в режиме записи или чтения информации. По двунаправленной 16-разрядной шине данных «DIO:0-15» вводятся сигналы данных, которые необходимо записать в слово памяти по заданному адресу, в режиме записи или чтения данных, которые считаны из слова памяти по заданному адресу в режиме чтения информации. На Фиг.17 и Фиг.18 приведены временные диаграммы сигналов, поступающих на микросхему соответственно в режиме записи и чтения информации, и сигналы, вырабатываемые блоками микросхемы.

Блок дешифратора адреса (16-1) «Дш.А» вырабатывает на одном «C:i» из своих выходов «С:0-4095» сигнал с уровнем логической «1», обеспечивающий обращение к выбранному слову матрицы запоминающих ячеек (16-9) «МЗЯ» в соответствии с кодом адреса, сигналы которого поступают по шине «А:0-11», при этом i равно численному значению кода адреса.

Блок ввода-вывода данных (16-2) «БВВД» обеспечивает передачу сигналов 16-разрядного кода данных: с шины «DIO:0-15» на входы «

Блок управления записью и чтением информации (16-3) («БУЗЧ») обеспечивает: передачу сигнала «

Блок управления ключами шин записи слова (16-4) «БУК ШЗС» в зависимости от состояния сигналов «С:0-4095», «

Блок управления ключами разрядных шин (16-5) «БУК ШР» в зависимости от состояния сигналов «

Блок ключей шин записи слова (16-6) «БК ШЗС» обеспечивает соединение концов «ШЗС» выбранного для записи слова к источнику «IЗС» и «ШО» в режиме записи и отключение шин «ШЗС» в соответствии с описанием работы (16-4) «БУК ШЗС».

Блок ключей шин разряда (16-7) «БК ШР» обеспечивает: соединение концов «LUP:i» к источникам тока «IЗР:0-15, Э» и «ШО» в режиме записи и их отключение в соответствии с описанием работы (16-5) «БУК ШР»; соединение концов «A» («ШР:i» к источнику тока «IЧ:0-15, Э» и отключение концов «Б» (16-37) «ШР:i» при высоком уровне сигнала чтения «Ч», при этом считанные из (16-9) «МЗЯ» сигналы «UP:0-15» подаются на блок усилителей чтения (16-10) «БУЧ» с «ШР-А:0-15», а сигнал чтения «0» «UP:Э» - с дополнительного выхода (16-7) «БК ШР».

Блок формирователя токов записи и чтения (16-8) «ФТЗЧ» вырабатывает: при высоком уровне сигнала записи «З» стабильные токи записи слова «IЗС» и разрядные токи записи «IЗР:0-15, Э»; при высоком уровне сигнала чтения «Ч» стабильные токи чтения «IЧ:0-15, Э».

Матрица запоминающих ячеек (16-9) «МЗЯ» предназначена для энергонезависимого хранения информации, записанной в 4096 шестнадцатиразрядных словах, и обеспечивает пословную запись и чтение информации. На Фиг.19 приведено схематическое изображение запоминающей ячейки «ЗЯ», которая состоит из магнитного туннельного перехода (19-1) «MTJ», (19-5) транзистора МОП и системы шин: (19-2) «ШР», (19-3) «ШЗС», (19-4) «ШЧС».

Каждое слово состоит из 17 «ЗЯ», одна из которых эталонная, установленная в состояние «0» и служащая для выработки эталонного напряжения UЭ при чтении информации из данного слова, что позволяет компенсировать частично технологические отклонения сопротивлений низкого RH и высокого RB уровней в (19-1) «MTJ» в словах /6/.

Блок усилителей сигналов чтения (16-10) «БУЧ» обеспечивает усиление считанных сигналов «UP:0-15» и выработку нормированных сигналов «D4:0-15» с уровнем логической «1» или «0» при поступлении сигнала «

На Фиг.20 приведена схема функциональная блока дешифратора адреса (16-1) «Дш.А».

При разработке больших матричных кристаллов (БМК) чаще всего применяются логические элементы типа «И-НЕ», «ИЛИ-НЕ» с числом входов не более 4 с коэффициентом разветвления не более 8 входов /7/. За один вход принимается два затвора транзисторов МОП. Для увеличения коэффициента разветвления используют параллельное соединение 2, 3 или 4 инверторов (далее по тексту «НЕ2», «НЕ3» или «НЕ4»), которые обеспечивают соответственно коэффициенты разветвления 16, 24 или 32 при использовании транзисторов МОП с одинаковыми параметрами (размерами).

В соответствии с этим для реализации функций блока (16-1) «Дш.А» выбрана функциональная схема, состоящая из трех однотипных дешифраторов «Дш.1-1», «Дш.1-2», «Дш.1-3» первого типа, построенных на основе элементов «4ИЛИ-НЕ» и шестнадцати однотипных дешифраторов «Дш.2.1-Дш.2.16», построенных на основе элементов «3И-НЕ».

Поскольку каждый выход «Bi» дешифратора первого типа «Дш.1» должен работать на 256 входов дешифраторов второго типа «Дш.2», он показан в виде шины, состоящей из 8 проводников, каждый из которых соединен с выходом инвертора «НЕ4», способным работать на 32 входа логических элементов.

В табл.1 приведено состояние выходов «В1-В16» дешифратора первого типа от комбинации сигналов, поступающих на его входы «а1-а4».

Из табл.1 следует, что числовое значение двоичного кода, сигналы которого поступают на входы «а4-а1», соответствуют номеру выхода, на котором вырабатывается сигнал с уровнем логической «1».

Дешифратор второго типа «Дш.2-1» вырабатывает сигнал с уровнем логической «1» на одном из выходов «Bi» при условии, что на его вход «а1» поступает с «Дш.1-1» сигнал с уровнем логической «1», при этом i=(NBДш.1-2)·16+(NBДш.1-3), где NB - номер выходов соответственно «Дш.1-2» и «Дш.1-3», на которых вырабатывается сигналы с уровнем логической «1», поступающие соответственно на входы «а2» и «а3» «Дш.2». Таким образом, на одном из выходов «C:i» (16-1) «Дш.А» вырабатывается сигнал с уровнем логической «1», где i соответствует числовому значению кода адреса «A11-A0».

Каждый выход дешифратора второго типа нагружен на 13 входов: 4 входа (16-4) «БУК ШЗС» и 17 затворов транзисторов МОП «ЗЯ» выбранного слова (16-9) «МЗЯ».

На Фиг.21 приведена принципиальная электрическая схема дешифратора первого типа. На каждом выходе «Bi» (i=0…15) дешифратора установлен блок инверторов 8×4, состоящий из 8 инверторов «НЕ4», выходы которых ниже будем обозначать «Bi-1», «Bi-2»…«Bi-8».

Вход каждого инвертора «НЕ4», входящего в блок инверторов 8×4, эквивалентен 4 простым входам (2 затвора транзисторов МОП). Поэтому между элементами «4ИЛИ-НЕ» и блоком инверторов установлен для согласования нагрузок инвертор «НЕ4».

В табл.2.1 приведено состояние выходов дешифратора от комбинации сигналов, поступающих на его входы «а1-а4».

На Фиг.22 приведена принципиальная электрическая схема одного (i) из 256 каналов дешифратора второго типа, где i=0,1…255.

На выходе «Bi» i-го канала «Дш.2» вырабатывается сигнал «C(i+n256)», где n=0, 1…15 соответственно для Дш.2-1, Дш.2-2…Дш.2-16.

В табл.2 приведены соединения входов «а1» «Дш.2-1-Дш.2-16» с выходами «Дш.1-1».

В табл.3 и 4 приведены соединения соответственно входов «а2» и «а3» любого «Дш.2» с выходами «Дш.1-2» и «Дш.1-3».

Дш.1-3

Блок ввода-вывода данных (16-2) «БВВД» в режиме записи должен отключать шины «DIO:0-15» от выходов усилителей чтения и вырабатывать сигналы «

В режиме чтения на входы инвертора «НЕ2» и элемента «2ИЛИ-НЕ» поступает сигнал «

Блок управления записью и чтением данных (16-3) «БУЗЧ» вырабатывает сигналы управления в режимах записи и чтения в соответствии с временными диаграммами, приведенными на Фиг.17 и Фиг.18. Сигналы чтения «

Блок управления ключами шин записи слова (16-4) «БУК ШЗС» выполнен: из двух одинаковых схем разветвления «Сх.Р1» и «Сх.Р2», предназначенных для разветвления соответственно сигналов «

Входы «У1» и «У2» каждых 8-и «Сх.УК.-i» («Сх.УК:0-7», «Сх.УК:8-15» и т.д.) соответственно объединены между собой, образуя 256 входов «У1:0-255» и «У2:0-255) «БСх.УК», при этом на «У1:1» и «У2:1» поступает соответственно сигнал «ЗT2-Bi» и «ЗТ1-Bi».

Сигналы с выходов «а1», «б1» и «а2», «б2» «Сх.УК:i» поступают соответственно на входы ключей «КА:i» и «КБ:i», выходы которых соединены соответственно с концами «А» и «Б» шины «ШЗС:i».

На Фиг.26 приведена принципиальная электрическая схема разветвления «Сх.Р».

Для увеличения коэффициента разветвления в схеме использованы инверторы «НЕ2» и «НЕ4», в которых параллельно соединены соответственно 2 и 4 инвертора. Инверторы «НЕ2» и «НЕ4» обеспечивают коэффициенты разветвления 16 и 32.

На входах «Сх.Р» установлены блоки инверторов «НЕ8×4»,. входы каждого блока соединены между собой и выходом инвертора «НЕ4».

Сигналы с 8-и выходов каждого блока «НЕ8×4» поступают на входы управления «У2i» («У1i») 16 схем управления ключами «Сх.УК:i».

На Фиг.27 приведена принципиальная электрическая схема схемы управления ключами «Сх.УК:i». Схема управления ключами «Сх.УК» обеспечивает выработку сигналов «а1», «б1», «а2», «б2» в зависимости от входных сигналов «P», «У1», «У2» в соответствии с табл.5.

Примечание: состояние «У1»=«У2» запрещено при «P»=«1», x может принимать состояние «1» или «0».

Принципиальная электрическая схема блока управления ключами шин разрядов (16-5) «БУК ШР» приведена на Фиг.28.

Схема «БУК ШР» состоит из инверторов «НЕ1», «НЕ3» и «НЕ1», «НЕ2», предназначенных для задержки, инвертирования и разветвления соответственно сигналов «

Примечание: состояние «

В табл.7 приведено состояние выхода ключа в зависимости от уровня сигналов управления.

Ключи используются в (16-6) «БК ШЗС» и (16-7) «БК ШР».

Блок ключей шин записи слова (16-6) «БК ШЗС» состоит из 4096 одинаковых каналов. На Фиг.30 приведена принципиальная электрическая схема одного из каналов (i), состоящего из двух ключей «К1» и «К2» и соединения их выходов «В1» и «В2» с концами «А» и «Б» шины «ШЗС:i».

В табл.8 приведены уровни входных сигналов управления, обеспечивающих отключение шины «ШЗС:i» от источника тока «IЗС» (состояние «IЗС»=0), и изменение направления тока «IЗС» для обеспечения записи «0» (ток «

На Фиг.30 и в табл.8 в скобках приведены токи, коммутируемые ключами блока (16-7) «БКШР».

На Фиг.31 приведена принципиальная электрическая схема блока ключей шин разряда (16-7) «БК ШР», состоящая из 17 пар ключей, соединенных с концами «А» Фиг.30, ключа «К1Ч», соединенного с концом «А» шины «ШР:Э» через резистор «R1», и логических элементов «НЕ» и «2ИЛИ-НЕ», обеспечивающих выработку сигналов «a1:i», «a2:i» управления ключами «К1» и «К2» (сигналы управления «61:i», «62:i» поступают с (16-5) «БУК ШР»), где i=Э, 0-15. На Фиг.31 не показано подключение ключей к «ШО» и источнику «+UП».

В режиме записи сигналы управления обеспечивают протекание токов «

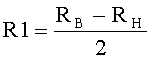

В режиме чтения: ключи «К2» и ключ «К1», непосредственно соединенный с концом «А» шины «ШР:Э», устанавливаются в третье состояние сигналами управления «a2:i», «а1:Э» высокого уровня и «б2:i», «б1:Э» низкого уровня, где i=Э, 0-15; ключи «К1» и «К1Ч» устанавливаются сигналами управления «a1:i», «б1:i» низкого уровня в состояние, обеспечивающее подачу токов чтения «IЧ:0-15» и «IЧ:Э» через резистор «R1» на концы «А» соответственно шин «ШР:i» (i=0-15, Э), при этом концы «Б» этих шин отключены от «ШО»; сигналы чтения «UP:0-15» поступают на (16-10) «БУЧ» с концов «А» шин «ШР:0-15», а эталонный сигнал UЭ=IЧЭ·(RH+R1) - с выхода «К1Ч», где

На Фиг.32 приведена принципиальная электрическая схема блока формирователя токов записи и чтения (16-8) «ФТЗЧ», основой которой является токовое зеркало, собранное на транзисторах МОП V1, V4-V21. При идентичности этих транзисторов токи «IЗС», «IЗР:0-15, Э» равны между собой и задаются в режиме записи током «1з», протекающим через резистор «R1» и открытый транзистор МОП V2, при этом транзистор V3 закрыт. В режиме чтения «IЧ:0-15, Э» равны между собой и задаются током «IЧ», протекающим через резистор «R2» и открытый транзистор V3, при этом транзистор V2 закрыт.

Описание работы и расчет токового зеркала приведен в /9/.

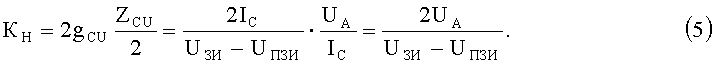

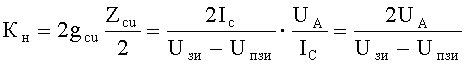

Изменение токов записи или чтения в зависимости от напряжения питания «+UП» составляет примерно 2% на 1 вольт, при этом должно выполняться условие:

где RH - низкое сопротивление MTJ, RB - высокое сопротивление MTJ «ЗЯ», UПЗИ - пороговое напряжение между затвором и истоком, при котором начинает протекать ток через транзистор МОП.

Напряжение UПЗИ составляет +1 В и -5 В соответственно для n-канального и p-канального транзистора МОП. С помощью ионного легирования подзатворного слоя можно получить UПЗИ=-1 В для p-канального транзистора МОП /10/.

Из соотношений (1) и (2) следует, что при UП=3,35±10%, IЗ=10 мА,

UПЗИ=1 B, RB=13 кОм сопротивление нагрузки RH не должно превышать 200 Ом, а ток чтения IЧ не должен превышать 0,15 мА.

На Фиг.33 приведено схематическое изображение «ЗЯ», системы шин и направления токов в шинах, обеспечивающих запись «0» («

Запоминающая ячейка состоит из магнитного туннельного перехода «MTJ» и n-канального транзистора МОП /10/.

Переход «MTJ» представляет собой «сэндвич», в котором два тонких слоя СС и ФС, проводящих ток ферромагнетиков, разделены тонким слоем И изолятора (обычно Al2O3), который при толщине менее 2 нм способен пропускать ток «IЧ» при открытом транзисторе МОП.

Сопротивление «MTJ» зависит от величины и направления векторов магнитного поля в СС и ФС, при этом направление вектора поля при записи информации в «ЗЯ» меняется только в СС. Принято считать, что если направление векторов магнитного поля в СС и ФС совпадают, то «ЗЯ» хранит «0», при этом «MTJ» имеет низкое сопротивление «RH», а если направления намагниченности коллениарны, то «ЗЯ» хранит «1», при этом «MTJ» имеет высокое сопротивление («RB»).

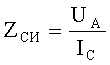

Для чтения информации, хранимой в «ЗЯ», необходимо пропустить через «MTJ» ток чтения «IЧ» от источника тока («IЧ» не зависит от «RH» или «RB») и измерить падение напряжения на сопротивлении «MTJ».

Основной характеристикой «MTJ» является относительное изменение сопротивления при хранении «1» и «0»:

На Фиг.34 приведена принципиальная электрическая схема матрицы запоминающих ячеек (16-9) («МЗЯ»), состоящей из 69632 запоминающих ячеек, размещенных под перекрестием шин «ШР» и «ШЗС», «ШЧС» в соответствии с Фиг.19.

Из-за несовершенства технологии изготовления «МЗЯ» сопротивления «RH» и «RB» «MTJ» в крайних словах (т.е. с номерами 0 и 4095) матрицы будут иметь наибольшие отклонения от среднего значения их в слове с номером 2047. Для компенсации этих отклонений в каждое слово введен эталонный разряд, шину «ШР:Э» которого помещают в середину слова.

Магнитный туннельный переход «ЗЯ» эталонного разряда хранит «О», который подновляется в цикле записи информации в слово. При чтении информации из эталонной «ЗЯ» в «БК ШР» вырабатывается эталонное напряжение

где

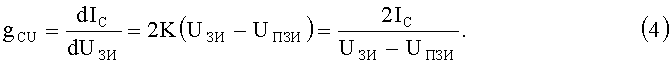

В качестве усилителя сигнала чтения «UP:i» следует использовать компаратор напряжения, который обеспечивает выработку сигнала «DЧ:i» с уровнем логической «1» или «0», если соответственно «UP:i»>UЭ или «UP:i»<UЭ. В качестве основного элемента при построении компараторов напряжения применяют инвертор КМОП, схема и передаточная характеристика которого приведена на Фиг.35.

Инвертор КМОП, работающий в области переключения, т.е. при UВХ от UC-ΔU до UC+ΔU (UC - напряжение порога переключения "1"→"0") имеет высокий коэффициент усиления. Каждый полевой транзистор можно рассматривать как нагрузку другого. Для полевых транзисторов IC=K(UЗИ-UПЗИ)2, где K (некоторая константа крутизны) и UПЗИ зависят от свойств p-канального и n-канального транзистора МОП. Динамическая передаточная проводимость

Активной нагрузкой каждого транзистора МОП является динамическое сопротивление канала «сток-исток»

При Кn=-Кp, UПЗИn=-UПЗИp и UAn=-UAp коэффициент усиления инвертора КМОП по напряжению равен:

При

Например, при Un=3 B, UПЗИ=1 В и UA=60 В коэффициент усиления Кн=240 на линейном участке передаточной характеристики.

На Фиг.36 приведена принципиальная электрическая схема компаратора напряжения (а) и аналогового ключа (б). В компараторе напряжения использованы два инвертора КМОП «HE-1», «HE-2», три двунаправленных аналоговых ключа «АК1», «АК2», «АК3» и разделительный конденсатор «С1». В исходном состоянии при низком уровне («0») сигналов «ЧТ1», «ЧТ2» и соответственно высоком уровне («1») сигналов «

Сигналы «ЧТ1» и «

Сигналы «ЧТ2» и «

где КН - коэффициент усиления инвертора «НЕ-1» по напряжению на линейном участке передаточной характеристики. Следует отметить, что компаратор не реагирует на синфазный сигнал за счет использования конденсатора C1, а его усиление на линейном участке равно

Идея построения описанного компаратора приведена в /9/, а работа двунаправленного аналогового ключа рассмотрена в /11/.

При этом по переднему фронту "1"→"0" сигнала разрешения записи первого цикла «

Наряду с возможностью интегрирования матрицы памяти «STT-MRAM» в технологию КМОП/КНД, другими аспектами, варианты осуществления изобретения имеют преимущество в энергосбережении, статической памяти и электрических признаков чтения/записи, рассмотренной выше технологии «STT-MRAM». Варианты реализации изобретения дают возможность рассмотреть много признаков, в том числе:

расширяемые аппаратные средства, масштабируемость посредством формирования процесса, реконфигурируемость, отсутствие инициализации, малую утечку в состоянии ожидания и сохранение записанной информации, маленькие размеры и высокую скорость записи/считывания.

ПРИЛОЖЕНИЕ «А»: Структура запоминающей ячейки MRAM

Конструкция запоминающей ячейки («ЗЯ») памяти «MTJ» показана на Фиг.6. В этой конструкции запоминающей ячейки («ЗЯ») имеются два магнитных слоя из материалов с различными свойствами, подобранными таким образом, что один слой переключается при меньшей напряженности поля, а другой - при большей. При использовании одного и того же материала, требуется изготовить слои различной толщины. В этом случае более тонкая пленка переключится при меньшей напряженности поля («мягкий» слой), более толстая - при большей напряженности («жесткий» слой). «Мягкий» слой используют для считывания информации, «жесткий» - для ее записи и хранения. «Мягкий» слой может быть многократно перемагничен без изменения состояния «жесткого» слоя.

Запись информации производится пропусканием тока одновременно по двум линиям: считывающей («Sense line»), или шины разрядов (ШР), и записывающей («Word line»), или шина записи слова «ШЗС»), на пересечении которых и находится данная ячейка. Для запоминания используется нижний ферромагнитный слой с большим значением коэрцитивного магнитного поля. Значению логического «О» («I») соответствует направление намагниченности слоя по (против) оси х.

В процессе считывания ток переменной полярности пропускается по записывающей линии «ШЗС». Создаваемое им магнитное поле недостаточно сильно для того, чтобы перемагнитить нижний слой, однако достаточно для перемагничивания верхнего ферромагнитного слоя. Поэтому при пропускании тока параллельная ориентация намагниченностей сменяется антипараллельной и т.д. Если пропускать по считывающей линии постоянный ток, то вследствие модуляции сопротивления элемента «MTJ», находящегося на пересечении двух линий (Фиг.5), напряжение считывающей линии также будет промодулировано, но с меньшей глубиной, так как изменяется сопротивление только одного элемента в линии. Состояние именно этого элемента и определяется в процессе считывания. Поскольку напряжение на всех считывающих линиях можно измерять одновременно, то происходит одновременно считывание со всех элементов, расположенных вдоль записывающей линии. На Фиг.7 в едином масштабе времени изображены зависимости тока «ШЗС», сопротивления элемента «MTJ», напряжения «ШР» и его производной для случаев, когда в ячейке записан «0» (а) и «1» (б).

Для считывания достаточно прохождения нескольких импульсов, его характерное время составляет величину порядка 50 нс. Время записи - порядка 100 нс. Ток записи (переключение «жесткого» слоя) тем больше, чем выше степень интеграции схемы. При формировании ячейки «MTJ» используется 2-D организация памяти (Фиг.5).

В ячейках «SDT» (Spin Dependent Tunneling) (Фиг.8) магнитные слои разделены диэлектриком (в «PSV» структурах промежуточный слой - медный). Для электронов проводимости ферромагнитных слоев этот слой является потенциальным барьером. Если его толщина составляет десяток ангстрем, то существует заметная вероятность туннелирования электронов из одного ферромагнитного слоя в другой. Именно этими процессами обусловлено наличие тока в направлении, перпендикулярном слоям. Оказалось, что туннельный ток больше, а сопротивление слоев меньше, когда намагниченности ферромагнитных слоев параллельны. При этом в результате туннелирования электрон большинства (меньшинства) остается таковым и после туннелирования. Поэтому при антипараллельной ориентации намагниченностей ферромагнитных слоев сопротивление в направлении, перпендикулярном слоям, больше, чем при параллельной ориентации намагниченностей, теоретически на 45%. Взаимодействие ферромагнитных слоев через диэлектрическую прослойку намного слабее, чем через проводящую. Оно обусловлено только электронами, туннелирующими через диэлектрический барьер. Если это взаимодействие приводит к антиферромагнитному упорядочению намагниченностей, то, прикладывая к системе магнитное поле, можно изменить ориентацию намагниченностей с антипараллельной на параллельную. Такая переориентация сопровождается падением сопротивления. Это явление носит название «туннельного магнитосопротивления».

Ячейки памяти «MRAM» на эффекте «SDT» обеспечивают изменение магнетосопротивления до 40% по сравнению с 6…9% для структур «PSV». Однако сопротивление ячеек «SDT», в отличие от «PSV», составляет тысячи Ом, при этом напряжение пробоя диэлектрического слоя не превышает 1…2 В. Это накладывает ограничения на величину тока через прибор, на уровне не более 1 мА, что недостаточно для надежного переключения ячеек. Кроме того, необходимы дополнительные внешние контакты, что снижает плотность компоновки по сравнению с ячейками «PSV».

Элементы памяти на ячейках «SDT» строятся по архитектуре «DRAM», или как триггерные. Сигналы считывания по уровню (30…40 мВ) соизмеримы с используемыми в полупроводниковой памяти.

В первых вариантах ячеек «MRAM» магнитное поле, генерируемое проводником тока, вызывало поворот вектора магнитной индукции свободного слоя. Состояние бита («0» или «1») определяется направлением тока, генерирующего магнитное поле. Вследствие технологического разброса в массиве ячеек памяти существовали вариации в величине генерируемых магнитных полей. Структура ячейки представлена на Фиг.9. Поэтому для уверенного переключения всех ячеек приходилось подавать многократно больший ток, чем это было бы необходимо при оптимальных условиях. В то же время требовалось удерживать магнитные поля на «полувыбранных» элементах массива в состоянии, гарантирующем надежное сохранение битов в неизменном виде. («Выбранные» - это ячейки, находящиеся на пересечении линий строк и столбцов, а «полувыбранные» - ячейки, расположенные в магнитном поле, генерируемом только одним из проводников, при протекании тока только по одной из линий.)

Сопротивления «MTJ» для этих двух состояний отличались всего на 15-30%. С ростом объемов матрицы памяти и уменьшением физических размеров ячейки сокращаются интервалы между проводниками и усиливается влияние магнитного поля на состояние соседних ячеек. Понятно, что никакого эффективного экранирования внутри кристалла реализовать невозможно. Электромагнитные наводки приводили к сбоям в работе памяти. Требовалось обеспечить довольно узкое «рабочее окно», внутри которого разряды уверенно бы программировались в нужное состояние при записи и также надежно сохранялись бы в исходном состоянии при «полувыборке» при необходимости выполнить жесткие требования к качеству материалов, стабильности и повторяемости технологических процессов.

Для устранения вышеуказанных недостатков специалистами фирмы «Motorola» («Freescale») была предложена новая структура ЗЯ «MRAM».

В новой структуре ЗЯ нет «полувыбранных» битов. Благодаря применению новой структуры свободного слоя, иной ориентации бита и специальной последовательности токовых импульсов, состояние разряда в массиве памяти может быть запрограммировано в «переключательном» режиме, названном в честь его изобретателя «методом Савченко». Структурная схема такой ЗЯ приведена на Фиг.10.

Переключательным новый метод назван потому, что одна и та же токовая импульсная последовательность используется как для записи «0», так и для записи «1». И всякий раз состояние свободного магнитного слоя переключается в противоположное магнитное состояние. Этот тип переключения значительно отличается от «обычного», где магнитный момент свободного слоя просто следовал за состоянием прикладываемого поля.

Во время операции установки бита магнитный вектор свободного слоя принимает одно из двух возможных состояний. Направление вектора поля задается с помощью внутренних медных проводников, расположенных в перпендикулярных направлениях относительно друг друга на вершине и в основании структуры «MTJ». Импульсы тока, протекающего через перпендикулярно расположенные медные проводники, создают магнитное поле, которое изменяет намагниченность свободного слоя той битовой ячейки, которая находится в области перекрещивания проводников (Фиг.11).

Такая трехслойная структура повышает скорость и стабильность операций стирания/записи, однако требует более высокого тока для выполнения этих операций, чем ячейки традиционной памяти. На практике среднее потребление остается на том же уровне, так как при записи байта данных не все биты требуют изменения, если только не изменяют значение байта с «FF» на «00» и обратно. Кроме того, процесс стирания/записи занимает крайне малое время порядка 25 нс. В результате по показателю потребления микросхема памяти типа «MRAM» выигрывает по сравнению с другими типами постоянных запоминающих устройств (ПЗУ), которые к тому же, существенно работают гораздо медленнее.

«Режим переключения Савченко» основан на уникальном поведении составного антиферромагнитного свободного слоя («SAF»), который формируется из двух ферромагнитных слоев, разделенных тончайшей немагнитной прослойкой, связывающей их вместе. Общие принципы формирования «MTJ» и структура этого «слоеного пирога», образующего вместе со стабильным слоем, имеющим неизменный магнитный момент, «MTJ», приведены на Фиг.12.

Моментно-сбалансированный составной слой «SAF» откликается на прикладываемое магнитное поле иначе, чем единственный магнитный слой «обычной» ячейки. Под действием поля, генерируемого токовыми линиями, два его антипараллельных магнитных момента будут вращаться примерно перпендикулярно прикладываемому магнитному полю. Импульсная токовая последовательность будет передвигать магнитные моменты слоев, поворачивая их в противоположном направлении по отношению к исходному положению. Она состоит из четырех фаз, в соответствии с которыми вращаются моменты свободного слоя (Фиг.13).

Очевидно, что каков бы ни был уровень тока, как бы близко ни располагались ячейки в матрице памяти, одиночная линия выборки не сможет переключить магнитный момент свободного слоя в противоположное состояние. Просто потому, что необходимой импульсной последовательности в полувыбранных разрядах не бывает. Она имеет место только на адресуемой ячейке, то есть на пересечении линий строк и столбцов, где есть магнитное поле от двух токовых линий. По этой причине существенно возрастает надежность работы ИС, удается полностью избежать нарушений, присущих «старой» структурной ячейке /1/.

Благодаря свойственной ячейке симметрии токовая последовательность обязательно переключает бит, и, следовательно, для выяснения необходимости перепрограммирования (перезаписи) разряда необходимо произвести предварительное чтение. Потребность в таком чтении, однако, практически не сказывается на скорости выполнения операции записи. Оно производится встроенными схемами и абсолютно незаметно для пользователя. В результате, в серийных ИМС памяти MR2A16A объемом 4 Мбит, выпускаемых компанией «Freescale», время цикла для операций записи и чтения равно 35 нс, что при параллельной загрузке данных (16 разрядов) позволяет достичь темпа накопления данных около 450 Мбит/с. Это очень хороший показатель, превзойти который в сегнетоэлектрической памяти пока не удалось. В ИМС «FRAM» фирмы «Ramtron» также выполняется лишний цикл при любом обращении к ячейке памяти (цикл восстановления данных), но в отличие от «MRAM» это чтение заметно влияет на длительность операций.

На Фиг.13 схематически представлена эволюция электродов элемента памяти. Первые структуры изготавливались с электродами из простых магнитных материалов. Для использования эффекта магнетосопротивления в элементах электроники было удобно зафиксировать намагниченность одного из электродов и управлять намагниченностью только второго (свободного) слоя.

Наибольшее распространение получил способ фиксации или «пиннинга» намагниченности на подслое антиферромагнетика с помощью обменных полей. Это позволяет увеличить коэрцитивное магнитное поле до нескольких тысяч эрстед. Из Фиг.13 следует, что верхний электрод всегда находился в магнитных полях, индуцированных нижним слоем. Это магнитостатическое взаимодействие слоев накладывает ограничения на управление верхним свободным слоем. Для уменьшения магнитостатического взаимодействия намагниченность нижнего слоя стали пиннинговать на так называемом искусственном антиферромагнетике - нижний электрод стал состоять из двух одинаковых магнитных слоев, связанных обменным образом (через прослойку Ru), а нижний слой этого многослойного электрода по-прежнему пининговался на антиферромагнетике. Таким образом, магнитостатическое взаимодействие между верхним и нижним электродами было существенно уменьшено. В дальнейшем и верхний электрод формируют с использованием искусственного антиферромагнетика, что позволяет, возможно, уменьшить магнитные поля рассеяния магниторезистивного элемента на соседние ячейки, что важно при конструировании чипов со сверхплотной записью информации.

При проектировании памяти «MRAM», пригодной для серийного производства, главной проблемой является высокая чувствительность к случайному перемагничиванию. При изменении определенного бита памяти высока вероятность того, что свободный магнитный слой соседних битов может быть также непреднамеренно изменен. Для повышения стабильности процесса установки бита и устранения эффекта непреднамеренного перемагничивания медные проводники с трех сторон экранируют специальным экраном, предотвращающим паразитные наводки на соседние битовые ячейки. Кроме этого, изолирующий экран направляет и фокусирует магнитное поле только на целевую битовую ячейку, что позволяет существенно снизить ток программирования.

Следует отметить основные недостатки технологии «MRAM»:

- большой ток записи;

- нестабильность магнитных параметров «ЗЯ»;

- температурная нестабильность ячеек памяти;

- технологические проблемы.

Теоретически «MRAM» могут работать при токах записи в несколько мА при размерах проводников 0,2…0,3 мкм. Однако на практике его величина достигает 120 мА и более. Существуют несколько способов снижения тока записи. Ток записи можно уменьшить, нанося на шину записи покрытие (сверху или с трех сторон). При этом происходит концентрация магнитного потока, снижается поток рассеивания, создается поле большей напряженности при меньших токах. Таким способом можно снизить ток записи примерно в 3 раза.

Другой подход - использование гиромагнитного эффекта при перемагничивании, для чего следует увеличить время нарастания (удлинить фронт) импульсов. При этом ток записи можно уменьшить еще в два раза. Кроме того, ток записи может быть уменьшен за счет снижения размеров ячеек, но до определенного предела.

В 80-х годах полагали, что если размеры ячеек сократить до ширины доменов, то проблемы намагничивания доменов в ячейках исчезнут, поскольку перемагничиваться будут спины только с одной степенью свободы. Эксперименты опровергли эту теорию. В ячейках существуют аномалии («vortices»), которые не позволяют сократить их размеры менее чем до нескольких десятых мкм в диаметре. Проблема решается путем использования круглых ячеек «MRAM», для которых аномалии несущественны.

Существуют определенные ограничения по ширине шин записи, которые не могут быть сделаны уже 1 мкм, поскольку при меньших размерах ячейки перестают надежно работать вследствие искажения магнитного поля на краях проводника при соизмеримых размерах его толщины и ширины.

Стабильность ячеек «MRAM» может быть рассмотрена с энергетической точки зрения. Запасенная магнитная энергия равна MHcV, где М - намагниченность, Нс - напряженность коэрцитивного поля, V - объем магнитного материала в ячейке. Для характерных размеров ячейки отношение магнитной энергии к kT (k - постоянная Больцмана, Т - температура) составляет около 20, при этом ошибка памяти становится несущественной. При уменьшении объема ячейки вероятность ошибки растет. При существующих режимах работы нижний предел для размера ячейки составляет около 0,1 мкм на сторону. Увеличение Не нежелательно, поскольку ведет к росту тока записи и перегреву ячеек.

Базовая конструкция ячейки «MRAM» была разработана в середине 80-х годов компанией «Honeywell». В ее основу были положены три основных принципа:

- для записи и хранения информации использовалось явление гистерезиса;

- считывание информации производилось на основе магнеторезистивного эффекта в той же структуре, в которой хранилась информация;

- ячейки памяти были интегрированы непосредственно в кремниевый кристалл.

В 1997 году фирма «Honeywell» разработала «MRAM» емкостью 256 кбайт на основе ячейки из двух сверхтонких ферромагнитных пленок, разделенных слоем материала с низкой проводимостью (TaN), а также пленок сложного состава, вытравленных в виде плоских проводников (полосок, шин). Однако первым серийным производителем «MRAM» стала корпорация «Freescale». На Фиг.14 представлена одна из реализации элемента памяти, используемая компанией «Freescale Semiconductor, Inc.» Перемагничивание свободного слоя происходит с помощью магнитного поля, созданным электрическим полем, протекающим по двум скрещенным шинам (проводам). В этом случае в элементе, находящемся в месте пересечения шин, создается максимальное магнитное поле, направленное под углом 45 градусов к оси анизотропии частицы. Как показывают расчеты, величина магнитного поля, необходимая для перемагничивания частицы, минимальна, если оно приложено под углом 45 к оси анизотропии частицы. Таким образом, решается сразу две проблемы - перемагничивание определенной ячейки и отсутствие паразитных переключений в соседних ячейках. Магнитное поле, создаваемое по отдельности каждой из шин на других элементах памяти, недостаточно для переключения элемента «MTJ» как по амплитуде, так и вследствие приложения не под оптимальным углом. Считывание информации с элемента производится малым током, при этом выбор элемента, с которого необходимо считать информацию, управляется транзистором, включенным последовательно в цепь с туннельным магнитным контактом.

На основе представленной архитектуры была разработана микросхема MR2A16A. Модуль памяти MR2A16A изготовлен по технологии с проектными нормами 0,18 мкм и является уже вторым поколением устройств на базе данной технологии. Емкость микросхемы составляет 4 Мбит с организацией 256К×16 бит. Управление осуществляется по стандартным входам: «chip enable», «write enable», «output enable» и «upper/lower byte select», обеспечивающим гибкость системы и предотвращающим конфликтные ситуации при обращении к шине (см. табл.ПА.1). В зависимости от состояния управляющих входов данные могут быть записаны/считаны как в 8-битном, так и в 16-битном формате. Устройство также поддерживает полностью статические операции.

Времена циклов чтения/записи/стирания малы, симметричны по длительности и составляют 35 нс. Диапазон рабочих напряжений микросхемы - 3…3,6 В, встроенная схема мониторинга питания предотвращает запись ячеек памяти при снижении уровня

питающего напряжения более чем на 0,5 В относительно рабочего. Рабочий температурный диапазон микросхем «MRAM» составляет - 40…+105°С.

Микросхемы MR2A16A выпускаются в корпусе 44-TSOP (type-II) в соответствии с техническими условиями «RoHS». В корпус микросхемы встроено защитное экранирование от внешних электромагнитных помех. Конфигурация выводов MR2A16A полностью соответствует микросхемам памяти типа SRAM, по принципу работы с памятью MRAM также схожа с SRAM. Поэтому чипы памяти MR2A16A могут применяться в существующих устройствах и системах, использующих память SRAM, без каких-либо изменений в схеме.

Эксперименты показали, что ячейки памяти MR2A16A выдерживают более 58 триллионов циклов записи и стирания, работая в наихудших эксплуатационных условиях. До настоящего времени не было зарегистрировано ни одного сбоя в работе ячеек памяти, и эксперимент по тестированию количества циклов записи/стирания ячеек памяти «MRAM» продолжается. В ходе испытаний микросхемы MR2A16A работали на частоте 4 МГц при температуре окружающей среды 90°С и на частоте 28,5 МГц при температуре окружающей среды 70°С.

Внутренняя структура микросхемы памяти представлена на Фиг.15. Фирмы «NEC» и «Toshiba» добились скорости считывания и записи 16 Мбит «MRAM» на уровне 100 Мбайт/с при напряжении питания 1,8 В. Площадь кристалла составляет 78,7 мм2, что на 30% меньше, чем у микросхем других типов аналогичной емкости. Элементы ИМС технологии КМОП изготовлены с проектными нормами 0,13 мкм, минимальные размеры элементов составляют 240 нм. Размер одной ячейки памяти 1,87 мкм2, время цикла записи/чтения - 34 нс.

«MRAM» обладает рядом преимуществ перед всеми остальными типами памяти, в том числе перед «FRAM», в первую очередь - это принципиальная неограниченность числа циклов перезаписи и высокое быстродействие. Преимущества технологии «MRAM» отражены в табл.1.2.

ПРИЛОЖЕНИЕ «Б»: Задержки распространения сигналов в блоках матрицы памяти «MRAM»

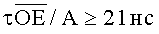

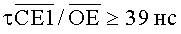

За единицу измерения времени принималось время переключения транзистора МОП из состояния "открыт" в состояние "закрыт" и наоборот, при этом считалось, что номинальное время переключения τп одинаково у p и n-канальных транзисторов, а технологическое отклонение его величины не превышает ±10%. В табл.ПБ-1 приведены расчетные значения задержки распространения сигналов в блоках матрицы памяти «MRAM».

Определим задержки и длительности сигналов, поступающих на входы микросхемы памяти, при величине τп=10 нс:

-

-

-

-

- t1≥218 нс;

-

- tA≥2143 нс.

На Фиг.19 приведены временные диаграммы сигналов, поступающих на микросхему памяти «MRAM» в режиме чтения, и выходные сигналы DIO:0-15, а также внутренние сигналы микросхемы:

- МОП ЗЯ - состояние МОП-транзисторов запоминающих ячеек слова i МЗЯ;

- iч:i, э - токи чтения на выходах ФТЗЧ;

- iч:i-A - токи чтения на выходах блока БК ШР;

- DЧ:i - сигналы чтения на выходах блока БУЧ при условии, приведенном в 2.12.3.8.

На временных диаграммах сигналы DIO:i, МОП ЗЯ, iч:i, э, iч:i-А, D4:i показаны при минимальной номинальной и максимальной величине их задержек.

На диаграмме сигналов D4:i обозначены временные интервалы:

- Δtл - интервал, в котором компаратор за счет замыкания ключа АК3 выведен на линейный участок характеристики, а через ключ АК1 производится заряд конденсатора С1;

- ΔtDЧ - интервал, в котором уровни сигналов DЧ:i соответствуют считанной из слова i МЗЯ информации.

На диаграмме сигналов «DIO:I» обозначен интервал «tDIO», в котором уровни сигналов «DIO:I» соответствуют считанной из слова «I» «МЗЯ» информации.

На заштрихованных участках диаграммы сигналы могут иметь любой уровень.

Литература

1. Патент US 5959465.

2. Патент US 6876228.

3. Соклоф С. Аналоговые интегральные схемы. Пер. с англ. А.Б. Перевезенцева, под ред. к. т.н. В.Д.Вернера. М.: Мир, 1988.

4. Чуа-Уоан Л.Г., Новак М.М., Канг С.Х. Программно-управляемая логическая схема, использующая магнеторезистивные устройства с передачей спинового вращения. Патент RU 2420865 С1 с приорит. от 31.03.2008, опубл. 10.06.2011 Бюл. №16.

5. Hosomi М.М., et al., A Novel Nonvolatile Memory with Spin Transfer Torque Magnetoresistive Magnetization Switching: Spin-RAM / Proceedings of IEDM conference (2005).

6. Jian-Gang Zhu, Proceedings of IEEE, V.96, N.11, p.1786, 2008.

7. Hirota E., Sakakima Н., Inomata K., Giant Magneto-Resistance Devices, Springer Series in surface science 40, 2001.

8. Gupta Arunava, Joshi Rajiv V. Non-Voltaite Magnetic Memory Cell and Devices / Pat. US 6034887, Mar.7, 2007.

9. Соклоф С. Аналоговые интегральные схемы. Пер. с англ. А.Б. Перевезенцева, под ред. к.т.н. В.Д.Вернера. М.: «Мир», 1988.

10. Шурыгина В. Энергонезависимая память / Электроника: наука технология бизнес, 2008. - №6.

11. Мальцев П.П., Долидзе Н.С., Критенко М.И., Пономарев С.Н., Портянко В.В., Посысаева Т.Т., Михалева Л.З. Цифровые интегральные микросхемы / Справочник. М.:«Радио и Связь», 1994.

Изобретение относится к схемам матриц ячеек памяти MRAM (Magnetic Random Access Memory) с передачей спинового значения. Технический результат заключается в увеличении плотности размещения отдельных транзисторных структур технологии МОП и запоминающих ячеек матрицы, а также повышении стойкости к нестационарным переходным процессам от воздействия ионизирующих излучений. Устройство матричного типа содержит множество устройств на магнитных туннельных переходах («MTJ») с передачей спинового вращения, организованных в матрицу запоминающих ячеек; устройство организации записи/чтения информации для конкретного устройства «MTJ», соединенное с соответствующими устройствами «MTJ» для изменения полярности намагниченности свободного слоя каждого устройства «MTJ», блок усилителя чтения данных на выходе матрицы запоминающих ячеек, выполненный с возможностью обнаруживать уровень сигнала и формировать двоичный выходной сигнал на основе сравнения уровня сигнала в разряде матрицы запоминающих ячеек в компараторе. При формировании топологии устройство «MTJ» выполнено в виде эллипса с осью легкого намагничивания, направленной по его большой оси. 11 з.п. ф-лы, 37 ил., 11 табл.

1. Интегрированная в СБИС технологии КМОП/КНИ с n+- и p+-поликремниевыми затворами матрица памяти «MRAM» с магниторезистивными устройствами с передачей спинового вращения (матрица памяти «STT-MRAM»), представляющая собой устройство матричного типа, управляемое внешними сигналами записи/чтения информации и ввода/вывода данных, содержащее:

множество устройств на магнитных туннельных переходах («MTJ») с передачей спинового вращения, организованных в матрицу запоминающих ячеек;

устройство организации записи/чтения информации для конкретного устройства «MTJ», включающее:

блок ввода/вывода данных,

блок дешифратора адресного кода,

блок управления ключами шин записи слова,

блок ключей шин записи слова,

блок управления ключами разрядных шин,

блок ключей разрядных шин,

блок управления записью/чтением данных,

блок формирователя тока записи/чтения,

источники тока записи слова, тока записи разряда, тока чтения в составе блока формирователя тока записи/чтения,

шины разрядные, шины записи слова, шины чтения слова, двунаправленную шину ввода/вывода данных,

соединенные с соответствующими устройствами «MTJ» для изменения полярности намагниченности свободного слоя каждого устройства «MTJ», причем блоки устройства организации записи/чтения информации объединены соответствующими шинами для формирования логического состояния на основе относительных полярностей свободного слоя и фиксированного слоя каждого устройства «MTJ»,

блок усилителя чтения данных на выходе матрицы запоминающих ячеек, соединенный с двунаправленной шиной ввода/вывода данных по цепям «UP:0-15,Э» и «DЧ:0-15», выполненный с возможностью обнаруживать уровень сигнала на конце «А» в шине разрядной и формировать двоичный выходной сигнал «DЧ:0-15» на основе сравнения уровня сигнала в разряде матрицы запоминающих ячеек в компараторе, включенным в состав блока усилителя чтения данных, с эталонным пороговым уровнем сигнала («UЭ»), отличающаяся тем,

что для придания исходной анизотропии намагниченности свободного и фиксированного ферромагнитного слоев каждой запоминающей ячейки матрицы памяти «STT-MRAM» при формировании топологии устройства «MTJ» оно выполнено в виде эллипса с осью легкого намагничивания, направленной по его большой оси, а для изменения полярности намагниченности верхнего свободного слоя устройства «MTJ» внешнее управляющее матрицей памяти «STT-MRAM» устройство соединено по цепям сигнала разрешения записи информации («

2. Матрица памяти «STT-MRAM» по п.1, отличающаяся тем, что для исключения статистического разброса величины магнитного момента нижнего закрепленного ферромагнитного слоя в каждом устройстве «MTJ», концы «А» разрядной шины «ШР-А:0-15, Э» этого устройства в режиме чтения данных соединены с одним из входов компаратора, а второй вход компаратора соединен с шиной записи/чтения, в которой генерируется выходной сигнал «UЭ» эталонного устройства «MTJ», расположенного в центре каждого слова матрицы запоминающих ячеек.

3. Матрица памяти «STT-MRAM» по п.1, отличающаяся тем, что для организации постоянного запоминающего устройства емкостью 64 кбит с 16-разрядной двунаправленной шиной ввода/вывода данных «DIO:0-15», она содержит множество запоминающих ячеек на основе устройств «MTJ», которые могут быть электрически приведены в состояние высокого сопротивления «RB» или низкого сопротивления «RH».

4. Матрица памяти «STT-MRAM» по п.1 или п.3, отличающаяся тем, что для обеспечения обращения к выбранному слову матрицы запоминающих ячеек выходы «C:i» блока дешифратора адреса, где i=0…4095 равно численному значению кода адреса, соединены с входом блока управления ключами шины записи слова и одновременно через блок ключей шины записи слова с шиной записи слова («ШЗС:i») матрицы запоминающих ячеек, где i=0…4095 равно численному значению кода адреса устройства «MTJ», с возможностью выработки на одном из выходов «C:i» сигнала с уровнем логической «1» при поступлении на вход дешифратора адреса по шине «А:0-11» от внешнего устройства параллельного адресного кода.

5. Матрица памяти «STT-MRAM» по п.1 или п.3, отличающаяся тем, что для обеспечения формирования сигналов 1-го и 2-го цикла записи («

6. Матрица памяти «STT-MRAM» по п.4, отличающаяся тем, что для генерации сигналов управления ключами блока управления ключами шины записи слова в зависимости от состояния входных сигналов «C:i», где i=0…4095, «

7. Матрица памяти «STT-MRAM» по п.5, отличающаяся тем, что для управления блоком ключей шины разряда выходы «б:0-15, Э» блока управления ключами шины разряда присоединены с одной стороны к блоку ключей шины разряда с логическим состоянием, определяемым состоянием входных сигналов внешнего устройства «