Изобретение относится к цифровым системам управления (ЦСУ) преобразователями на базе микропроцессора и предназначено для обеспечения работы ЦСУ в режимах исчезновения и восстановления питающего напряжения, а также в режимах ненормированного отклонения питающего напряжения, где требуется обеспечить работу преобразователя (при подаче питающего напряжения) с теми же начальными условиями, которые имели место до исчезновения питающего напряжения. Областью применения преобразователей с таким устройством являются системы гарантированного питания или электрические сети, где в качестве резервных источников применяются дизельгенераторы или другие альтернативные источники питания с широким диапазоном изменения выходного напряжения.

В системах гарантированного питания возможны ситуации, когда после отключения основного питающего напряжения осуществляется переход на альтернативные резервные источники питания, например дизель-генератор [1]. Питающее напряжение при этом может колебаться в значительных пределах, что может привести к неустойчивой работе микропроцессорной системы управления (МСУ) преобразователем. В основном это связано со снижением напряжения питания микросхем. В основном это связано со снижением напряжения питания микросхем до уровня минимальных паспортных значений. Как правило, напряжение питания микросхем формируется блоком питания из входного напряжения преобразователя, содержащего мощные С-фильтры, которые обеспечивают медленный спад напряжения питания микросхем при отключении системы управления или медленный рост при ее включении, при этом неустойчивая работа микросхем возникает на уровне минимального напряжения питания микросхем и как следствие возможна неточная передача информации между внешним устройствами МСУ (особенно с внешними запоминающими устройствами), что делает невозможным повторные запуски преобразователя при достижении достаточного уровня питающего напряжения. Поэтому стоит задача сохранения полезной информации и обеспечения устойчивой работы МСУ при значительных ненормируемых отклонениях напряжения питающей (или резервной) сети, включении или отключении питающего напряжения.

Известны схемы начальной установки микропроцессорной системы управления [2,3] , где сигнал начальной установки микропроцессора и внешних устройств RESET обеспечивает начальный запуск системы управления только при включении МСУ. В основе этих схем лежит RC-цепочка, конденсатор которой и формирует сигнал RESET в момент включения МСУ.

Схема [4] , принимаемая за прототип, представляет собой типичную конфигурацию МСУ, где микропроцессор устанавливается в начальное состояние сигналом RESET (по вариантам [2,3], а управление внешними устройствами (включая элементы внешней памяти) осуществляется с помощью микропроцессорных сигналов управления внешними устройствами, шинами данных (ШД) и адреса (ША). Схема не содержит элементов, позволяющих обеспечить сохранность информации и устойчивую работу МСУ при снижении напряжения питания преобразователя.

Цель изобретения - повышение надежности цифровой системы управления преобразователем на базе микропроцессора в режимах исчезновения и восстановления питающего напряжения.

Это достигается введением компаратора, на вход которого подается разность напряжений уставки и часть нестабилизированного напряжения питания микросхем. Напряжение уставки формируется первым делителем напряжения, состоящим из резистора и стабилитрона. Часть нестабилизированного напряжения, пропорциональная входному напряжению питания преобразователя, формируется вторым делителем напряжения, состоящим из резисторов. Выход компаратора управляет ключом, который подключен параллельно конденсатору, образующему с резистором последовательную цепочку между общим проводом и плюсом стабилизированного питания микросхем. Сигнал начальной установки микропроцессора RESET (сигнал высокого уровня) формируется первым элементом И-НЕ, на вход которого подается напряжение с конденсатора, а сигнал  (сигнал низкого уровня) вторым элементом И-НЕ, на вход которого подается сигнал с первого элемента И-НЕ. Добавляются элементы И-НЕ на каждый из соответствующих выходов селектора внешних устройств по числу внешних устройств, на каждый из соответствующих выходов микропроцессорных сигналов управления внешними устройствами. Сигнал

(сигнал низкого уровня) вторым элементом И-НЕ, на вход которого подается сигнал с первого элемента И-НЕ. Добавляются элементы И-НЕ на каждый из соответствующих выходов селектора внешних устройств по числу внешних устройств, на каждый из соответствующих выходов микропроцессорных сигналов управления внешними устройствами. Сигнал  и один из соответствующих сигналов с элемента И-НЕ на выходе селектора внешних устройств подаются на первый элемент 2И-НЕ, сигнал

и один из соответствующих сигналов с элемента И-НЕ на выходе селектора внешних устройств подаются на первый элемент 2И-НЕ, сигнал  и один из соответствующих сигналов с элемента И-НЕ на выходе микропроцессорных сигналов управления внешними устройствами подаются на второй элемент 2И-НЕ, другие необходимые микропроцессорные сигналы управления внешними устройствами подаются на соответствующие последующие элементов 2И-НЕ. Полученные сигналы с элементов 2И-НЕ подаются на соответствующие микросхемы внешних устройств.

и один из соответствующих сигналов с элемента И-НЕ на выходе микропроцессорных сигналов управления внешними устройствами подаются на второй элемент 2И-НЕ, другие необходимые микропроцессорные сигналы управления внешними устройствами подаются на соответствующие последующие элементов 2И-НЕ. Полученные сигналы с элементов 2И-НЕ подаются на соответствующие микросхемы внешних устройств.

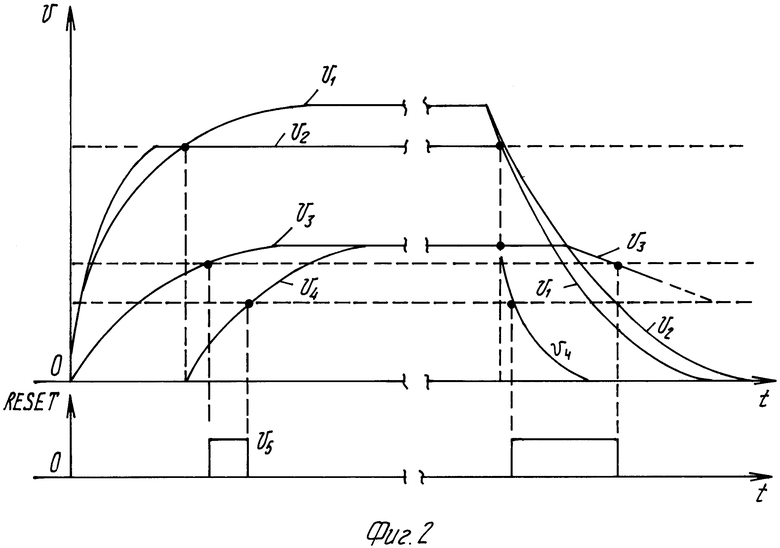

На фиг. 1 представлена схема предлагаемого устройства, где введены следующие обозначения:

Uпит. нестаб -нестабилизированное питание микросхем, пропорциональное входному напряжению питания преобразователя;

Uпит.стаб - стабилизированное питание микросхем;

Uпит.аб - питание от аккумуляторной батареи;

ША - шина адреса;

АБ - аккумуляторная батарея;

RESET,  - сигнал (высокого и низкого уровня) сброса процессора и внешних устройств в исходное состояние;

- сигнал (высокого и низкого уровня) сброса процессора и внешних устройств в исходное состояние; - сигнал записи (низкого уровня);

- сигнал записи (низкого уровня); - сигнал чтения (высокий уровень) и записи (низкого уровня) на входе ОЗУ;

- сигнал чтения (высокий уровень) и записи (низкого уровня) на входе ОЗУ; - сигнал выбора микросхемы (низкий уровень).

- сигнал выбора микросхемы (низкий уровень).

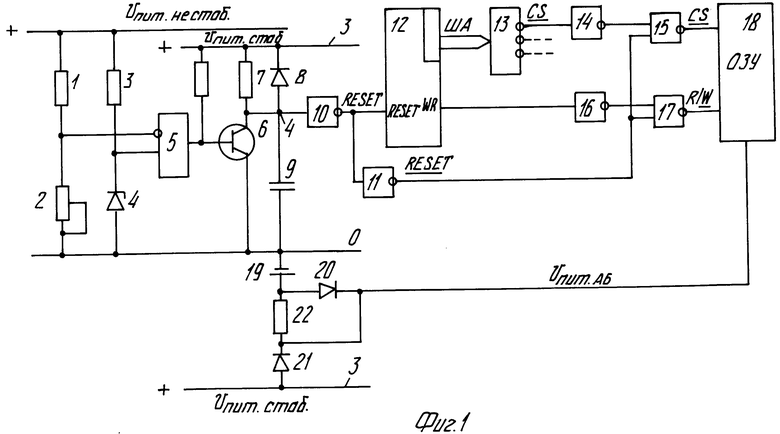

На фиг. 2 представлены временные диаграммы напряжений в контрольных точках схемы по фиг. 1 и формирования сигнала начальной установки RESET МСУ.

Схема предлагаемого устройства (фиг. 1) содержит первый делитель напряжения из последовательно соединенных резисторов 1 и подстрочного резистора 2, подключенного к источнику нестабилизированного питания (Uпит. нестаб) и второй делитель напряжения, состоящий из последовательно соединенного резистора 3 и стабилитрона 4. Средняя точка первого делителя напряжения соединена с инверсным входом компаратора 5, средняя точка второго делителя соединена с первым входом компаратора 5. Выход компаратора 5 поступает на базу транзисторного ключа 6. Коллектор транзисторного ключа 6 через резистор 7 присоединяется к источнику стабилизированного питания (Uпит.стаб), эмиттер соединен с общим проводом (О). Между источником стабилизированного питания и общим проводом находится последовательная цепочка из диода 8 и конденсатора 9, причем катод диода соединен с плюсом стабилизированного источника питания (Uпит.стаб.), а общая точка диода 8 и конденсатора 9 соединен с коллектором транзисторного ключа 6 и входом элемента И-НЕ 10. Выход элемента И-НЕ 10 подается на вход элемента И-НЕ 11 и вход RESET микропроцессора 12. Микропроцессор 12 соединяется с помощью ША с селектором адреса внешних устройств 13, выход которого CS соединяется с элементом И-НЕ 14 (количество элементов И-НЕ зависит от числа внешних устройств). Выход элемента И-НЕ 14 соединяется с первым входом элемента 2И-НЕ 15, на второй вход элемента 2И-НЕ 15 подается сигнал  с выхода элемента И-НЕ 11. Сигнал записи

с выхода элемента И-НЕ 11. Сигнал записи  микропроцессора 12 (или сигнал чтения, в зависимости от конфигурации МСУ) подается на элемент И-НЕ 16, выход которого соединен с первым входом элемента 2И-НЕ 17, на второй вход которого подается сигнал

микропроцессора 12 (или сигнал чтения, в зависимости от конфигурации МСУ) подается на элемент И-НЕ 16, выход которого соединен с первым входом элемента 2И-НЕ 17, на второй вход которого подается сигнал  с выхода элемента И-НЕ 11. Выходы элементов 2И-НЕ 15 и 17 подаются соответственно на управляющие входы CS и R/W внешнего устройства 18. Питания (Uпит.аб) внешнего оперативного запоминающего устройства (ОЗУ) осуществляется от аккумуляторной батареи (АБ) 19 через диод 20. Заряд АБ 19 осуществляется через диод 21 и резистор 22 от источника стабилизированного питания.

с выхода элемента И-НЕ 11. Выходы элементов 2И-НЕ 15 и 17 подаются соответственно на управляющие входы CS и R/W внешнего устройства 18. Питания (Uпит.аб) внешнего оперативного запоминающего устройства (ОЗУ) осуществляется от аккумуляторной батареи (АБ) 19 через диод 20. Заряд АБ 19 осуществляется через диод 21 и резистор 22 от источника стабилизированного питания.

Принцип работы схемы рассмотрим для случая, когда в качестве внешнего устройства 18 (фиг. 1) применяется ОЗУ. На фиг. 2 показаны временные диаграммы напряжений в контрольных точках фиг. 1, обведенных кружками. На фиг. 2 дополнительно показаны:

Uвх.уст - напряжение уставки, пропорциональной минимальному входному напряжению питания преобразователя;

Uип.мин - максимальное напряжение стабилизированного питания микросхем, при котором микросхема выполняет свое функциональное назначения;

Uсраб - напряжение срабатывания микросхем по входу (при переходе из состояния высокого уровня в низкий и наоборот).

При подачи напряжения питания на МСУ напряжение в точке 1 (кривая 1 на фиг. 2) повторяет напряжение нестабилизированного питания в определенном масштабе (делитель напряжения на резисторах 1 и 2). В точке 2 (кривая 2 на фиг. 2) напряжение сначала повторяет напряжение источника нестабилизированного питания, затем стабилизируется стабилитроном 4 на уровне выбранной установки (Uвх.уст на фиг. 2). Стабилизированное питание (кривая 3 на фиг. 2) имеет запаздывание по времени относительно нестабилизированного питания за счет фильтрации нестабилизированного питания. В момент пересечения кривых 1 и 2 на выходе компаратора формируется сигнал низкого уровня, который позволяет закрыть транзисторный ключ 6, после чего производится заряд конденсатора 9 через резистор 7. Напряжение стабилизированного питания Uпит.стаб 3 пересекает пороговое напряжение Uип.мин раньше, чем напряжение на входе логического элемента 10 достигнет порога срабатывания Uсраб. На интервале между точкой пересечения кривой 3 с Uип.мин и точкой пересечения кривой 4 с Uсраб, на выходе элемента 10 вырабатывается сигнал высокого уровня RESET. При этом происходит сброс процессора в исходное состояние, а сигналом  (на выходе элемента 11) осуществляется запрет прохождения микропроцессорных управляющих сигналов

(на выходе элемента 11) осуществляется запрет прохождения микропроцессорных управляющих сигналов  и выбора микросхемы

и выбора микросхемы  от микропроцессора 12 к микросхеме 18.

от микропроцессора 12 к микросхеме 18.

При снижении напряжения питания преобразователя и, соответственно, МСУ напряжение в точке 1 (фиг. 1) достигает напряжения Uвх.уст, при этом напряжение на выходе компаратора 5 становится положительным и включается транзисторный ключ 6, который разряжает конденсатор 9. Напряжение в точке 4 (фиг. 1) снижается до уровня Uсраб, и на выходе элемента 10 появляется сигнал высокого уровня RESET, который сбрасывает микропроцессор 12 в исходное состояние, а сигналом  осуществляется запрет прохождения микропроцессорных сигналов управления R/W и сигнала выбора микросхемы

осуществляется запрет прохождения микропроцессорных сигналов управления R/W и сигнала выбора микросхемы  . В рассматриваемом случае на элемент 18 (ОЗУ) запрещается подача сигнала записи и выбора микросхемы как при подаче напряжения, так и при его исчезновении фиг. 2), что важно для сохранения промежуточной информации и недопущения записи ложных данных. Данные в ОЗУ (микросхема 18) сохраняются за счет использования АБ 19, которая автоматически включается при исчезновении напряжения питания.

. В рассматриваемом случае на элемент 18 (ОЗУ) запрещается подача сигнала записи и выбора микросхемы как при подаче напряжения, так и при его исчезновении фиг. 2), что важно для сохранения промежуточной информации и недопущения записи ложных данных. Данные в ОЗУ (микросхема 18) сохраняются за счет использования АБ 19, которая автоматически включается при исчезновении напряжения питания.

В случае использования других внешних устройств 18, организуется запрет на прохождение тех управляющих сигналов от микропроцессора 12, которые необходимо запретить для данного внешнего устройства с добавлением соответствующих элементов 2И-НЕ.

Источники информации.

1. Адамия Г.Г., Беркович Е.И., Картавых А.С. и др. Статические агрегаты бесперебойного питания. Под ред. Ф.И.Ковалева. - М.: Энергоатомиздат, 1992, 288 с.

2. Однокристальные микроЭВМ. -М.: МИКАП, 1994, 400 с. рис. 8-16, с.316.

3. Нерода В.Я., Торбинский В.Э. и Шлыков Е.Л. Однокристальные микроЭВМ МС -51. -М.: Диджитал Компонентс, 1995, 164 с. рис. 2.16.

4. Абрайтис В. В., Аверьянов Н.Н., Белоус А.И. и др. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник в 2-х т. Под ред. В.А.Шахнова. - М.: Радио и связь, 1988, Т.1, 368 с. рис. 3.84, с.170.

Использование: изобретение относится к цифровым системам управления преобразователями на базе микропроцессора и предназначено для применения в системах гарантированного питания или в электрических сетях, где в качестве резервных источников используются источники питания с широким диапазоном изменения выходного напряжения. Цель изобретения - повышение надежности цифровой системы управления преобразователем на базе микропроцессора в режимах исчезновения и восстановления питающего напряжения. Это достигается путем введения в типовую конфигурацию микропроцессорной системы управления, где микропроцессор устанавливается в первоначальное состояние сигналом RESET, а управление внешними устройствами осуществляется сигналами микропроцессора, передаваемыми с помощью шин данных и адреса, компаратора, двух делителей напряжения, управляемого ключа и логических элементов И - НЕ и 2И - НЕ. На вход компаратора подается разность напряжения уставки и части нестабилизированного напряжения питания. Выходной сигнал компаратора управляет ключом, подключенным параллельно конденсатору последовательной RC-цепочки, подключенной к стабилизированному источнику питания, с которого подается сигнал на вход логического элемента И - НЕ, формирующего сигнал высокого уровня RESET. Сигнал низкого уровня RESET формируется вторым элементом И - НЕ, на вход которого подается сигнал с выхода первого. Сигнал RESET и один из сигналов с элемента И - НЕ на выходе селектора внешних устройств подаются на первый элемент 2И - НЕ, сигнал RESET и один из сигналов с элемента И - НЕ на выходе микропроцессорных сигналов управления внешними устройствами подаются на второй элемент 2И - НЕ. Сигналы с элементов 2И- НЕ подаются на соответствующие микросхемы внешних устройств. 2 ил.

Устройство автоматического формирования сигнала начальной установки микропроцессорной системы управления преобразователем, содержащее RC-цепочку, связанную общей точкой с входом RESET микропроцессора и подключенную крайним выводом резистора к потенциальному выводу источника стабилизированного питания, а крайним выводом конденсатора к общему выводу, селектор адреса, входом соединенный с выходом микропроцессора при помощи шин адреса, а выходами связанный с соответствующими внешними устройствами, отличающееся тем, что введены компаратор, два делителя напряжения, управляемый ключ, n + 3 элемента И - НЕ и (n + 1) элементов 2И - НЕ, где n - число внешних устройств, причем делители напряжения подключены к выводам источника питания, пропорционального напряжению питания преобразователя, первый делитель напряжения выполнен на последовательно соединенных резисторах, второй делитель напряжения выполнен на последовательно соединенных стабилитроне и резисторе, на вход компаратора подается разность напряжения уставки, сформированного на втором делителе напряжения и части напряжения питания преобразователя, сформированной первым делителем напряжения, управляемый ключ подключен параллельно конденсатору RC-цепочки, а цепь его управления связана с выходом компаратора, общая точка RC-цепочки соединена с входом RESET микропроцессора через первый элемент И - НЕ, выход первого элемента И - НЕ соединен с входом второго элемента И - НЕ, выход чтения-записи микропроцессора подключен к входу третьего элемента И - НЕ, выход которого соединен с первым входом первого элемента 2И - НЕ, выходы селектора адреса связаны с входами соответственно четвертого и последующих элементов И - НЕ, выходы четвертого и последующих элементов И - НЕ связаны с первыми входами соответственно второго и последующих элеметов 2И - НЕ, а вторые входы элементов 2И - НЕ соединены с выходом второго элемента И - НЕ, выход первого элемента 2И - НЕ связан с входом чтения - записи внешних устройств, а выходы второго и каждого последующего элементов 2И - НЕ свяазаны с входом выбора микросхемы соответствующих внешних устройств.

| Нерода В.Я., Торбинский В.Э., Штыков Е.Л | |||

| Способ запрессовки не выдержавших гидравлической пробы отливок | 1923 |

|

SU51A1 |

| Диджитал Компонатс, 1995, рис | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Микропроцессоры и микропроцесорные комплекты интегральных микросхем | |||

| Справочник/ Под ред.В.А.Шахнова, М.: Радио и связь, 1988, т | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Аппарат для передачи фотографических изображений на расстояние | 1920 |

|

SU170A1 |

Авторы

Даты

1998-03-10—Публикация

1996-09-27—Подача