Изобретение относится к вычислительной технике и может использоваться в узлах коммутации сообщений (пакетов) сети передачи данных (сети ПД) автоматизированной системы управления (АСУ) при управлении передачей данных по широковещательному многоточечному радиоканалу, имеющему динамическую неполно связную структуру.

Известно устройство для управления передачей данных по радиоканалу (А.С. СССР N 1162016.16, МПК5 H 04 L 7/00, 1985г.), содержащее последовательно соединенные синхронизатор и первый элемент И, а также элемент задержки, элемент ИЛИ и последовательно соединенные счетчик и триггер цикла передачи, последовательно соединенные генератор случайных чисел, блок сравнения и триггер разрешения передачи, а также последовательно соединенные второй элемент И и формирователь импульсов, что позволяет увеличить степень использования пропускной способности канала. Однако, данное устройство обладает недостаточной скоростью передачи по радиоканалу, в устройстве отсутствуют средства предотвращения конфликтов при поступлении в канал разнородного потока данных.

Наиболее близким по технической сущности и выполняемым функциям к заявляемому является устройство для управления передачей данных но радиоканалу (А. С. СССР N 1319298, МПК5 H 04 L 7/00, опубликованное 23.06.87.), содержащее генератор случайных чисел и синхронизатор, первый, второй, третий и четвертый элементы И, счетчик, блок сравнения, триггер цикла передачи, триггер разрешения передачи, два формирователя импульсов, элемент ИЛИ, два элемента задержки, причем выход синхронизатора связан с первым входом первого элемента И и вторым входом второго элемента И, вход запроса передачи является третьим входом второго элемента И и связан с первым входом триггера разрешения передачи, выход которого связан со вторым входом элемента ИЛИ, входом элемента задержки и является выходом разрешения передачи, выход элемента задержки подключен к четвертому входу первою элемента И, третий вход которого связан с выходом триггера цикла передачи и первым входом второго элемента И, выход второго элемента И связан со входом формирователя импульсов и входом генератора случайных чисел, выход которою соединен с первым входом блока сравнения, второй вход которого подключен к первому выходу счетчика, выход формирователя импульсов связан с первым входом элемента ИЛИ, второй выход счетчика соединен со вторым входом триггера цикла передачи, а вход счетчика подключен к выходу первого элемента И, выход блока сравнения подключен к входу формирователя импульсов, выход которого соединен с дополнительным элементом задержки и третьим входом элемента ИЛИ, а выход элемента ИЛИ является выходом "Включение передатчика", выход дополнительного элемента задержки связан с первыми входами третьего и четвертого элементов И, второй вход третьего элемента И соединен с выходом четвертого элемента и является выходом сигнала "Столкновение", причем выход третьего элемента И связан со вторым входом триггера разрешения передачи, а второй вход четвертого элемента И подключен ко второму входу первого элемента И и первому входу триггера цикла передачи и является входом "Сигнал несущей". Устройство обеспечивает увеличение скорости передачи информации по радиоканалу.

Однако устройство-прототип имеет недостатки:

Устройство-прототип обладает недостаточной пропускной способностью при передаче разнородного потока данных, в силу того, что устройство не различает поток разнородных данных (файлы, навигационная информация).

Целью изобретения является разработка устройства передачи данных по радиоканалу, обеспечивающего повышение пропускной способности канала множественного доступа за счет предотвращения конфликтов путем адаптации к изменению параметров нагрузки.

Поставленная цель достигается тем, что в известное устройство управления передачей данных по радиоканалу, содержащее генератор случайных чисел, синхронизатор, счетчик, первый элемент И, первый вход которого является управляющим входом устройства, RS-триггер, второй элемент И, блок сравнения, причем выход синхронизатора соединен со входом счетчика и первым входом второго элемента И, групповой выход счетчика соединен со счетным входом блока сравнения, вход случайных чисел которого соединен с групповым выходом генератора случайных чисел, выход первого элемента И соединен со входом генератора случайных чисел, дополнительно введены третий элемент И, блок выделения признака навигационного пакета, генератор тактовых импульсов, блок выделения адреса, блок определения интервала поступления пакета и блок таймеров. Выход первого элемента И дополнительно соединен со входом сброса RS-триггера, вход установки которого соединен с выходом блока сравнения, и первым входом третьего элемента И. Выход второго элемента И соединен со вторым входом первого элемента И. Выход RS-тригтера соединен со вторым входом второго элемента И. Информационный вход блока выделения признака навигационного пакета подключен к информационному входу блока выделения адреса и является информационным входом устройства. Выход третьего элемента И является управляющим выходом устройства. Сигнальный выход блока выделения признака навигационного пакета соединен с первым сигнальным входом блока определения интервала поступления пакета и управляющим входом блока выделения адреса. Первый выход сигнала "Сброс" блока определения интервала поступления пакета соединен со входом сигнала "Сброс" блока выделения признака навигационного пакета. Выход блока выделения адреса соединен со вторым сигнальным входом блока определения интервала поступления пакета, второй выход сигнала "Сброс" которого соединен с входом сигнала "Сброс" блока выделения адреса. Выход генератора тактовых импульсов соединен с тактовыми входами блоков выделения признака навигационного пакета, блока выделения адреса, блока определения интервала поступления пакета и блока таймеров. Групповой выход блока определения интервала поступления пакета соединен со входом блока таймеров, выход которого соединен с инверсным входом третьего элемента И.

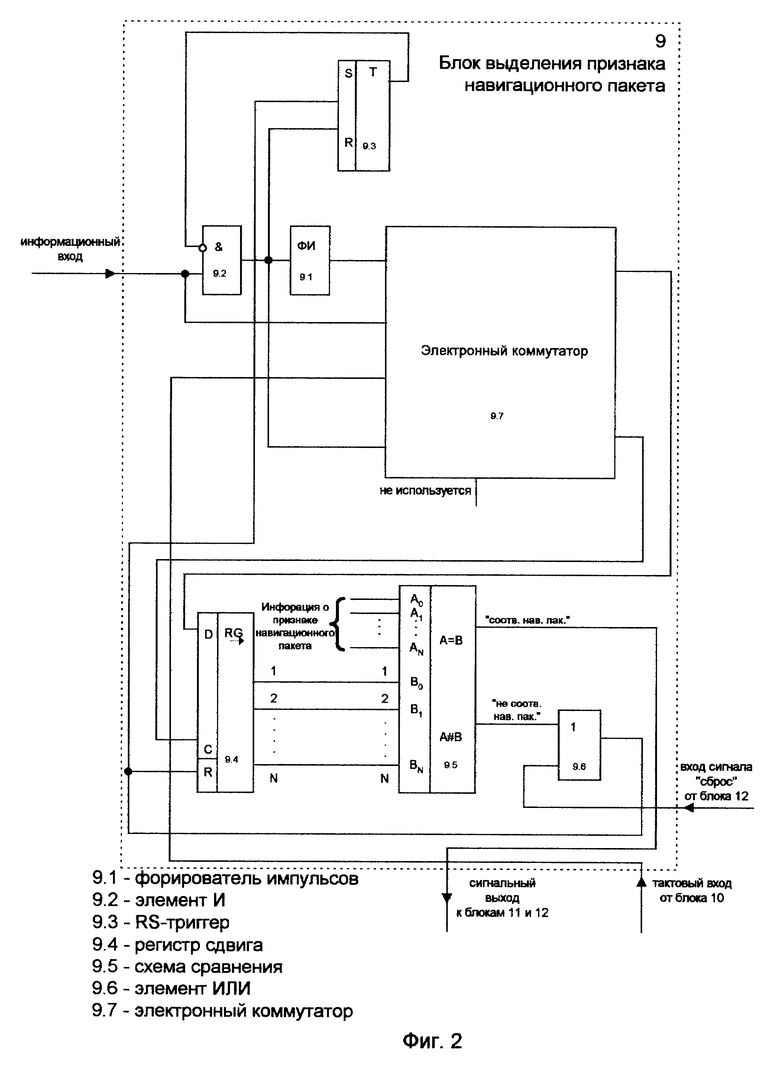

Блок выделения признака навигационного пакета состоит из формирователя импульсов, элемента И, RS-триггера, регистра сдвига, схемы сравнения, элемента ИЛИ, электронного коммутатора. Прямой вход элемента И является информационным входом блока и соединен с информационным входом электронного коммутатора. Выход элемента И подключен к входу формирователя импульсов, входу сброса RS-триггера и к второму управляющему входу электронного коммутатора. Выход формирователя импульсов соединен с первым управляющим входом электронного коммутатора. Тактовый вход электронного коммутатора является тактовым входом блока. Вход установки RS-триггера соединен со входом сброса регистра сдвига и выходом элемента ИЛИ. Выход RS-триггера, соединен с инверсным входом элемента И. Информационный выход электронного коммутатора соединен с информационным входом регистра сдвига, тактовый вход которого соединен с тактовым выходом электронного коммутатора. N выходов регистра сдвига, где N = 2,3. . . , соединены с соответствующими N входами второй группы входов схемы сравнения, а N входов первой группы входов которой являются информационными входами о признаке навигационного пакета. Выход "Соответствие навигационного пакета" схемы сравнения является сигнальным выходом блока, а выход схемы сравнения "Несоответствие навигационному пакету" соединен с первым входом элемента ИЛИ, второй вход которого является входом сигнала "Сброс" блока.

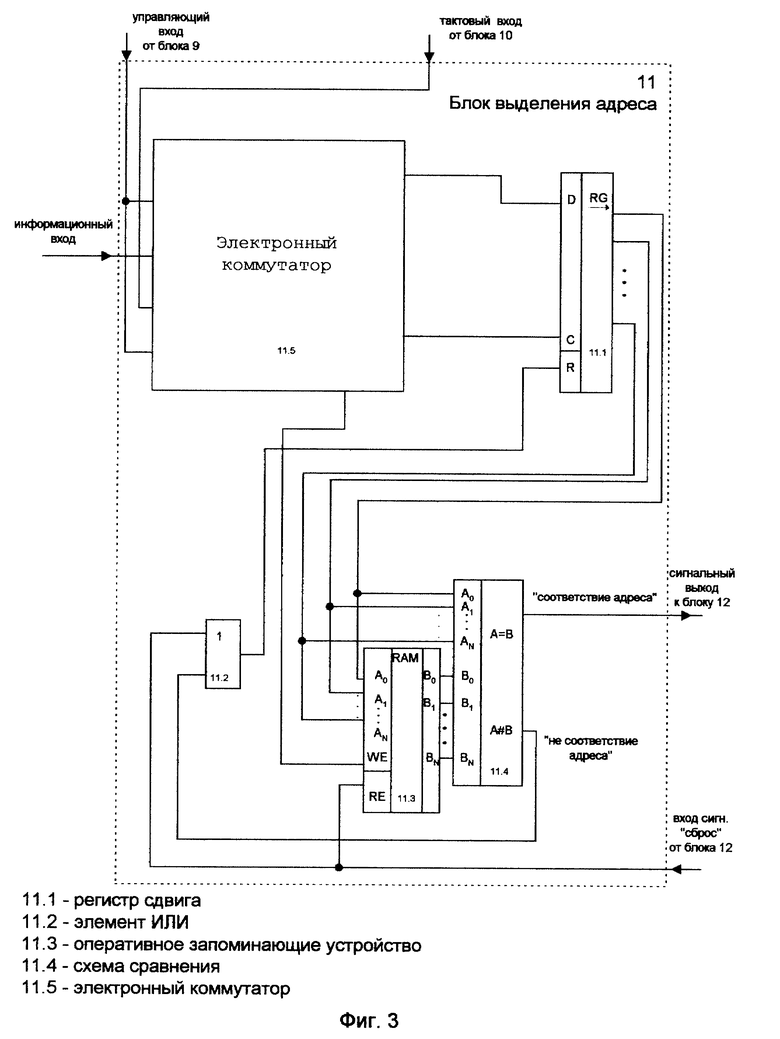

Блок выделения адреса состоит из регистра сдвига, элемента ИЛИ, оперативного запоминающего устройства, схемы сравнения, электронного коммутатора. Первый управляющий вход электронного коммутатора является управляющим входом блока и соединен одновременно со вторым управляющим входом электронного коммутатора. Информационный выход которого соединен с информационным входом регистра сдвига, тактовый вход электронного коммутатора является тактовым входом блока, а тактовый выход электронного коммутатора соединен с тактовым входом регистра сдвига. Вход сброса которого соединен с выходом элемента ИЛИ. Выход разрешения записи электронного коммутатора соединен со входом разрешения записи оперативного запоминающего устройства, вход разрешения чтения которого является входом сигнала "Сброс" блока и подключен к первому входу элемента ИЛИ. N входов данных оперативного запоминающего устройства, где N-2,3. . ., соединены с соответствующими N выходами регистра сдвига и N входами первой группы входов схемы сравнения. N выходов оперативного запоминающего устройства соединены с соответствующими N входами второй группы входов схемы сравнения. Выход "Соответствие адреса" которой является сигнальным выходом блока, а выход "Несоответствие адреса" соединен со вторым входом элемента ИЛИ.

Благодаря новой совокупности существенных признаков за счет введения блока выделения признака навигационного пакета, блока выделения адреса, элемента И, генератора тактовых импульсов, блока определения интервала поступления пакета и блока таймеров обеспечивается устранение конфликтов в канале множественного доступа при передаче навигационных пакетов, тем самым повышается пропускная способность канала множественного доступа.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

Заявляемое устройство поясняется чертежами, на которых:

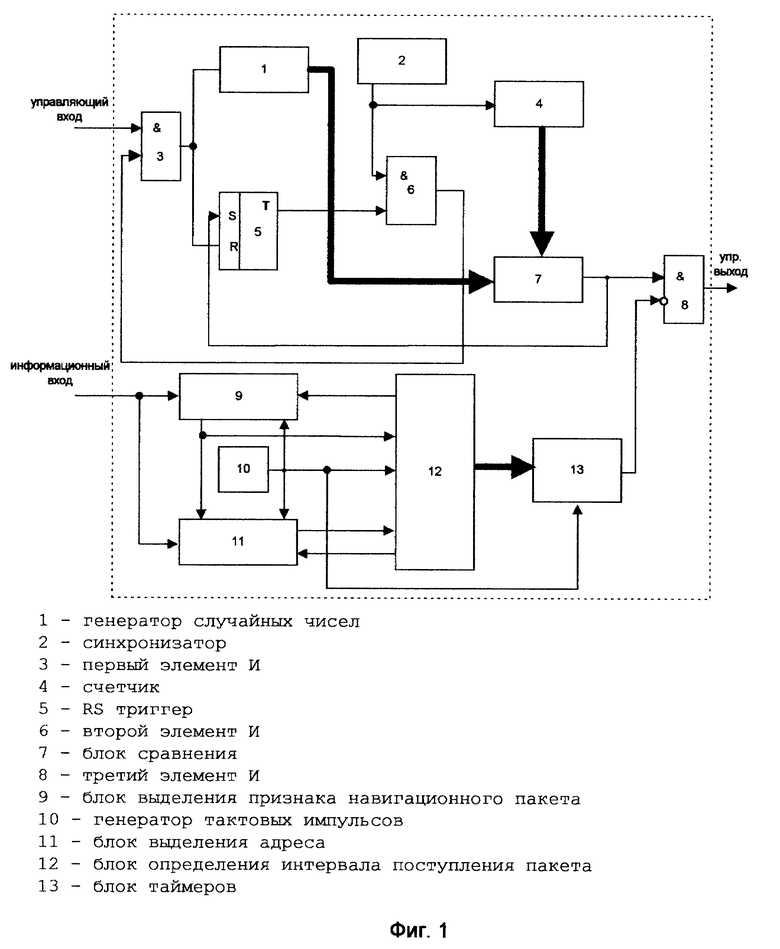

фиг. 1 - функциональная схема устройства управления передачей данных по радиоканалу;

фиг. 2 - схема блока выделения признака навигационного пакета;

фиг. 3 - схема блока выделения адреса;

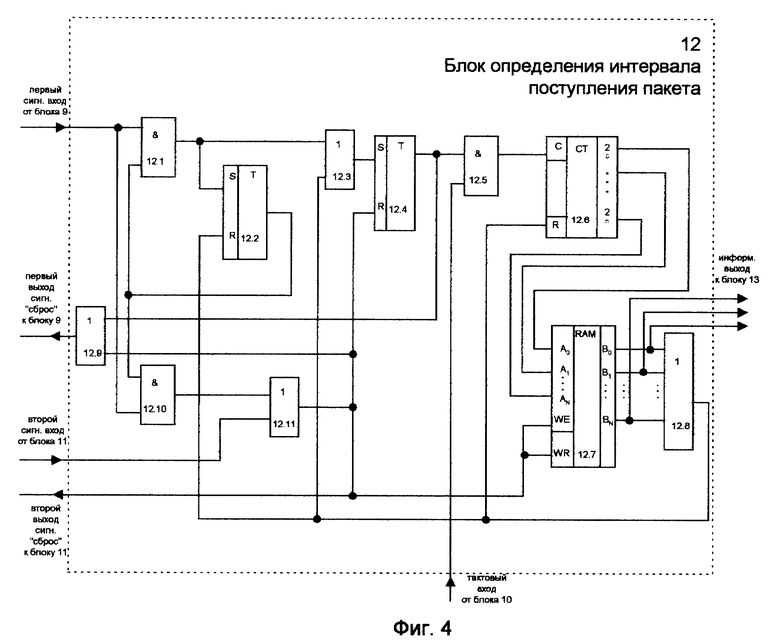

фиг. 4 - схема блока определения интервала поступления пакета;

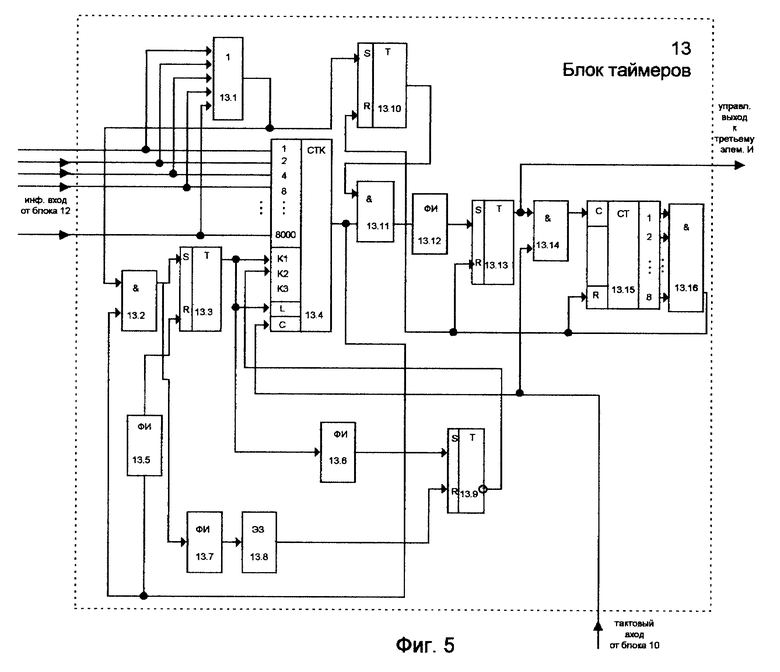

фиг. 5 - схема блока таймеров;

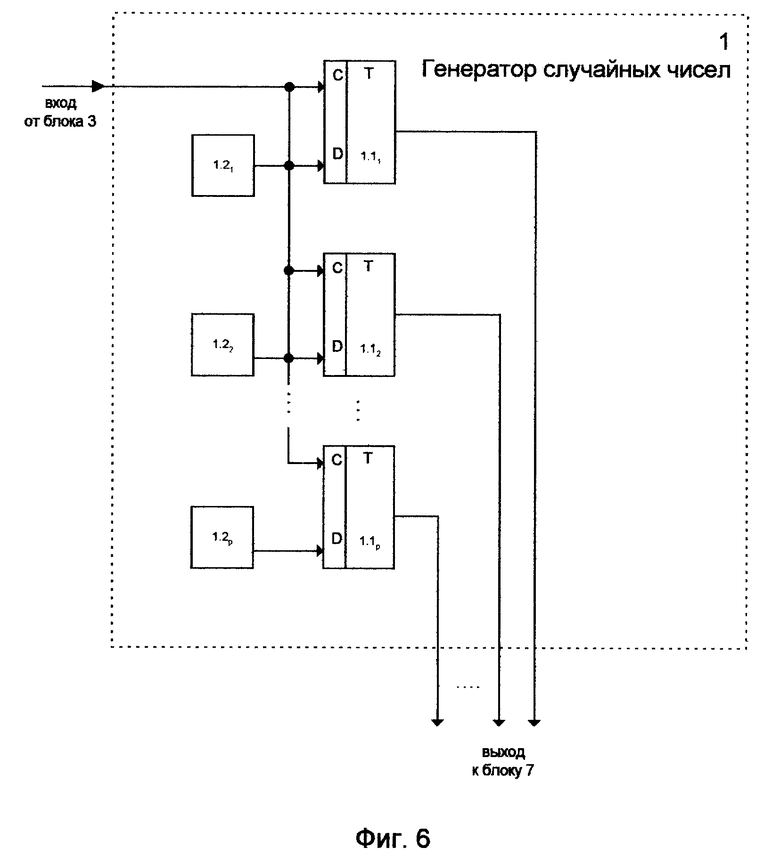

фиг. 6 - схема генератора случайных чисел;

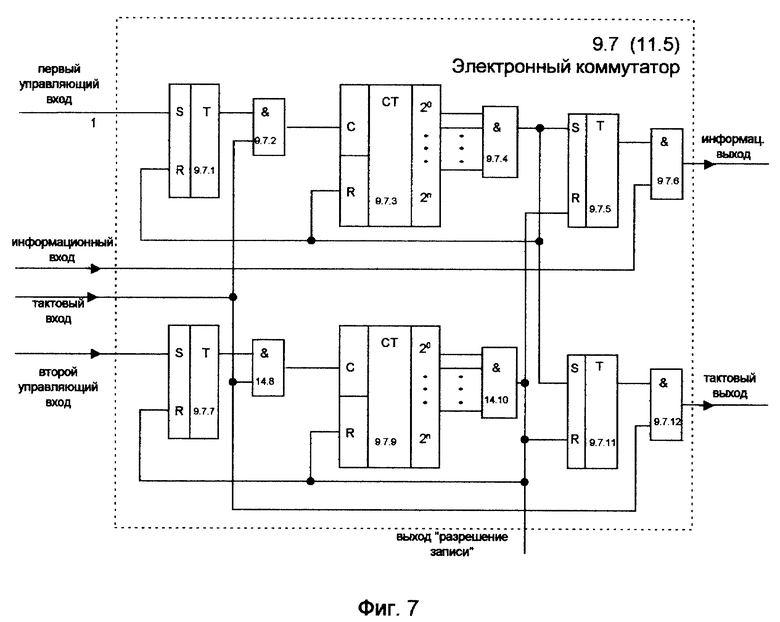

фиг. 7 - схема электронного коммутатора.

Заявляемое устройство управления передачей данных по радиоканалу, показанное на фиг. 1, состоит из: генератора случайных чисел 1, синхронизатора 2, первого элемента И 3, счетчика 4, RS-триггера 5, второго элемента И 6, блока сравнения 7, третьего элемента И 8, блока выделения признака навигационного пакета 9, генератора тактовых импульсов 10, блока выделения адреса 11, блока определения интервала поступления пакета 12, блока таймеров 13. Первый вход первого элемента И 3 является управляющим входом устройства. Выход синхронизатора 2 соединен со входом счетчика 4 и первым входом второго элемента И 6. Групповой выход счетчика 4 соединен со счетным входом блока сравнения 7. Вход случайных чисел которого соединен с групповым выходом генератора случайных чисел 1. Выход первого элемента И 3 соединен со входом генератора случайных чисел 1 и входом сброса R RS-триггера 5. Вход установки S которого соединен с выходом блока сравнения 7 и первым входом третьего элемента И 8. Выход второго элемента И 6 соединен со вторым входом первого элемента И 3. Выход RS-триггера 5 соединен со вторым входом второго элемента И 6. Информационный вход блока выделения признака навигационного пакета 9 подключен к информационному входу блока выделения адреса 11 и является информационным входом устройства. Выход третьего элемента И 8 является управляющим выходом устройства. Сигнальный выход блока выделения признака навигационного пакета 9 соединен с первым сигнальным входом блока определения интервала поступления пакета 12 и управляющим входом блока выделения адреса 11. Первый выход сигнала "Сброс" блока определения интервала поступления пакета 12 соединен со входом сигнала "Сброс" блока выделения признака навигационного пакета 9. Выход блока выделения адреса 11 соединен со вторым сигнальным входом блока определения интервала поступления пакета 12, второй выход сигнала "Сброс" которого соединен с входом сигнала "Сброс" блока выделения адреса 11. Выход генератора тактовых импульсов 10 соединен с тактовыми входами блоков выделения признака навигационного пакета 9, блока выделения адреса 11, блока определения интервала поступления пакета 12 и блока таймеров 13. Групповой выход блока определения интервала поступления пакета 12 соединен со входом блока таймеров 13, выход которого соединен с инверсным входом третьего элемента И 8.

Блок выделения признака навигационного пакета предназначен для выделения признака навигационного пакета. Может быть реализован по схеме, показанной на фиг. 2. Он состоит из формирователя импульсов 9.1, элемента И 9.2, RS-тригтера 9.3, регистра сдвига 9.4, схемы сравнения 9.5, элемента ИЛИ 9.6, электронного коммутатора 9.7. Прямой вход элемента И 9.2 является информационным входом блока и соединен с информационным входом электронного коммутатора 9.7. Выход элемента И 9.2 подключен к входу формирователя импульсов 9.1, входу сброса R RS-триггера 9.3 и к второму управляющему входу электронного коммутатора 9.7. Выход формирователя импульсов 9.1 соединен с первым управляющим входом электронного коммутатора 9.7. Тактовый вход электронного коммутатора 9.7 является тактовым входом блока. Вход установки S RS-триггера 9.3 соединен с входом сброса R регистра сдвига 9.4 и выходом элемента ИЛИ 9.6. Выход RS-триггера 9.3 соединен с инверсным входом элемента И 9.2.

Информационный выход электронного коммутатора 9.7 соединен с информационным D входом регистра сдвига 9.4, тактовый вход C которого соединен с тактовым выходом электронного коммутатора 9.7. Выходы регистра сдвига 9.4 соединены с соответствующими входами второй группы входов схемы сравнения 9.5, а ее первая группа входов является информационным входом о признаке навигационного пакета схемы сравнения 9.5. Выход "Соответствие навигационного пакета" схемы сравнения 9.5 является сигнальным выходом блока, а ее выход "Несоответствие навигационному пакету" соединен с первым входом элемента ИЛИ 9.6, второй вход которого является входом сигнала "Сброс" блока.

Блок выделения адреса предназначен для выделения адреса поступающего пакета. Может быть реализован по схеме, показанной на фиг. 3. Он состоит из регистра сдвига 11.1, элемента ИЛИ 11.2, оперативного запоминающего устройства 11.3, схемы сравнения 11.4, электронного коммутатора 11.5. Первый управляющий вход электронного коммутатора 11.5 является управляющим входом блока и соединен одновременно со вторым управляющим входом электронного коммутатора 11.5. Информационный выход которого соединен с информационным входом D регистра сдвига 11.1, тактовый вход электронного коммутатора 11.5 является тактовым входом блока, а тактовый выход электронного коммутатора 11.5 соединен с тактовым входом C регистра сдвига 11.1. Вход сброса R которого 11.1 соединен с выходом элемента ИЛИ 11.2. Выход разрешения записи электронного коммутатора 11.5 соединен со входом разрешения записи оперативного запоминающего устройства 11.3, вход разрешения чтения которого является входом сигнала "Сброс" блока и подключен к первому входу элемента ИЛИ 11.2. Первая группа входов A0, A1...AN оперативного запоминающего устройства 3 соединена с соответствующими выходами регистра сдвига 11.1 и первой группой входов A0, A1. ..AN схемы сравнения 11.4. Выходы B0, B1...BN оперативного запоминающего устройства 11.3 соединены со входами B0, B1...BN схемы сравнения 11.4. Выход A= B "Соответствие адреса" схемы сравнения 11.4 является сигнальным выходом блока, а выход A ≠ B "Несоответствие адреса" соединяется со вторым входом элемента ИЛИ 11.2.

Блок определения интервала поступления пакета предназначен для определения интервала поступления пакета. Может быть реализован по схеме, показанной на фиг. 4. Он состоит из элементов И 12.1, 12.5, 12.10, RS-триггеров 12.2, 12.4, элементов ИЛИ 12.3, 12.9, 12.8, 12.11 счетчика 12.6, оперативного запоминающего устройства (ОЗУ) 12.7. Первый вход элемента И 12.1 является первым сигнальным входом блока и вторым входом элемента И 12.10. Второй вход этого элемента соединен с выходом RS-триггера 12.2 и первым входом элемента И 12.10. Выход элемента И 12.1 соединен со входом установки S RS-триггера 12.2 и первым входом элемента ИЛИ 12.3. Второй вход элемента ИЛИ 12.3 соединен со входом сброса R RS-триггера 12.2, входом сброса R счетчика 12.6 и выходом элемента ИЛИ 12.8. Выход элемента ИЛИ 12.3 является входом установки S RS-триггера 12.4, вход сброса R которого соединен со вторым выходом элемента ИЛИ 12.9, выходом элемента ИЛИ 12.11, входами разрешения записи WE и разрешения чтения RE ОЗУ 12.7 и является вторым выходом сигнала "Сброс" блока. Выход RS-триггера 12.4 является первым входом элемента И 12.5 и одновременно соединен с первым выходом элемента ИЛИ 12.9. Второй вход элемента И 12.5 является тактовым входом блока, а его выход является тактовым входом C счетчика 12.6. Выходы счетчика 20 - 2n являются входами A0-AN для ОЗУ 12.7. Выходы ОЗУ 12.7 B0-BN соединены с соответствующими входами элемента ИЛИ 12.8 и являются информационным выходом блока. Первый вход элемента ИЛИ 12.11 соединен с выходом элемента И 12.10, а второй вход является вторым сигнальным входом блока. Вход элемента ИЛИ 12.9 является первым выходом сигнала "Сброс" блока.

Блок таймеров предназначен для отсчета интервала поступления пакета и для выработки сигнала блокирования собственной передачи. Блок может быть реализован по схеме, показанной на фиг. 5. Он состоит из элемента ИЛИ 13.1, элементов И 13.2, 13.11, 13.14, 13.16, RS-триггеров 13.3, 13.9, 13.10, 13.13, счетчика с переменным коэффициентом деления 13.4, счетчика 11.15, формирователей импульсов 13.5, 13.6, 13.7, 13,12 элемента задержки 13.8. Входы элемента ИЛИ 13.1 являются информационным входом блока и соединены со входами 1-8000 счетчика с переменным коэффициентом деления 13.4. Выход элемента И 13.1 соединен с первым входом элемента И 13.2 и входом установки S RS-тригтера 13.10. Второй вход элемента И 13.2 соединен со входом формирователей импульсов 13.5 и выходом счетчика с переменным коэффициентом деления 13.4 и вторым входом элемента И 13.11. Выход элемента И 13.2 является входом установки S RS-тригтера 13.3 и соединен со входом формирователя импульсов 13.7. Выход формирователя импульсов 13.5 соединен со входом сброса R RS-тригтера 13.3. Выход которого соединен со входами K1 и L счетчика с переменным коэффициентом деления 13.4 и входом формирователя импульсов 13.6. Тактовый вход С счетчика с переменным коэффициентом деления 13.4 соединен со вторым входом элемента И 13.14 и является тактовым входом блока, а вход К2 этого же счетчика соединен с инверсным выходом RS-тригтера 13.9. Вход установки S которого соединен с выходом формирователя импульсов 13.6, а вход сброса R с выходом элемента задержки 13.8. Вход данного элемента задержки соединен с выходом формирователя импульсов 13.7. Первый вход элемента И 13.11 соединен с выходом RS-триггера 13.10. Выход элемента И 13.11 является входом формирователя импульсов 13.12 и входом сброса R RS триггера 13.10. Выход формирователя импульсов 13.12 соединен со входом установки S RS-триггера 13.13. Вход сброса R которого соединен со входом сброса R счетчика 13.15, входом сброса R RS-триггера 13.10 и выходом элемента И 13.16. Выход RS-триггера 13.13 является управляющим выходом блока и соединен с первым входом элемента И 13.14. Второй вход которого соединен с тактовым входом C счетчика 13.15. Выходы 1-8 которого соединяются с соответствующими входами элемента И 13.16.

Генератор случайных чисел предназначен для случайного выбора момента начала передачи. Может быть реализован по схеме, показанной на фиг. 6. Он состоит из p D-триггеров элементы (1.1.1-1.1.р) и p генераторов шума элементы (1.2.1-.2.р). Тактовые входы C всех D-триггеров и являются входом блока. Информационные входы D D-триггеров соединены с выходами генераторов шума 1.2.1 - 1.2. р. Выходы D-триггеров 1.1.1-1.1.p являются групповым выходом блока.

Электронный коммутатор предназначен для отсчета количества символов, предшествующих символам признака пакета и собственно символов признака пакета и формирования управляющего сигнала. Может быть реализован по схеме, показанной на фиг. 7. Он состоит из RS-триггеров 9.7.1, 9.7.7, 9.7.5, 9.7.11, элементов И 9.7.2, 9.7.8, 9.7.4, 9.7.10, 9.7.6, 9.7.12, счетчиков 9.7.3, 9.7.9. Причем управляющий вход устройства является входом установки S RS-триггера 9.7.1, вход сброса R которого соединен со входом сброса R счетчика 9.7.3 и входами установки S RS-триггеров 9.7.5 и 9.7.11 и выходом элемента И 9.7.4. Выход RS-триггера 9.7.1 является первым входом элемента И 14.2. Второй вход которого является тактовым входом устройства и соединен со вторым входом элемента И 9.7.8 и вторым входом элемента И 9.7.12. Выход элемента И 14.2 соединен с тактовым входом С счетчика 9.7.3. Выходы 20...2n которого соединены с соответствующими входами элемента И 9.7.4. Вход сброса R RS-триггера 9.7.5 соединен с выходом элемента И 9.7.10, входами сброса R RS-триггеров 9.7.11, 9.7.7 и счетчика 9.7.9 и является выходом "Разрешение записи" электронного коммутатора. Выход RS-триггера 9.7.5 соединен с первым входом элемента И 9.7.6, второй вход которого является информационным входом блока, а выход - информационным выходом электронного коммутатора. Вход установки S RS-триггера 9.7.7 является управляющим входом устройства, а выход - первым входом элемента И 9.7.8. Выход которого соединен с тактовым входом счетчика 9.7.9. Выходы 20 . . . 2n которого соединены с соответствующими входами элемента И 9.7.10. Выход RS-триггера 9.7.11 соединен с первым входом элемента И 9.7.12. Выход которого является тактовым выходом устройства.

Генератор шума 1.2.1 - 1.2. p предназначен для формирования случайно изменяющихся во времени выходных напряжений и описан - Элементы радиоэлектронных устройств. / Б.И. Коротков, - М.: Радио и связь, 1988, рис.7.24, с. 107.

D-триггеры 1.1.1-1.1.p описаны - Основы импульсной и цифровой техники / Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, с. 90 - 91.

Синхронизатор 2 представляет собой генератор тактовых импульсов и описан - Микросхемы и их применение: Справ. пособие. / 1984, с. 213, рис. 7.6. Может быть реализован на интегральных микросхемах (ИМС) серий 511, 176.

Счетчик 4 описан - Журнал "Радио", 1987, 1, стр. 43. Может быть реализован на ИМС КА561ИЕ15б (счетчик с переменным коэффициентом деления).

Блок сравнения 7 описан - Импульсные цифровые устройства /И.О. Лебедев, А. М. Сидоров. - Л.: ВАС, 1980, с.51, рис. 2.33, 2.34. Может быть реализован на ИМС серий 133, 564.

Генератор тактовых импульсов 10 описан - Микросхемы и их применение: Справ. пособие. / 1984, - с. 213, рис. 7.6. Может быть реализован на интегральных микросхемах (ИМС) серий 16.101, 176.

Счетчики 11.3, 11.10, 12.6, 13.4, 13.15, 9.7.3, 9.7.9 известны и описаны - Основы импульсной и цифровой техники/ Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, рис. 5.38, с. 169 - 172.

Регистры сдвига 9.4, 11.1 предназначены для преобразования информации путем ее сдвига под воздействием сдвигающих (тактовых) импульсов. Может быть реализован по схеме, описанной - Основы импульсной и цифровой техники/ Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, рис.5.28, с. 158 - 159.

Формирователи импульсов 9.1, 13.5, 13.6, 13.7, 13.12, входящие в блок выделения признака навигационного пакета, и блок таймеров предназначены для формирования из логического уровня короткого импульса, идентичны, известны и описаны - Основы цифровой техники. /Л.А. Мальцева, - М.: Радио и связь, 1986, - рис. 21, с.30.

Логические элементы И, входящие блоки заявленного устройства известны и описаны - Основы цифровой техники /Л.А. Мальцева, Э.М. Фромберг. - М.: Радио и связь, - с. 30 - 31. Могут быть реализованы на ИМС серий 133 и 564.

Логические элементы ИЛИ, входящие блоки заявленного устройства известны и описаны - Основы импульсной и цифровой техники/ Под общей ред. А.М. Сидорова, - СПВВИУС, 1995, рис. 2.4, с. 39-41.

RS-триггеры, входящие блоки заявленного устройства известны и описаны - Микросхемы и их применение: Справ. пособие. /В.А. Катушев, В.Н. Вениаминов, В. Г. Ковалев и др. - М.: Радио и связь, 1984, - с.122, рис.4.16. Могут быть реализованы на ИМС серий 133, 564.

Схемы сравнения 9.5, 11.4, входящие в блок выделения признака навигационного пакета и блок выделения адреса, известны и описаны - Популярные цифровые микросхемы: Справочник. /В.Л. Шило, - Челябинск: Металлургия 1989, - с. 261.

Оперативные запоминающие устройства 11.3, 12.7, входящие в блок выделения адреса и блок определения интервала поступления пакета, известны и описаны - Популярные цифровые микросхемы: справочник. /В.Л. Шило, - Челябинск: Металлургия, 1989, с. 161.

Элемент задержки 13.8, входящий в блок таймеров, может быть реализован на базе регистра сдвига, известен и описан - Цифровые интегральные микросхемы: Справочник. /П.П. Мальцев и др., - М.: Радио и связь 1994, с.52.

Функциональная схема устройства, реализующего выполнение описанных функций управления передачей данных по радиоканалу, приведена на фиг. 1.

Заявленное устройство работает следующим образом.

При включении питания (схема питания не приводится) триггер 5 устанавливается в режим хранения логической единицы. Синхронизатор 2 выдает импульсы с интервалом времени, равным длительности интервала передачи пакета, при этом импульсы поступают на первый вход второго элемента И 6 и на тактовый вход счетчика 4, вызывая последовательную смену кодовых комбинаций на выходе счетчика 4 (число кодовых комбинаций равно числу "окон" в цикле передачи).

При возникновении необходимости в передаче пакета на управляющий вход устройства поступает сигнал запроса передачи (в виде уровня логической единицы). При этом очередной сигнал с выхода синхронизатора 2 (в виде единичного импульса) через открытый второй элемент И 6 поступает на управляющий вход первого элемента И 3. Так как первый элемент И 3 открыт по сигнальному входу сигналом запроса передачи, то единичный импульс с выхода первого элемента И 3 поступает на вход R триггера 5, переводя его в нулевое состояние, а также на управляющий вход генератора случайных чисел 1, который выдает в параллельном коде на второй сигнальный вход блока сравнения 7 кодовую комбинацию, соответствующую номеру окна в цикле передачи, выбранного для передачи пакета. При этом триггер 5 закрывает второй элемент И 6.

В момент совпадения кодовых комбинаций на первом и втором входах блока сравнения 7 последний выдает сигнал "Разрешение передачи" в виде единичного импульса через открытый третий элемент И 8 на управляющий выход устройства, а также переводит триггер 5 в единичный режим (сигнал "Запрос передачи" с управляющего входа устройства снимается). Таким образом, устройство готово к передаче очередного пакета.

Все передаваемые в канале множественного доступа пакеты поступают на информационный вход устройства. При выделении блоком 9 из поступившего пакета признака навигационной информации сигнал с уровнем логической единицы с сигнального выхода последнего поступает на первый сигнальный вход блока определения интервала поступления пакета 12, в котором осуществляется измерение длительности интервала времени между смежными моментами передачи навигационных пакетов корреспондентом, адрес которого выделен из пакета и хранится в ОЗУ блока выделения адреса 11. При повторном получении навигационного пакета от того же корреспондента информация о длительности интервала поступления пакетов с информационного выхода блока определения интервала поступления пакета 12 поступает на информационный вход блока таймеров 13. По окончании каждого интервала данная информация уточняется. Блок таймеров 13 по окончании каждого интервала блокирует возможную выдачу сигнала "Разрешение передачи" (так как сигнал с уровнем логической единицы с выхода блока таймеров 13 поступает на инверсный вход третьего элемента И 8 и закрывает его на время прохождения навигационного пакета в канале). Тем самым устраняются конфликты при передаче навигационных пакетов в канале множественного доступа.

Блок выделения признака навигационного пакета 9, функциональная схема которого приведена на фиг. 2, работает следующим образом. При прохождении по каналу множественного доступа информации содержимое пакета с информационного входа устройства через открытый элемент И 9.2 поступает на формирователь импульсов 9.1. Импульс с выхода последнего поступает на первый управляющий вход электронного коммутатора 9.7. В результате работы коммутатора поступление информации и тактовых импульсов на входы регистра сдвига 9.4 прекращается. Кодовая комбинация признака пакета, выделенная из заголовка пакета, в параллельном коде поступает с выходов регистра сдвига 9.4 на вторые входы схемы сравнения 9.5 (па первые ее входы постоянно подается кодовая комбинация признака навигационного пакета). Если кодовые комбинации на входах A0-An и B0-Bn схемы сравнения 9.5 совпадают (то есть в канале был передан навигационный пакет), то сигнал с уровнем логической единицы с выхода схемы сравнения 9.5 поступает на сигнальный выход блока выделения адреса 11 и блока определения интервала поступления пакета 12. В исходное состояние блок выделения признака навигационного пакета 9 переводится сигналом с уровнем логической единицы, поступающим из блока определения интервала поступления пакета 12 или соответствующим сигналом с выхода (A=B) схемы сравнения 9.5 (при этом переводится в нулевое состояние регистр сдвига 9.4 и триггер 9.3).

Блок выделения адреса 11, функциональная схема которого представлена на фиг. 3, работает следующим образом. В том случае, если из передаваемого в канале множественного доступа пакета блок 9 выделяет признак навигационного пакета, сигнал с уровнем логической единицы с выхода блока 9 поступает на первый и второй управляющие входы электронного коммутатора 11.5. Далее в электронном коммутаторе осуществляется выделение адреса из заголовка пакета. С выходов регистра сдвига 11.1 кодовая комбинация адреса поступает одновременно на первые входы схемы сравнения 11.4 и на информационные входы оперативного запоминающего устройства (ОЗУ) 11.3. Сигнал с уровнем логической единицы с выхода элемента И 11.2 (по окончании отсчета полного количества символов адреса) поступает на вход разрешения записи WE ОЗУ 11.3 (при этом кодовая комбинация адреса записывается в ОЗУ). При очередном приеме пакета адрес, хранящийся в ОЗУ 11.3, сравнивается с адресом, выделенным из заголовка пакета и поступающим на первые входы (A0-An) схемы сравнения 11.4. Сравнение осуществляется в момент прихода от блока определения интервала поступления пакета 12 сигнала разрешения считывания, поступающего на вход RE ОЗУ 11.3 (при этом также переводится в нулевое состояние регистр сдвига 11.1), положительный результат сравнения (сигнал с уровнем логической единицы) с выхода A=B схемы сравнения 11.4 поступает в блок 12.

Блок определения интервала поступления пакета 12, функциональная схема которого представлена на фиг. 4, работает следующим образом. Если блок выделения признака навигационного пакета 9 выявил наличие данного признака в поступившем из канала пакете, то сигнал с уровнем логической единицы поступает на первый сигнальный вход блока определения интервала поступления пакета 12. При этом через открытый элемент И 12.1 (так как триггер 12.2 находится в нулевом состоянии) и элемент ИЛИ 12.3 данный сигнал переводит триггеры 12.2, 12.4 в единичное состояние. Сигнал с уровнем логической единицы с выхода триггера 12.4 открывает элемент И 12.5 (последовательность тактовых импульсов поступает на счетный вход счетчика 12.6), а также поступает в блок выделения признака навигационного пакета 9 через элемент ИЛИ 12.9 (регистр сдвига последнего переводится в нулевое состояние). Сигнал с уровнем логической единицы с выхода триггера 12.2 закрывает элемент И 12.1 и открывает элемент И 12.10. После выделения из очередного, поступившего из канала множественного доступа пакета, признака навигационного пакета и при условии совпадения адреса с принятым ранее, сигнал с уровнем логической единицы с выхода блока выделения адреса 11 поступает на второй сигнальный вход блока определения интервала поступления пакета 12. При этом сигнал с уровнем логической единицы с выхода элемента ИЛИ 12.11 переводит триггер 12.4 в нулевое состояние, поступает на входы разрешения записи WE и считывания RE оперативного запоминающего устройства (ОЗУ) 12.7, а также поступает в блок выделения адреса 11 и через элемент ИЛИ 12.9 - в блок выделения признака навигационного пакета 9 и переводит регистры сдвига этих блоков в нулевое состояние (подготовив тем самым блоки к приему очередного навигационного пакета). Имеющаяся в данный момент на выходах счетчика 12.6 кодовая комбинация, соответствующая длительности интервала поступления навигационного пакета от корреспондента с i-м адресом, записывается в ОЗУ 12.7 и считывается из него, поступая на вход блока таймеров 13 (который отсчитывает данный интервал). Одновременно сигнал с уровнем логической единицы с выхода элемента ИЛИ 12.8 поступает на вход R счетчика 12.6 и обнуляет его. Кроме того, он переводит в единичное состояние триггеры 12.2 и 12.4 (тем самым обеспечивается выполнение очередного измерения интервала поступления навигационного пакета).

Блок таймеров 13 работает следующим образом. В исходном состоянии на выходе счетчика с переменным коэффициентом деления 13.4 имеется уровень логической единицы. Триггеры 13.3, 13.9, 13.10 и 13.13 находятся в нулевом состоянии, элемент И 13.2 открыт по второму управляющему входу. При поступлении от блока определения интервала поступления пакета 12 кодовой комбинации, соответствующей длительности интервала между поступлениями пакетов, сигнал с уровнем логической единицы с выхода элемента ИЛИ 13.1 переводит в единичное состояние триггер 13.10, а также триггер 13.3 (через открытый элемент И 13.2) При этом уровень логической единицы поступает на управляющие входы K1 и L счетчика 13.4. Триггер 13.9 импульсом с выхода формирователя импульсов 13.6 переводится в единичное состояние, на управляющем входе K2 счетчика 13.4 устанавливается уровень логического нуля. Через интервал времени, равный трем периодам прохождения тактовых импульсов, триггер 13.9 переводится в нулевое состояние единичным импульсом с выхода элемента задержки 13.8. С этого момента счетчик 13.4 начинает отсчет тактовых импульсов, поступающих на его счетный вход C. По окончании отсчета сигнал с уровнем логической единицы с выхода счетчика 13.4 через открытый элемент И 13.11 поступает на вход формирователя импульсов 13.12, импульс с выхода последнего переводит триггер 13.13 в единичное состояние. С выхода триггера 13.13 на управляющий выход блока таймеров 13 поступает сигнал блокировки передачи. Длительность интервала поступления данного сигнала определяется счетчиком 13.15, который отсчитывает интервал времени, равный длительности интервала передачи пакета в канале, после чего переводит триггер 13.13 в нулевое состояние. Сигнал блокировки с выхода блока таймеров 13 снимается, блок переходит в исходное состояние.

Генератор случайных чисел 2, функциональная схема которого приведена на фиг. 6, работает следующим образом. Каждая группа D-триггеров 1.1 обеспечивает различную длину кодовой комбинации на выходе генератора случайных чисел 2. Ha D входах каждого из D-триггеров 1.1 имеют место случайно изменяющиеся во времени выходные напряжения независимых генераторов шума 1.2. Если в момент появления импульса на C входе p-готриггера 1.1 выходное напряжение p-го генератора шума 1.2 ниже порога срабатывания триггера, то на выходе триггера будет иметь место уровень логического нуля (в противном случае - уровень логической единицы). Случайная кодовая комбинация с выходов триггеров 1.1 поступает на второй сигнальный вход блока сравнения 7.

Электронный коммутатор, функциональная схема которого приведена на фиг. 7, работает следующим образом. Управляющий сигнал переводит RS-триггеры 9.7.1 и 9.7.7 в режим хранения логической единицы, в результате последовательность тактовых импульсов через открытые элементы И 9.7.2, 9.7.8 поступает на счетные входы со счетчиков 9.7.3, 9.7.9. Счетчик 9.7.3 отсчитывает количество символов заголовка, предшествующих символам признака пакета, после чего сигналом с уровнем логической единицы переводит триггер 9.7.1 в нулевое состояние (поступление тактовых импульсов на вход счетчика 9.7.3 прекращается), а триггеры 9.7.5, 9.7.11 переводятся в единичное состояние. На информационный вход блока поступает последовательность символов заголовка пакета, начиная с первого из символов признака пакета. Сам счетчик 9.7.3 также переходит в нулевое состояние. Счетчик 9.7.9, закончив отсчет количества символов, предшествующих символам признака пакета, и количества символов собственно признака пакета, выдает сигнал с уровнем логической единицы на входы R триггеров 9.7.7, 9.7.5, 9.7.11 и переводит их в нулевое состояние. При этом поступление информации и тактовых импульсов прекращается.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2001 |

|

RU2211540C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2004 |

|

RU2259017C1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1996 |

|

RU2115952C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1998 |

|

RU2133500C1 |

| СПОСОБ И УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТОВ ДАННЫХ В КАНАЛЕ СВЯЗИ ОБЩЕГО ПОЛЬЗОВАНИЯ | 1998 |

|

RU2137312C1 |

Изобретение относится к вычислительной технике и может использоваться в узлах коммутации сообщений (пакетов) сети передачи данных. Техническим результатом при реализации изобретения является обеспечение повышения пропускной способности канала множественного доступа. Устройство управления передачей данных по радиоканалу состоит из генератора случайных чисел, синхронизатора, трех элементов И, счетчика, RS-триггера, блока сравнения, блока выделения признака навигационного пакета, генератора тактовых импульсов, блока выделения адреса, блока определения интервала поступления пакета, блока таймеров. Благодаря введенным блоку выделения признака навигационного пакета, блоку выделения адреса, третьему элементу И, генератору тактовых импульсов, блоку определения интервала поступления пакета и блоку таймеров обеспечивается устранение конфликтов в канале множественного доступа при передаче навигационных пакетов и тем самым повышается пропускная способность канала множественного доступа. 2 з.п. ф-лы, 7 ил.

| Устройство для управления передачей данных по радиоканалу | 1986 |

|

SU1319298A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1995 |

|

RU2099889C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| DE 4121450 C1, 20.02.92 | |||

| US 4908871 A, 20.03.90. | |||

Авторы

Даты

2000-01-10—Публикация

1998-11-12—Подача