Устройство относится к техническим средствам для определения теплофизических характеристик и может быть использоваться как при исследовании свойств новых материалов, так и в тепловом неразрушающем контроле.

Известны способы определения теплофизических характеристик многослойных материалов [1, 2], основанные на измерении температуры поверхности образцов, нагретых с помощью импульсных источников, и обработке результатов измерений, полученных в течение определенного интервала времени. Указанные способы позволяют определить теплофизические характеристики многослойных материалов в том случае, когда известны заранее характеристики одного из слоев. Для послойного определения теплофизических характеристик перечисленные выше способы неприемлемы.

Известно устройство для определения теплофизических параметров материалов [3], содержащее источник импульсного нагрева, термопару, усилитель, повторитель, интеграторы, дифференциатор, нуль-орган, триггер, умножитель, вычитатель, измеритель и источник опорного напряжения.

Недостатками известного устройства [3] являются невысокая точность вследствие невозможности учета тепловых потерь и искажения помехами начального участка термограммы, а также невозможность послойного определения характеристик многослойных образцов.

Известно устройство для прецизионного определения характеристик материалов [4], наиболее близкое по структуре к предлагаемому устройству, содержащее источник импульсного нагрева, вход которого соединен с выходом синхронизатора, термопару, подключенную через усилитель к входу дифференциатора, а также первый и второй интеграторы, источник опорного напряжения, при этом первый вход управления первого интегратора соединен с выходом синхронизатора, а информационный вход - с выходом источника опорного напряжения, информационный вход второго интегратора соединен с выходом усилителя, информационные входы третьего, четвертого и пятого интеграторов соединены с выходом источника опорного напряжения, а выходы каждого из них соединены с первыми входами первого, второго и третьего компараторов соответственно, вторые входы которых соединены с выходом масштабного усилителя, а вход масштабного усилителя соединен с выходом первого интегратора, выход первого компаратора соединен с первыми входами управления второго, третьего, четвертого и шестого интеграторов, выход второго компаратора соединен с вторыми входами управления четвертого и шестого интеграторов, входом управления пятого интегратора и первым входом управления седьмого интегратора, второй вход управления которого соединен с выходом третьего компаратора и вторым входом управления пятого компаратора, а информационный вход - с информационными входами второго и шестого интеграторов, выходом усилителя и входом дифференциатора, выход которого соединен с входом экстрематора, а выход экстрематора соединен с вторыми входами управления первого, второго и третьего интеграторов, причем выходы масштабного усилителя, второго, шестого и седьмого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно.

Известное устройство предназначено для определения теплофизических характеристик однослойных образцов, что ограничивает его функциональные возможности.

Цель изобретения - расширение функциональных возможностей устройства за счет способности определения характеристик материалов многослойных объектов при одностороннем доступе.

В устройство, содержащее источник импульсного нагрева, вход которого через синхронизатор соединен с пусковой клеммой, термопару, подключенную через усилитель к входу дифференциатора, два компаратора, пять интеграторов и источник опорного напряжения, при этом первый вход управления первого интегратора и вход управления второго интегратора соединены с выходом синхронизатора, информационные входы с первого по четвертый интеграторов соединены с выходом источника опорного напряжения, информационный вход пятого интегратора соединен с выходом усилителя, выход первого интегратора соединен с первым входом первого компаратора, второй вход которого соединен через масштабный усилитель с выходом третьего интегратора, выход масштабного усилителя соединен с первым входом второго компаратора, второй вход которого соединен с выходом четвертого интегратора, а выход соединен с первым входом управления четвертого интегратора, дополнительно введены датчик длительности импульса, сумматор, блок умножения, нуль-орган, три делителя частоты, два триггера, два управляемых ключа, два логических элемента ИЛИ, запоминающее устройство и блок управления, при этом выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с первым входом сумматора, второй вход которого соединен с выходом усилителя, а выход соединен через нуль-орган с первым входом первого делителя частоты, второй вход которого соединен с выходом датчика длительности импульса нагрева, вторым входом управления первого интегратора, первым входом первого логического элемента ИЛИ и первым входом первого триггера, а выход соединен с первым входом первого управляемого ключа, второй вход которого соединен с первым выходом второго триггера, а выход соединен с вторым входом первого триггера, первый выход которого является первым выходом устройства, а второй выход соединен с первым входом второго управляемого ключа, второй и третий входы которого соединены с выходом первого делителя частоты и вторым выходом второго триггера соответственно, а выход соединен с первыми входами управления третьего и пятого интегратора, вторым входом управления четвертого интегратора и первым входом блока управления, второй вход которого соединен с выходом второго компаратора и первым входом второго делителя частоты, второй вход которого соединен с первым входом третьего делителя частоты, выходом синхронизатора и первым входом второго логического элемента ИЛИ, второй вход которого соединен с выходом третьего делителя частоты, третьим входом управления четвертого интегратора и вторым входом первого логического элемента ИЛИ, а выход соединен с первым входом второго триггера, второй вход которого соединен с выходом первого компаратора, выход первого логического элемента ИЛИ соединен с вторым входом управления третьего интегратора и третьим входом блока управления третьего интегратора и третьим входом блока управления, четвертый вход которого соединен с выходом второго делителя частоты, вторым входом управления пятого интегратора и вторым входом третьего делителя частоты, первый выход блока управления соединен с третьим входом управления пятого интегратора, второй выход блока управления соединен с первым входом запоминающего устройства второй и третий входы которого соединены соответственно с выходом пятого интегратора и выходом масштабного усилителя, а выход является вторым выходом устройства.

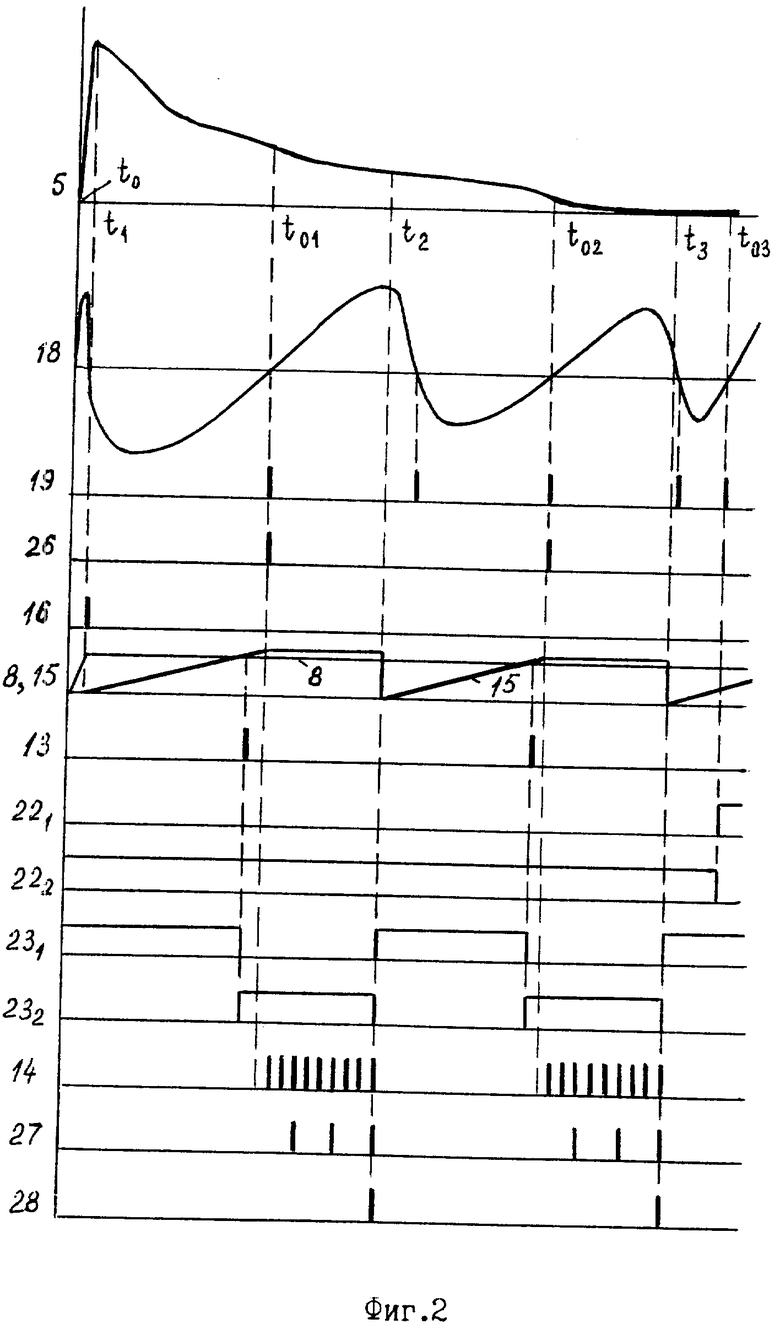

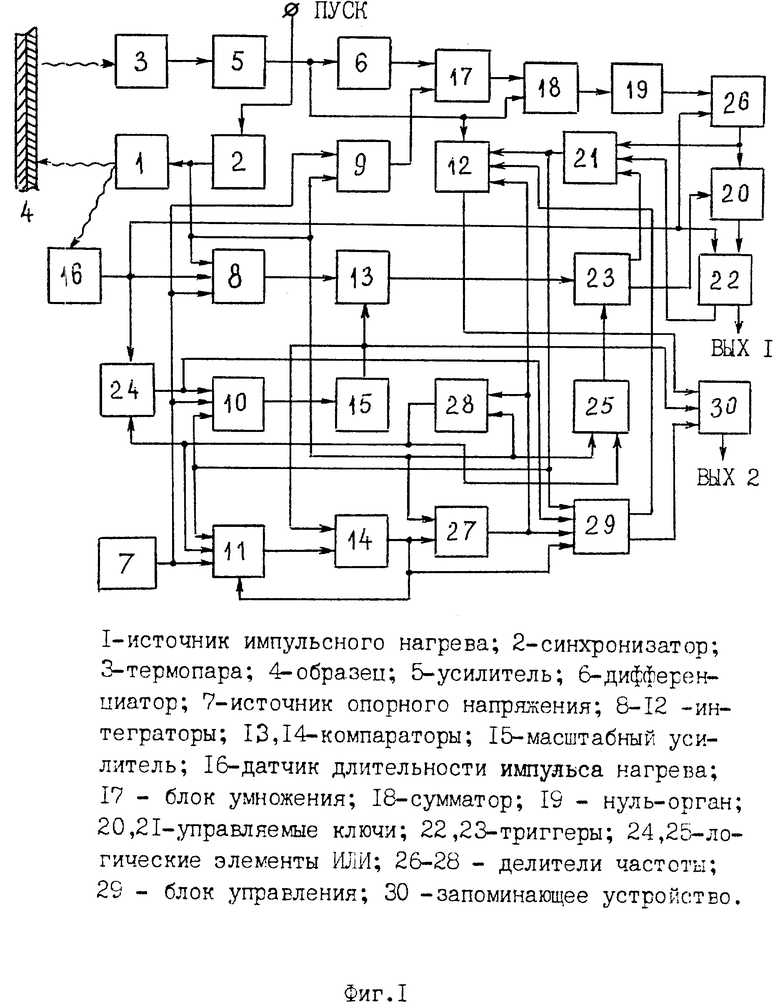

На фиг. 1 изображена схема устройства, на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит источник 1 импульсного нагрева, синхронизатор 2, термопару 3, измеряющую температуру поверхности образца 4, усилитель 5, дифференциатор 6, источник 7 опорного напряжения, интеграторы 8-12, компараторы 13, 14, масштабный усилитель 15, датчик 16 длительности импульса нагрева, блок 17 умножения, сумматор 18, нуль-орган 19, управляемые ключи 20, 21, триггеры 22, 23, логические элементы ИЛИ 24, 25, делители 26-28 частоты, блок 29 управления, запоминающее устройство 30.

Источник 1 импульсного нагрева оптически связан с датчиком 16 длительности импульса нагрева и многослойным образом 4, температура поверхности которого измеряется термопарой 3. Вход источника 1 соединен с выходом синхронизатора 2. Вход синхронизатора 2 соединен с пусковой клеммой. Термопара 3 соединена с входом усилителя 5. Выход усилителя 5 соединен с входом дифференциатора 6, информационным входом интегратора 12 и вторым входом сумматора 18. Выход дифференциатора 6 соединен с первым входом блока 17 умножения. Второй вход блока 17 соединен с выходом интегратора 9. Выход блока 17 соединен с первым входом сумматора 18. Выход сумматора 18 соединен с входом нуль-органа 19. Выход нуль-органа 19 соединен с первым входом делителя 26 частоты. Второй вход делителя 26 соединен с выходом датчика 16, вторым входом управления интегратора 8, первым входом логического элемента ИЛИ 24 и первым входом триггера 22. Выход делителя 26 соединен с первым входом управляемого ключа 20 и вторым входом управляемого ключа 21. Второй вход управляемого ключа 20 соединен с первым выходом триггера 23. Выход управляемого ключа 20 соединен с вторым входом триггер 22. первый выход триггера 22 соединен с первым выходом устройства. Второй выход триггера 22 соединен с первым входом управляемого ключа 21. Третий вход управляемого ключа 21 соединен с вторым выходом триггера 23. Выход управляемого ключа 21 соединен с первым входом управления интегратора 12, первым входом блока 29 управления, вторым входом управления интегратора 11 и первым входом управления интегратора 10. Второй вход управления интегратора 10 соединен с выходом логического элемента ИЛИ 24 и третьим входом блока 29. Информационный вход интегратора 10 соединен с выходом источника 7 опорного напряжения, информационным входом интегратора 11, информационным входом интегратора 8 и информационным входом интегратора 9. Вход управления интегратора 9 соединен с выходом синхронизатора 2, первым входом логического элемента ИЛИ 25, первым входом делителя 28 частоты, вторым входом делителя 27 частоты и первым входом управления интегратора 8. Выход интегратора 8 соединен с первым входом компаратора 13. Второй вход компаратора 13 соединен через масштабный усилитель 15 с выходом интегратора 10, третьим входом запоминающего устройства 30 и первым входом компаратора 14. Второй вход компаратора 14 соединен с выходом интегратора 11. Выход компаратора 14 соединен с первым входом управления интегратора 11, вторым входом блока 29 и первым входом делителя 27. Выход делителя 27 соединен с четвертым входом блока 29, вторым входом управления интегратора 12 и вторым входом делителя 28. Выход делителя 28 соединен с вторым входом логического элемента ИЛИ 24, третьим входом управления интегратора 11 и вторым входом логического элемента ИЛИ 25. Выход логического элемента ИЛИ 25 соединен с первым входом триггера 23. Второй вход триггера 23 соединен с выходом компаратора 13. Первый выход блока 29 соединен с третьим входом управления интегратора 12. Второй выход блока 29 соединен с первым входом запоминающего устройства 30. Второй вход запоминающего устройства 30 соединен с выходом интегратора 12. Выход запоминающего устройства 30 соединен с вторым выходом устройства.

Устройство работает следующим образом. В момент времени t0 с выхода синхронизатора 2 поступает сигнал на вход источника 1 импульсного нагрева. Источник 1 запускается, при этом тепловой поток поступает на поверхность исследуемого образца 4. Одновременно сигнал с выхода синхронизатора 2 поступает на управляющие входы интеграторов 8 и 9, входы установки исходного состояния делителя 27, 28 и первый вход логического элемента ИЛИ 25.

Интеграторы 8 и 9 переводятся в режим интегрирования напряжения с выхода источника 7. Делители 27 и 28 устанавливаются в исходное (нулевое) состояние. Сигнал с выхода логического элемента ИЛИ 25 поступает на вход установки исходного состояния триггера 23. Триггер 23 устанавливается в исходное состояние. Исходному состоянию триггера 23 соответствует такое состояние, при котором на втором выходе триггера 23 сигнал отсутствует. Управляемый ключ 20 открыт сигналом с первого выхода триггера 23. Управляемый ключ 21 закрыт вследствие отсутствия сигнала на его третьем входе.

Температура поверхности образца 4 измеряется термопарой 3, сигнал с выхода которой усиливается усилителем 5 и поступает на вход дифференциатора 6, информационный вход интегратора 12 и второй вход сумматора 18. С выхода дифференциатора 6 сигнал, пропорциональный производной температуры T поверхности образца 4, поступает на первый вход блока 17. На второй вход блока 17 с выхода интегратора 9 поступает сигнал, величина которого пропорциональна интервалу времени, в течение которого интегратор 9 находится в режиме интегрирования.

Сигнал с выхода блока 17, пропорциональный произведению дифференциала сигнала на выходе усилителя 5 и сигнала, пропорционального интервалу времени с момента пуска устройства, поступает на вход сумматора 18. На второй вход сумматора 18 поступает сигнал с выхода усилителя 5. Сигнал с выхода сумматора 18, пропорциональный сумме сигналов на его входах, поступает на вход нуль-органа 19.

В момент времени окончания импульса нагрева срабатывает датчик 16. Сигнал с выхода датчика 16 поступает на входы установки исходного состояния триггера 22 и делителя 26, второй вход управления интегратора 8 и первый вход логического элемента ИЛИ 2. Триггер 22 и делитель 26 устанавливаются в исходное состояние. Исходному состоянию триггера 22 соответствует такое состояние, при котором сигнал на его первом выходе отсутствует. Исходному состоянию делителя 26, коэффициент деления которого KI=2, соответствует такое состояние, при котором делитель 26 срабатывает в момент поступления на его первый вход сигнала с выхода нуль-органа 19. Интегратор 8 переводится в режим хранения. Величина сигнала на выходе интегратора 8 пропорциональна длительности импульса нагрева.

С выхода логического элемента ИЛИ 24 сигнал поступает на третий вход блока 29 управления и второй вход управления интегратора 10. Блок 29 устанавливается в исходное состояние. Интегратор 10 переводится в режим интегрирования. Сигнал с выхода интегратора 10 поступает на вход масштабного усилителя 15, коэффициент усиления которого K=1/16. Сигнал с выхода масштабного усилителя 15 поступает на второй вход компаратора 13, на первый вход которого поступает сигнал с выхода интегратора 8.

При равенстве сигналов на входах срабатывает компаратор 13 и сигнал с его выхода перебрасывает триггер 23. Триггер 23 устанавливается в таком состоянии, при котором появляется сигнал на его втором выходе. Открывается управляемый ключ 21 закрывается управляемый ключ 20.

Если делитель 26 срабатывает ранее компаратора 13, сигнал с выхода делителя 26 через управляемый ключ 20 поступает на второй вход триггера 22. Триггер 22 перебрасывается в такое состояние, при котором появляется сигнал на его первом выходе. Управляемый ключ 21 закрывается, так как на его первом входе, соединенном с вторым выходом триггера 22, сигнал отсутствует, и определение характеристик образца 4 становится невозможным.

Если компаратор 13 срабатывает ранее делителя 26, сигнал с выхода компаратора 13 перебросит триггер 23 в такое состояние, при котором на его втором выходе появится сигнал, открывающий управляемый ключ 21. Управляемый ключ 20 закрывается, так как на первом выходе триггера 23 сигнал отсутствует. Сигнал с выхода делителя 26 через управляемый ключ 21 поступает на первые входы управления интеграторов 10 и 12, второй вход управления интегратора 11 и первый вход блока 29. Интегратор 10 переводится в режим хранения. Интеграторы 11 и 12 переводятся в режим интегрирования. Сигнал с второго выхода блока 29 поступает на первый вход запоминающего устройства 30. В запоминающее устройство 30 записывается величина сигнала, поступающего на третий вход запоминающего устройства 30 с выхода масштабного усилителя 15. Так как на информационные входы интеграторов 8-11 поступает сигнал с выхода источника 7 опорного напряжения, величины сигналов на выходах интеграторов 8-11 пропорциональны интервалам времени, в течение которых интеграторы 8-11 находятся в режиме интегрирования.

На первый вход компаратора 14 поступает сигнал с выхода масштабного усилителя 15. Величина этого сигнала пропорциональна интервалу времени  - интервал времени от момента срабатывания датчика 16 до момента поступления на первый вход интегратора 10 сигнала с выхода управляемого ключа 21. На второй вход компаратора 14 поступает сигнал с выхода интегратора 11. При равенстве сигналов на входах компаратор 14 срабатывает. На выходе компаратора 14 появляется сигнал, который поступает на первый вход делителя 27, коэффициент деления которого K2=3, второй вход блока 29 и первый вход управления интегратора 11. Интегратор 11 срабатывает в нулевое состояние, при этом режим интегрирования сохраняется. На втором выходе блока 29 появляется сигнал, который поступает на первый вход запоминающего устройства 30. В запоминающее устройство 30 записывается величина сигнала на выходе интегратора 12, пропорционального интегралу от сигнала на выходе усилителя 5 в интервале времени

- интервал времени от момента срабатывания датчика 16 до момента поступления на первый вход интегратора 10 сигнала с выхода управляемого ключа 21. На второй вход компаратора 14 поступает сигнал с выхода интегратора 11. При равенстве сигналов на входах компаратор 14 срабатывает. На выходе компаратора 14 появляется сигнал, который поступает на первый вход делителя 27, коэффициент деления которого K2=3, второй вход блока 29 и первый вход управления интегратора 11. Интегратор 11 срабатывает в нулевое состояние, при этом режим интегрирования сохраняется. На втором выходе блока 29 появляется сигнал, который поступает на первый вход запоминающего устройства 30. В запоминающее устройство 30 записывается величина сигнала на выходе интегратора 12, пропорционального интегралу от сигнала на выходе усилителя 5 в интервале времени  от момента поступления на первый вход управления интегратора 12 сигнала с выхода делителя 26.

от момента поступления на первый вход управления интегратора 12 сигнала с выхода делителя 26.

С первого выхода блока 29 сигнал поступает на второй вход управления интегратора 12, приводя его в нулевое состояние, при этом режим интегрирования интегратора 12 сохраняется.

После второго и третьего срабатываний компаратора 14 в запоминающее устройство 30 записываются величины сигналов с выхода интегратора 12, пропорциональные интегралам от сигнала на выходе усилителя 5, вычисленным в интервалах времени, равных  . Таким образом, в запоминающее устройство 30 после третьего срабатывания компаратора 14 записаны величины сигналов, пропорциональные интервалу времени

. Таким образом, в запоминающее устройство 30 после третьего срабатывания компаратора 14 записаны величины сигналов, пропорциональные интервалу времени  и трем последовательно вычисленным с одинаковым шагом, равным

и трем последовательно вычисленным с одинаковым шагом, равным  , интегралам от сигнала на выходе усилителя 5.

, интегралам от сигнала на выходе усилителя 5.

При поступлении на вход делителя 27 третьего сигнала с выхода компаратора 14 срабатывает делитель 27. С выхода делителя 27 сигнал поступает на третий вход управления интегратора 12, четвертый вход блока 29 и второй вход делителя 28, коэффициент деления которого K3=3. Интегратор 12 переводится в режим хранения, прекращается подача сигналов с выходов блока 29 на входы интегратора 12 и запоминающего устройства 30.

При поступлении на вход делителя 28 третьего сигнала с выхода делителя 27 срабатывает делитель 28. Сигнал с выхода делителя 28 поступает на третий вход управления интегратора 11, второй вход логического элемента ИЛИ 24 и второй вход логического элемента ИЛИ 25. Интегратор 11 переводится в режим хранения. С выхода логического элемента ИЛИ 25 сигнал поступает на первый вход триггера 23, устанавливая триггер 23 в исходное состояние, которому соответствует наличие сигнала на его первом выходе. С выхода логического элемента ИЛИ 24 сигнал поступает на второй вход интегратора 10, сбрасывая интегратор 10 в нулевое состояние, при этом устанавливается режим интегрирования интегратор 10. Одновременно сигнал с выхода логического элемента ИЛИ 24 поступает на третий вход блока 29, устанавливая блок 29 в исходное состояние.

Порядок работы устройства при втором и последующих циклах вычисления характеристик соответственно второго и последующих слоев материала образца 4 аналогичен описанному выше, начиная с момента срабатывания датчика 16.

На временных диаграммах (фиг. 2) изображено сверху вниз состояние выходов усилителя 5, сумматора 18, нуль-органа 19, делителя 26, датчика 16, интегратора 8 и масштабного усилителя 15, компаратора 13, первого выхода триггера 22, второго выхода триггера 22, первого выхода триггера 23, второго выхода триггера 23, компаратора 14, делителя 27, делителя 28.

Таким образом, при импульсном нагреве излучением от источника 1 импульсного нагрева поверхности непрозрачного или полупрозрачного для излучения нагрева многослойного образца 4 конечной толщины ,

,

где

n - количество слоев; Li - толщина i-го слоя; i=1,2,..n.

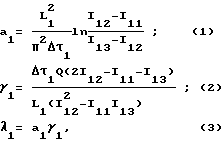

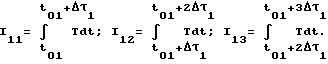

Через количество поглощенной энергии Q кусочным интегрированием температурной кривой T с заданным устройством постоянным шагом по времени Δτ1 , начиная с момента времени t01, теплофизические характеристики материала первого слоя образца 4 определяют по формулам: ,

,

где

a1, λ1 - коэффициенты температуропроводности и теплопроводности материала первого слоя образца 4 соответственно;

γ1 - объемная теплоемкость материала первого слоя образца 4; .

.

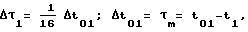

Определяемый самим устройством шаг интегрирования ,

,

где

t1 - момент времени окончания импульса нагрева;

t01 - момент времени, соответствующий равенству нулю функции F = T+2T′Δt на участке возрастания функции F (от минимума функции F до ее максимума).

За момент времени начала интегрирования принят момент времени, при котором F=0, так как момент времени начала регуляризации температурного режима совпадает с моментом времени достижения минимума функцией Φ = T2Δt , где Δt - интервал времени от момента времени запуска источника 1 до текущего момента времени Δt = t-t0 [5], а минимуму функции Φ соответствует равенство нулю первой производной по времени

Φ′ = T(T+2T′Δt). .

Если величина Δτ1 меньше длительности τи импульса нагрева Δτ1≤ τи , вычисление I11, I12, I13 и теплофизических характеристик материалов образца 4 не производится вследствие невозможности оценки погрешности определения теплофизических характеристик.

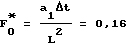

Если величина Δτ1 больше длительности τи импульса нагрева Δτ1>τи , то устройством производится вычисление величины интегралов I11, I12, I13 и определяется момент времени t2 начала цикла вычислений. Так как шаг интегрирования Δτ1 выбран равным  , а момент времени начала интегрирования, совпадающий с началом регуляризации температурного режима, соответствует [1, 5]:

, а момент времени начала интегрирования, совпадающий с началом регуляризации температурного режима, соответствует [1, 5]: ,

,

шаг интегрирования Δτ1 соответствует F0=0,01.

Учитывая, что влияние материала второго слоя образца 4 на температурный режим начинается при F0=0,25 [1, 5], длительности интервала времени Δ t0= t2-t01 соответствует ΔF0= F0-F

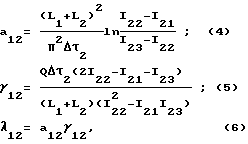

Эффективные теплофизические характеристики материалов первого и второго слоев совместно определяют по формулам: ,

,

где

a12 - коэффициент эффективной температуропроводнисти материалов первого и второго слоев образца 4;

γ12 - объемная эффективная теплоемкость материалов первого и второго слоев образца 4;

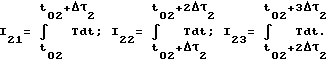

λ12 - коэффициент эффективной теплопроводности материалов первого и второго слоев образца 4; .

.

Определяемый устройством шаг интегрирования во втором цикле вычислений ,

,

где

t02 - момент времени, соответствующий равенству нулю функции F=T+2T' Δ t на участке возрастания функции F (от минимума функции F до ее максимума) во втором цикле вычислений теплофизических характеристик.

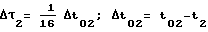

Теплофизические характеристики материала второго слоя образца 4 определяют по формулам: ,

,

где ;

;

a2 - коэффициент температуропроводности материала второго слоя образца 4;

γ2 - объемная теплоемкость материала второго слоя;

λ2- коэффициент теплопроводности материала второго слоя;

Теплофизические характеристики материалов третьего и последующих слоев образца 4 определяют аналогичным образом, используя теплофизические характеристики материалов трех слоев образца 4, для которых они определены.

Вычисления по формулам (1)-(9) и им подобным (для второго и третьего слоев совместно, третьего слоя и т.д.) не представляют сложности и реализуются стандартными алгоритмами.

Если в i-ом цикле вычислений определяемая устройством величина ,

,

меньше длительности τи импульса нагрева Δτi<τи , то вычисление теплофизических характеристик материалов i-го и последующих слоев образца 4 не производится вследствие невозможности оценки погрешности определения теплофизических характеристик.

Таким образом, устройство обладает расширенными функциональными возможностями, позволяющими определять теплофизические характеристики материалов многослойных объектов при одностороннем доступе.

Источники информации

1. Блохин С. П. и др. Определение отношения тепловых активностей слоев двухслойной системы бесконтактным методом. - В сб. "Теплофизика ядерно-энергетических установок". М.: Энергоатомиздат, 1986, с. 20-24.

2. Balageas D.L, Kraper J.C, Cielo P. Pulsed photothermal modelling of layered materials.- J.Appl.Phys, 1986, v. 59, N 2.

3. А.с. СССР N 1557499, G 01 N 25/18, 1990.

4. А.с. СССР N 1755150, G 01 N 25/18, 1992.

5. Троицкий О.Ю. Импульсный тепловой неразрушающий контроль слоистых материалов. - Механика композитных материалов, 1992, N 4, с. 534-538.

Использование: относится к техническим средствам для определения теплофизических характеристик и может использоваться при исследовании свойств новых материалов и в тепловом неразрушающем контроле. Сущность: устройство содержит источник 1 импульсного нагрева, синхронизатор 2, термопару 3, измеряющую температуру поверхности образца. Термопара подключена через усилитель 5 к входу дифференциатора 6. На выходе интеграторов 8-12 формируются сигналы, пропорциональные длительности импульса нагрева, интервалам времени с момента запуска устройства и от момента окончания импульса нагрева до момента начала интегрирования. Логика работы устройства обеспечивается управляемыми ключами 20,21, триггерами 22,23, логическими элементами ИЛИ 24,25, делителями частоты 26-28. Величина сигналов, пропорциональных вычисленным интегралом и шагу интегрирования, фиксируется запоминающим устройством 30. Установка начальных условий в каждом цикле вычислений и управление работой устройства осуществляется с помощью блока управления 29. Устройство позволяет определять теплофизические характеристики материалов однослойных и многослойных объектов при одностороннем доступе. 2 ил.

Устройство для определения характеристик материалов, содержащее источник импульсного нагрева, вход которого через синхронизатор соединен с пусковой клеммой, термопару, подключенную через усилитель к входу дифференциатора, два компаратора, пять интеграторов и источник опорного напряжения, при этом первый вход управления первого интегратора и вход управления второго интегратора соединены с выходом синхронизатора, информационные входы с первого по четвертый интеграторов соединены с выходом источника опорного напряжения, информационный вход пятого интегратора соединен с выходом усилителя, выход первого интегратора соединен с первым входом первого компаратора, второй вход которого соединен через масштабный усилитель с выходом третьего интегратора, выход масштабного усилителя соединен с первым входом второго компаратора, второй вход которого соединен с выходом четвертого интегратора, а выход соединен с первым входом управления четвертого интегратора, отличающееся тем, что оно дополнительно содержит датчик длительности импульса нагрева, сумматор, блок умножения, нуль-орган, три делителя частоты, два триггера, два управляемых ключа, два логических элемента ИЛИ, запоминающее устройство и блок управления, при этом выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с первым входом сумматора, второй вход которого соединен с выходом усилителя, а выход соединен с входом нуль-органа, выход которого соединен с первым входом первого делителя частоты, второй вход которого соединен с выходом датчика длительности импульса нагрева, вторым входом управления первого интегратора, первым входом первого логического элемента ИЛИ и первым входом первого триггера, а выход соединен с первым входом первого управляемого ключа, второй вход которого соединен с первым выходом второго триггера, а выход соединен с вторым входом первого триггера, первый выход которого является первым выходом устройства, а второй выход соединен с первым входом второго управляемого ключа, второй и третий входы которого соединены с выходом первого делителя частоты и вторым выходом второго триггера соответственно, а выход соединен с первыми входами управления третьего и пятого интеграторов, вторым входом управления четвертого интегратора и первым входом блока управления, второй вход которого соединен с выходом второго компаратора и первым входом второго делителя частоты, второй вход которого соединен с первым входом третьего делителя частоты, выходом синхронизатора и первым входом второго логического элемента ИЛИ, второй вход которого соединен с выходом третьего делителя частоты, третьим входом управления четвертого интегратора и вторым входом первого логического элемента ИЛИ, а выход соединен с первым входом второго триггера, второй вход которого соединен с выходом первого компаратора, выход первого логического элемента ИЛИ соединен с вторым входом управления третьего интегратора и третьим входом блока управления, четвертый вход которого соединен с выходом второго делителя частоты, вторым входом управления пятого интегратора и вторым входом третьего делителя частоты, первый выход блока управления соединен с третьим входом управления пятого интегратора, второй выход блока управления соединен с первым входом запоминающего устройства, второй и третий входы которого соединены с выходом пятого интегратора и выходом масштабного усилителя соответственно, а выход является вторым выходом устройства.

| SU, авторское свидетельство, 1557499, G 01 N 25/18, 1990 | |||

| SU, авторское свидетельство, 1755150, G 01 N 25/18, 1992. |

Авторы

Даты

1998-04-10—Публикация

1996-08-12—Подача