Текст описания в факсимильном виде (см. графическую часть). Т

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2013 |

|

RU2544312C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2009 |

|

RU2392612C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК | 1997 |

|

RU2132548C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2006 |

|

RU2307344C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2001 |

|

RU2184955C1 |

| Тензометрическое устройство | 1991 |

|

SU1796890A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИНХРОННОЙ МАШИНЫ | 1990 |

|

RU2018953C1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Устройство для определения параметров динамического звена | 1983 |

|

SU1160372A1 |

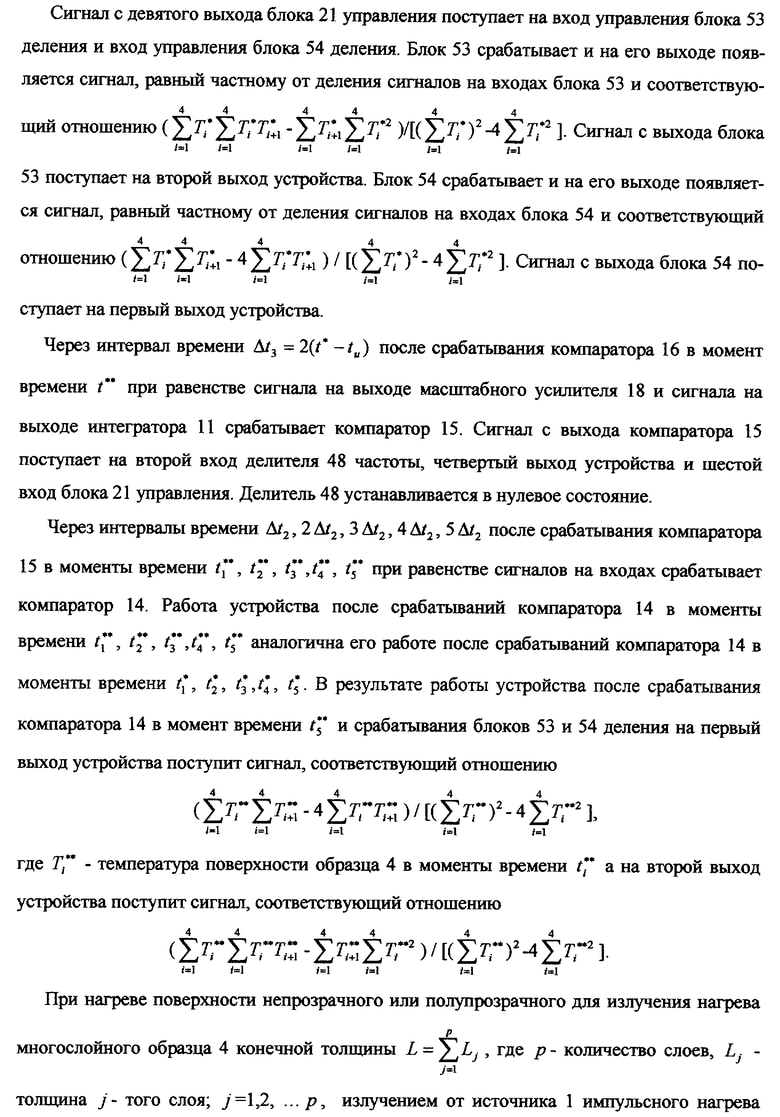

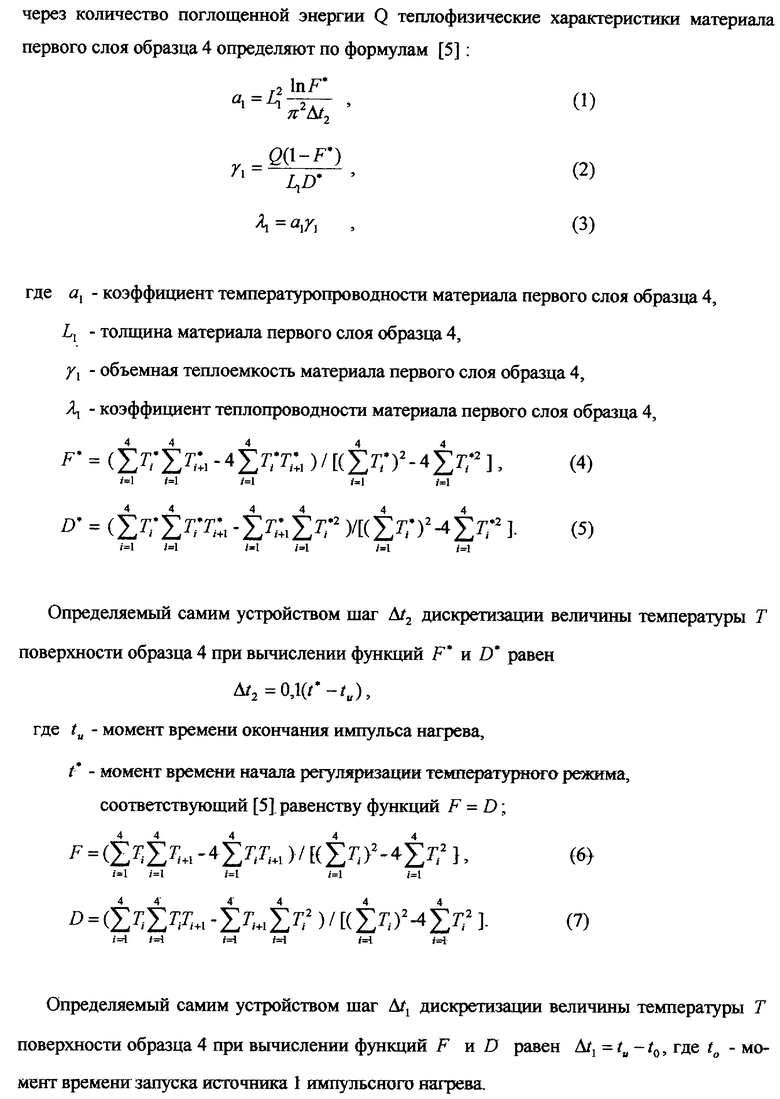

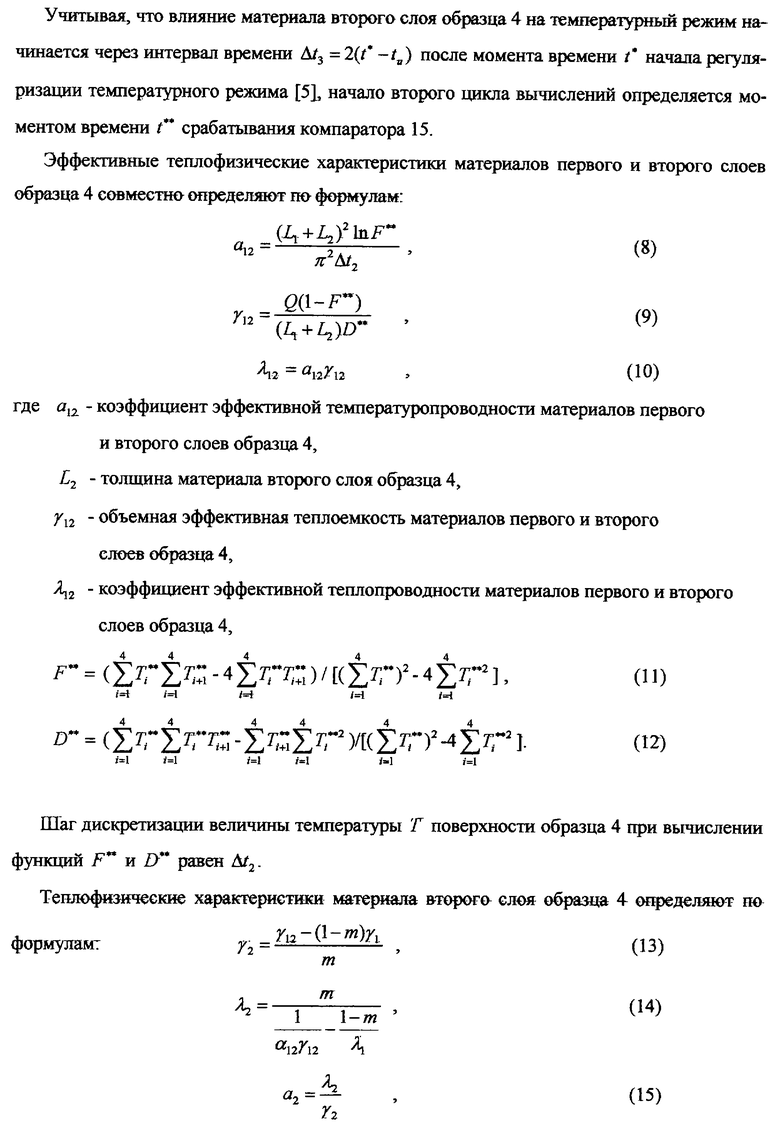

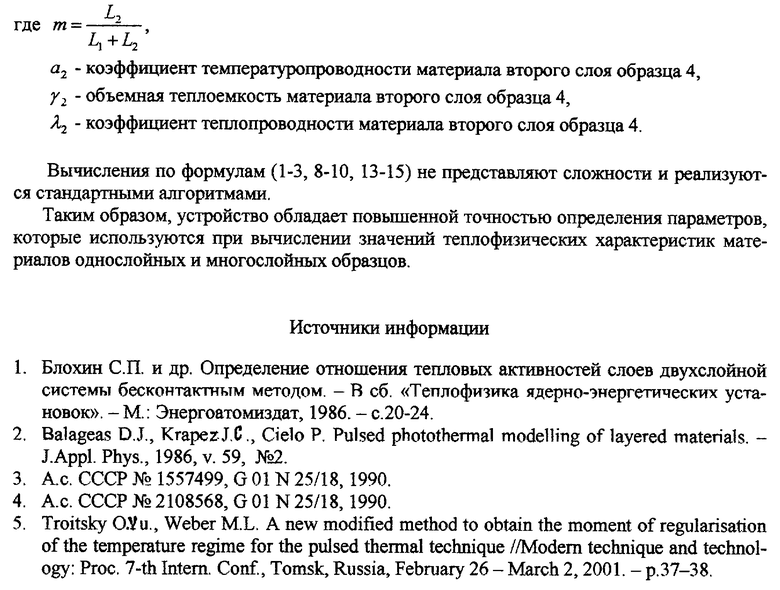

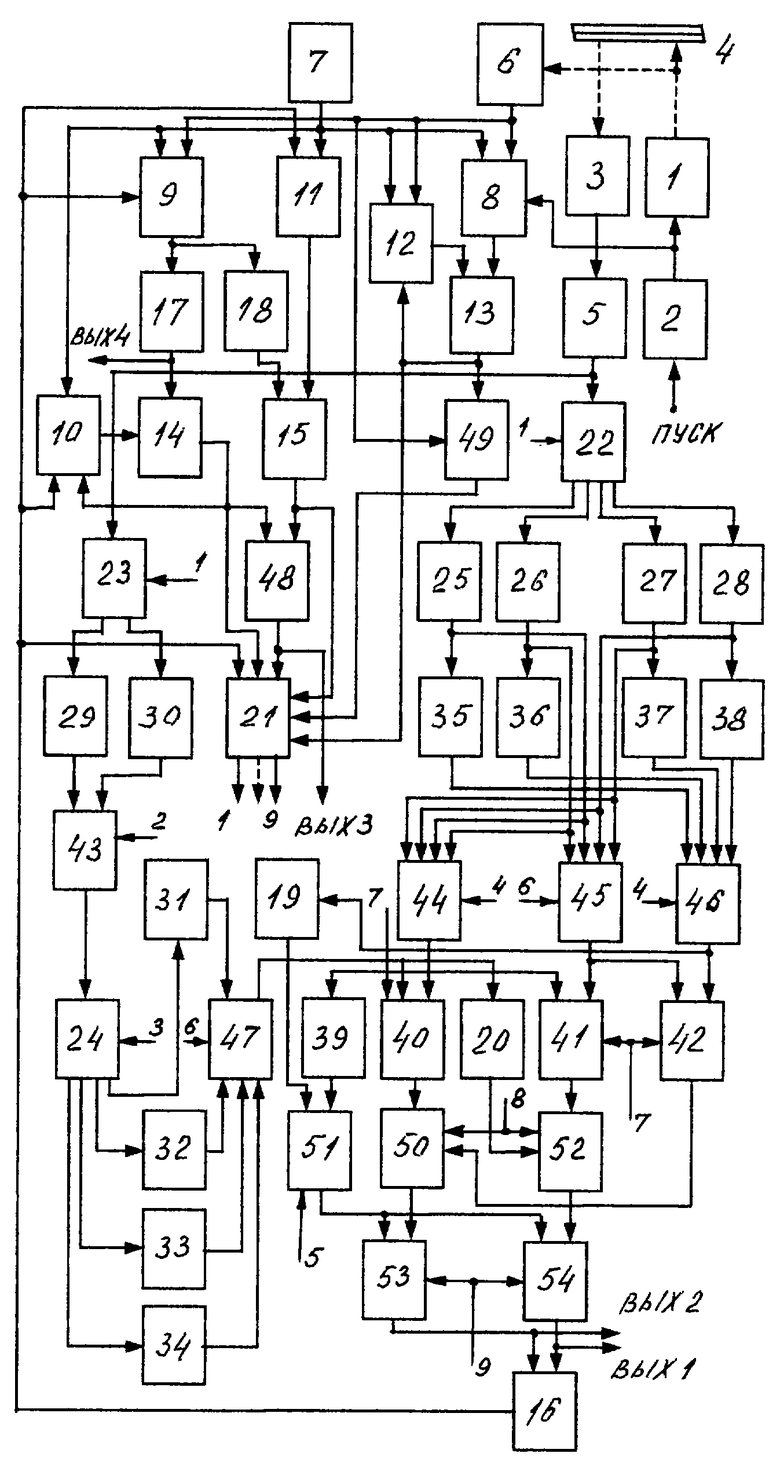

Устройство относится к техническим средствам для определения теплофизических характеристик твердых материалов. Устройство содержит источник импульсного нагрева, синхронизатор, термопару, измеряющую температуру поверхности образца. Термопара подключена через усилитель к входам коммутаторов. На выходах интеграторов формируются сигналы, величины которых пропорциональны длительности импульса нагрева, интервалам времени от срабатывания датчика до срабатывания компаратора, а также шагу дискретизации величины температуры поверхности образца. Логика работы устройства обеспечивается компараторами, коммутаторами и делителями частоты. Установка начальных условий в каждом цикле вычислений и управление работой блоков умножения, сумматоров, блоков вычитания и блоков деления осуществляется блоком управления. Устройство позволяет определять характеристики однослойных и многослойных объектов при одностороннем доступе. 1 ил.

Устройство для определения характеристик материалов, содержащее источник импульсного нагрева, вход которого через синхронизатор соединен с пусковой клеммой, термопару, подключенную к входу усилителя, два компаратора, пять интеграторов, масштабный усилитель, датчик длительности импульса нагрева, блок умножения, сумматор, два делителя частоты, запоминающее устройство, блок управления и источник опорного напряжения, при этом выход синхронизатора соединен с первым входом управления первого интегратора, второй вход управления которого соединен с выходом датчика длительности импульса нагрева, а выход соединен с первым входом первого компаратора, информационные входы с первого по четвертый интеграторов соединены с выходом источника опорного напряжения, выход второго интегратора соединен через первый масштабный усилитель с первым входом второго компаратора, второй вход которого соединен с выходом третьего интегратора, а выход соединен с первым входом управления третьего интегратора и первым входом первого делителя частоты, выход которого соединен с первым входом блока управления, второй вход которого соединен с выходом второго компаратора, отличающееся тем, что оно дополнительно содержит два компаратора, три масштабных усилителя, три блока умножения, три сумматора, девять запоминающих устройств, три коммутатора, пять квадраторов, три блока вычитания и два блока деления, при этом первый вход управления пятого интегратора соединен с выходом датчика длительности импульса нагрева, первым входом управления второго интегратора и первым входом второго делителя частоты, второй вход которого соединен с выходом первого компаратора, вторым входом управления пятого интегратора и третьим входом блока управления, а выход соединен с четвертым входом блока управления, пятый вход которого соединен с вторым входом первого делителя частоты и выходом третьего компаратора, первый вход которого соединен с выходом четвертого интегратора, а второй вход соединен через второй масштабный усилитель с выходом второго интегратора, выход усилителя соединен с входом первого коммутатора, первый выход которого соединен с входом первого запоминающего устройства, выход которого соединен с первым входом первого сумматора, первым входом второго сумматора и входом первого квадратора, выход которого соединен с первым входом третьего сумматора, второй вход которого соединен с выходом второго квадратора, вход которого соединен с вторым входом первого сумматора, вторым входом второго сумматора и выходом второго запоминающего устройства, вход которого соединен с вторым выходом первого коммутатора, третий выход которого соединен с входом третьего запоминающего устройства, выход которого соединен с третьим входом первого сумматора, третьим входом второго сумматора и входом третьего квадратора, выход которого соединен с третьим входом третьего сумматора, четвертый вход которого соединен с выходом четвертого квадратора, вход которого соединен с четвертым входом первого сумматора, четвертым входом второго сумматора и выходом четвертого запоминающего устройства, вход которого соединен с четвертым выходом первого коммутатора, выход первого сумматора соединен с входом пятого квадратора, первым входом первого блока умножения и первым входом второго блока умножения, второй вход которого соединен с выходом второго сумматора и первым входом третьего блока умножения, второй вход которого соединен с входом третьего масштабного усилителя и выходом третьего сумматора, а выход соединен с первым входом первого блока вычитания, второй вход которого соединен с выходом первого блока умножения, а выход соединен с первым входом первого блока деления, второй вход которого соединен с выходом второго блока вычитания и первым входом второго блока деления, второй вход которого соединен с выходом третьего блока вычитания, а выход соединен с первым выходом устройства и первым входом четвертого компаратора, второй вход которого соединен с выходом первого блока деления и вторым выходом устройства, а выход соединен с вторым входом управления второго интегратора, вторым входом управления третьего интегратора, входом управления четвертого интегратора и шестым входом блока управления, выход усилителя соединен с входом второго коммутатора, первый выход которого соединен с входом пятого запоминающего устройства, а второй выход соединен с входом шестого запоминающего устройства, выход которого соединен с первым входом четвертого блока умножения, второй вход которого соединен с выходом пятого запоминающего устройства, а выход соединен с входом третьего коммутатора, первый выход которого соединен с входом седьмого запоминающего устройства, выход которого соединен с первым входом четвертого сумматора, второй вход которого соединен с выходом восьмого запоминающего устройства, вход которого соединен с вторым выходом третьего коммутатора, третий выход которого соединен с входом девятого запоминающего устройства, а четвертый выход соединен с входом десятого запоминающего устройства, выход которого соединен с третьим входом четвертого сумматора, четвертый вход которого соединен с выходом девятого запоминающего устройства, а выход соединен с вторым входом первого блока умножения и входом четвертого масштабного усилителя, выход которого соединен с первым входом третьего блока вычитания, второй вход которого соединен с выходом второго блока умножения, выход пятого интегратора соединен с вторым входом первого компаратора, выход третьего масштабного усилителя соединен с первым входом второго блока вычитания, второй вход которого соединен с выходом пятого квадратора, первый выход блока управления соединен с входом управления первого коммутатора и входом управления второго коммутатора, второй выход блока управления соединен с входом управления четвертого блока умножения, третий выход блока управления соединен с входом управления третьего коммутатора, четвертый выход блока управления соединен с входом управления первого сумматора и входом управления третьего сумматора, пятый выход блока управления соединен с входом управления второго блока вычитания, шестой выход блока управления соединен с входом управления второго сумматора и входом управления четвертого сумматора, седьмой выход блока управления соединен с входом управления первого блока умножения, второго блока умножения и третьего блока умножения, восьмой выход блока управления соединен с входом управления первого блока вычитания и входом управления третьего блока вычитания, девятый выход блока управления соединен с входом управления первого блока деления и входом управления второго блока деления, выход первого делителя частоты соединен с третьим выходом устройства, выход первого масштабного усилителя соединен с четвертым выходом устройства.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| УСТРОЙСТВО ДЛЯ КОМПЛЕКСНОГО ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК ТВЕРДЫХ МАТЕРИАЛОВ | 1998 |

|

RU2154268C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК | 1997 |

|

RU2132548C1 |

| SU 1660472 A1, 27.01.2000. | |||

Авторы

Даты

2003-09-20—Публикация

2002-05-28—Подача