Изобретение относится к техническим средствам для определения характеристик материалов и может использоваться как при исследовании свойств новых материалов, так и в тепловом неразрушающем контроле.

Известно устройство [1. А. с. СССР №1265562, G01N 25/18, 1986], реализующее способ определения теплофизических свойств твердых материалов. Устройство [1] имеет невысокую точность и низкую помехозащищенность, так как теплофизические характеристики материалов определяют на основании данных о характерной точке первой производной температурной кривой, расстоянии от точки нагрева до точки измерения температуры и мощности импульса излучения нагрева.

Известно устройство для определения теплофизических параметров материалов [2. А. с. СССР №1557499, G01N 25/18, 1990]. Устройство [2] имеет невысокую точность вследствие определения теплофизических характеристик материалов на основании определения характерной точки по второй производной температурной кривой. Невысока также точность устройства, так как при интегрировании температурной кривой с момента подачи импульса нагрева (без учета длительности этого импульса) большое влияние на точность измерения оказывают помехи на начальном участке температурной кривой.

Известно устройство для прецизионного определения характеристик материалов [3. А. с. СССР №1755150, G01N 25/18, 1992]. Устройство [3] определяет момент времени начала регуляризации режима нагрева образца на основании анализа второй производной температурной кривой, что снижает точность определения этого момента. Кроме того, при одностороннем доступе к объекту анализа температурная кривая не имеет точки перегиба, что не дает возможности определить с помощью известного устройства момент времени начала регуляризации режима нагрева, а это, в свою очередь, уменьшает функциональные возможности устройства в определенных условиях (известное устройство может применяться в лабораторных условиях и на объектах с возможностью двухстороннего доступа).

Известны устройства для определения характеристик материалов [4. Патент РФ №2154268, G01N 25/18, 2000. 5. Патент РФ №2184955, G01N 25/18, 2002], определяющие теплофизические характеристики материалов с помощью двухстороннего импульсного теплового метода, что уменьшает функциональные возможности известных устройств [4, 5] и не позволяет использовать их для определения характеристик материалов изделий с возможностью одностороннего доступа.

Известно устройство для определения теплофизических характеристик [6. Патент РФ №2132548, G01N 25/18, 1999]. Устройство [6] имеет невысокую точность, так как критерий, с помощью которого определяется момент времени начала регуляризации температурного режима материала образца, основан на использовании эмпирической зависимости, применение которой приводит к погрешности определения момента времени начала регуляризации температурного режима, превышающей 5% вследствие асимптотического поведения первой производной выбранной функции в области нулевого значения. Определение величин одинаковых интервалов времени, в течение которых производится интегрирование величины измеряемой температуры известным устройством [6], производится с помощью трех различных измерительных каналов, что также приводит к увеличению погрешности устройства.

Известно устройство для определения характеристик материалов [7. Патент РФ №2307344, G01N 25/18, 2007], наиболее близкое по структуре к заявляемому устройству, содержащее источник импульсного нагрева, термопару, подключенную через усилитель к входу дифференциатора, пять интеграторов, компаратор, масштабный усилитель, датчик длительности импульса нагрева, блок деления, вход делителя которого соединен с выходом усилителя, блок умножения, экстрематор, переключатель, два делителя частоты, два блока памяти и источник опорного напряжения, при этом первый вход управления первого интегратора соединен с выходом компаратора, а информационные входы первого и второго интеграторов - с выходом источника опорного напряжения, причем выходы масштабного усилителя, третьего, четвертого и пятого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно, выход второго интегратора соединен с входом масштабного усилителя, выход которого соединен с первым входом компаратора, второй вход которого соединен с выходом первого интегратора, выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с входом делимого блока деления, выход которого соединен с входом экстрематора, выход которого соединен с вторым входом управления первого интегратора и первыми входами управления второго, третьего, четвертого и пятого интеграторов и первым входом управления переключателя, второй вход управления которого соединен с выходом компаратора и входом первого делителя частоты, третий вход управления переключателя соединен с выходом датчика длительности импульса нагрева, третьим входом управления первого интегратора, вторым входом управления второго интегратора и входом управления первого блока памяти, выход которого является пятым выходом устройства, а информационный вход соединен с выходом усилителя, информационными входами второго блока памяти и переключателя, первый выход которого соединен с информационным входом третьего интегратора, второй выход переключателя соединен с информационным входом четвертого интегратора, третий выход переключателя соединен с информационным входом пятого интегратора, второй вход управления которого соединен с вторыми входами управления третьего и четвертого интеграторов, выходом первого делителя частоты и входом второго делителя частоты, выход которого соединен с входом управления второго блока памяти, выход которого является шестым выходом устройства, вход источника импульсного нагрева соединен с пусковой клеммой.

Известное устройство [7] имеет ограниченные функциональные возможности, не позволяющие определять величины продольных по отношению к поверхности составляющих теплофизических характеристик анизотропных материалов.

Задачей изобретения является расширение функциональных возможностей устройства для определения характеристик материалов.

Для решения задачи изобретения в устройство, содержащее источник импульсного нагрева, термопару, подключенную через усилитель к входу дифференциатора, пять интеграторов, компаратор, масштабный усилитель, датчик длительности импульса нагрева, блок деления, вход делителя которого соединен с выходом усилителя, блок умножения, экстрематор, переключатель, два делителя частоты и два блока памяти, источник опорного напряжения, при этом первый вход управления первого интегратора соединен с выходом компаратора, а информационные входы первого и второго интеграторов - с выходом источника опорного напряжения, причем выходы масштабного усилителя, третьего, четвертого и пятого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно, выход второго интегратора соединен с входом масштабного усилителя, выход которого соединен с первым входом компаратора, второй вход которого соединен с выходом первого интегратора, выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с входом делимого блока деления, выход которого соединен с входом экстрематора, выход которого соединен с вторым входом управления первого интегратора, первыми входами управления второго, третьего, четвертого и пятого интеграторов и первым входом управления переключателя, второй вход управления которого соединен с выходом компаратора и входом первого делителя частоты, третий вход управления переключателя соединен с выходом датчика длительности импульса нагрева, третьим входом управления первого интегратора, вторым входом управления второго интегратора и входом управления первого блока памяти, выход которого является пятым выходом устройства, а информационный вход соединен с выходом усилителя, информационными входами второго блока памяти и переключателя, первый выход которого соединен с информационным входом третьего интегратора, второй выход переключателя соединен с информационным входом четвертого интегратора, третий выход переключателя соединен с информационным входом пятого интегратора, второй вход управления которого соединен с вторыми входами управления третьего и четвертого интеграторов, выходом первого делителя частоты и входом второго делителя частоты, выход которого соединен с входом управления второго блока памяти, выход которого является шестым выходом устройства, вход источника импульсного нагрева соединен с пусковой клеммой, дополнительно введены три термопары, три усилителя, четыре компаратора, два блока памяти, два интегратора, три блока вычитания, два сумматора, три масштабных усилителя и два блока деления, при этом выходы второй, третьей и четвертой термопар соединены через второй, третий и четвертый усилители с первыми входами второго, третьего и четвертого компараторов соответственно, выход второго компаратора соединен с первым входом управления шестого интегратора, второй вход управления которого соединен с выходом третьего компаратора, третий вход управления шестого интегратора соединен с первым входом управления седьмого интегратора, пусковой клеммой, входом управления третьего блока памяти и первым входом управления четвертого блока памяти, информационный вход шестого интегратора соединен с выходом источника опорного напряжения и информационным входом седьмого интегратора, второй вход управления которого соединен с вторым входом управления четвертого блока памяти и выходом четвертого компаратора, а выход соединен с первым входом пятого компаратора, второй вход которого соединен с выходом шестого интегратора и входом делителя второго блока деления, а выход соединен с входом управления третьего блока деления, вход делимого которого соединен с выходом второго блока деления, вход делителя третьего блока деления соединен с выходом первого сумматора, а выход является седьмым выходом устройства, выход второго усилителя соединен с первым входом второго сумматора и первым входом первого блока вычитания, второй вход которого соединен с вторым входом второго сумматора и выходом четвертого усилителя, а выход соединен с входом второго масштабного усилителя, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом третьего масштабного усилителя, вход которого соединен с выходом второго блока вычитания, первый вход которого соединен с выходом второго сумматора, а второй вход соединен с выходом четвертого масштабного усилителя, вход которого соединен с первым входом третьего блока вычитания, информационным входом четвертого блока памяти и первым входом третьего компаратора, второй вход которого соединен с вторыми входами второго и четвертого компараторов и выходом третьего блока памяти, информационный вход которого соединен с выходом первого усилителя, выход четвертого блока памяти соединен с вторым входом третьего блока вычитания, выход которого соединен с входом делимого второго блока деления.

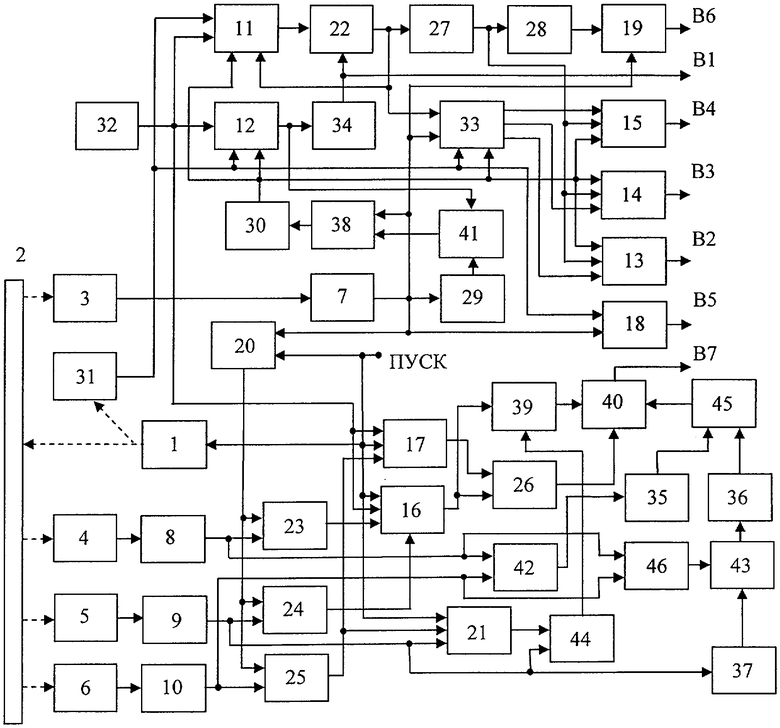

На чертеже изображена схема устройства.

Устройство содержит источник 1 импульсного нагрева, термопары 3-6, измеряющие температуру поверхности образца 2, усилители 7-10, интеграторы 11-17, блоки 18-21 памяти, компараторы 22-26, делители 27, 28 частоты, дифференциатор 29, экстрематор 30, датчик 31 длительности импульса нагрева, источник 32 опорного напряжения, переключатель 33, масштабные усилители 34-37, блоки 38-40 деления, блок 41 умножения, блоки 42-44 вычитания, сумматоры 45, 46.

Источник 1 импульсного нагрева оптически связан с датчиком 31 и образцом 2. Первая термопара 3 расположена на поверхности образца 2 в центре пятна нагрева, имеющего радиус r0. Вторая 4, третья 5 и четвертая 6 термопары расположены в точках i-1, i, i+1 на поверхности образца 2 на прямой, проходящей через центр пятна нагрева, на расстояниях ri-1, ri, ri+1 от центра пятна нагрева соответственно; ri-1>r0,

ri-ri-1=ri+1-ri=Δr. Величины зон нечувствительности компараторов 23-25 одинаковы и превышают максимальное значение погрешности измерения температуры поверхности образца 2 термопарами 4-6.

Вход источника 1 импульсного нагрева соединен с пусковой клеммой. Первая термопара 3 соединена с входом первого усилителя 7. Выход первого усилителя 7 соединен с входом дифференциатора 29, входом делителя первого блока деления 38 и информационными входами переключателя 33, первого 18, второго 19 и третьего 20 блоков памяти. Первый вход управления первого интегратора 11 соединен с выходом первого компаратора 22, вторым входом управления переключателя 33 и входом первого делителя 27 частоты. Информационные входы первого 11, второго 12, шестого 16 и седьмого 17 интеграторов соединены с выходом источника 32 опорного напряжения. Выход второго интегратора 12 соединен с входом первого масштабного усилителя 34 и вторым входом блока умножения 41. Выход дифференциатора 29 соединен с первым входом блока умножения 41. Выход блока умножения 41 соединен с входом делимого первого блока деления 38. Выход первого блока деления 38 соединен с входом экстрематора 30. Выход экстрематора 30 соединен с вторым входом управления первого интегратора 11, первыми входами управления второго 12, третьего 13, четвертого 14 и пятого 15 интеграторов и первым входом управления переключателя 33. Выход датчика 31 соединен с третьим входом управления первого интегратора 11, вторым входом управления второго интегратора 12, входом управления первого блока памяти 18 и третьим входом управления переключателя 33. Первый выход переключателя 33 соединен с информационным входом третьего интегратора 13, второй выход переключателя 33 соединен с информационным входом четвертого интегратора 14, третий выход переключателя 33 соединен с информационным входом пятого интегратора 15. Выход первого масштабного усилителя 34 соединен с первым входом первого компаратора 22 и первым В1 выходом устройства. Выход первого интегратора 11 соединен с вторым входом первого компаратора 22. Выход первого делителя частоты 27 соединен с вторыми входами управления третьего 13, четвертого 14 и пятого 15 интеграторов и входом второго делителя 28 частоты. Выход второго делителя 28 частоты соединен с входом управления второго блока памяти 19. Выходы третьего 13, четвертого 14 и пятого 15 интеграторов соединены с вторым В2, третьим В3 и четвертым В4 выходами устройства соответственно. Выходы первого 18 и второго 19 блоков памяти соединены с пятым В5 и шестым В6 выходами устройства соответственно. Вторая термопара 4 соединена с входом второго усилителя 8. Выход второго усилителя 8 соединен с первым входом второго компаратора 23, первым входом первого блока вычитания 42 и первым входом второго сумматора 46. Третья термопара 5 соединена с входом третьего усилителя 9. Выход третьего усилителя 9 соединен с первым входом третьего компаратора 24, информационным входом четвертого блока памяти 21, первым входом третьего блока вычитания 44 и входом четвертого масштабного усилителя 37. Четвертая термопара 6 соединена с входом четвертого усилителя 10. Выход четвертого усилителя 10 соединен с первым входом четвертого компаратора 25, вторым входом первого блока вычитания 42 и вторым входом второго сумматора 46. Выход второго компаратора 23 соединен с первым входом управления шестого интегратора 16. Выход третьего компаратора 24 соединен с вторым входом управления шестого интегратора 16. Выход четвертого компаратора 25 соединен с вторым входом управления седьмого интегратора 17 и вторым входом управления четвертого блока памяти 21. Первый вход управления четвертого блока памяти 21 соединен с третьим входом управления шестого интегратора 16, первым входом управления седьмого интегратора 17, входом управления третьего блока памяти 20 и пусковой клеммой. Выход третьего блока памяти 20 соединен с вторыми входами второго 23, третьего 24 и четвертого 25 компараторов. Выход шестого интегратора 16 соединен с входом делителя второго блока деления 39 и вторым входом пятого компаратора 26. Выход седьмого интегратора 17 соединен с первым входом пятого компаратора 26. Выход пятого компаратора 26 соединен с входом управления третьего блока деления 40. Выход первого блока вычитания 42 соединен с входом второго масштабного усилителя 35. Выход второго масштабного усилителя 35 соединен с первым входом первого сумматора 45. Выход четвертого блока памяти 21 соединен с вторым входом третьего блока вычитания 44. Выход третьего блока вычитания 44 соединен с входом делимого второго блока деления 39. Выход второго блока деления 39 соединен с входом делимого третьего блока деления 40. Выход второго сумматора 46 соединен с первым входом второго блока вычитания 43. Выход четвертого масштабного усилителя 37 соединен с вторым входом второго блока вычитания 43. Выход второго блока вычитания 43 соединен с входом третьего масштабного усилителя 36. Выход третьего масштабного усилителя 36 соединен с вторым входом первого сумматора 45. Выход первого сумматора 45 соединен с входом делителя третьего блока деления 40. Выход третьего блока деления 40 соединен с седьмым В7 выходом устройства.

Устройство работает следующим образом.

При пуске устройства сигнал поступает на вход источника 1 импульсного нагрева. Источник 1 запускается, при этом тепловой поток от источника 1 поступает на поверхность образца 2 и вход датчика 31. Температура поверхности образца 2 в центре пятна нагрева измеряется первой термопарой 3, сигнал с выхода которой усиливается первым усилителем 7 и поступает на информационные входы первого 18 и второго 19 блоков памяти, переключателя 33, вход делителя первого блока 38 деления и вход дифференциатора 29.

При срабатывании в момент времени tu датчика 31 сигнал с его выхода поступает на третий вход управления первого интегратора 11, второй вход управления второго интегратора 12, третий вход управления переключателя 33 и вход управления первого блока 18 памяти. Первый 11 и второй 12 интеграторы, переключатель 33 и первый блок 18 памяти устанавливаются в исходное состояние. Исходному состоянию первого интегратора 11 соответствует такое состояние, при котором первый интегратор 11 находится в режиме хранения и на его выходе сигнал отсутствует (нулевое состояние). Исходному состоянию второго интегратора 12 соответствует такое состояние, при котором второй интегратор 12 находится в режиме интегрирования и на его выходе сигнал отсутствует. Исходному состоянию переключателя 33 соответствует такое состояние, при котором информационный вход переключателя 33 отключен от его первого, второго и третьего выходов. Исходному состоянию первого блока 18 памяти соответствует режим записи величины сигнала, поступающего на информационный вход первого блока 18 памяти с выхода первого усилителя 7. В первый блок 18 памяти записывается значение сигнала на выходе первого усилителя 7, соответствующее величине Tu температуры поверхности образца 2 в центре пятна нагрева в момент времени tu. С выхода первого блока 18 памяти сигнал, соответствующий величине Tu температуры поверхности образца 2 в центре пятна нагрева в момент времени tu, поступает на пятый В5 выход устройства. С выхода дифференциатора 29 сигнал, пропорциональный первой производной T' температуры T поверхности образца 2 в центре пятна нагрева, поступает на первый вход блока 41 умножения. На второй вход блока 41 умножения поступает с выхода второго интегратора 12 сигнал, величина которого пропорциональна интервалу времени τ, в течение которого второй интегратор 12 находится в режиме интегрирования. С выхода блока 41 умножения на вход делимого первого блока 38 деления поступает сигнал, величина которого пропорциональна произведению τT'. С выхода первого усилителя 7 на вход делителя первого блока 38 деления поступает сигнал, величина которого пропорциональна величине Т температуры поверхности образца 2 в центре пятна нагрева. С выхода первого блока 38 деления на вход экстрематора 30 поступает сигнал, величина которого пропорциональна частному от деления величины сигнала, пропорционального произведению τT', на величину сигнала, пропорционального температуре T поверхности образца 2 в центре пятна нагрева.

При достижении в момент времени tм сигналом на выходе первого блока 38 деления минимального значения срабатывает экстрематор 30. Сигнал с выхода экстрематора 30 поступает на второй вход управления первого интегратора 11, первые входы управления второго 12, третьего 13, четвертого 14 и пятого 15 интеграторов и первый вход управления переключателя 33. Первый интегратор 11 переводится в режим интегрирования величины сигнала, поступающего на его информационный вход с выхода источника 32 опорного напряжения. Второй интегратор 12 переводится в режим хранения. Интеграторы 13-15 устанавливаются в нулевое состояние и в режим интегрирования сигналов, поступающих на их информационные входы с выходов переключателя 33. Переключатель 33 устанавливается в такое состояние, при котором сигнал, поступающий на его информационный вход с выхода первого усилителя 7, поступает на первый выход переключателя 33. С выхода первого усилителя 7 сигнал через переключатель 33 поступает на информационный вход третьего интегратора 13. На первый вход первого компаратора 22 через первый масштабный усилитель 34, коэффициент усиления которого k1=0,1, поступает сигнал с выхода второго интегратора 12. На второй вход первого компаратора 22 поступает сигнал с выхода первого интегратора 11.

При равенстве в момент времени t1 сигналов на входах первый компаратор 22 срабатывает. Сигнал с выхода первого компаратора 22 поступает на первый вход управления первого интегратора 11, вход первого делителя 27 частоты и второй вход управления переключателя 33. Интегратор 11 устанавливается в нулевое состояние. Переключатель 33 устанавливается в такое состояние, при котором его информационный вход отключается от первого выхода и подключается к второму выходу. С выхода первого усилителя 7 сигнал через переключатель 33 поступает на информационный вход четвертого интегратора 14.

При равенстве в момент времени t2 сигналов на входах первый компаратор 22 вновь срабатывает. Сигнал с выхода первого компаратора 22 поступает на первый вход управления первого интегратора 11, вход первого делителя 27 частоты и второй вход управления переключателя 33. Первый интегратор 11 устанавливается в нулевое состояние. Переключатель 33 устанавливается в такое состояние, при котором его информационный вход отключается от второго выхода и подключается к третьему выходу. С выхода первого усилителя 7 сигнал через переключатель 33 поступает на информационный вход пятого интегратора 15.

При равенстве в момент времени t3 сигналов на входах первый компаратор 22 вновь срабатывает. Сигнал с выхода первого компаратора 22 поступает на первый вход управления первого интегратора 11, вход первого делителя 27 частоты и второй вход управления переключателя 33. Первый интегратор 11 устанавливается в нулевое состояние. Переключатель 33 устанавливается в такое состояние, при котором его информационный вход отключается от третьего выхода. Первый делитель 27 частоты, коэффициент деления которого К1=3, срабатывает, и сигнал с его выхода поступает на вход второго делителя 28 частоты и вторые входы управления интеграторов 13-15. Интеграторы 13-15 устанавливаются в режим хранения. Сигналы с выходов третьего 13, четвертого 14 и пятого 15 интеграторов поступают на второй В2, третий В3 и четвертый В4 выходы устройства соответственно.

Первый делитель 27 частоты также срабатывает в моменты времени t6, t9, t12 и т.д. Сигнал с выхода первого делителя 27 частоты поступает на вход второго делителя 28 частоты. При равенстве сигналов на входах в момент времени t60 первый компаратор 22 срабатывает в шестидесятый раз. Сигнал с выхода первого компаратора 22 поступает на вход первого делителя 27 частоты. Первый делитель 27 частоты срабатывает в двадцатый раз. Сигнал с выхода первого делителя 27 частоты поступает на вход второго делителя 28 частоты. Второй делитель 28 частоты, коэффициент деления которого К2=20, срабатывает. Сигнал с выхода второго делителя 28 частоты поступает на вход управления второго блока 19 памяти. Второй блок 19 памяти устанавливается в режим записи. Во второй блок 19 памяти записывается значение сигнала на выходе первого усилителя 7, соответствующее величине температуры Тк поверхности образца 2 в центре пятна нагрева в момент времени t60. С выхода второго 19 блока памяти сигнал, соответствующий величине температуры ТК поверхности образца 2 в центре пятна нагрева в момент времени t60, поступает на шестой В6 выход устройства.

При пуске устройства сигнал с пусковой клеммы поступает также на третий вход управления шестого интегратора 16, первый вход управления седьмого интегратора 17, вход управления третьего блока памяти 20 и первый вход управления четвертого блока памяти 21. Шестой 16 и седьмой 17 интеграторы, третий 20 и четвертый 21 блоки памяти устанавливаются в исходное состояние. Исходному состоянию шестого интегратора 16 соответствует такое состояние, при котором шестой интегратор 16 находится в режиме хранения и на выходе шестого интегратора 16 сигнал отсутствует (нулевое состояние). Исходному состоянию седьмого интегратора 17 соответствует такое состояние, при котором седьмой интегратор 17 находится в режиме хранения и на выходе седьмого интегратора 17 сигнал отсутствует (нулевое состояние). Исходному состоянию третьего блока памяти 20 соответствует режим хранения. На выходе третьего блока памяти 20 величина сигнала в исходном состоянии соответствует температуре поверхности образца 2 в центре пятна нагрева при пуске устройства, измеряемой первой термопарой 3. Исходному состоянию четвертого блока памяти 21 соответствует режим записи. На выходе четвертого блока памяти 21 величина сигнала в исходном состоянии соответствует величине Тi, температуры, измеряемой третьей термопарой 5 в точке i на поверхности образца 2 при пуске устройства.

Сигналы с выходов второй 4, третьей 5 и четвертой 6 термопар усиливаются вторым 8, третьим 9 и четвертым 10 усилителями соответственно. Сигнал с выхода второго усилителя 8, соответствующий величине Ti-1 температуры в точке i-1 на поверхности образца 2, поступает на первый вход второго компаратора 23, первый вход первого блока вычитания 42 и первый вход второго сумматора 46. Сигнал с выхода третьего усилителя 9, соответствующий величине Ti температуры в точке i на поверхности образца 2, поступает на первый вход третьего компаратора 24, информационный вход четвертого блока памяти 21, первый вход третьего блока вычитания 44 и вход четвертого масштабного усилителя 37, коэффициент усиления которого k4=2. Сигнал с выхода четвертого масштабного усилителя 37, соответствующий произведению 2Ti, поступает на второй вход второго блока вычитания 43. Сигнал с выхода четвертого усилителя 10, соответствующий величине Ti+1 температуры в точке i+1 на поверхности образца 2, поступает на первый вход четвертого компаратора 25, второй вход первого блока вычитания 42 и второй вход второго сумматора 46.

Сигнал с выхода третьего блока памяти 20 поступает на вторые входы второго 23, третьего 24 и четвертого 25 компараторов. Сигнал с выхода первого блока вычитания 42, соответствующий разности Ti+1-Ti-1 температур в точках i+1 и i-1 на поверхности образца 2, поступает на вход второго масштабного усилителя 35, коэффициент усиления k2 которого соответствует величине отношения 1/(2riΔr), Δr=ri-ri-1. Сигнал с выхода второго масштабного усилителя 35, соответствующий отношению (Ti+1-Ti-1)/(2riΔr), поступает на первый вход первого сумматора 45. Сигнал с выхода второго сумматора 46, соответствующий сумме Ti+1+Ti-1 температур в точках i+1 и i-1 на поверхности образца 2, поступает на первый вход второго блока вычитания 43. Сигнал с выхода второго блока вычитания 43, соответствующий разности (Ti+1+Ti-1)-2Ti, поступает на вход третьего масштабного усилителя 36, коэффициент усиления k3 которого соответствует отношению 1/(Δr)2. Сигнал с выхода третьего масштабного усилителя 36, соответствующий отношению (Ti+1+Ti-1-2Ti)/(Δr)2, поступает на второй вход первого сумматора 45. Сигнал с выхода первого сумматора 45, соответствующий сумме

F1=(Ti+1-Ti-1)/(2riΔr)+(Ti+1+Ti-1-2Ti)/(Δr)2,

поступает на вход делителя третьего блока деления 40.

При достижении в момент времени ti-1 сигналом на первом входе второго компаратора 23 уровня, превышающего уровень сигнала на его втором входе на величину зоны нечувствительности, сигнал с выхода второго компаратора 23 поступает на первый вход управления шестого интегратора 16. Шестой интегратор 16 переводится в режим интегрирования сигнала, поступающего на информационный вход с выхода источника 32 опорного напряжения.

При достижении в момент времени ti сигналом на первом входе третьего компаратора 24 уровня, превышающего уровень сигнала на его втором входе на величину зоны нечувствительности, сигнал с выхода третьего компаратора 24 поступает на второй вход управления шестого интегратора 16. Шестой интегратор 16 переводится в режим хранения. Сигнал с выхода шестого интегратора 16, соответствующий интервалу времени Δt=ti-ti-1, поступает на второй вход пятого компаратора 26 и вход делителя второго блока деления 39.

При достижении в момент времени ti+1 сигналом на первом входе четвертого компаратора 25 уровня, превышающего уровень сигнала на его втором входе на величину зоны нечувствительности, сигнал с выхода четвертого компаратора 25 поступает на второй вход управления седьмого интегратора 17 и второй вход управления четвертого блока памяти 21. Седьмой интегратор 17 переводится в режим интегрирования сигнала, поступающего на его информационный вход с выхода источника 32 опорного напряжения. Четвертый блок памяти 21 переводится в режим хранения.

Сигнал с выхода четвертого блока памяти 21, соответствующий величине Ti1 температуры поверхности образца 2 в точке i в момент времени ti+1 срабатывания четвертого компаратора 25, поступает на второй вход третьего блока вычитания 44. Сигнал с выхода третьего блока вычитания 44, соответствующий разности Ti-Ti1, поступает на вход делимого второго блока деления 39. Сигнал с выхода второго блока деления 39, соответствующий отношению F2=(Ti-Ti1)/Δt, поступает на вход делимого третьего блока деления 40.

С выхода седьмого интегратора 17 сигнал поступает на первый вход пятого компаратора 26. При равенстве сигналов на входах в момент времени t* пятый компаратор 26 срабатывает. Сигнал с выхода пятого компаратора 26 поступает на вход управления третьего блока деления 40. Третий блок деления 40 срабатывает. Сигнал с выхода третьего блока деления 40, соответствующий отношению F2/F1 в момент времени t* срабатывания пятого компаратора 26, поступает на седьмой В7 выход устройства.

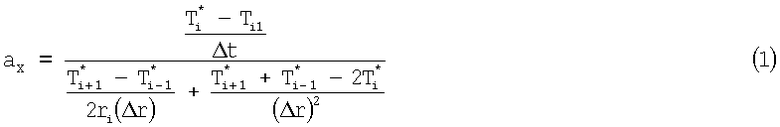

Таким образом, при импульсном нагреве излучением от источника 1 импульсного нагрева поверхности плоского непрозрачного или полупрозрачного для излучения нагрева образца 2 конечной толщины δ продольная относительно поверхности образца 2 составляющая aX коэффициента температуропроводности материала образца 2, полученная из дифференциального уравнения теплопроводности, представленного в конечных разностях, определяется путем запоминания в момент времени ti+1 температуры Ti1 в точке i, измерения в момент времени t* температур T* i-1, T* i, T* i+1 в точках i-1, i, i+1 соответственно и вычисления величины aX по формуле

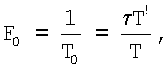

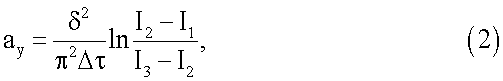

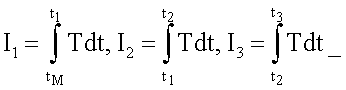

Перпендикулярная относительно поверхности образца 2 составляющая ау коэффициента температуропроводности материала образца 2 определяется кусочным интегрированием температурной кривой с задаваемым самим устройством постоянным шагом по времени Δτ=0,1(tм-tu), начиная с момента времени начала регуляризации температурного режима образца 2, соответствующим моменту времени tм достижения минимального значения функцией

где То - критерий термической однородности, характеризующий тепловое взаимодействие импульса нагрева с материалом образца 2 [7. Troitsky O.Y., Reiss Н. Remote nondestructive monitoring of coatings and materials by the flash technique // High Temperatures - High Pressures, 2000, v.32, p.391-395];

T! - первая производная температуры материала образца 2 в центре пятна нагрева; τ=t-tu, t - текущий момент времени;

по формуле

где Δτ - величина сигнала на выходе первого масштабного усилителя 34;

- величины сигналов на выходах третьего 13, четвертого 14 и пятого 15 интеграторов соответственно.

Другие теплофизические характеристики материала образца 2 определяются через количество поглощенной энергии Q по формулам

где γ - объемная теплоемкость материала образца 2;

λx, λу - продольная и перпендикулярная относительно поверхности составляющие коэффициента теплопроводности материала образца 2 соответственно;

bx, by - продольная и перпендикулярная относительно поверхности составляющие коэффициента теплоусвояемости материала образца 2 соответственно.

Коэффициент абсорбции µ материала образца 2 для длины волны возбуждения определяется методом итераций из уравнения

где Tк - установившаяся температура материала образца 2 в центре пятна нагрева в момент времени t60 через интервал времени τk=6(tм-tu) после момента времени tм начала регуляризации температурного режима;

Tu - температура материала образца 2 в центре пятна нагрева в момент времени tu окончания импульса нагрева.

Таким образом, по сравнению с прототипом предлагаемое устройство обладает расширенными функциональными возможностями за счет определения продольных относительно поверхности составляющих теплофизических характеристик исследуемых материалов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2013 |

|

RU2544312C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2006 |

|

RU2307344C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ТЕПЛОФИЗИЧЕСКИХ ХАРАКТЕРИСТИК | 1997 |

|

RU2132548C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2002 |

|

RU2212653C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2001 |

|

RU2184955C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Устройство для определения параметров динамического звена | 1983 |

|

SU1160372A1 |

| Устройство для определения параметров динамического звена | 1987 |

|

SU1478194A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2004 |

|

RU2255330C1 |

Изобретение относится к области теплового контроля материалов. Устройство дополнительно содержит три термопары, три усилителя, четыре компаратора, два блока памяти, два интегратора, три блока вычитания, два сумматора, три масштабных усилителя и два блока деления, при этом выходы второй, третьей и четвертой термопар соединены через второй, третий и четвертый усилители с первыми входами второго, третьего и четвертого компараторов соответственно, выход второго компаратора соединен с первым входом управления шестого интегратора, второй вход управления которого соединен с выходом третьего компаратора, третий вход управления шестого интегратора соединен с первым входом управления седьмого интегратора, пусковой клеммой, входом управления третьего блока памяти и первым входом управления четвертого блока памяти, информационный вход шестого интегратора соединен с выходом источника опорного напряжения и информационным входом седьмого интегратора. Технический результат - расширение функциональных возможностей устройства. 1 ил.

Устройство для определения характеристик материалов, содержащее источник импульсного нагрева, первую термопару, подключенную через первый усилитель к входу дифференциатора, пять интеграторов, первый компаратор, первый масштабный усилитель, датчик длительности импульса нагрева, первый блок деления, вход делителя которого соединен с выходом первого усилителя, блок умножения, экстрематор, переключатель, два делителя частоты, два блока памяти и источник опорного напряжения, при этом первый вход управления первого интегратора соединен с выходом первого компаратора, а информационные входы первого и второго интеграторов - с выходом источника опорного напряжения, причем выходы первого масштабного усилителя, третьего, четвертого и пятого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно, выход второго интегратора соединен с входом первого масштабного усилителя, выход которого соединен с первым входом первого компаратора, второй вход которого соединен с выходом первого интегратора, выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с входом делимого первого блока деления, выход которого соединен с входом экстрематора, выход которого соединен со вторым входом управления первого интегратора, первыми входами управления второго, третьего, четвертого и пятого интеграторов и первым входом управления переключателя, второй вход управления которого соединен с выходом первого компаратора и входом первого делителя частоты, третий вход управления переключателя соединен с выходом датчика длительности импульса нагрева, третьим входом управления первого интегратора, вторым входом управления второго интегратора и входом управления первого блока памяти, выход которого является пятым выходом устройства, а информационный вход соединен с выходом первого усилителя, информационными входами второго блока памяти и переключателя, первый выход которого соединен с информационным входом третьего интегратора, второй выход переключателя соединен с информационным входом четвертого интегратора, третий выход переключателя соединен с информационным входом пятого интегратора, второй вход управления которого соединен со вторыми входами управления третьего и четвертого интеграторов, выходом первого делителя частоты и входом второго делителя частоты, выход которого соединен с входом управления второго блока памяти, выход которого является шестым выходом устройства, вход источника импульсного нагрева соединен с пусковой клеммой, отличающееся тем, что дополнительно содержит три термопары, три усилителя, четыре компаратора, два блока памяти, два интегратора, три блока вычитания, два сумматора, три масштабных усилителя и два блока деления, при этом выходы второй, третьей и четвертой термопар соединены через второй, третий и четвертый усилители с первыми входами второго, третьего и четвертого компараторов соответственно, выход второго компаратора соединен с первым входом управления шестого интегратора, второй вход управления которого соединен с выходом третьего компаратора, третий вход управления шестого интегратора соединен с первым входом управления седьмого интегратора, пусковой клеммой, входом управления третьего блока памяти и первым входом управления четвертого блока памяти, информационный вход шестого интегратора соединен с выходом источника опорного напряжения и информационным входом седьмого интегратора, второй вход управления которого соединен со вторым входом управления четвертого блока памяти и выходом четвертого компаратора, а выход соединен с первым входом пятого компаратора, второй вход которого соединен с выходом шестого интегратора и входом делителя второго блока деления, а выход соединен с входом управления третьего блока деления, вход делимого которого соединен с выходом второго блока деления, вход делителя третьего блока деления соединен с выходом первого сумматора, а выход является седьмым выходом устройства, выход второго усилителя соединен с первым входом второго сумматора и первым входом первого блока вычитания, второй вход которого соединен со вторым входом второго сумматора и выходом четвертого усилителя, а выход соединен с входом второго масштабного усилителя, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом третьего масштабного усилителя, вход которого соединен с выходом второго блока вычитания, первый вход которого соединен с выходом второго сумматора, а второй вход соединен с выходом четвертого масштабного усилителя, вход которого соединен с первым входом третьего блока вычитания, информационным входом четвертого блока памяти и первым входом третьего компаратора, второй вход которого соединен со вторыми входами второго и четвертого компараторов и выходом третьего блока памяти, информационный вход которого соединен с выходом первого усилителя, выход четвертого блока памяти соединен со вторым входом третьего блока вычитания, выход которого соединен с входом делимого второго блока деления.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2006 |

|

RU2307344C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2004 |

|

RU2255330C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| US 5044767 А, 03.09.1991. | |||

Авторы

Даты

2010-06-20—Публикация

2009-05-18—Подача