Устройство относится к техническим средствам для определения характеристик материалов и может использоваться как при исследовании свойств новых материалов, так и в тепловом неразрушающем контроле.

Известно устройство для определения характеристик материалов [Патент RU 2392612 C1, МПК (2006.01) G01N 25/18, опубликован 20.06.2010], выбранное в качестве прототипа, содержащее источник импульсного нагрева, четыре термопары, четыре усилителя, дифференциатор, семь интеграторов, пять компараторов, четыре масштабных усилителя, датчик длительности импульса нагрева, три блока деления, блок умножения, экстрематор, переключатель, два делителя частоты, четыре блока памяти, два сумматора, источник опорного напряжения и три блока вычитания. Первая термопара подключена через первый усилитель к входу дифференциатора. Вход делителя первого блока деления соединен с выходом первого усилителя. Первый вход управления первого интегратора соединен с выходом первого компаратора. Информационные входы первого и второго интеграторов соединены с выходом источника опорного напряжения. Выходы первого масштабного усилителя, третьего, четвертого и пятого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно. Выход второго интегратора соединен с входом первого масштабного усилителя, выход которого соединен с первым входом первого компаратора, второй вход которого соединен с выходом первого интегратора. Выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с входом делимого первого блока деления, выход которого соединен с входом экстрематора, выход которого соединен со вторым входом управления первого интегратора, первыми входами управления второго, третьего, четвертого и пятого интеграторов и первым входом управления переключателя, второй вход управления которого соединен с выходом первого компаратора и входом первого делителя частоты. Третий вход управления переключателя соединен с выходом датчика длительности импульса нагрева, третьим входом управления первого интегратора, вторым входом управления второго интегратора и входом управления первого блока памяти, выход которого является пятым выходом устройства. Информационный вход первого блока памяти соединен с выходом первого усилителя, информационными входами второго блока памяти и переключателя, первый выход которого соединен с информационным входом третьего интегратора. Второй выход переключателя соединен с информационным входом четвертого интегратора. Третий выход переключателя соединен с информационным входом пятого интегратора, второй вход управления которого соединен со вторыми входами управления третьего и четвертого интеграторов, выходом первого делителя частоты и входом второго делителя частоты, выход которого соединен с входом управления второго блока памяти, выход которого является шестым выходом устройства. Вход источника импульсного нагрева соединен с пусковой клеммой. Выходы второй, третьей и четвертой термопар соединены через второй, третий и четвертый усилители с первыми входами второго, третьего и четвертого компараторов соответственно. Выход второго компаратора соединен с первым входом управления шестого интегратора, второй вход управления которого соединен с выходом третьего компаратора. Третий вход управления шестого интегратора соединен с первым входом управления седьмого интегратора, пусковой клеммой, входом управления третьего блока памяти и первым входом управления четвертого блока памяти. Информационный вход шестого интегратора соединен с выходом источника опорного напряжения и информационным входом седьмого интегратора, второй вход управления которого соединен со вторым входом управления четвертого блока памяти и выходом четвертого компаратора, а выход соединен с первым входом пятого компаратора, второй вход которого соединен с выходом шестого интегратора и входом делителя второго блока деления, а выход соединен с входом управления третьего блока деления, вход делимого которого соединен с выходом второго блока деления. Вход делителя третьего блока деления соединен с выходом первого сумматора, а выход является седьмым выходом устройства. Выход второго усилителя соединен с первым входом второго сумматора и первым входом первого блока вычитания, второй вход которого соединен со вторым входом второго сумматора и выходом четвертого усилителя, а выход соединен с входом второго масштабного усилителя, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом третьего масштабного усилителя, вход которого соединен с выходом второго блока вычитания, первый вход которого соединен с выходом второго сумматора, а второй вход соединен с выходом четвертого масштабного усилителя, вход которого соединен с первым входом третьего блока вычитания, информационным входом четвертого блока памяти и первым входом третьего компаратора, второй вход которого соединен со вторыми входами второго и четвертого компараторов и выходом третьего блока памяти, информационный вход которого соединен с выходом первого усилителя. Выход четвертого блока памяти соединен со вторым входом третьего блока вычитания, выход которого соединен с входом делимого второго блока деления.

Выбранное в качестве прототипа устройство имеет ограниченные функциональные возможности, не позволяющие определять величины теплофизических характеристик изотропных материалов образцов, толщина которых неизвестна.

Задачей изобретения является расширение функциональных возможностей устройства для определения характеристик материалов.

Для решения задачи изобретения в устройство, содержащее источник импульсного нагрева, четыре термопары, четыре усилителя, дифференциатор, семь интеграторов, пять компараторов, четыре масштабных усилителя, датчик длительности импульса нагрева, три блока деления, блок умножения, экстрематор, переключатель, два делителя частоты, четыре блока памяти, два интегратора, два сумматора и источник опорного напряжения, при этом первая термопара подключена через первый усилитель к входу дифференциатора, вход делителя первого блока деления соединен с выходом первого усилителя, первый вход управления первого интегратора соединен с выходом первого компаратора, а информационные входы первого и второго интеграторов - с выходом источника опорного напряжения, причем выходы первого масштабного усилителя, третьего, четвертого и пятого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно, выход второго интегратора соединен с входом первого масштабного усилителя, выход которого соединен с первым входом первого компаратора, второй вход которого соединен с выходом первого интегратора, выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с входом делимого первого блока деления, выход которого соединен с входом экстрематора, выход которого соединен с вторым входом управления первого интегратора, первыми входами управления второго, третьего, четвертого и пятого интеграторов и первым входом управления переключателя, второй вход управления которого соединен с выходом первого компаратора и входом первого делителя частоты, третий вход управления переключателя соединен с выходом датчика длительности импульса нагрева, третьим входом управления первого интегратора, вторым входом управления второго интегратора и входом управления первого блока памяти, выход которого является пятым выходом устройства, а информационный вход соединен с выходом первого усилителя, информационными входами второго блока памяти и переключателя, первый выход которого соединен с информационным входом третьего интегратора, второй выход переключателя соединен с информационным входом четвертого интегратора, третий выход переключателя соединен с информационным входом пятого интегратора, второй вход управления которого соединен с вторыми входами управления третьего и четвертого интеграторов, выходом первого делителя частоты и входом второго делителя частоты, выход которого соединен с входом управления второго блока памяти, выход которого является шестым выходом устройства, вход источника импульсного нагрева соединен с пусковой клеммой, выходы второй, третьей и четвертой термопар соединены через второй, третий и четвертый усилители с первыми входами второго, третьего и четвертого компараторов соответственно, выход второго компаратора соединен с первым входом управления шестого интегратора, второй вход управления которого соединен с выходом третьего компаратора, третий вход управления шестого интегратора соединен с первым входом управления седьмого интегратора, пусковой клеммой, входом управления третьего блока памяти и первым входом управления четвертого блока памяти, информационный вход шестого интегратора соединен с выходом источника опорного напряжения и информационным входом седьмого интегратора, второй вход управления которого соединен с вторым входом управления четвертого блока памяти и выходом четвертого компаратора, а выход соединен с первым входом пятого компаратора, второй вход которого соединен с выходом шестого интегратора и входом делителя второго блока деления, а выход соединен с входом управления третьего блока деления, вход делимого которого соединен с выходом второго блока деления, вход делителя третьего блока деления соединен с выходом первого сумматора, а выход является седьмым выходом устройства, выход второго усилителя соединен с первым входом второго сумматора и первым входом первого блока вычитания, второй вход которого соединен со вторым входом второго сумматора и выходом четвертого усилителя, а выход соединен с входом второго масштабного усилителя, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом третьего масштабного усилителя, вход которого соединен с выходом второго блока вычитания, первый вход которого соединен с выходом второго сумматора, а второй вход соединен с выходом четвертого масштабного усилителя, вход которого соединен с первым входом третьего блока вычитания, информационным входом четвертого блока памяти и первым входом третьего компаратора, второй вход которого соединен со вторыми входами второго и четвертого компараторов и выходом третьего блока памяти, информационный вход которого соединен с выходом первого усилителя, выход четвертого блока памяти соединен со вторым входом третьего блока вычитания, выход которого соединен с входом делимого второго блока деления, дополнительно введены блок управления, два блока памяти, делитель частоты, два масштабных усилителя, переключатель, блок деления, два квадратора, два блока умножения, два блока вычитания и четыре сумматора, при этом выход первого усилителя соединен с информационным входом второго переключателя, информационными входами третьего и четвертого сумматоров и входом первого квадратора, выход которого соединен с информационным входом пятого сумматора, выход которого соединен со входом пятого масштабного усилителя, выход которого соединен с первым информационным входом четвертого блока вычитания, второй информационный вход которого подключен к выходу второго квадратора, вход которого подключен к выходу третьего сумматора и первому информационному входу второго блока умножения, второй информационный вход которого подключен к выходу четвертого сумматора, а выход соединен с первым информационным входом пятого блока вычитания, второй информационный вход которого через шестой масштабный усилитель подключен к выходу шестого сумматора, а выход соединен с входом делимого четвертого блока деления, вход делителя которого подключен к выходу четвертого блока вычитания, а выход соединен с восьмым выходом устройства, первый выход второго переключателя соединен со входом пятого блока памяти, второй выход второго переключателя соединен со входом шестого блока памяти, выход которого соединен с первым информационным входом третьего блока умножения, второй информационный вход которого подключен к выходу пятого блока памяти, а выход соединен с информационным входом шестого сумматора, выход экстрематора соединен с первым входом блока управления и первым входом третьего делителя частоты, второй вход которого подключен к выходу первого компаратора и второму входу блока управления, а выход соединен с третьим входом блока управления, первый выход блока управления соединен со входами управления третьего и пятого сумматоров, второй выход блока управления соединен со входом управления второго переключателя, третий выход блока управления соединен со входом управления третьего блока умножения, четвертый выход блока управления соединен со входом управления шестого сумматора, пятый выход блока управления соединен со входом управления четвертого сумматора, шестой выход блока управления соединен со входом управления второго блока умножения, седьмой выход блока управления соединен со входами управления четвертого и пятого блоков вычитания, восьмой выход блока управления соединен со входом управления четвертого блока деления.

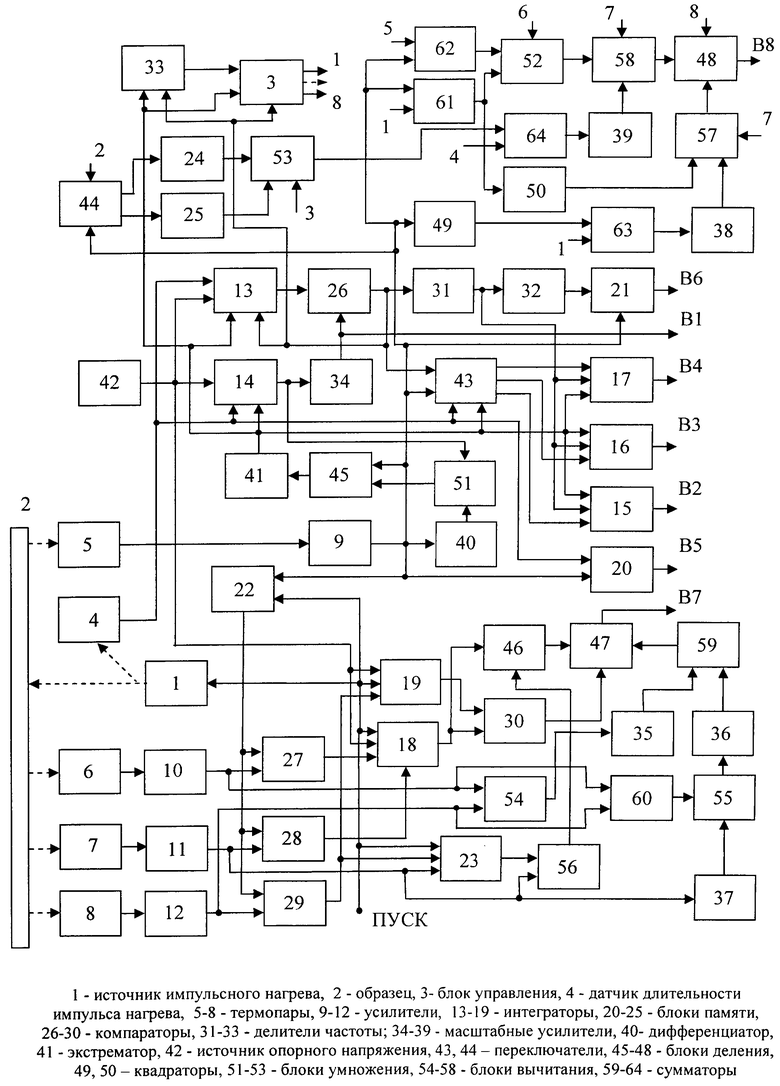

На чертеже изображена схема устройства.

Устройство содержит источник 1 импульсного нагрева, образец 2, блок управления 3, датчик 4 длительности импульса нагрева, термопары 5-8, усилители 9-12, интеграторы 13-19, блоки 20-25 памяти, компараторы 26-30, делители 31-33 частоты, масштабные усилители 34-39, дифференциатор 40, экстрематор 41, источник 42 опорного напряжения, переключатели 43, 44, блоки 45-48 деления, квадраторы 49, 50, блоки 51-53 умножения, блоки 54-58 вычитания, сумматоры 59-64.

Источник 1 импульсного нагрева оптически связан с датчиком 4 и образцом 2. Первая термопара 5 расположена на поверхности образца 2 в центре пятна нагрева, имеющего радиус r0. Вторая 6, третья 7 и четвертая 8 термопары расположены в точках i-1, i, i+1 на поверхности образца 2 на прямой, проходящей через центр пятна нагрева, на расстояниях ri-1, ri, ri+1 от центра пятна нагрева соответственно; ri-1>r0, ri-ri-1=ri+1-ri=Δr. Величины зон нечувствительности компараторов 26-30 одинаковы и превышают максимальное значение погрешности измерения температуры поверхности образца 2 термопарами 5-8.

Вход источника 1 импульсного нагрева соединен с пусковой клеммой. Первая термопара 5 соединена с входом первого усилителя 9. Выход первого усилителя 9 соединен с входом дифференциатора 40, входом делителя первого блока деления 45 и информационными входами первого переключателя 43, первого 20, второго 21 и третьего 22 блоков памяти. Первый вход управления первого интегратора 13 соединен с выходом первого компаратора 26, вторым входом управления первого переключателя 43 и входом первого делителя 31 частоты. Информационные входы первого 13, второго 14, шестого 18 и седьмого 19 интеграторов соединены с выходом источника 42 опорного напряжения. Выход второго интегратора 14 соединен с входом первого масштабного усилителя 34 и вторым входом первого блока умножения 51. Выход дифференциатора 40 соединен с первым входом первого блока умножения 51. Выход первого блока умножения 51 соединен с входом делимого первого блока деления 45. Выход первого блока деления 45 соединен с входом экстрематора 41. Выход экстрематора 41 соединен со вторым входом управления первого интегратора 13, первыми входами управления второго 14, третьего 15, четвертого 16 и пятого 17 интеграторов и первым входом управления первого переключателя 43. Выход датчика 4 соединен с третьим входом управления первого интегратора 13, вторым входом управления второго интегратора 14, входом управления первого блока памяти 20 и третьим входом управления первого переключателя 43. Первый выход первого переключателя 43 соединен с информационным входом третьего интегратора 15, второй выход первого переключателя 43 соединен с информационным входом четвертого интегратора 16, третий выход первого переключателя 43 соединен с информационным входом пятого интегратора 17. Выход первого масштабного усилителя 34 соединен с первым входом первого компаратора 26 и первым В1 выходом устройства. Выход первого интегратора 13 соединен со вторым входом первого компаратора 26. Выход первого делителя частоты 31 соединен со вторыми входами управления третьего 15, четвертого 16 и пятого 17 интеграторов и входом второго делителя 32 частоты. Выход второго делителя 32 частоты соединен с входом управления второго блока памяти 21. Выходы третьего 15, четвертого 16 и пятого 17 интеграторов соединены с вторым В2, третьим В3 и четвертым В4 выходами устройства соответственно. Выходы первого 20 и второго 21 блоков памяти соединены с пятым В5 и шестым В6 выходами устройства соответственно. Вторая термопара 6 соединена с входом второго усилителя 10. Выход второго усилителя 10 соединен с первым входом второго компаратора 27, первым входом первого блока вычитания 54 и первым входом второго сумматора 60. Третья термопара 7 соединена с входом третьего усилителя 11. Выход третьего усилителя 11 соединен с первым входом третьего компаратора 28, информационным входом четвертого блока памяти 23, первым входом третьего блока вычитания 56 и входом четвертого масштабного усилителя 37. Четвертая термопара 8 соединена с входом четвертого усилителя 12. Выход четвертого усилителя 12 соединен с первым входом четвертого компаратора 29, вторым входом первого блока вычитания 54 и вторым входом второго сумматора 60. Выход второго компаратора 27 соединен с первым входом управления шестого интегратора 18. Выход третьего компаратора 28 соединен со вторым входом управления шестого интегратора 18. Выход четвертого компаратора 29 соединен со вторым входом управления седьмого интегратора 19 и вторым входом управления четвертого блока памяти 23. Первый вход управления четвертого блока памяти 23 соединен с третьим входом управления шестого интегратора 18, первым входом управления седьмого интегратора 19, входом управления третьего блока памяти 22 и пусковой клеммой. Выход третьего блока памяти 22 соединен со вторыми входами второго 27, третьего 28 и четвертого 29 компараторов. Выход шестого интегратора 18 соединен с входом делителя второго блока деления 46 и вторым входом пятого компаратора 30. Выход седьмого интегратора 19 соединен с первым входом пятого компаратора 30. Выход пятого компаратора 30 соединен с входом управления третьего блока деления 47. Выход первого блока вычитания 54 соединен с входом второго масштабного усилителя 35. Выход второго масштабного усилителя 35 соединен с первым входом первого сумматора 59. Выход четвертого блока памяти 23 соединен с вторым входом третьего блока вычитания 56. Выход третьего блока вычитания 56 соединен с входом делимого второго блока деления 39. Выход второго блока деления 39 соединен с входом делимого третьего блока деления 47. Выход второго сумматора 60 соединен с первым входом второго блока вычитания 55. Выход четвертого масштабного усилителя 37 соединен со вторым входом второго блока вычитания 55. Выход второго блока вычитания 55 соединен с входом третьего масштабного усилителя 36. Выход третьего масштабного усилителя 36 соединен с вторым входом первого сумматора 59. Выход первого сумматора 59 соединен с входом делителя третьего блока деления 47. Выход третьего блока деления 47 соединен с седьмым В7 выходом устройства. Выход первого усилителя 9 соединен с информационным входом второго переключателя 44, информационными входами третьего 61 и четвертого 62 сумматоров и входом первого квадратора 49. Выход первого квадратора 49 соединен с информационным входом пятого сумматора 63. Выход пятого сумматора 63 соединен со входом пятого масштабного усилителя 38. Выход пятого масштабного усилителя 38 соединен с первым информационным входом четвертого блока 57 вычитания. Второй информационный вход четвертого блока 57 вычитания подключен к выходу второго квадратора 50. Выход третьего сумматора 61 соединен со входом второго квадратора 50 и первым информационным входом второго блока 52 умножения. Выход четвертого сумматора 62 соединен со вторым информационным входом второго блока 52 умножения. Выход второго блока 52 умножения соединен с первым информационным входом пятого блока 58 вычитания. Выход шестого сумматора 64 соединен со входом шестого масштабного усилителя 39. Выход шестого масштабного усилителя 39 соединен со вторым информационный входом пятого блока 58 вычитания. Выход пятого блока 58 вычитания соединен с входом делимого четвертого блока 48 деления. Выход четвертого блока 57 вычитания соединен с входом делителя четвертого блока 48 деления. Выход четвертого блока 48 деления соединен с восьмым выходом В8 устройства. Первый выход второго переключателя 44 соединен со входом пятого блока 24 памяти. Второй выход второго переключателя 44 соединен со входом шестого блока 25 памяти. Выход шестого блока 25 памяти соединен с первым информационным входом третьего блока 53 умножения. Выход пятого блока 24 памяти соединен со вторым информационный входом третьего блока 53 умножения. Выход третьего блока 53 умножения соединен с информационным входом шестого сумматора 64. Выход экстрематора 41 соединен с первым входом блока управления 3 и первым входом третьего делителя частоты 33. Выход первого компаратора 26 соединен со вторым входом третьего делителя частоты 33 и вторым входом блока управления 3. Выход третьего делителя частоты 33 соединен с третьим входом блока управления 3. Первый выход блока управления 3 соединен со входами управления третьего 61 и пятого 63 сумматоров. Второй выход блока управления 3 соединен со входом управления второго переключателя 44. Третий выход блока управления 3 соединен со входом управления третьего блока 53 умножения. Четвертый выход блока управления 3 соединен со входом управления шестого сумматора 64. Пятый выход блока управления 3 соединен со входом управления четвертого сумматора 62. Шестой выход блока управления 3 соединен со входом управления второго блока умножения 52. Седьмой выход блока управления 3 соединен со входами управления четвертого 57 и пятого 58 блоков вычитания. Восьмой выход блока управления 3 соединен со входом управления четвертого блока 48 деления.

Устройство работает следующим образом.

При пуске устройства сигнал поступает на вход источника 1 импульсного нагрева. Источник 1 запускается, при этом тепловой поток от источника 1 поступает на поверхность образца 2 и вход датчика 4. Температура поверхности образца 2 в центре пятна нагрева измеряется первой термопарой 5, сигнал с выхода которой усиливается первым усилителем 9 и поступает на информационные входы первого 20 и второго 21 блоков памяти, переключателя 43, вход делителя первого блока 45 деления и вход дифференциатора 40.

При срабатывании в момент времени tи датчика 4 сигнал с его выхода поступает на третий вход управления первого интегратора 13, второй вход управления второго интегратора 14, третий вход управления переключателя 43 и вход управления первого блока 20 памяти. Первый 13 и второй 14 интеграторы, переключатель 43 и первый блок 20 памяти устанавливаются в исходное состояние. Исходному состоянию первого интегратора 13 соответствует такое состояние, при котором первый интегратор 13 находится в режиме хранения и на его выходе сигнал отсутствует (нулевое состояние). Исходному состоянию второго интегратора 14 соответствует такое состояние, при котором второй интегратор 14 находится в режиме интегрирования и на его выходе сигнал отсутствует. Исходному состоянию переключателя 43 соответствует такое состояние, при котором информационный вход переключателя 43 отключен от его первого, второго и третьего выходов. Исходному состоянию первого блока 20 памяти соответствует режим записи величины сигнала, поступающего на информационный вход первого блока 20 памяти с выхода первого усилителя 9. В первый блок 20 памяти записывается значение сигнала на выходе первого усилителя 9, соответствующее величине Tи температуры поверхности образца 2 в центре пятна нагрева в момент времени tи. С выхода первого блока 20 памяти сигнал, соответствующий величине Tи температуры поверхности образца 2 в центре пятна нагрева в момент времени tи, поступает на пятый В5 выход устройства. С выхода дифференциатора 40 сигнал, пропорциональный первой производной T! температуры T поверхности образца 2 в центре пятна нагрева, поступает на первый вход первого блока 51 умножения. На второй вход блока 51 умножения поступает с выхода второго интегратора 14 сигнал, величина которого пропорциональна интервалу времени τ, в течение которого второй интегратор 14 находится в режиме интегрирования. С выхода блока 51 умножения на вход делимого первого блока 45 деления поступает сигнал, величина которого пропорциональна произведению τT!. С выхода первого усилителя 9 на вход делителя первого блока 45 деления поступает сигнал, величина которого пропорциональна величине T температуры поверхности образца 2 в центре пятна нагрева. С выхода первого блока 45 деления на вход экстрематора 41 поступает сигнал, величина которого пропорциональна частному от деления величины сигнала, пропорционального произведению τT!, на величину сигнала, пропорционального температуре Т поверхности образца 2 в центре пятна нагрева.

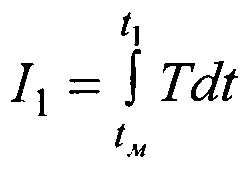

При достижении в момент времени tм сигналом на выходе первого блока 45 деления минимального значения срабатывает экстрематор 41. Сигнал с выхода экстрематора 41 поступает на второй вход управления первого интегратора 13, первые входы управления второго 14, третьего 15, четвертого 16 и пятого 17 интеграторов и первый вход управления переключателя 43. Первый интегратор 13 переводится в режим интегрирования величины сигнала, поступающего на его информационный вход с выхода источника 42 опорного напряжения. Второй интегратор 14 переводится в режим хранения. Интеграторы 15-17 устанавливаются в нулевое состояние и в режим интегрирования сигналов, поступающих на их информационные входы с выходов переключателя 43. Переключатель 43 устанавливается в такое состояние, при котором сигнал, поступающий на его информационный вход с выхода первого усилителя 9, поступает на первый выход переключателя 43. С выхода первого усилителя 9 сигнал через переключатель 43 поступает на информационный вход третьего интегратора 15. На первый вход первого компаратора 26 через первый масштабный усилитель 34, коэффициент усиления которого k1=0,1, поступает сигнал с выхода второго интегратора 14. На второй вход первого компаратора 26 поступает сигнал с выхода первого интегратора 13.

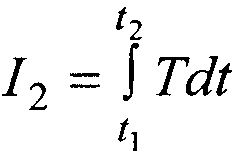

При равенстве в момент времени t1 сигналов на входах первый компаратор 26 срабатывает. Сигнал с выхода первого компаратора 26 поступает на первый вход управления первого интегратора 13, вход первого делителя 31 частоты и второй вход управления первого переключателя 43. Интегратор 13 устанавливается в нулевое состояние. Переключатель 43 устанавливается в такое состояние, при котором его информационный вход отключается от первого выхода и подключается к второму выходу. С выхода первого усилителя 9 сигнал через переключатель 43 поступает на информационный вход четвертого интегратора 16.

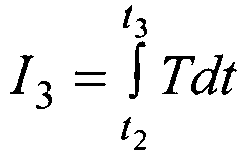

При равенстве в момент времени t2 сигналов на входах первый компаратор 26 вновь срабатывает. Сигнал с выхода первого компаратора 26 поступает на первый вход управления первого интегратора 13, вход первого делителя 31 частоты и второй вход управления переключателя 43. Первый интегратор 13 устанавливается в нулевое состояние. Переключатель 43 устанавливается в такое состояние, при котором его информационный вход отключается от второго выхода и подключается к третьему выходу. С выхода первого усилителя 9 сигнал через переключатель 43 поступает на информационный вход пятого интегратора 17.

При равенстве в момент времени t3 сигналов на входах первый компаратор 26 вновь срабатывает. Сигнал с выхода первого компаратора 26 поступает на первый вход управления первого интегратора 13, вход первого делителя 31 частоты и второй вход управления переключателя 43. Первый интегратор 13 устанавливается в нулевое состояние. Переключатель 43 устанавливается в такое состояние, при котором его информационный вход отключается от третьего выхода. Первый делитель 31 частоты, коэффициент деления которого К1=3, срабатывает, и сигнал с его выхода поступает на вход второго делителя 32 частоты и вторые входы управления интеграторов 15-17. Интеграторы 15-17 устанавливаются в режим хранения. Сигналы с выходов третьего 15, четвертого 16 и пятого 17 интеграторов поступают на второй В2, третий В3 и четвертый В4 выходы устройства соответственно.

Первый делитель 31 частоты также срабатывает в моменты времени t6, t9, t12 и т.д. Сигнал с выхода первого делителя 31 частоты поступает на вход второго делителя 32 частоты. При равенстве сигналов на входах в момент времени t60 первый компаратор 26 срабатывает в шестидесятый раз. Сигнал с выхода первого компаратора 26 поступает на вход первого делителя 31 частоты. Первый делитель 31 частоты срабатывает в двадцатый раз. Сигнал с выхода первого делителя 31 частоты поступает на вход второго делителя 32 частоты. Второй делитель 32 частоты, коэффициент деления которого К2=20, срабатывает. Сигнал с выхода второго делителя 32 частоты поступает на вход управления второго блока 21 памяти. Второй блок 21 памяти устанавливается в режим записи. Во второй блок 21 памяти записывается значение сигнала на выходе первого усилителя 9, соответствующее величине температуры Tк поверхности образца 2 в центре пятна нагрева в момент времени t60. С выхода второго блока 21 памяти сигнал, соответствующий величине температуры Tк поверхности образца 2 в центре пятна нагрева в момент времени t60, поступает на шестой В6 выход устройства.

При пуске устройства сигнал с пусковой клеммы поступает также на третий вход управления шестого интегратора 18, первый вход управления седьмого интегратора 19, вход управления третьего блока 22 памяти и первый вход управления четвертого блока 23 памяти. Шестой 18 и седьмой 19 интеграторы, третий 22 и четвертый 23 блоки памяти устанавливаются в исходное состояние. Исходному состоянию шестого интегратора 18 соответствует такое состояние, при котором шестой интегратор 18 находится в режиме хранения и на выходе шестого интегратора 18 сигнал отсутствует (нулевое состояние). Исходному состоянию седьмого интегратора 19 соответствует такое состояние, при котором седьмой интегратор 19 находится в режиме хранения и на выходе седьмого интегратора 19 сигнал отсутствует (нулевое состояние). Исходному состоянию третьего блока памяти 22 соответствует режим хранения. На выходе третьего блока памяти 22 величина сигнала в исходном состоянии соответствует температуре поверхности образца 2 в центре пятна нагрева при пуске устройства, измеряемой первой термопарой 5. Исходному состоянию четвертого блока памяти 23 соответствует режим записи. На выходе четвертого блока памяти 23 величина сигнала в исходном состоянии соответствует величине Ti температуры, измеряемой третьей термопарой 7 в точке i на поверхности образца 2 при пуске устройства.

Сигналы с выходов второй 6, третьей 7 и четвертой 8 термопар усиливаются вторым 10, третьим 11 и четвертым 12 усилителями соответственно. Сигнал с выхода второго усилителя 10, соответствующий величине Ti-1 температуры в точке i-1 на поверхности образца 2, поступает на первый вход второго компаратора 27, первый вход первого блока вычитания 54 и первый вход второго сумматора 60. Сигнал с выхода третьего усилителя 11, соответствующий величине Ti температуры в точке i на поверхности образца 2, поступает на первый вход третьего компаратора 28, информационный вход четвертого блока памяти 23, первый вход третьего блока вычитания 56 и вход четвертого масштабного усилителя 37, коэффициент усиления которого k4=2. Сигнал с выхода четвертого масштабного усилителя 37, соответствующий произведению 2Тi, поступает на второй вход второго блока вычитания 55. Сигнал с выхода четвертого усилителя 12, соответствующий величине Ti+1 температуры в точке i+1 на поверхности образца 2, поступает на первый вход четвертого компаратора 29, второй вход первого блока вычитания 54 и второй вход второго сумматора 60.

Сигнал с выхода третьего блока памяти 22 поступает на вторые входы второго 27, третьего 28 и четвертого 29 компараторов. Сигнал с выхода первого блока вычитания 54, соответствующий разности Ti+1-Ti-1 температур в точках i+1 и i-1 на поверхности образца 2, поступает на вход второго масштабного усилителя 35, коэффициент усиления k2 которого соответствует величине отношения 1/(2riΔr), Δr=ri-ri-1. Сигнал с выхода второго масштабного усилителя 35, соответствующий отношению (Ti+1-Ti-1)/(2riΔr), поступает на первый вход первого сумматора 59. Сигнал с выхода второго сумматора 60, соответствующий сумме Ti+1+Ti-1 температур в точках i+1 и i-1 на поверхности образца 2, поступает на первый вход второго блока вычитания 55. Сигнал с выхода второго блока вычитания 55, соответствующий разности (Тi+1+Ti-1)-2Ti, поступает на вход третьего масштабного усилителя 36, коэффициент усиления k3 которого соответствует отношению 1/(Δr)2. Сигнал с выхода третьего масштабного усилителя 36, соответствующий отношению (Ti+1+Ti-1-2Ti)/(Δr)2, поступает на второй вход первого сумматора 59. Сигнал с выхода первого сумматора 59, соответствующий сумме F1=(Ti+1-Ti-1)/(2tiΔr)+(Ti+1+Ti-1-2Ti)/(Δr)2, поступает на вход делителя третьего блока деления 47.

При достижении в момент времени ti-1 сигналом на первом входе второго компаратора 27 уровня, превышающего уровень сигнала на его втором входе на величину зоны нечувствительности, сигнал с выхода второго компаратора 27 поступает на первый вход управления шестого интегратора 18. Шестой интегратор 18 переводится в режим интегрирования сигнала, поступающего на информационный вход с выхода источника 42 опорного напряжения.

При достижении в момент времени ti сигналом на первом входе третьего компаратора 28 уровня, превышающего уровень сигнала на его втором входе на величину зоны нечувствительности, сигнал с выхода третьего компаратора 28 поступает на второй вход управления шестого интегратора 18. Шестой интегратор 18 переводится в режим хранения. Сигнал, соответствующий интервалу времени Δt=ti-ti-1, с выхода шестого интегратора 18 поступает на второй вход пятого компаратора 30 и вход делителя второго блока деления 46.

При достижении в момент времени ti+1 сигналом на первом входе четвертого компаратора 29 уровня, превышающего уровень сигнала на его втором входе на величину зоны нечувствительности, сигнал с выхода четвертого компаратора 29 поступает на второй вход управления седьмого интегратора 19 и второй вход управления четвертого блока памяти 23. Седьмой интегратор 19 переводится в режим интегрирования сигнала, поступающего на его информационный вход с выхода источника 42 опорного напряжения. Четвертый блок памяти 23 переводится в режим хранения.

Сигнал с выхода четвертого блока памяти 23, соответствующий величине Ti1 температуры поверхности образца 2 в точке i в момент времени ti+1 срабатывания четвертого компаратора 29, поступает на второй вход третьего блока вычитания 56. Сигнал с выхода третьего блока вычитания 56, соответствующий разности Ti-Ti1, поступает на вход делимого второго блока деления 46. Сигнал с выхода второго блока 46 деления, соответствующий отношению F2=(Ti-Ti1)/Δt, поступает на вход делимого третьего блока 47 деления.

С выхода седьмого интегратора 19 сигнал поступает на первый вход пятого компаратора 30. При равенстве сигналов на входах в момент времени t* пятый компаратор 30 срабатывает. Сигнал с выхода пятого компаратора 30 поступает на вход управления третьего блока 47 деления. Третий блок 47 деления срабатывает. Сигнал с выхода третьего блока 47 деления, соответствующий отношению F2/F1 в момент времени t* срабатывания пятого компаратора 30, поступает на седьмой выход В7 устройства.

В момент времени tм сигнал с выхода экстрематора 41 поступает также на первый вход блока 3 управления и первый вход третьего блока 33 деления частоты. Блок 3 управления устанавливается в исходное состояние. Исходному состоянию блока 3 управления соответствует такое состояние, при котором на выходах блока 3 управления сигналы отсутствуют. Третий блок 33 деления частоты устанавливается в исходное (нулевое) состояние.

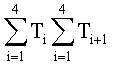

В момент времени t1 сигнал с выхода первого компаратора 26 поступает также на второй вход блока 3 управления и второй вход третьего блока 33 деления частоты. Сигнал с первого выхода блока 3 управления поступает на входы управления третьего сумматора 61 и пятого сумматора 63. В третьем сумматоре 61 записывается первое слагаемое - величина сигнала, поступающего на информационный вход третьего сумматора 61 с выхода первого усилителя 9, соответствующая температуре T1 поверхности образца 2 в момент времени t1. Сигнал с выхода третьего сумматора 61 поступает на первый вход второго блока 52 умножения и вход второго квадратора 50. С выхода второго квадратора 50 сигнал поступает на первый вход четвертого блока 57 вычитания. В пятом сумматоре 63 записывается первое слагаемое - величина сигнала, поступающего на информационный вход пятого сумматора 63 через квадратор 49 с выхода первого усилителя 9, соответствующая квадрату

В момент времени t2 сигнал с выхода первого компаратора 26 поступает также на второй вход блока 3 управления и второй вход управления третьего блока 33 деления частоты. Сигнал с первого выхода блока 3 управления поступает на входы управления третьего сумматора 61 и пятого сумматора 63. В третьем сумматоре 61 записывается второе слагаемое - величина сигнала, поступающего на информационный вход третьего сумматора 61 с выхода первого усилителя 9, соответствующая температуре T2 поверхности образца 2 в момент времени t2. Сигнал с выхода третьего сумматора 61 поступает на первый вход второго блока 52 умножения и вход второго квадратора 50. С выхода второго квадратора 50 сигнал поступает на первый вход четвертого блока 57 вычитания. В пятом сумматоре 63 записывается второе слагаемое - величина сигнала, поступающего на информационный вход пятого сумматора 63 через квадратор 49 с выхода первого усилителя 9, соответствующая квадрату

В момент времени t3 сигнал с выхода первого компаратора 26 поступает также на второй вход блока 3 управления и второй вход третьего блока 33 деления частоты. Сигнал с первого выхода блока 3 управления поступает на входы управления третьего сумматора 61 и пятого сумматора 63. В третьем сумматоре 61 записывается третье слагаемое - величина сигнала, поступающего на информационный вход третьего сумматора 61 с выхода первого усилителя 9, соответствующая температуре T3 поверхности образца 2 в момент времени t3. Сигнал с выхода третьего сумматора 61 поступает на первый вход второго блока 52 умножения и вход второго квадратора 50. С выхода второго квадратора 50 сигнал поступает на первый вход четвертого блока 57 вычитания. В пятом сумматоре 63 записывается третье слагаемое - величина сигнала, поступающего на информационный вход пятого сумматора 63 через квадратор 49 с выхода первого усилителя 9, соответствующая квадрату

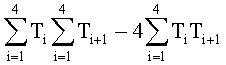

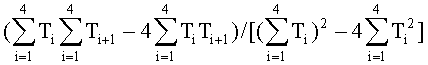

В момент времени t4 сигнал с выхода первого компаратора 26 поступает также на второй вход блока 3 управления и второй вход управления третьего блока 33 деления частоты. Сигнал с первого выхода блока 3 управления поступает на входы управления третьего сумматора 61 и пятого сумматора 63. В третьем сумматоре 61 записывается четвертое слагаемое - величина сигнала, поступающего на информационный вход третьего сумматора 61 с выхода первого усилителя 9, соответствующая температуре T4 поверхности образца 2 в момент времени t4. Сигнал с выхода третьего сумматора 61 поступает на первый вход второго блока 52 умножения и вход второго квадратора 50. С выхода второго квадратора 50 сигнал, соответствующий квадрату суммы

В момент времени t5 сигнал с выхода первого компаратора 26 поступает также на второй вход блока 3 управления и второй вход третьего блока 33 деления частоты. Сигнал со второго выхода блока 3 управления поступает на вход управления второго переключателя 44. Второй переключатель 44 устанавливается в такое состояние, при котором сигнал с выхода первого усилителя 9 через второй переключатель 44 поступает на вход пятого блока 24 памяти. В пятом блоке 24 памяти сохраняется величина сигнала, соответствующая температуре T5 поверхности образца 2 в момент времени t5. Сигнал с выхода пятого блока 24 памяти поступает на первый вход третьего блока 53 умножения. Сигнал с третьего выхода блока 3 управления поступает на вход управления третьего блока 53 умножения. Третий блок 53 умножения срабатывает. На выходе третьего блока 53 умножения появляется сигнал, соответствующий произведению T4T5. Сигнал с выхода третьего блока 53 умножения поступает на вход шестого сумматора 64. Сигнал с четвертого выхода блока 3 управления поступает на вход управления шестого сумматора 64. В шестом сумматоре 64 записывается четвертое слагаемое - величина сигнала, поступающего на информационный вход шестого сумматора 64 с выхода третьего блока 53 умножения, соответствующая произведению T4T5. Сигнал с выхода шестого сумматора 64 поступает на вход шестого масштабного усилителя 39, коэффициент усиления которого равен k6=4. Сигнал с выхода шестого масштабного усилителя 39, соответствующий произведению

Таким образом, при импульсном нагреве излучением от источника 1 импульсного нагрева поверхности плоского непрозрачного или полупрозрачного для излучения нагрева образца 2 известной толщины δ1 продольная относительно поверхности образца 2 составляющая a

x коэффициента температуропроводности материала образца 2, полученная из дифференциального уравнения теплопроводности, представленного в конечных разностях, определяется путем запоминания в момент времени ti+1 температуры Ti1 в точке i, измерения в момент времени t* температур

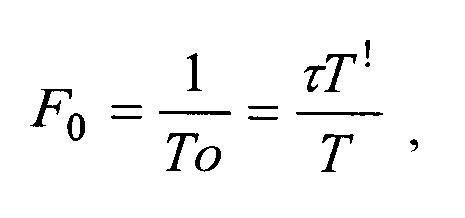

Перпендикулярная относительно поверхности образца 2 составляющая a y коэффициента температуропроводности материала образца 2 определяется кусочным интегрированием температурной кривой с задаваемым самим устройством постоянным шагом по времени Δτ=0,1(tм-tи), начиная с момента времени начала регуляризации температурного режима образца 2, соответствующим моменту времени tм достижения минимального значения функцией

где To - критерий термической однородности, характеризующий тепловое взаимодействие импульса нагрева с материалом образца 2;

T! - первая производная температуры материала образца 2 в центре пятна нагрева;

τ=t-tи, t - текущий момент времени;

по формуле

где ΔT - величина сигнала на выходе первого масштабного усилителя 34;

,

,  ,

,  - величины сигналов на выходах третьего 15, четвертого 16 и пятого 17 интеграторов соответственно.

- величины сигналов на выходах третьего 15, четвертого 16 и пятого 17 интеграторов соответственно.

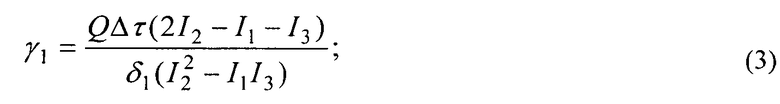

Другие теплофизические характеристики материала образца 2 известной толщины δ1 определяются через количество поглощенной энергии Q по формулам:

где γ1 - объемная теплоемкость материала образца 2;

λx, λy - продольная и перпендикулярная относительно поверхности составляющие коэффициента теплопроводности материала образца 2 соответственно;

bx, by - продольная и перпендикулярная относительно поверхности составляющие коэффициента теплоусвояемости материала образца 2 соответственно.

Коэффициент абсорбции µ1 материала образца 2 известной толщины δ1 для длины волны возбуждения определяется методом итераций из уравнения

где Tκ - установившаяся температура материала образца 2 в центре пятна нагрева в момент времени t60 через интервал времени τκ=6(tм-tи) после момента времени tм начала регуляризации температурного режима;

Tи - температура материала образца 2 в центре пятна нагрева в момент времени tи окончания импульса нагрева.

При импульсном нагреве излучением от источника 1 импульсного нагрева поверхности плоского непрозрачного или полупрозрачного для излучения нагрева изотропного материала образца 2 неизвестной толщины δ2 коэффициент температуропроводности a 2=a x-a y определяется по формуле (1).

Другие теплофизические характеристики изотропного материала образца 2 неизвестной толщины δ2 определяются через количество поглощенной энергии Q по формулам:

где γ2 - объемная теплоемкость изотропного материала образца 2;

δ2 - толщина образца 2;

λ2 - коэффициент теплопроводности изотропного материала образца 2;

b2 - коэффициент теплоусвояемости изотропного материала образца 2.

Толщина δ2 образца 2 определяется по формуле

где  .

.

Коэффициент абсорбции µ2 изотропного материала образца 2 толщиной δ2 для длины волны возбуждения определяется методом итераций из уравнения

.

.

Таким образом, по сравнению с прототипом предлагаемое устройство обладает расширенными функциональными возможностями за счет определения теплофизических характеристик изотропных материалов образцов, толщина которых неизвестна.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2009 |

|

RU2392612C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2006 |

|

RU2307344C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2002 |

|

RU2212653C1 |

| Устройство для определения параметров динамического звена | 1983 |

|

SU1160372A1 |

| Устройство для определения параметров динамического звена | 1987 |

|

SU1478194A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| Анализатор частотных характеристик | 1985 |

|

SU1307373A1 |

| Адаптивный временной дискретизатор | 1990 |

|

SU1791822A1 |

| Тензометрическое устройство | 1991 |

|

SU1796890A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

Устройство относится к области измерительной техники и может быть использовано для теплового контроля материалов. Устройство содержит источник импульсного нагрева, четыре термопары, четыре усилителя, дифференциатор, семь интеграторов, пять компараторов, шесть масштабных усилителей, датчик длительности импульса нагрева, четыре блока деления, три блока умножения, экстрематор, переключатель, два делителя частоты, четыре блока памяти, шесть сумматоров, источник опорного напряжения, пять блоков вычитания, блок управления, шесть блоков памяти, переключатель, четыре блока деления и два квадратора. Технический результат - расширение функциональных возможностей устройства. 1 ил.

Устройство для определения характеристик материалов, содержащее источник импульсного нагрева, четыре термопары, четыре усилителя, дифференциатор, семь интеграторов, пять компараторов, четыре масштабных усилителя, датчик длительности импульса нагрева, три блока деления, блок умножения, экстрематор, переключатель, два делителя частоты, четыре блока памяти, два сумматора, источник опорного напряжения и три блока вычитания, при этом первая термопара подключена через первый усилитель к входу дифференциатора, вход делителя первого блока деления соединен с выходом первого усилителя, первый вход управления первого интегратора соединен с выходом первого компаратора, а информационные входы первого и второго интеграторов - с выходом источника опорного напряжения, причем выходы первого масштабного усилителя, третьего, четвертого и пятого интеграторов являются первым, вторым, третьим и четвертым выходами устройства соответственно, выход второго интегратора соединен с входом первого масштабного усилителя, выход которого соединен с первым входом первого компаратора, второй вход которого соединен с выходом первого интегратора, выход дифференциатора соединен с первым входом блока умножения, второй вход которого соединен с выходом второго интегратора, а выход соединен с входом делимого первого блока деления, выход которого соединен с входом экстрематора, выход которого соединен со вторым входом управления первого интегратора, первыми входами управления второго, третьего, четвертого и пятого интеграторов и первым входом управления переключателя, второй вход управления которого соединен с выходом первого компаратора и входом первого делителя частоты, третий вход управления переключателя соединен с выходом датчика длительности импульса нагрева, третьим входом управления первого интегратора, вторым входом управления второго интегратора и входом управления первого блока памяти, выход которого является пятым выходом устройства, а информационный вход соединен с выходом первого усилителя, информационными входами второго блока памяти и переключателя, первый выход которого соединен с информационным входом третьего интегратора, второй выход переключателя соединен с информационным входом четвертого интегратора, третий выход переключателя соединен с информационным входом пятого интегратора, второй вход управления которого соединен со вторыми входами управления третьего и четвертого интеграторов, выходом первого делителя частоты и входом второго делителя частоты, выход которого соединен с входом управления второго блока памяти, выход которого является шестым выходом устройства, вход источника импульсного нагрева соединен с пусковой клеммой, выходы второй, третьей и четвертой термопар соединены через второй, третий и четвертый усилители с первыми входами второго, третьего и четвертого компараторов соответственно, выход второго компаратора соединен с первым входом управления шестого интегратора, второй вход управления которого соединен с выходом третьего компаратора, третий вход управления шестого интегратора соединен с первым входом управления седьмого интегратора, пусковой клеммой, входом управления третьего блока памяти и первым входом управления четвертого блока памяти, информационный вход шестого интегратора соединен с выходом источника опорного напряжения и информационным входом седьмого интегратора, второй вход управления которого соединен со вторым входом управления четвертого блока памяти и выходом четвертого компаратора, а выход соединен с первым входом пятого компаратора, второй вход которого соединен с выходом шестого интегратора и входом делителя второго блока деления, а выход соединен с входом управления третьего блока деления, вход делимого которого соединен с выходом второго блока деления, вход делителя третьего блока деления соединен с выходом первого сумматора, а выход является седьмым выходом устройства, выход второго усилителя соединен с первым входом второго сумматора и первым входом первого блока вычитания, второй вход которого соединен со вторым входом второго сумматора и выходом четвертого усилителя, а выход соединен с входом второго масштабного усилителя, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом третьего масштабного усилителя, вход которого соединен с выходом второго блока вычитания, первый вход которого соединен с выходом второго сумматора, а второй вход соединен с выходом четвертого масштабного усилителя, вход которого соединен с первым входом третьего блока вычитания, информационным входом четвертого блока памяти и первым входом третьего компаратора, второй вход которого соединен со вторыми входами второго и четвертого компараторов и выходом третьего блока памяти, информационный вход которого соединен с выходом первого усилителя, выход четвертого блока памяти соединен со вторым входом третьего блока вычитания, выход которого соединен с входом делимого второго блока деления, отличающееся тем, что дополнительно содержит блок управления, два блока памяти, делитель частоты, два масштабных усилителя, переключатель, блок деления, два квадратора, два блока умножения, два блока вычитания и четыре сумматора, при этом выход первого усилителя соединен с информационным входом второго переключателя, информационными входами третьего и четвертого сумматоров и входом первого квадратора, выход которого соединен с информационным входом пятого сумматора, выход которого соединен со входом пятого масштабного усилителя, выход которого соединен с первым информационным входом четвертого блока вычитания, второй информационный вход которого подключен к выходу второго квадратора, вход которого подключен к выходу третьего сумматора и первому информационному входу второго блока умножения, второй информационный вход которого подключен к выходу четвертого сумматора, а выход соединен с первым информационным входом пятого блока вычитания, второй информационный вход которого через шестой масштабный усилитель подключен к выходу шестого сумматора, а выход соединен с входом делимого четвертого блока деления, вход делителя которого подключен к выходу четвертого блока вычитания, а выход соединен с восьмым выходом устройства, первый выход второго переключателя соединен со входом пятого блока памяти, второй выход второго переключателя соединен со входом шестого блока памяти, выход которого соединен с первым информационным входом третьего блока умножения, второй информационный вход которого подключен к выходу пятого блока памяти, а выход соединен с информационным входом шестого сумматора, выход экстрематора соединен с первым входом блока управления и первым входом третьего делителя частоты, второй вход которого подключен к выходу первого компаратора и второму входу блока управления, а выход соединен с третьим входом блока управления, первый выход блока управления соединен со входами управления третьего и пятого сумматоров, второй выход блока управления соединен со входом управления второго переключателя, третий выход блока управления соединен со входом управления третьего блока умножения, четвертый выход блока управления соединен со входом управления шестого сумматора, пятый выход блока управления соединен со входом управления четвертого сумматора, шестой выход блока управления соединен со входом управления второго блока умножения, седьмой выход блока управления соединен со входами управления четвертого и пятого блоков вычитания, восьмой выход блока управления соединен со входом управления четвертого блока деления.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2009 |

|

RU2392612C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2006 |

|

RU2307344C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2004 |

|

RU2255330C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 2002 |

|

RU2212653C1 |

| JP 0056061640 A, 27.05.1981 | |||

Авторы

Даты

2015-03-20—Публикация

2013-10-14—Подача