Настоящее изобретение относится к способу управления работой порта последовательного доступа к видеопамяти, заключающемуся в том, что формируют сигнал разрешения передачи одного строчного элемента из порта памяти производного доступа в регистры порта памяти последовательного доступа, или сигнал разрешения передачи одного строчного элемента из порта памяти произвольного доступа в соответствующий регистр порта памяти последовательного доступа в реальном масштабе времени, формируют сигнал считывания данных из порта памяти произвольного доступа в последовательные регистры порта памяти последовательного доступа, осуществляют операцию считывания данных из порта памяти последовательного доступа, формируют сигнал записи данных от внешнего устройства в последовательные регистры порта памяти последовательного доступа, формируют сигнал передачи данных из регистра порта памяти последовательного доступа в соответствующий строчный элемент порта памяти произвольного доступа и осуществляют пересылку данных из порта памяти с последовательным доступом в порт памяти с произвольным доступом, формируют сигнал псевдопересылки данных от внешнего устройства в последовательные регистры порта памяти последовательного доступа.

Видеопамять произвольного доступа VRAM графического дисплея на ранней стадии имела порт памяти произвольного доступа 64К х 1 и порт памяти последовательного доступа 256К х 1, но затем была создана память 256К RAM, имеющая порт доступа 64К х 4. После этого в ходе совершенствования функций памяти 64К х 1 VRAM были разработаны функции побитовой записи и пересылки в реальном времени, в результате чего сформировался стандартный тип видеопамяти VRAM. Имеющиеся на текущий момент возможности объединения в единое целое 1 Мегабитов обусловили появление видеопамяти двух типов: 256К х 4 и 128К х 8. С другой стороны, когда данные пересылают из процессора на периферийное оборудование в известных (информационных) запоминающих устройствах произвольного доступа (DRAM), сначала выполняют пересылку данных в память и только затем осуществляют доступ к данным в памяти. В этом случае процессор не может переслать данные в память, когда доступ к памяти получают периферийные устройства. В видеопамятях VRAM, однако, когда процессор пересылает данные через первый порт памяти, память оказывается в то же самое время доступной через второй порт.

Это обстоятельство ниже описано со ссылками на фиг. 1.

На фиг. 1 изображена видеопамять VRAM 10, имеющая первый (RAM) порт памяти произвольного доступа 1 и второй порт памяти последовательного доступа (SAM) 2. Порт RAM 1 соединен с портом SAM 2 через посредство передающего данные вентиля DTG. Первый порт P1 видеопамяти VRAM 10, соединенный с процессором, используется для произвольного доступа, а второй порт P2, соединенный с экранным дисплейным устройством, используется для последовательного доступа. К тому же, одна сторона порта RAM 1 соединена с первым портом P1 через столбцовый декодер 4, и другая его сторона соединена со строчным декодером, но строчный декодер не изображен и позицией 5 обозначена управляющая часть. Поскольку порт SAM 2 обеспечивает высокоскоростной последовательный доступ, видеопамять VRAM 10 широко применяется в высокой разрушающей способности или высокоскоростных дисплейных системах.

Поэтому во время цикла пересылки операции считывания данных из порта RAM 1 переписываются в порт SAM 2 и устанавливается режим считывания этих данных в порт SAM 2. Аналогично данные, находящиеся в порту SAM 2, записываются в порт RAM 1 во время цикла пересылки операции записывания, и режим записывания данных реализуется циклом пересылки операции записывания и режимом псевдозаписывания PWT. На время, когда режим записывания данных оказывается преобразованным, в режиме считывания данных в порт SAM 2 должен быть обойден цикл пересылки операции считывания, и данные из порта RAM 1 предоставляются порту SAM2 таким образом, что порт SAM 2 не может непосредственно выполнить операцию считывания после записывания данных из порта SAM 2. Поэтому при массовом производстве видеопамяти RAM тестирование порта SAM оказывается невозможным, поскольку порт SAM не способен выполнять операции считывания и записывания независимо от порта RAM.

Объектом настоящего изобретения является способ управления работой порта последовательного доступа к видеопамяти, в котором порт последовательного доступа SAM самостоятельно может выполнять операции записывания и считывания вне зависимости от порта RAM при тестировании видеопамяти RAM.

Эту цель можно достигнуть путем того, что дополнительно формируют сигнал псевдопересылки считывания, за счет которого осуществляют блокировку передачи данных из регистра порта памяти последовательного доступа в соответствующий строчный элемент порта памяти произвольного доступа и который используют в качестве сигнала разрешения последовательного считывания данных из порта памяти произвольного доступа в соответствующие регистры порта памяти последовательного доступа в реальном масштабе времени.

В способе согласно изобретению сигнал псевдопересылки считывания, за счет которого осуществляют блокировку передачи данных из регистра порта памяти последовательного доступа в соответствующий строчный элемент порта памяти произвольного доступа, формируют с помощью блока управления.

В заявленном способе сигнал псевдопересылки считывания, за счет которого осуществляют блокировку передачи данных из регистра порта памяти последовательного доступа в соответствующий строчный элемент порта памяти произвольного доступа, подают на контактные площадки, прикрепленные на порту последовательного доступа.

Заявленный способ позволяет выполнять цикл пересылки считывания, за которым данные, находящиеся в порту RAM, пересылают на порт SAM в режиме пересылки операции считывания или режиме пересылки операции считывания в реальном времени и данные, находящиеся в порту SAM, пересылают в режиме последовательного считывания; выполнять цикл пересылки операции записывания, за которой данные от внешнего устройства непосредственно запоминают в порту SAM при считывании с внешнего устройства в режиме последовательного записывания и данные, находящиеся в порту SAM, пересылают на порт RAM в режиме пересылки операции записывания; выполнять режим псевдопересылки операции записывания; выполнять режим псевдопересылки операции записывания, который преобразуют в режим последовательного записывания без пересылки данных между циклом пересылки считывания и циклом пересылки операции записывания; и выполнять режим псевдопересылки операции считывания, который преобразуют в режим последовательного считывания без пересылки данных между циклом пересылки операции считывания и циклом пересылки операции записывания.

Эти и другие цели, признаки и преимущества настоящего изобретения станут очевидны после ознакомления с приведенным ниже подробным описанием предпочтительных вариантов осуществления настоящего изобретения, которое ведется со ссылками на приложенные чертежи.

На фиг. 1 показана блок-схема структуры известной видеопамяти VRAM.

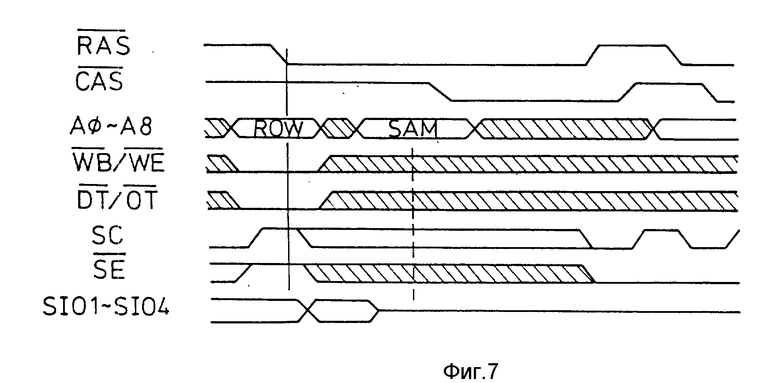

Фиг. 2-7 представляет временную диаграмму каждого из операционных режимов порта SAM видеопамяти VRAM.

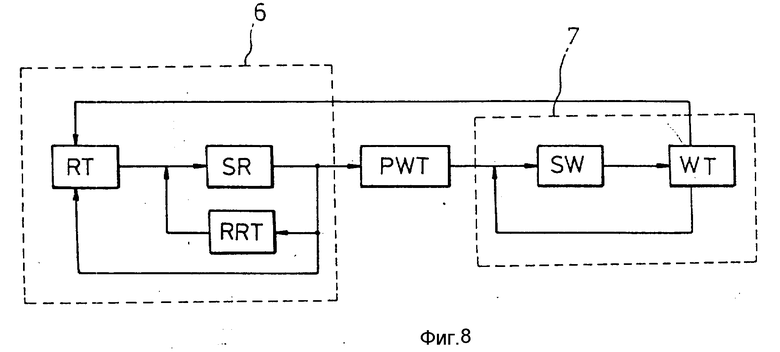

Фиг. 8 представляет диаграмму последовательности режимных переходов, иллюстрирующую работу SAM в известном двухпортовом запоминающем устройстве.

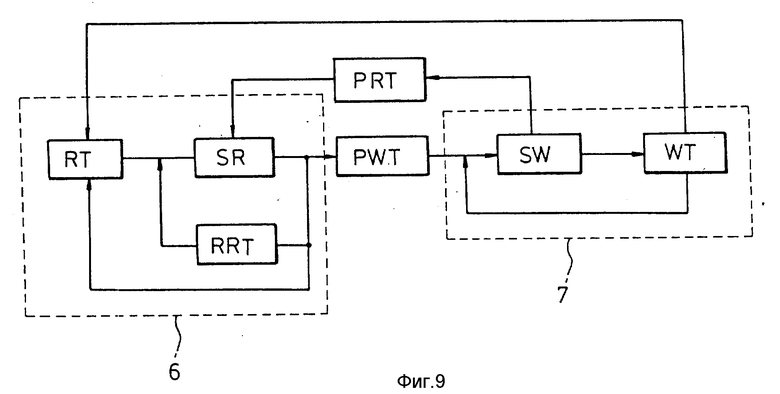

Фиг. 9 представляет диаграмму режимных переходов, иллюстрирующую операционное состояние SAM в соответствии с настоящим изобретением.

Со ссылками на фиг. 1 ниже описана работа известной видеопамяти VRAM 10. Порт RAM 1, имеющийся в видеопамяти VRAM 10, соединен с процессором (не изображен) через первый порт P1, в то время как порт SAM 2, имеющийся в видеопамяти VRAM 10, соединен с дисплейным устройством 3 через посредство второго порта P2. Данные, пересылаемые от процессора, произвольным образом запоминаются в порту RAM 1 через столбцовый декодер 4 и строчный декодер (не изображен). Данные, хранящиеся в порту RAM 1, пересылаются по одному строчному элементу на порт SAM 2 в режиме пересылки операции считывания РТ. В то же самое время данные пересылаются на SAM 2 порт через передающий данные вентиль DTG. Порт SAM 2 имеет последовательные регистры, соответствующие одному строчному элементу порта RAM 1, поэтому данные принимаются и выдаются последовательно по строчному элементу.

В режиме последовательного считывания SR данные, хранящиеся в порту SAM 2, выводятся на дисплейное устройство 3 через второй порт P2. Также в случае запоминания данных в порту RAM 1, непосредственно через порт SAM 2 поступающих от входного устройства, подобного первому записывающему устройству и т. п. , порт SAM 2 сначала переводится в режим псевдопересылки операции записывания PWT и затем переводится в режим последовательного записывания без пересылки данных, в результате чего данные записываются в порт SAM 2 через второй порт P2. Далее, в режиме пересылки операции записывания WT данные, хранящиеся в порту SAM 2, пересылаются в порт RAM и на этот раз эти данные пересылаются через передающий данные вентиль DTG.

В такой видеопамяти VRAM применительно к порту SAM выполняются режимы, перечисленные ниже:

- режим пересылки операции считывания RT,

- режим пересылки операции считывания в реальном масштабе времени RRT,

- режим последовательного считывания SR,

- режим последовательного записывания SW,

- режим пересылки операции записывания WT,

- режим псевдопересылки операции записывания PWT.

Обмен данными между портом RAM и портом SAM осуществляется только в режимах пересылки при установленном режиме последовательного считывания SR или режиме последовательного записывания SW. При другой модификации режима последовательного считывания SR или последовательного записывания SW порт SAM работает независимо от порта RAM. В частности, в режиме псевдопересылки операции считывания PWT обмен данными между портом RAM и портом SAM не осуществляется, а только происходит переход к режиму последовательного записывания.

Работа порта SAM обеспечивается комбинациями из шести режимов, причем переходы от режима к режиму производятся так, как иллюстрирует фиг. 8. Режимные переходы происходят последовательно только в направлении, указанном стрелкой (фиг. 8).

Каждый режим осуществляет определенные функции, описанные ниже.

(1) Режим пересылки операции считывания RT.

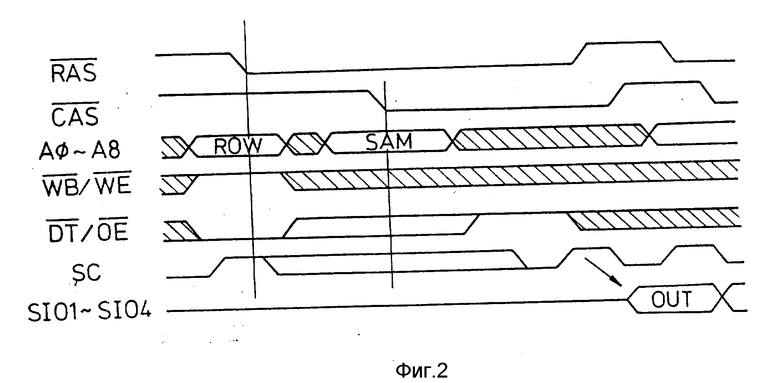

В этом режиме происходит пересылка данных объемом один строчный элемент из порта RAM в последовательные регистры порта SAM. На этот раз последний нарастающий фронт последовательного тактового сигнала SC должен идти впереди активного фронта стробирующего строчный адрес сигнала  . После окончания режима пересылки операции считывания RT устанавливается режим последовательного считывания SR для последовательного считывания данных внутренним образом. Фиг. 2 показывает временную диаграмму режима пересылки операции считывания P.

. После окончания режима пересылки операции считывания RT устанавливается режим последовательного считывания SR для последовательного считывания данных внутренним образом. Фиг. 2 показывает временную диаграмму режима пересылки операции считывания P.

На фиг. 2 сигнал  является стробом строчного адреса, сигнал

является стробом строчного адреса, сигнал  является стробом столбцового адреса, AO-A8 представляют сигналы адресов и S101-S104 являются входными-выходными сигналами. Там же,

является стробом столбцового адреса, AO-A8 представляют сигналы адресов и S101-S104 являются входными-выходными сигналами. Там же,  являются тактовым сигналом, управляющим пересылкой данных и выходом порта RAM,

являются тактовым сигналом, управляющим пересылкой данных и выходом порта RAM,  является тактовым сигналом последовательного доступа (считывания/записывания) и

является тактовым сигналом последовательного доступа (считывания/записывания) и  является последовательным разрешающим тактовым сигналом.

является последовательным разрешающим тактовым сигналом.

(2) Режим пересылки операции считывания в реальном масштабе времени RRT.

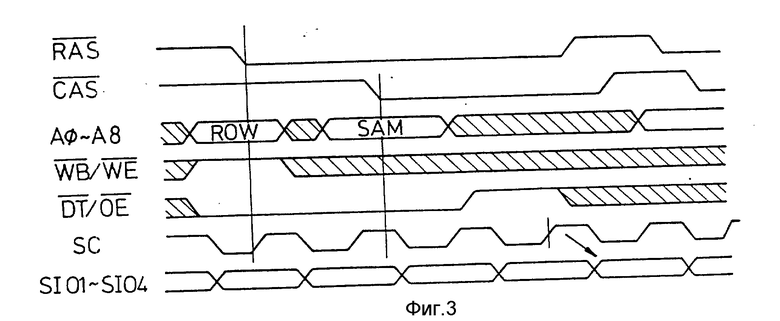

В этом режиме производится последовательная обработка потока данных, объем которых превышает размер последовательного регистра. Единственное отличие этого режима от режима пересылки операции считывания RT состоит в том, что последний такт сигнала SC и сигнал  должны быть синхронизированы. Далее, сигнал

должны быть синхронизированы. Далее, сигнал  должен быть синхронизирован с сигналами

должен быть синхронизирован с сигналами  . В этом режиме одновременно выполняется доступ в реальном времени и пересылка данных. Временная диаграмма этого режима представлена на фиг. 3.

. В этом режиме одновременно выполняется доступ в реальном времени и пересылка данных. Временная диаграмма этого режима представлена на фиг. 3.

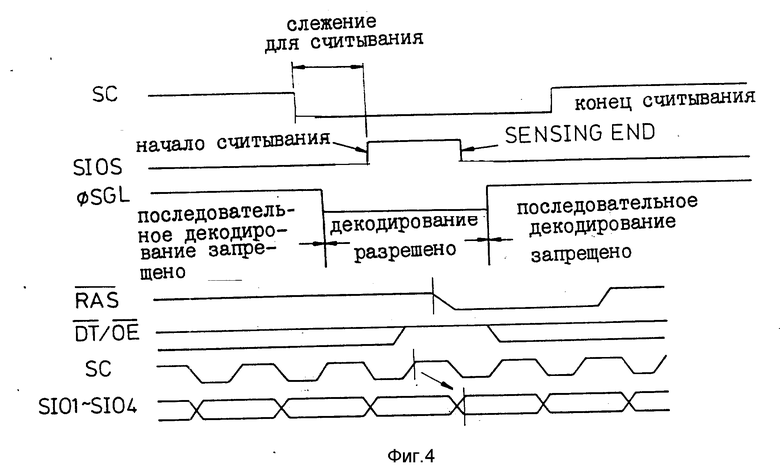

(3) Режим последовательного считывания SR.

Этот режим используется для быстрого считывания данных в последовательные регистры в соответствии с сигналом SC после того, как порт SAM установлен в этом режим режимом пересылки операции считывания RT или режимом пересылки операции считывания в реальном времени RRT. Тактовая диаграмма этого режима представлена на фиг. 4.

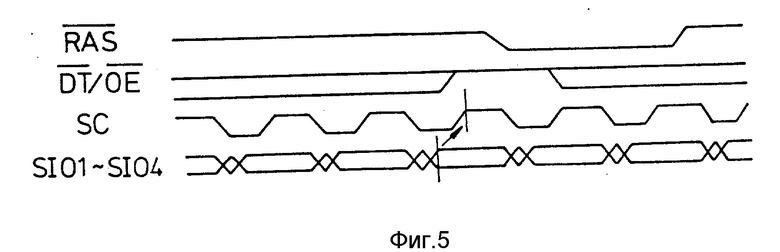

(4) Режим последовательного записывания SW.

Этот режим служит для быстрого записывания двух последовательных данных в последовательные регистры порта SAM. С точки зрения внешнего тактирования этот режим не отличается от режима последовательного считывания SR. Операция последовательного записывания выполняется по той же схеме тактирования, что и сигнал SC, поскольку этот режим устанавливается внутренним образом после режима пересылки операции записывания или режима псевдопересылки операции записывания PWT. Тактовая диаграмма этого режима представлена на фиг. 5.

(5) Режим пересылки операции записывания WT.

В этом режиме выполняется пересылка данных, которые хранятся в последовательном регистре после завершения режима последовательного записывания SW в порт RAM по одному строчному элементу. Далее, после завершения этого режима порт SAM внутренним образом переводится в режим последовательного записывания SW. Тактовая диаграмма этого режима представлена на фиг. 6.

(6) Режим псевдопересылки операции запиcывания PWT.

Пересылка данных из порта SAM в порт RAM происходит в режиме пересылки операции записывания WT после записывания данных в последовательные регистры. Чтобы выполнить режим последовательного записывания SW после режима последовательного считывания SR, порт SAM должен быть переведен в режим последовательного записывания SW. Это объясняется тем, что в порт RAM будут посланы неправильные данные, если режим пересылки операции записывания WT будет выполнен раньше, чем порт SAM будет переведен в режим последовательного записывания SW. Таким образом, данные не должны пересылаться из порта SAM в порт RAM в течение перехода от режима последовательного считывания SR в режим последовательного записывания SW. Режим псевдопересылки операции записывания PWT служит для перехода от режима последовательного считывания SR в режим последовательного записывания SW без пересылки данных. Временная диаграмма этого режима представлена на фиг. 7. Работу порта SAM определяют шесть режимов, названных выше, которые выполняются в последовательности, проиллюстрированной на фиг. 8.

Фиг. 8 иллюстрирует последовательность смены режимов, определяющих работу порта SAM известного двухпортового запоминающего устройства. На фиг. 8 изображены цикл пересылки операции считывания 6, цикл пересылки операции записывания 7 и режим псевдопересылки операции записывания PWT между циклом пересылки операции считывания 6 и циклом пересылки операции записывания 7. Режим последовательного считывания SR выполняется лишь в том случае, если предварительно выполнена пересылка считывания или операция пересылки считывания в реальном времени. В видеопамяти VRAM режим пересылки операции считывания RT или режим пересылки операции считывания в реальном масштабе времени RRT исходно устанавливается аппаратными средствами. Поэтому при пересылке данных из порта RAM в порт SAM данные порта RAM пересылаются в порт SAM по одному строчному элементу в режиме пересылки операции считывания RT или режиме пересылки операции считывания в реальном времени RRT. Данные, хранящиеся в последовательных регистрах, быстро считываются в режиме последовательного считывания SR и также пересылаются на дисплейное устройство.

С другой стороны, чтобы данные от внешнего устройства непосредственно поступали в порт SAM, сначала надо установить режим последовательного записывания SW. Именно, для перехода от режима последовательного считывания SR в режим последовательного записывания SW надо выполнить режим псевдопересылки операции записывания PWT. В режиме псевдопересылки операции записывания PWT пересылка данных не осуществляется. В режиме последовательного записывания SW данные, поступающие от внешнего устройства, могут непосредственно поступать для запоминания в порт SAM. Дополнительно, чтобы вновь считать данные, запомненные в порту SAM, этот режим надо заменить на режим последовательного считывания SP, однако нельзя непосредственно от режима последовательного записывания SW перейти к режиму последовательного считывания SR, как это видно на фиг. 8. Поэтому после перехода от режима последовательного записывания SW в режим пересылки операции записывания WT данные, находящиеся в последовательных регистрах порта SAM, пересылаются в порт RAM в режиме пересылки операции записывания WT. Чтобы вновь переслать данные, хранящиеся в порту RAM, в порт SAM после того, как данные записаны в порт SAM при выполнении режима пересылки операции считывания RT, данные, хранящиеся в порту SAM, считываются в режиме последовательного считывания SR. Поэтому при тестировании SAM порта на исправность путем сравнения исходных данных с данными, считываемыми из порта SAM, должен осуществляться режим пересылки операции считывания RT, в результате чего всегда происходит обмен данными между портом RAM и портом SAM, а потому нет возможности тестировать SAM независимо.

Фиг. 9 представляет последовательность переходов от режима к режиму, иллюстрирующую работу SAM в двухпортовом запоминающем устройстве, соответствующем настоящему изобретению. Как видно, на фиг. 9 есть цикл пересылки операции считывания 6 и цикл пересылки операции записывания 7, аналогичные изображенным на фиг. 8. Дополнительно, режим псевдопересылки операции считывания RRT и режим псевдопересылки операции записывания PWT вставлены между циклом пересылки операции считывания 6 и циклом пересылки операции записывания 7. Основные операции цикла пересылки при считывании 6 и цикла пересылки при записывании 7 идентичны представленным на фиг. 8; режим псевдопересылки операции записывания, служащий для перехода от цикла пересылки при считывании 6 к циклу пересылки при записывании 7, также идентичен с представленным на фиг. 8.

Однако в соответствии с настоящим изобретением, как видно на фиг. 9, порт SAM можно переводить из режима последовательного записывания SW в режим последовательного считывания SR посредством режима псевдопересылки операции считывания RRT без пересылки данных для выполнения тестирования SAM путем сравнения исходных данных с данными, считываемыми из порта SAM. Это значит, что если режим псевдопересылки операции считывания RRT выполняется после запоминания данных внешнего устройства в порту SAM в режиме последовательного записывания SW, порт SAM переходит в режим последовательного считывания без пересылки данных. Поэтому данные, хранящиеся в порту SAM, считываются для сравнения с исходными данными для проверки порта SAM на исправность.

Описанная выше операция ниже разъясняется со ссылками на фиг. 1. После изготовления видеопамяти VRAM процессами полупроводниковой технологии RAM и порт SAM проверяют на пластинчатом (вафельном) устройстве для обнаружения неисправностей. Тестирование RAM выполняют известным способом. Чтобы тестировать SAM при массовом изготовлении видеопамяти VRAM, делают контактные площадки, используемые лишь пластинчатым устройством, образующие третий порт P3. Далее режим псевдопересылки операции считывания RRT для переключения с режима последовательного записывания SW на режим последовательного считывания SR осуществляется управляющими тактовыми сигналами управляющей части 5. Когда VRAM изготавливается на пластине и тестируется порт SAM, сначала выполняется режим последовательного записывания SW в цикле пересылки при записывании 7. В это время тестовые данные запоминаются в порту SAM 2, поступая через порт P2, и режим псевдопересылки при считывании выполняется по тактовым сигналам от управляющей части 5, причем третий порт P3 служит для передачи данных, хранящихся в порту SAM 2, во второй порт P2. Затем порт SAM переводится в режим последовательного считывания SR без пересылки данных между портом SAM и портом RAM. Данные, хранящиеся в порту SAM, считываются в режиме последовательного считывания SR, для того, чтобы их можно было сравнить с исходными данными для проверки исправности порта SAM.

Как сказано выше, в соответствии с настоящим изобретением порт RAM и порт SAM можно весьма просто проверять на исправность на пластинчатом устройстве в процессе массового изготовления двухпортовых запоминающих устройств, имеющих порт RAM и SAM. В частности, в соответствии с настоящим изобретением можно весьма просто проверить порт SAM на исправность тестированием именно SAM, поскольку порт SAM можно перевести из режима последовательного записывания SW в режим последовательного считывания SR через посредство режима псевдопересылки операции записывания PWT без пересылки данных.

Настоящее изобретение не ограничивается описанным вариантом осуществления. Специалистам в данной области должны быть ясны разнообразные модификации описанного варианта осуществления, а также другие варианты осуществления настоящего изобретения из приведенного описания. Предполагается исходя из сказанного, что приложенная формула изобретения перекрывает все подобные модификации и варианты осуществления, находящиеся в пределах объема изобретения.

Изобретение относится к способу управления работой порта последовательного доступа к видеопамяти, имеющей порт памяти произвольного доступа - RAM и порт памяти последовательного доступа - SAM. Порт SAM можно перевести из режима "Последовательная запись" - SW в режим "Последовательное считывание" - SR через посредство режима "Считывание - псевдопересылка" RRT без пересылки данных для сравнения исходных данных с данными, считываемыми из порта SAM, при тестировании SAM. Способ позволяет осуществлять проверку на исправность порт RАM и порт SAM на пластинчатом устройстве в процессе массового изготовления двухпортовых запоминающих устройств. 2 з.п.ф-лы, 9 ил.

| SU, авторское свидетельство, 1298754, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| US, патент, 4703449, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1348860, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| WO, заявка РСТ/US 88/00613, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-04-20—Публикация

1990-06-22—Подача