Изобретение относится к устройствам управления буфера вывода данных из запоминающего устройства, в частности к устройствам управления предварительным зарядом выходного буферного блока для использования при детектировании перемены адреса, при которой перед тем, как истинные данные выдаются на выход, выходная клемма сдвигается к требуемому уровню за счет того, что цепь предварительного заряда подразделяется в соответствии с тем, составляют ли инверсные данные "0" или "1", и если инверсные выходные данные составляют "1", выходная клемма разряжается, а если инверсные выходные данные составляют "0", то выходная клемма заряжается.

Полупроводниковое устройство памяти записывает данные с клеммы ввода во внутренних ячейках памяти и, если необходимо, считывает запомненные данные из внутренних ячеек памяти на клемме вывода, причем при выполнении такого считывания и записи необходимо выполнить ряд внутренних этапов. Процедура вывода данных состоит из множества этапов: подачи сигнала адреса столбца, стробирования ввода/вывода, выбора линии ввода/вывода, выбора линии подачи сигнала разрешения данных, выбора шины данных и выдачи данных.

Если подан сигнал адреса столбца, то выдается стробирующий импульс для выбора клеммы ввода/вывода, а затем выбирается линия ввода/вывода. Затем на этапах выбора линии ввода/вывода и линии подачи сигнала разрешения данных выполняется второе считывание, чтобы повысить малое напряжение линии ввода/вывода до более высокого напряжения, выбрать шину данных и выдать сигнал данных.

Между шиной данных и клеммой вывода данных требуется преобразование сигнала данных, так чтобы уровень сигнала, который был перед шиной данных КМОП-уровня, на ее выходе стал ТТЛ-уровнем. Соответственно, чтобы сдвигать уровень сигнала, используется буфер вывода.

Обычно для сдвига уровня буфера вывода использовались схемы, в которых схема предварительного заряда благодаря действию импульса управления предварительным зарядом удерживается вместе с МОП-транзисторами М1, М2 во включенном или выключенном состоянии, в результате чего создается цепь постоянного тока.

Известны схемы, в которых рассеяние постоянного тока может быть предотвращено путем стробирования импульса управления предварительным зарядом DCPP, но в этом случае, когда инверсные данные имеют уровень "0", клемма вывода данных не может быть предварительно заряжена до высокоимпедансного уровня, а кроме того, в секции предварительного заряда требуется использование МОП-транзистора большого размера.

Целью изобретения является создание устройства управления предварительным зарядом выходного буферного блока, в котоpом шумы, возникающие на выходной стороне секции предварительного заряда, могут быть устранены и скорость обработки данных в схеме, управляемой детектированием перемены адреса, может быть повышена.

Другой целью изобретения является создание устройства управления предварительным зарядом, в котором секция предварительного заряда, учитывая надежность фиксатора на выходной стороне, может состоять из КМОП-транзисторов.

При достижении вышеуказанных целей в соответствии с состоянием инверсных данных ("1" или "0") возбуждаются различные МОП-транзисторы, составляющие схему предварительного заряда. При подаче уровня L ("0") инверсных данных секция предварительного заряда образует цепь заряда, так что общий уровень должен повыситься и сигнал ТТЛ-уровня будет выводиться с высокой скоростью.

При достижении вышеуказанных целей в устройстве управления предварительным зарядом в соответствии с состоянием инверсных данных на выходной стороне выходная сторона буфера вывода заряжается или разряжается в соответствии с инверсными данными от секции генерирования сигнала данных, а уровень выходной клеммы падает или возрастает заранее до того, как через выходную клемму буфера вывода подаются затем истинные данные.

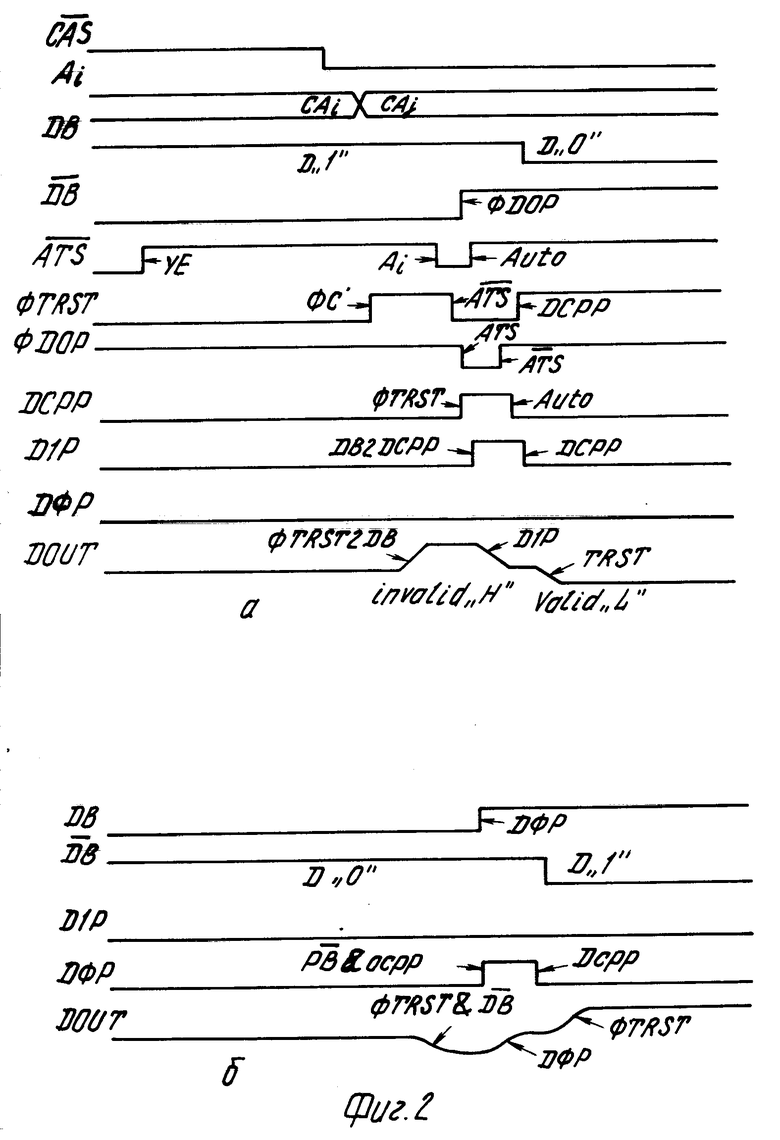

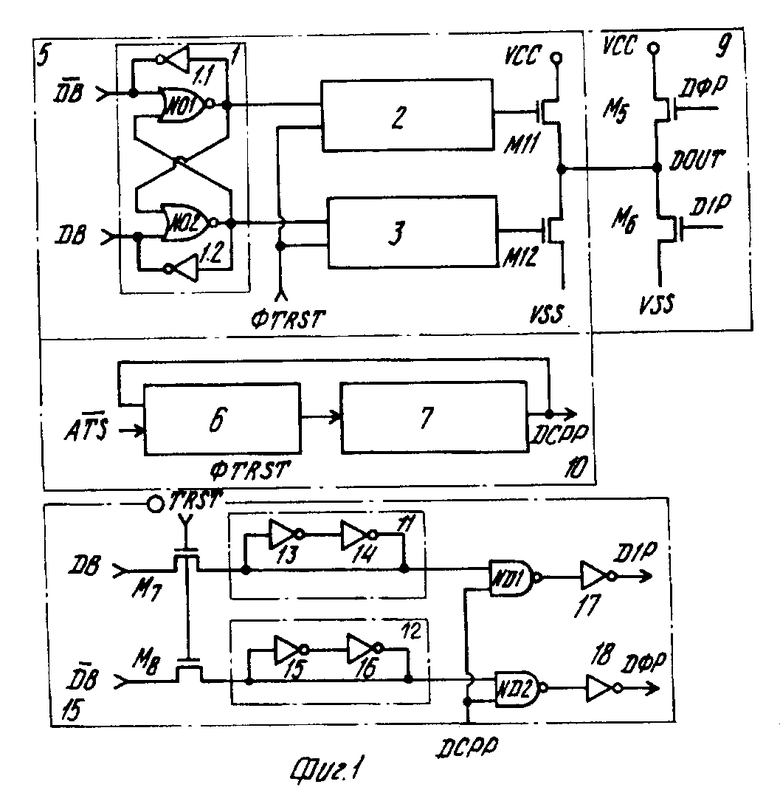

На фиг. 1 представлена схема управления предварительным зарядом буфера вывода в соответствии с изобретением; на фиг. 2а и б временные диаграммы, показывающие операции предварительного заряда буфера вывода в соответствии с изобретением.

Устройство управления предварительным зарядом содержит выходной буферный 1 элемент памяти, на который подается сигнал данных с шины данных DB,  , первый и второй формирователи 2 и 3 уровня для выдачи на выход данных "1" или "0" после приема выходного сигнала блока 1 и сигнала управления ⊘TRST, выходной буферный блок 5, состоящий из ключевых элементов М 11 и М 12, управляемых посредством выходных сигналов указанных формирователей 2 и 3, блок 10 управления предварительным зарядом, который включает формирователь 6 разрешающих импульсов для генерирования в ответ на сигналы перемены адреса

, первый и второй формирователи 2 и 3 уровня для выдачи на выход данных "1" или "0" после приема выходного сигнала блока 1 и сигнала управления ⊘TRST, выходной буферный блок 5, состоящий из ключевых элементов М 11 и М 12, управляемых посредством выходных сигналов указанных формирователей 2 и 3, блок 10 управления предварительным зарядом, который включает формирователь 6 разрешающих импульсов для генерирования в ответ на сигналы перемены адреса  сигналов управления ⊘TRST с тремя состояниями и формирователь 7 импульсов правления для подачи на выход импульсов управления предварительным зарядом, и блок 9 предварительного заряда для приема выходных сигналов DOUT блока 5.

сигналов управления ⊘TRST с тремя состояниями и формирователь 7 импульсов правления для подачи на выход импульсов управления предварительным зарядом, и блок 9 предварительного заряда для приема выходных сигналов DOUT блока 5.

Устройство содержит далее секцию 15 генерирования сигнала перемены данных для подачи сигнала данных DD⊘PP, DIP к указанному блоку 9 предварительного заряда, состоящую из буферных ключевых элементов М 7 и М 8 для подачи сигналов данных DB,  , второго и третьего буферных элементов 11 и 12 памяти для защелкивания выходных сигналов с указанных буферных ключевых элементов М 7 и М 8, элементов НЕ 17 и 8 и элементов И-НЕ ND 1 и ND 2 для совпадения сигналов указанных буферных элементов 11, 12 памяти и указанных импульсов управления предварительным зарядом DCCP от блока 10 управления предварительным зарядом.

, второго и третьего буферных элементов 11 и 12 памяти для защелкивания выходных сигналов с указанных буферных ключевых элементов М 7 и М 8, элементов НЕ 17 и 8 и элементов И-НЕ ND 1 и ND 2 для совпадения сигналов указанных буферных элементов 11, 12 памяти и указанных импульсов управления предварительным зарядом DCCP от блока 10 управления предварительным зарядом.

Блок 9 предварительного заряда состоит из ключевых элементов М 5 и М 6, которые подключены к выходной клемме DOUT буферного блока 5, причем указанный блок 9 предварительного заряда подключен к выходу буферного блока 5.

В вышеописанной конструкции сигнал данных, подаваемый на шины данных DB,  , представляет данные, передаваемые через порт ввода/вывода, а сигнал с тремя состояниями ⊘TRST появляется после задержки спадающего фронта сигнала включения адреса столбцов

, представляет данные, передаваемые через порт ввода/вывода, а сигнал с тремя состояниями ⊘TRST появляется после задержки спадающего фронта сигнала включения адреса столбцов  и определяет: должны ли данные (DB,

и определяет: должны ли данные (DB,  ) выдаваться на выходную клемму.

) выдаваться на выходную клемму.

Как показано на фиг.2а, сигнал управления ⊘TRST переходит от высокого уровня к низкому, когда сигнал перемены адреса  спадает. Посредством спадающего фронта сигнала

спадает. Посредством спадающего фронта сигнала  генерируется импульс управления предварительным зарядом DCРP импульс, имеющий автоматическую ширину AUTO.

генерируется импульс управления предварительным зарядом DCРP импульс, имеющий автоматическую ширину AUTO.

Импульс заряда линии шины данных ⊘DOP имеет функцию предварительного заряда клемм линии шины данных DB и линии подачи сигнала разрешения данных D1 в то время, когда сигнал перемены адреса  имеет уровень L.

имеет уровень L.

Сначала в общих выражениях будет описано возбуждение схемы по предлагаемому изобретению. В том случае, когда на шину данных  в буферном блоке 5 загружаются данные "0", а на шину данных DB загружаются данные "1", выход элемента ИЛИ-НЕ ND 1 через элемент 1 памяти становится равным А, а выход элемента ND 2 ИЛИ-НЕ становится равным "0".

в буферном блоке 5 загружаются данные "0", а на шину данных DB загружаются данные "1", выход элемента ИЛИ-НЕ ND 1 через элемент 1 памяти становится равным А, а выход элемента ND 2 ИЛИ-НЕ становится равным "0".

Следовательно, в формирователи 2 и 3 уровня выдается сигнал уровня Н.

Если приводится в действие первый формирователь 2, имеющий данные "1", тогда сигнал уровня Н подается на ключевой элемент М 11, так что выходная клемма DOUT приобретает состояние уровня "1" (уровень Н), тогда как если приводится в действие второй формирователь 3, имеющий данные "0", тогда уровень Н сигнала включает ключевой элемент М 12, так что выходная клемма DOUT приобретает состояние уровня Н.

Теперь, обращаясь к фиг.2а, будет описана работа схемы по изобретению для случая состояния "1" инверсных данных.

Когда вырабатывается сигнал разрешения цепи  , который представляет механический машинный цикл, включается (в состояние Н) сигнал ⊘TRST ("С") управления буферного блока 5. В этом случае адрес столбцов CAi представляет инверсный адрес, а CAj представляет истинный адрес столбцов. Если ячейка данных, соответствующая инверсному адресу столбцов CAi, представляет "1", а ячейка данных, соответствующая истинному адресу столбцов CAj, представляет "0", уровень выходной клеммы DOUT, когда включается сигнал ⊘TRST (состояние "1"), возрастает от высокоимпедансного уровня до высокого напряжения. В этот момент включаются буферные ключевые элементы М 7 и М 8 и элемент 11 памяти переходит в уровень Н, а элемент 12 памяти в уровень L. Затем адрес столбцов изменяется от CAi к CAj и, следовательно, сигнал перемены адреса

, который представляет механический машинный цикл, включается (в состояние Н) сигнал ⊘TRST ("С") управления буферного блока 5. В этом случае адрес столбцов CAi представляет инверсный адрес, а CAj представляет истинный адрес столбцов. Если ячейка данных, соответствующая инверсному адресу столбцов CAi, представляет "1", а ячейка данных, соответствующая истинному адресу столбцов CAj, представляет "0", уровень выходной клеммы DOUT, когда включается сигнал ⊘TRST (состояние "1"), возрастает от высокоимпедансного уровня до высокого напряжения. В этот момент включаются буферные ключевые элементы М 7 и М 8 и элемент 11 памяти переходит в уровень Н, а элемент 12 памяти в уровень L. Затем адрес столбцов изменяется от CAi к CAj и, следовательно, сигнал перемены адреса  во время длительности импульса переходит к уровню L. Как показано ранее, если сигнал

во время длительности импульса переходит к уровню L. Как показано ранее, если сигнал  переходит от уровня Н к уровню L, указанным блоком 10 генерируется импульс автоматического предварительного заряда DCPP.

переходит от уровня Н к уровню L, указанным блоком 10 генерируется импульс автоматического предварительного заряда DCPP.

Секция 15 генерирования сигнала перемены данных работает таким образом, что при подаче сигнала управления с тремя состояниями ⊘TRST, благодаря действию элементов И-НЕ ND 1 и ND 2 и элементов НЕ 17 и 18, данные шин данных  и DB должны подаваться через буферные ключевые элементы М 7 и М 8, а данные DIP, DD⊘PP должны подаваться на выход через элементы 11 и 12 памяти.

и DB должны подаваться через буферные ключевые элементы М 7 и М 8, а данные DIP, DD⊘PP должны подаваться на выход через элементы 11 и 12 памяти.

Когда включается импульс управления предварительным зарядом DCPP, данные DD⊘PP, DIP генерируются в соответствии с состоянием инверсных данных, которые подаются через шины данных  и DB. Если инверсные данные представляют "1", данные DIP будут иметь уровень Н, а длинные DD⊘PP будут иметь уровень L, тогда как если инверсные данные представляют "0", данные DD⊘P P будут генерировать сигнал уровня Н, а данные DIP будут генерировать сигнал уровня L, подаваемые на ключевые элементы М 5, М 6 блока 9 предварительного заряда.

и DB. Если инверсные данные представляют "1", данные DIP будут иметь уровень Н, а длинные DD⊘PP будут иметь уровень L, тогда как если инверсные данные представляют "0", данные DD⊘P P будут генерировать сигнал уровня Н, а данные DIP будут генерировать сигнал уровня L, подаваемые на ключевые элементы М 5, М 6 блока 9 предварительного заряда.

Сигналы данных, которые подаются через шины данных DB и  , подаются через элемент 1 памяти, состоящий из элементов ИЛИ-НЕ NO1, NO2 и элементов 11 и 12 памяти, на формирователи 2 и 3 уровня, откуда на ключевые элементы М 11 и М 12 подаются сигналы управления с тремя состояниями ⊘TRST.

, подаются через элемент 1 памяти, состоящий из элементов ИЛИ-НЕ NO1, NO2 и элементов 11 и 12 памяти, на формирователи 2 и 3 уровня, откуда на ключевые элементы М 11 и М 12 подаются сигналы управления с тремя состояниями ⊘TRST.

В результате, если инверсные данные представляют "1", сигнал данных DIP будет иметь уровень Н, включая ключевой элемент М 6 блока 9 предварительного заряда, и, следовательно, выходная клемма DOUT разряжается через ключевой элемент М 6, понижая тем самым инверсный уровень напряжения DOUT перед достижением истинных данных "1".

С другой стороны, если инверсные данные представляют "0", сигнал данных DD⊘PP будет иметь уровень Н, включая ключевой элемент М 6. Соответственно, выходная клемма DOUT заряжается через ключевой элемент М 5, тем самым повышая инверсный уровень напряжения DOUT перед достижением истинных данных Н.

В результате можно в значительной степени уменьшить шумы и весьма повысить скорость.

Если инверсные данные имеют уровень Н, на выходной клемме DOUT (фиг.2а) вырабатывается выходной сигнал, состоящий из комбинации сигнала управления ⊘TRST и сигнала состояния шины данных DB. Если инверсные данные представляют "1", в течение постоянного времени включается ключевой элемент М 6, первоначально понижая уровень вместе с сигналом DIP.

Соответственно, истинные данные, подаваемые в следующий адресный сегмент CAj, загружаются на пониженном уровне, тем самым уменьшая шумы и повышая скорость.

Теперь будет дано описание уровня выходной клеммы DOUT для случая, когда инверсные данные имеют уровень L, как показано на фиг.2б.

В этом случае, как в случае, представленном на фиг.2а, инверсные данные "0" будут загружаться в сегмент адреса CAi адреса колонок Ai, а истинные данные "1" будут загружаться в сегмент адреса CAj.

Поэтому выходная клемма DOUT создаст выходной сигнал, состоящий из комбинации сигнала управления с тремя состояниями ⊘TRST и сигнала состояния шины данных  , причем инверсные данные представляют уровень L, и ключевой элемент М 5 включается в состояние "0" инверсных данных, чтобы повысить первоначально уровень вместе с сигналом данных DD⊘P P.

, причем инверсные данные представляют уровень L, и ключевой элемент М 5 включается в состояние "0" инверсных данных, чтобы повысить первоначально уровень вместе с сигналом данных DD⊘P P.

Соответственно, истинные данные, загружаемые в следующий сегмент адреса СAj, загружаются на повышенном уровне, тем самым уменьшая шумы и повышая скорость.

Как показано выше, в соответствии с предлагаемым изобретением выходная сторона заряжается или разряжается в соответствии с тем, представляет ли состояние инверсных данных "1" или "0", в результате чего время перехода от инверсных данных к истинным данным и шумы могут быть уменьшены и истинные данные подаются в состоянии, заряженном или разряженном заранее, так что скорость обработки может быть повышена.

В частности, блок 9 предварительного заряда в соответствии с предлагаемым изобретением использует n-канальные МОП-транзисторы, в результате чего гарантируется надежность во время работы фиксатора и тому подобного, делая возможным использовать в буфере вывода МОП-транзисторы малого размера.

Изобретение относится к вычислительной технике. Его использование в запоминающих устройствах с произвольной выборкой позволяет повысить скорость и снизить шумы переключения. Устройство содержит буферный элемент 1 памяти, ключевые элементы М 11 и М 12 выходного буферного блока 5, ключевые элементы М 5 и М 6 блока 9 предварительного заряда, буферные ключевые элементы М 7 и М 8, элементы И НЕ N D 1 и N D 2, элементы НЕ 17 и 18 и блок 10 управления предварительным зарядом. Технический результат достигается благодаря введению буферных элементов 11 и 12 памяти, формирователей 2 и 3 уровня и выполнению блока 10 на формирователе 6 разрешающих импульсов и формирователе 7 импульсов управления. 1 з. п. ф-лы, 2 ил.

| Патент США N 4658382, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1995-12-27—Публикация

1990-06-08—Подача