Изобретение относится к полупроводниковой памяти и в частности к синхронной динамической памяти с произвольным доступом, которая способна обеспечивать обращение к матрице ячеек памяти синхронно к системным синхроимпульсом от внешней системы, такой как центральный процессор (CPU).

Компьютерная система обычно включает CPU для выполнения команд по данным задачам и главную память для хранения данных, программ и тому подобного, запрашиваемого CPU. Для того чтобы улучшить характеристики компьютерной системы в основном стараются увеличить быстродействие CPU, а также сделать время доступа к главной памяти как можно короче, так чтобы CPU мог работать, по крайней мере, без состояний ожидания. Циклы тактовых импульсов современных CPU, таких как последние микроконтроллеры, уменьшаются все больше и больше с тактовыми частотами 33, 66, 100 МГц и тому подобное. Однако рабочая скорость динамической памяти с произвольным доступом (DRAM) с высокой степенью интеграции, являющейся весьма дешевой с точки зрения затрат на один бит и использующаяся как главное устройство памяти, не способна поспевать за все возрастающей скоростью CPU. Для DRAM характерно минимальное время доступа по  (строб адреса строки), то есть минимальный период времени между активными состояниями

(строб адреса строки), то есть минимальный период времени между активными состояниями  во время которого сигнал

во время которого сигнал  меняет свой уровень с высокого на низкий и осуществляет вывод данных из кристалла с адресами столбцов, зафиксированными активацией

меняет свой уровень с высокого на низкий и осуществляет вывод данных из кристалла с адресами столбцов, зафиксированными активацией  (строб адреса столбца). Такое время доступа по

(строб адреса столбца). Такое время доступа по  называется "задержка от RAS" (задержка выдачи данных при активации сигнала PA), а время между активацией сигнала

называется "задержка от RAS" (задержка выдачи данных при активации сигнала PA), а время между активацией сигнала  и выводом данных из кристалла называется "задержка от

и выводом данных из кристалла называется "задержка от  " (задержка выдачи данных при активации сигнала

" (задержка выдачи данных при активации сигнала  ). Кроме того, требуется время регенерации перед последующим выполнением цикла или операции чтения. Эти факторы уменьшают общую рабочую скорость DRAM, приводя к возникновению состояний ожидания CPU.

). Кроме того, требуется время регенерации перед последующим выполнением цикла или операции чтения. Эти факторы уменьшают общую рабочую скорость DRAM, приводя к возникновению состояний ожидания CPU.

Чтобы компенсировать разрыв между быстродействием CPU и быстродействием главной памяти, подобной DRAM, компьютерная система включает расширенную высокоскоростную буферную память, такую как кэш-память, которая располагается между CPU и главной памятью. Кэш-память запоминает данные, запрашиваемые CPU из главной памяти. Когда CPU запрашивает данные, контроллер кэш-памяти перехватывает запрос и проверяет кэш-память на предмет наличия в ней этих данных. Если необходимые данные там имеются, то это называется "кэш-попаданием", и высокоскоростная передача данных немедленно выполняется из кэш-памяти в CPU. Если же они там отсутствуют, то это называется "кэш-промах", и контроллер кэш-памяти считывает данные из более медленной главной памяти. Эти считанные данные сохраняются в кэш-памяти и посылаются в CPU. Таким образом по следующему запросу этих данных они могут быть немедленно считаны из кэш-памяти. В случае кэш-попадания может быть осуществлена высокоскоростная передача данных из кэш-памяти. Однако в случае кэш-промаха нельзя ожидать высокоскоростной передачи данных из главной памяти, что вызывает состояния ожидания CPU. Таким образом чрезвычайно важно разработать DRAMы, применяемые в качестве главной памяти, так чтобы обеспечить высокоскоростную работу.

Передача данных между DRAM и CPU или кэш-памятью осуществляется последовательными блоками информации или данных. Для передачи последовательных данных с высокой скоростью в DRAM реализуются различные виды рабочих режимов, такие как страничный, статических столбцов, полубайтный и т.п. Эти рабочие режимы описаны в патентах США N 3969706 и N 4750839. Матрица ячеек памяти DRAM с полубайтным режимом разделена на четыре равные части, так что множество ячеек памяти может быть доступно по одним и тем же адресам. Данные временно хранятся в сдвиговом регистре, так чтобы их можно было последовательно считывать и записывать. Однако так как DRAM с полубайтным режимом не может пересылать непрерывно более 5-битовых данных, такая система не может быть предложена для применения в высокоскоростных системах передачи данных. Страничный режим и режим статических столбцов, после выбора одного и того же строчного адреса в течение одного  периода, могут последовательно обращаться к адресам столбцов синхронно с

периода, могут последовательно обращаться к адресам столбцов синхронно с  переключениями, или циклами, и обнаружением перемещения адресов столбцов соответственно. Однако так как PAM со страничным и статических столбцов режимами нуждается в дополнительном времени, таком как время установки и время хранения адресов столбцов, для приема следующего адреса столбца после выбора предыдущего, невозможно обращаться к связным данным с частотой обращения к памяти выше 100 бит/с, то есть, невозможно уменьшить время

переключениями, или циклами, и обнаружением перемещения адресов столбцов соответственно. Однако так как PAM со страничным и статических столбцов режимами нуждается в дополнительном времени, таком как время установки и время хранения адресов столбцов, для приема следующего адреса столбца после выбора предыдущего, невозможно обращаться к связным данным с частотой обращения к памяти выше 100 бит/с, то есть, невозможно уменьшить время  цикла ниже 10 нс. Также, так как какое-либо уменьшение времени

цикла ниже 10 нс. Также, так как какое-либо уменьшение времени  цикла в страничном режиме не может гарантировать достаточное время для выбора столбца для записи данных в выбранную ячейку памяти во время операции записи, то в память могут быть записаны данные с ошибками. Однако так как эти высокоскоростные рабочие режимы не синхронизированы с системными синхроимпульсами CPU, всякий раз, когда CPU заменяется на более скоростной, система пересылки данных должна использовать заново разработанный DRAM-контроллер. Таким образом, чтобы иметь возможность работать вместе с высокоскоростными процессорами, такими как CISK и RISK (компьютеры с упрощенным набором команд), необходимо такое развитие синхронных DRAM, которое сделало бы возможным обращение к данным синхронно с системным тактовым импульсом микропроцессора при высокой скорости. Упоминание о синхронных DRAM без детального раскрытия схемных решений появилось в Nikkey Microdevices in April, 1992, pages 158-161.

цикла в страничном режиме не может гарантировать достаточное время для выбора столбца для записи данных в выбранную ячейку памяти во время операции записи, то в память могут быть записаны данные с ошибками. Однако так как эти высокоскоростные рабочие режимы не синхронизированы с системными синхроимпульсами CPU, всякий раз, когда CPU заменяется на более скоростной, система пересылки данных должна использовать заново разработанный DRAM-контроллер. Таким образом, чтобы иметь возможность работать вместе с высокоскоростными процессорами, такими как CISK и RISK (компьютеры с упрощенным набором команд), необходимо такое развитие синхронных DRAM, которое сделало бы возможным обращение к данным синхронно с системным тактовым импульсом микропроцессора при высокой скорости. Упоминание о синхронных DRAM без детального раскрытия схемных решений появилось в Nikkey Microdevices in April, 1992, pages 158-161.

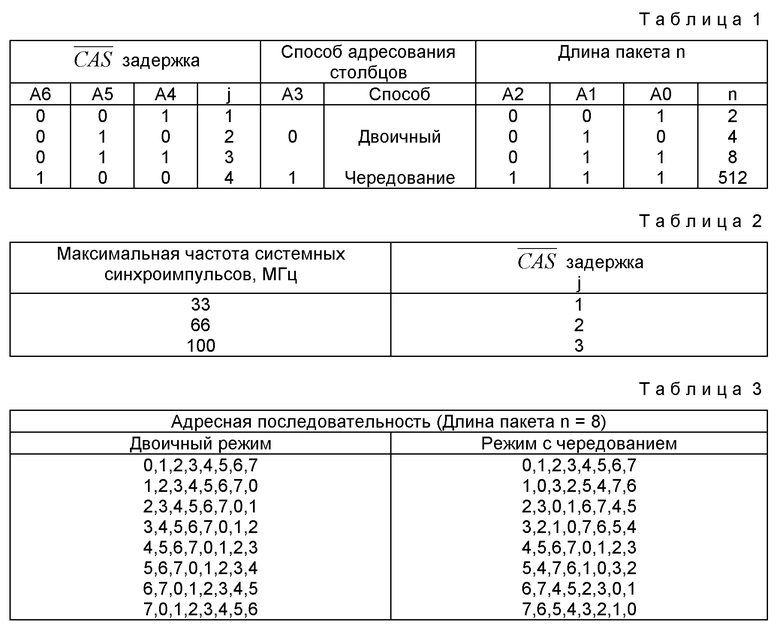

Для повышения удобства использования и расширения области применения желательно разрешить синхронной DRAM на кристаллах работать не только при различных частотах системных синхроимпульсов, но также иметь возможность программировать DRAM для работы в различных режимах, таких как:

с задержкой, зависящей от частоты синхроимпульсов;

с длиной или размером пакета, определяющим количество выходных битов;

с адресацией по столбцам и т.п.

Примеры выбора рабочего режима в DRAM, описаны в патенте США N 4833650, выданном 23 мая 1989, и в патенте США N 4987325, выданном 22 января 1991, в которых преследуются те же цели. В этих прежних разработках раскрывается технология выбора одного из рабочих режимов, таких как страничный, статических столбцов и полубайтовый. Выбор рабочего режима в этих предшествующих разработках осуществляется посредством разрушения плавких перемычек с помощью лазерного луча от внешней лазерной установки или электрического тока от внешнего источника питания или с помощью специально подобранных контактных площадок. Однако в этих предшествующих технологиях может быть выбран только один рабочий режим, причем выбранный рабочий режим не может быть заменен на другой рабочий режим. Таким образом, предшествующие разработки имеют тот недостаток, что не допускается изменения рабочих режимов, если это необходимо. В основу настоящего изобретения положена задача устранить вышеперечисленные недостатки.

Поставленная задача решается тем, что создают синхронную динамическую память с произвольным доступом, с высокими характеристиками, в которой входные и выходные данные способны синхронизироваться по внешнему системному синхроимпульсу, память, которая позволяет работать с высокой скоростью передачи данных.

Эта синхронная динамическая память с произвольным доступом способна работать при различных частотах системных синхроимпульсов, а количество входных или выходных данных можно программировать.

Другой задачей, решаемой настоящим изобретением является создание вычислительного устройства, в котором вычислительные операции могли бы выполняться либо в двоичном, либо в режиме чередования.

Еще одной задачей, решаемой настоящим изобретением является создание полупроводниковой памяти, которая может запрещать выполнение ненужных внутренних операций в кристалле памяти, независимо от количества входных или выходных данных, и может устанавливать различные рабочие режимы.

Еще одной задачей, решаемой настоящим изобретением, является создание полупроводниковой памяти, включающей схему пересылки данных для обеспечения восстановления и пересылки данных, действующую с высокой скоростью передачи данных, и содержащей, по крайней мере, два банка памяти, рабочие режимы которых могут устанавливаться в полупроводниковой памяти на кристалле.

В соответствии с первым аспектом настоящего изобретения полупроводниковая память, сформированная на полупроводниковом кристалле, имеющем различные рабочие режимы, включает в себя входное адресное устройство для приема внешнего адреса, указывающего, по меньшей мере, на один из рабочих режимов кристалла, устройство для генерирования управляющего сигнала установки режима для операции установки режима и устройство для хранения кодов, основанных на внешнем адресе, в соответствии с управляющим сигналом установки кода и формирования сигнала рабочего режима, представляющего рабочий режим, определенный этими кодами.

В соответствии с другим аспектом настоящего изобретения полупроводниковая память, имеющая множество рабочих режимов, включает устройство для формирования сигнала превышения потенциала источника питания заранее заданного уровня и устройство для автоматического хранения множества кодовых сигналов в соответствии с указанным сигналом превышения и формирования внутреннего сигнала рабочего режима, указывающего на внутренние рабочие режимы, определяемые кодовыми сигналами.

В соответствии с другим аспектом настоящего изобретения динамическая память с произвольным доступом включает:

множество банков памяти, причем каждый банк содержит множество ячеек памяти и действует либо в активном цикле, обозначающем цикл считывания, либо в цикле записи, либо в цикле регенерации;

устройство для приема строб-сигнала строчного адреса и фиксации логического уровня строб-сигнала строчного адреса в ответ на передний либо задний фронт синхроимпульсов;

входное адресное устройство для приема сгенерированных вовне адресов, по которым выбирается один из банков памяти;

и устройство для:

приема зафиксированного логического уровня сигнала от устройства для приема и фиксации;

приема адреса от входной адресной схемы;

вывода сигнала активации к банку памяти, выбранному по адресу, и сигналов бездействия к невыбранным банкам памяти, когда зафиксированный логический уровень равен первому уровню, так что выбранный банк памяти, реагирующий на сигнал активации, работает в активном цикле, в то время как невыбранные банки памяти, реагирующие на сигналы бездействия, работают в цикле регенерации.

В соответствии с еще одним аспектом настоящего изобретения полупроводниковая память, сформированная на полупроводниковом кристалле, получающем внешний синхроимпульс и выдающем данные, считанные из ячеек памяти с помощью буферного устройства вывода данных, включает устройство дня генерирования сигнала длины пакета, отражающего время вывода данных, и выдающей данные синхронно с синхроимпульсом с помощью буферного устройства вывода данных в течение временного интервала, соответствующего сигналу длины пакета.

В соответствии с другим аспектом настоящего изобретения полупроводниковая память включает матрицу ячеек памяти, состоящую из множества ячеек памяти, разбитых по строкам и столбцам. Множество субматриц получено путем разбиения матрицы ячеек памяти в строчном направлении, причем каждая субматрица имеет множество словарных шин, подсоединенных к соответствующим столбцам ячеек памяти и множество разрядных шин, подсоединенных соответственно к соответствующим строкам ячеек памяти. Разрядные шины каждой субматрицы разделены на первые группы разрядных шин и вторые группы разрядных шин, которые соответственно разделены на первые подгруппы разрядных шин и вторые подгруппы разрядных шин. Первые группы каждой субматрицы чередуются со вторыми группами, вследствие чего первые подгруппы каждой субматрицы чередуются со вторыми подгруппами и вследствие чего магистрали ввода/вывода (1/0) расположены соответственно параллельно словарным шинам между субматрицами на их внешних сторонах. Эти магистрали разделены на первые 1/0 магистрали и вторые 1/0 магистрали, расположенные соответственно на нечетных и четных позициях. Каждая 1/0 магистраль разделена на первые 1/0 шины и вторые 1/0 шины. Первые и вторые 1/0 шины, относящиеся к первым 1/0 магистралям, соответственно соединены с помощью переключателей выбора столбца с разрядными шинами первых и вторых подгрупп первых групп смежных субматриц. Первые и вторые 1/0 шины вторых 1/0 магистралей соответственно соединены с помощью ключей выбора столбца с разрядными шинами первых и вторых подгрупп вторых групп соседних субматриц.

Далее изобретение поясняется описанием конкретных примеров его выполнения и прилагаемыми чертежами, на которых

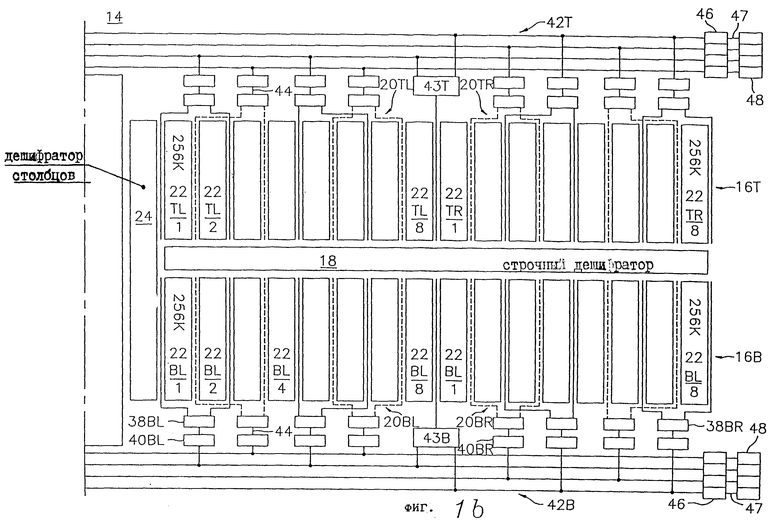

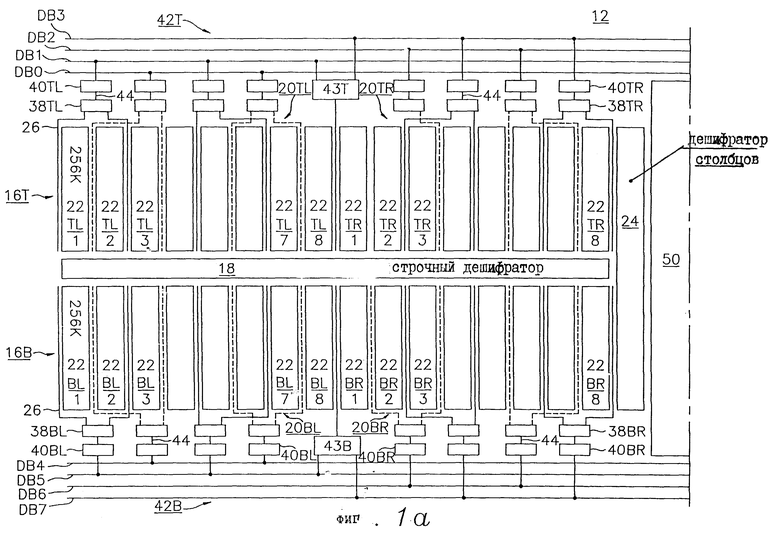

Фиг.1 изображает схему, состоящую из фигур 1a и 1b, которые представляют различные составные части, сформированные на одном и том же полупроводниковом кристалле, синхронной DRAM в соответствии с настоящим изобретением.

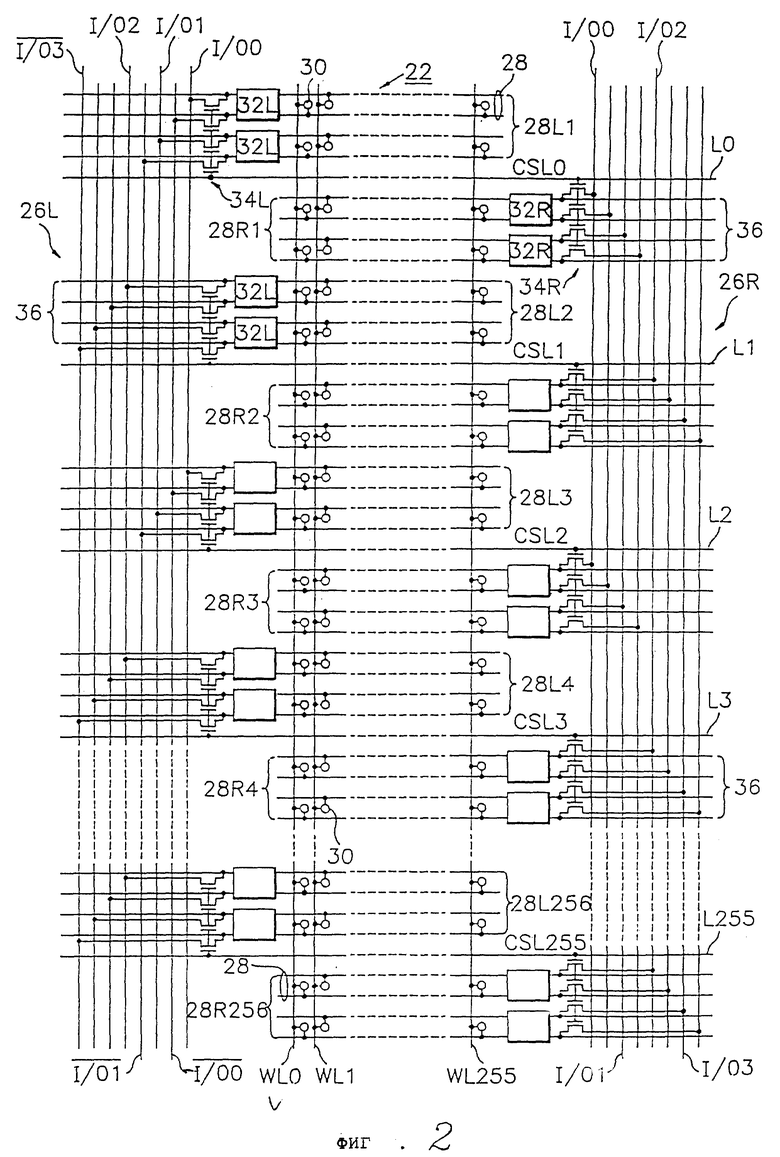

Фиг.2 представляет собой схему, показывающую организацию взаимосвязи одной из субматриц на фиг.1 с соединенными с ней шинными парами 1/0.

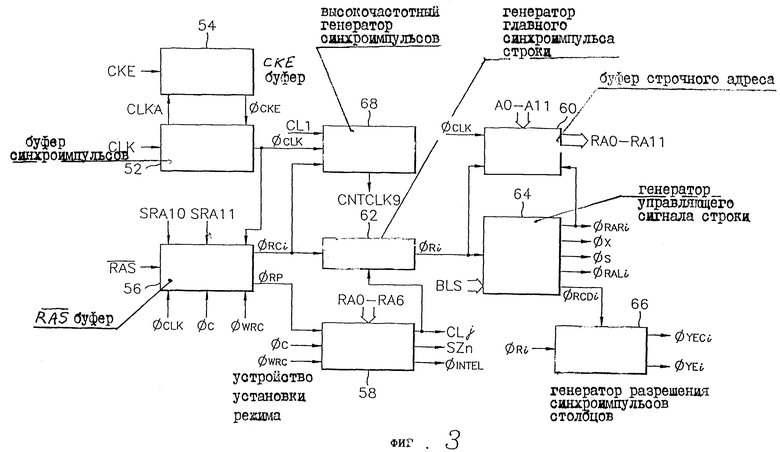

Фиг.3 представляет собой блок-схему устройства управления строками в соответствии с настоящим изобретением.

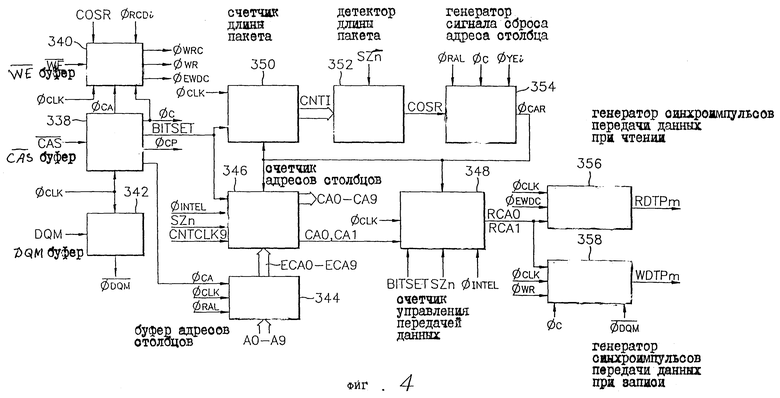

Фиг. 4 представляет собой блок-схему устройства управления столбцами в соответствии с настоящим изобретением.

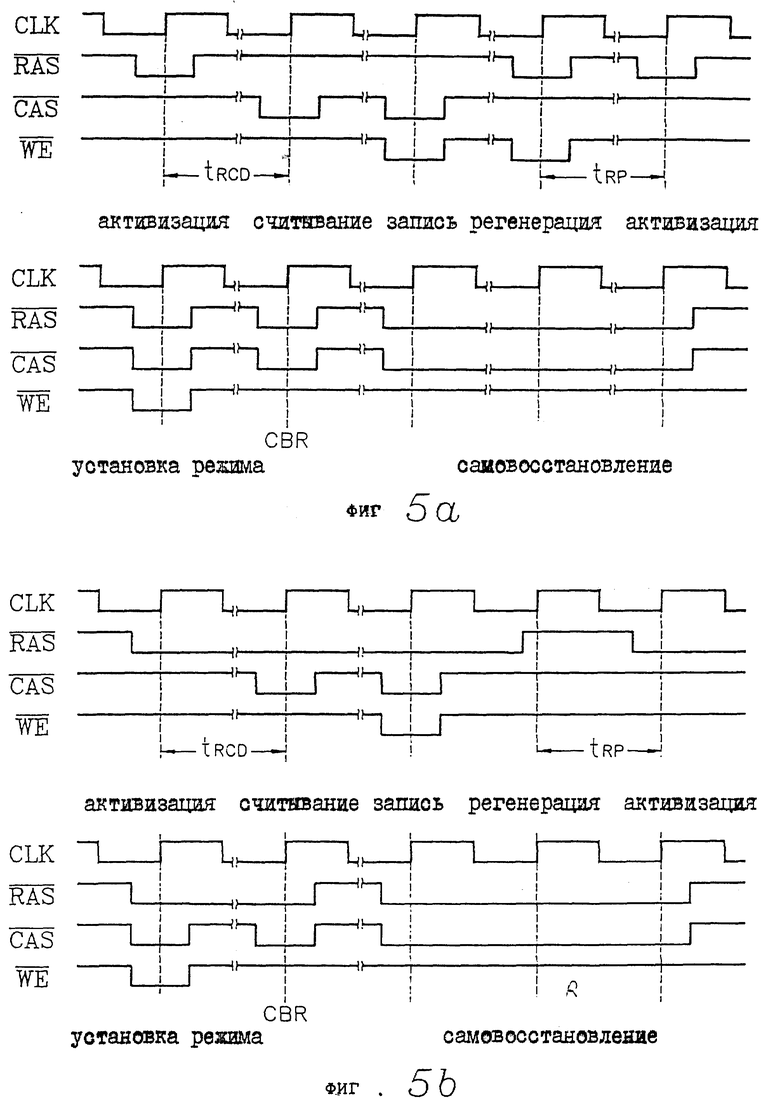

Фиг. 5a и 5b представляют собой временные диаграммы, показывающие различные команды, используемые при обработке фронта и уровня сигнала  соответственно.

соответственно.

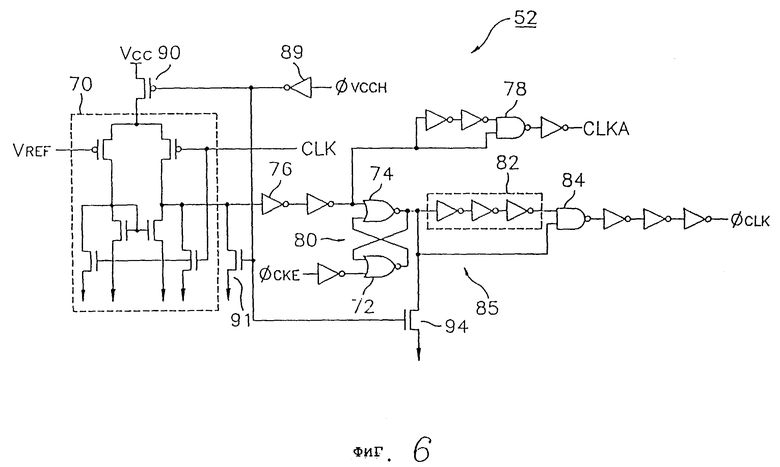

Фиг.6 представляет собой схему устройства буфера синхроимпульсов (CLK) в соответствии с настоящим изобретением.

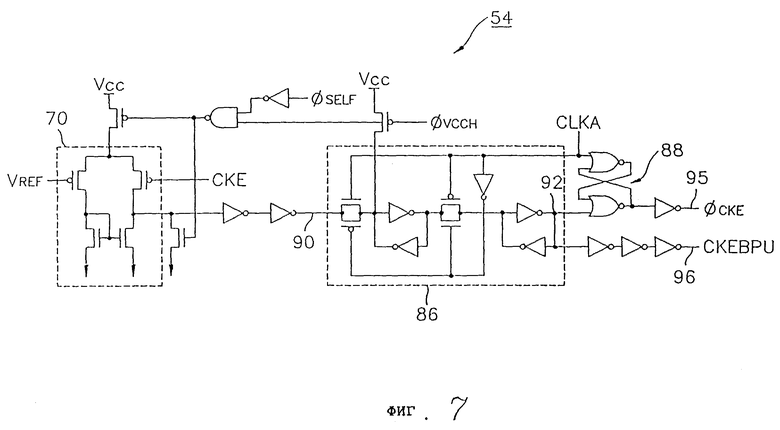

Фиг. 7 представляет собой схему устройства буфера запуска синхроимпульса (CKE) в соответствии с настоящим изобретением.

Фиг.8 представляет собой временную диаграмму CLK и CKE буферов, соответственно показанных на фиг.6 и 7.

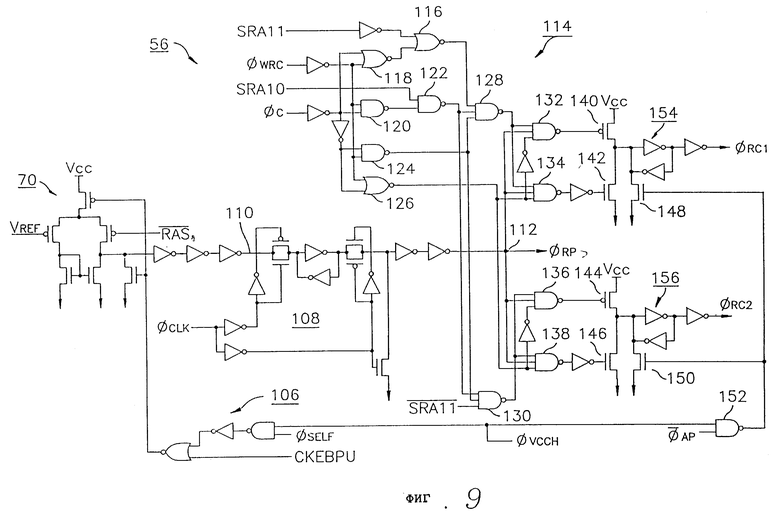

Фиг. 9 представляет собой схему многофункционального входного буфера импульсного  в соответствии с настоящим изобретением.

в соответствии с настоящим изобретением.

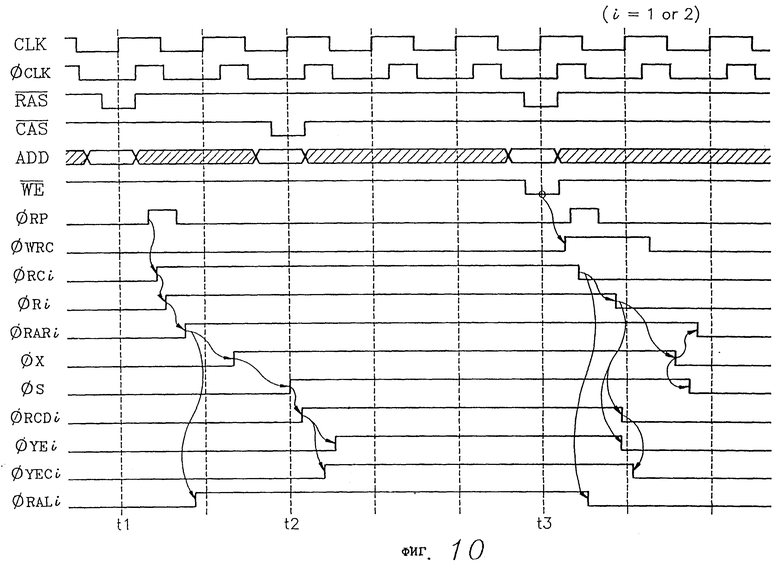

Фиг.10 представляет собой временную диаграмму управляющих сигналов столбцов и синхроимпульсов, используемых в настоящем изобретении.

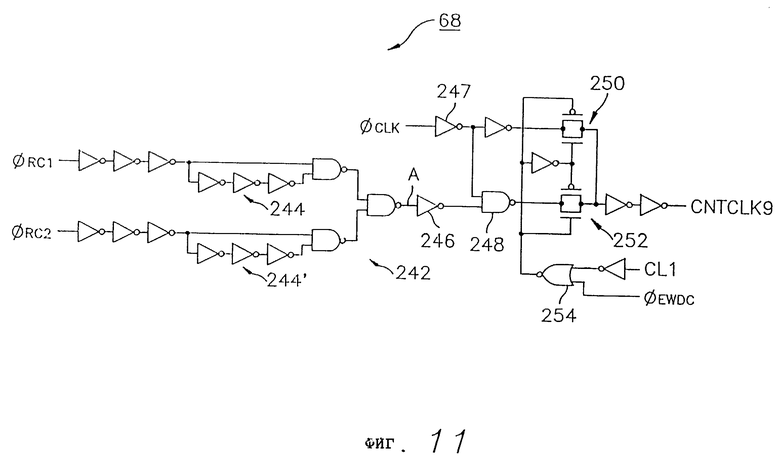

Фиг.11 представляет собой схему генератора высокочастотных синхроимпульсов для генерирования множества синхроимпульсов для регенерации в соответствии с настоящим изобретением.

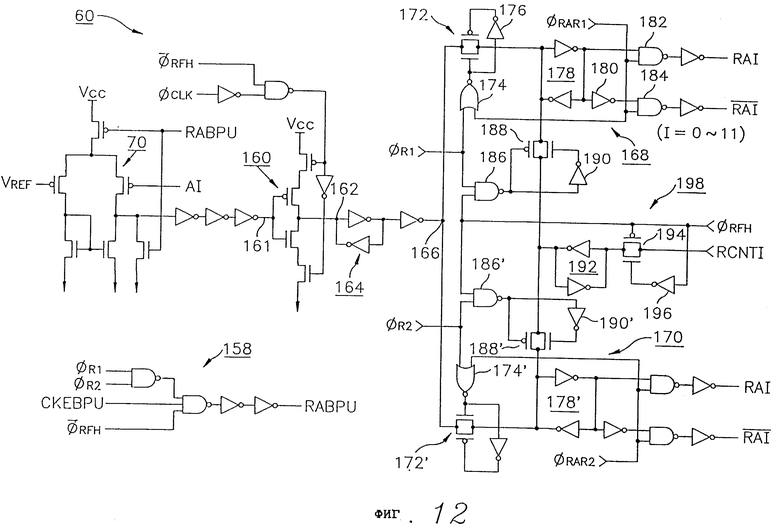

Фиг.12 представляют собой схему буфера адресов столбцов в соответствии с настоящим изобретением.

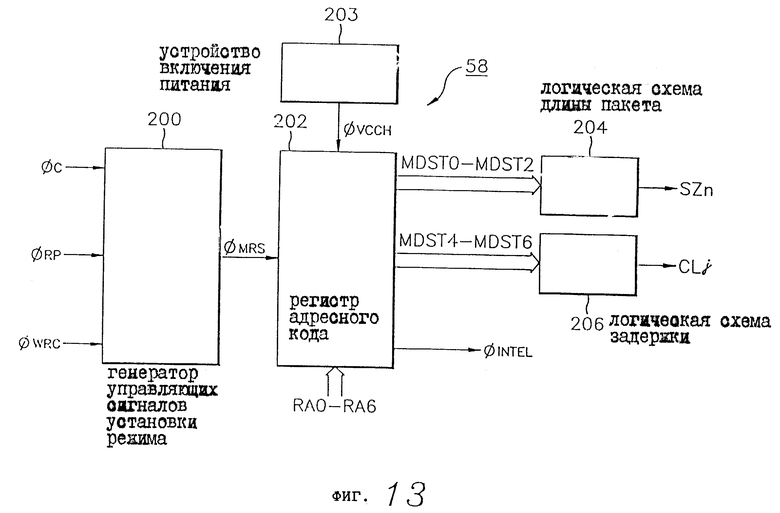

Фиг.13 представляет собой блок-схему устройства установки рабочего режима в соответствии с настоящим изобретением.

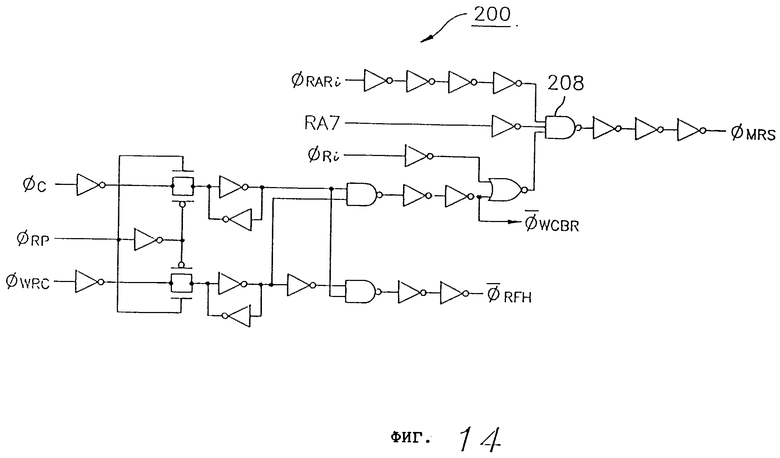

Фиг. 14 представляет собой схему устройства генерирования управляющего сигнала установки режима для схемы на фиг.13.

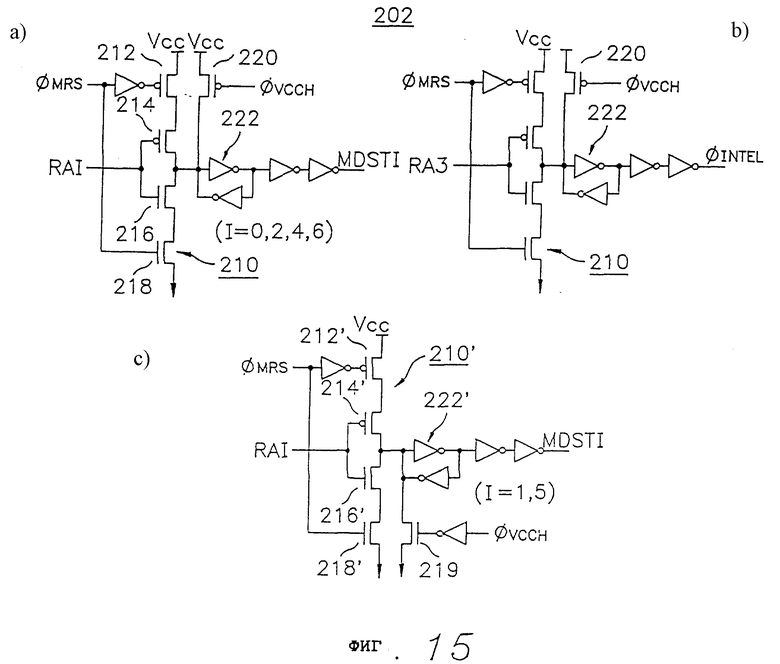

Фиг.15a-15c представляют собой схемы регистра кода адреса на фиг.13.

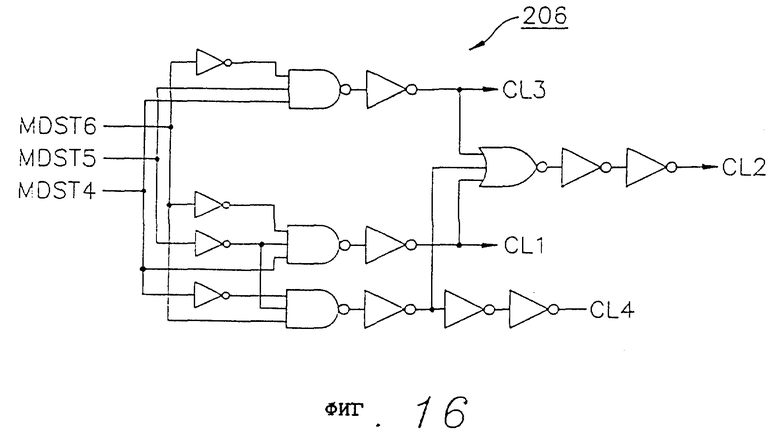

Фиг. 16 представляет собой схему логического устройства задержки на фиг. 13.

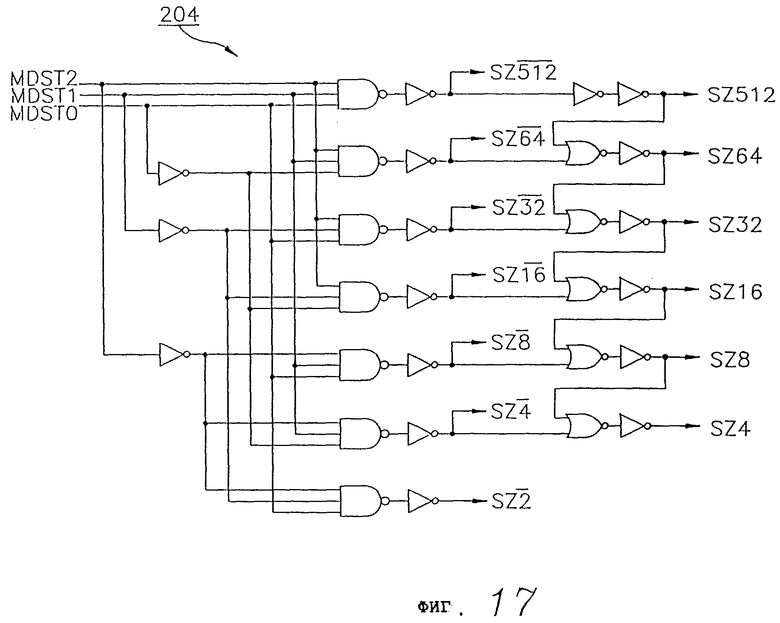

Фиг. 17 представляет собой схему логического устройства длины пакета на фиг.13.

Фиг.18 представляет собой схему устройства формирования управляющего сигнала авторегенерации в соответствии с настоящим изобретением.

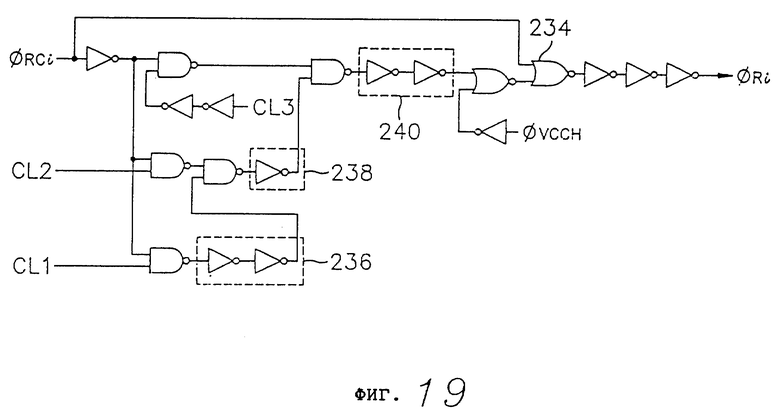

Фиг. 19 представляет собой схему устройства генерирования главного строчного синхроимпульса для генерирования главного строчного синхроимпульса ⊘ Ri в соответствии с настоящим изобретением.

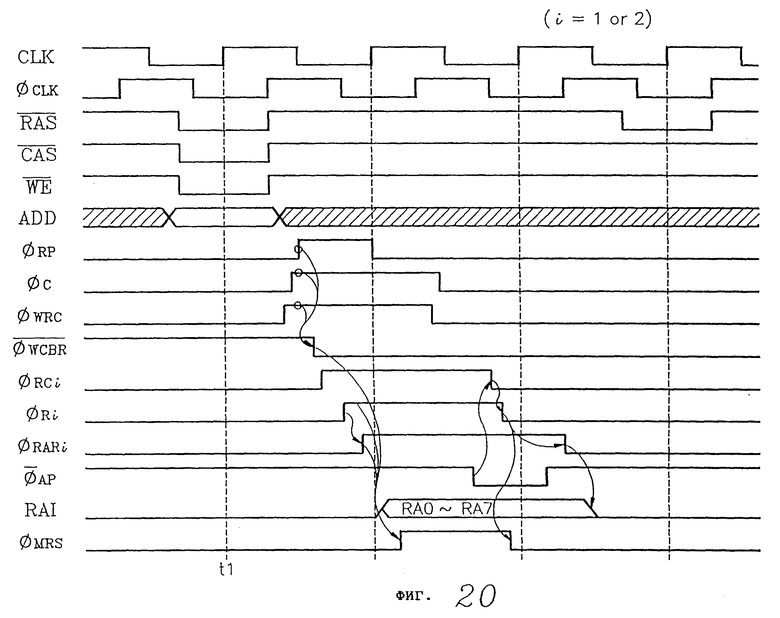

Фиг. 20 представляет собой временную диаграмму, показывающую временную связь установки режима и авторегенерации в соответствии с настоящим изобретением.

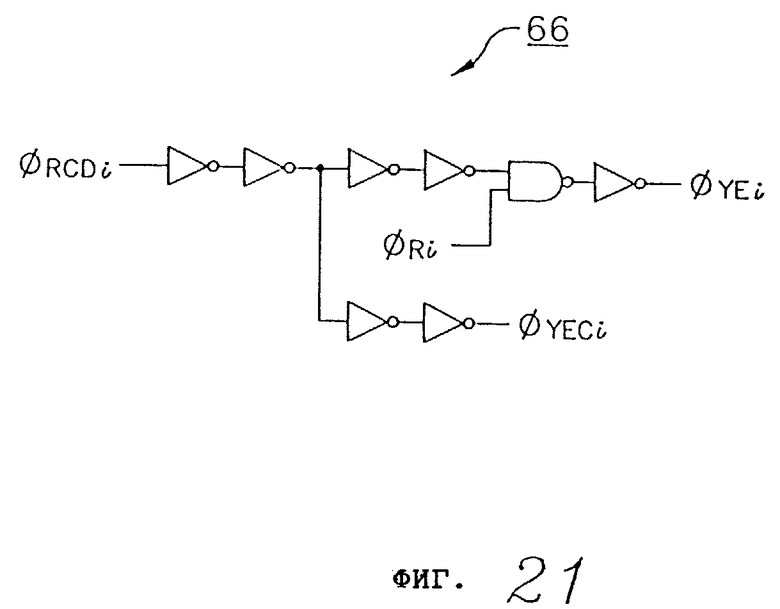

Фиг. 21 представляет собой схему устройства для формирования сигналов, разрешающих генерирование управляющих сигналов столбцов.

Фиг.22 представляет собой временную диаграмму генератора высокочастотных синхроимпульсов на фиг.11.

Фиг. 23 представляет собой блок-схему прохождения данных, связанных с одной из магистралей данных, в соответствии с настоящим изобретением.

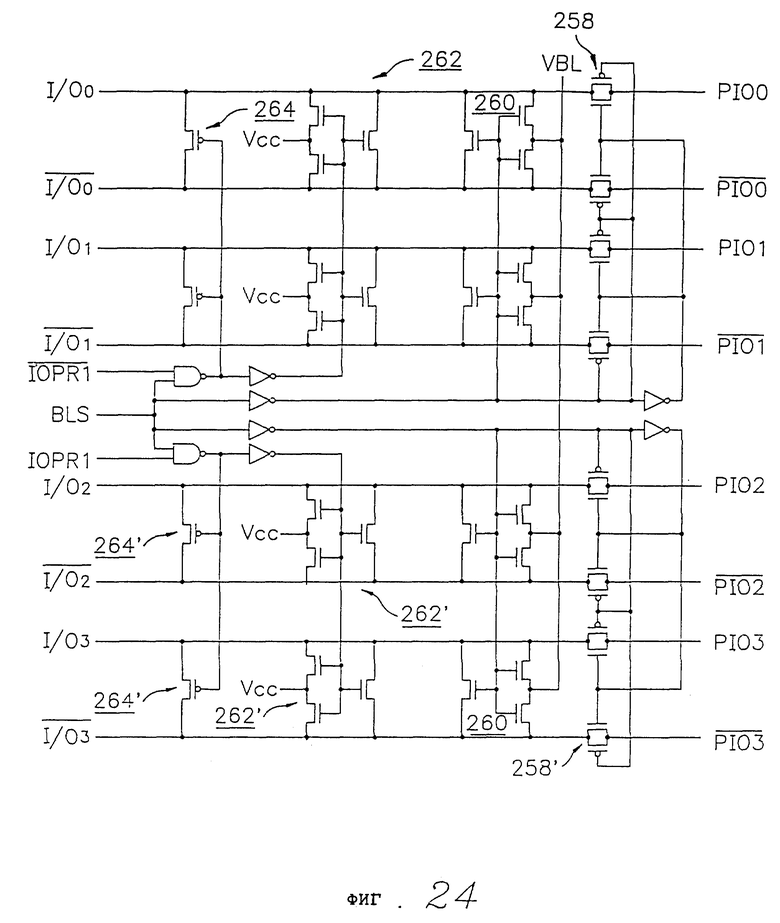

Фиг. 24 представляет собой схему устройства для 1/0 регенерации и выбора в соответствии с настоящим изобретением.

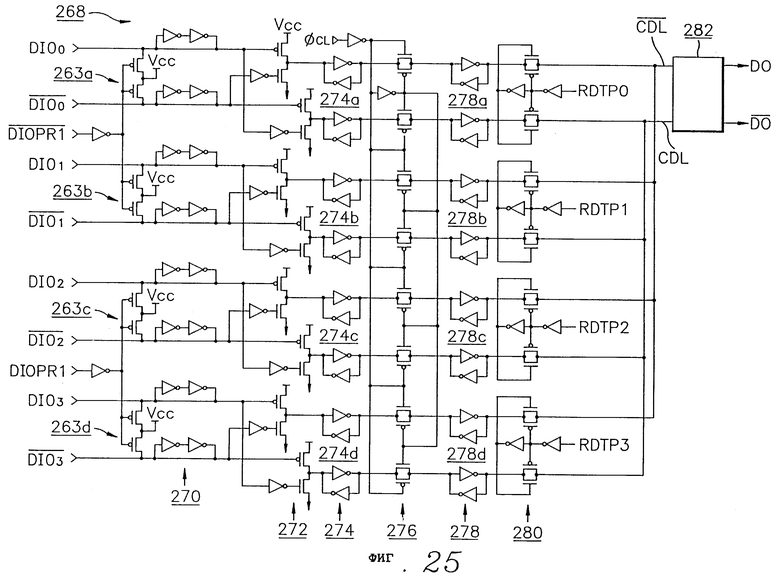

Фиг. 25 представляет собой схему выходного мультиплексора данных в соответствии с настоящим изобретением.

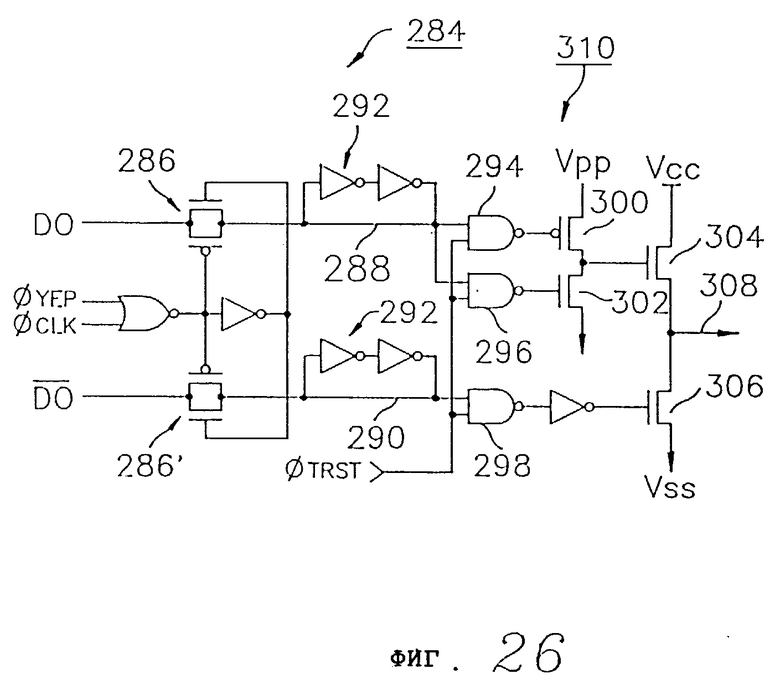

Фиг.26 представляет собой схему выходного буфера данных в соответствии с настоящим изобретением.

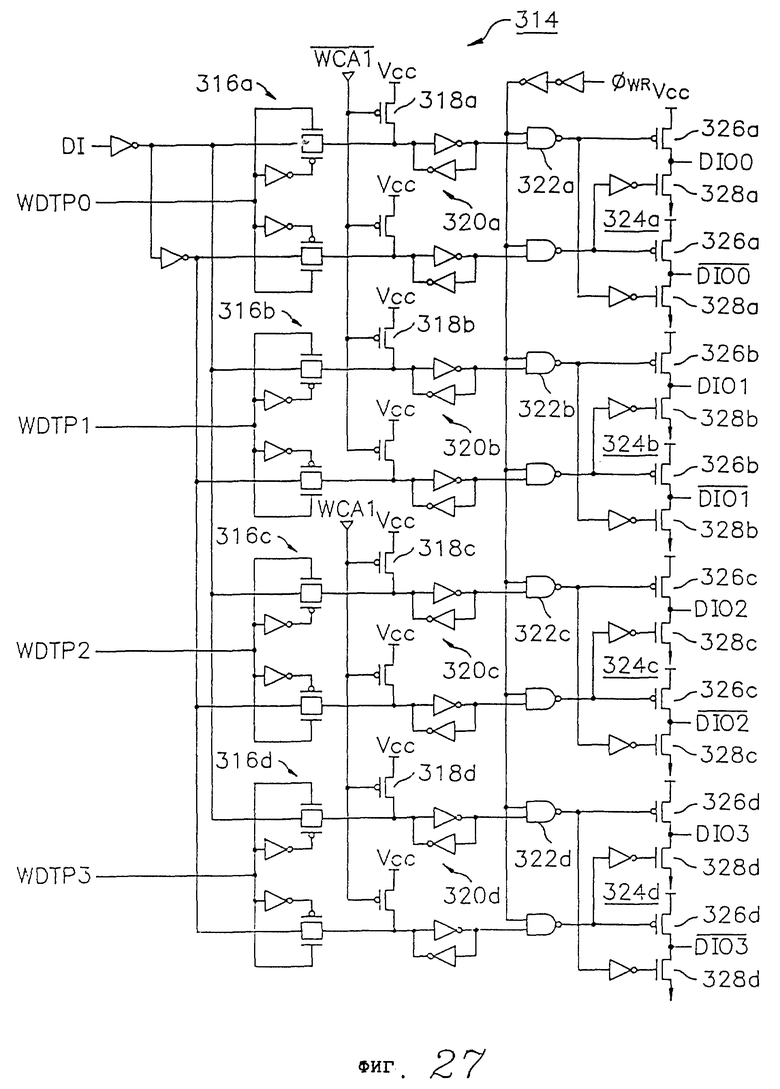

Фиг. 27 представляет собой подробную схему входного демультиплексора данных в соответствии с настоящим изобретением.

Фиг.28 представляет собой схему драйвера шины параллельного ввода/вывода (PIO) в соответствии с настоящим изобретением.

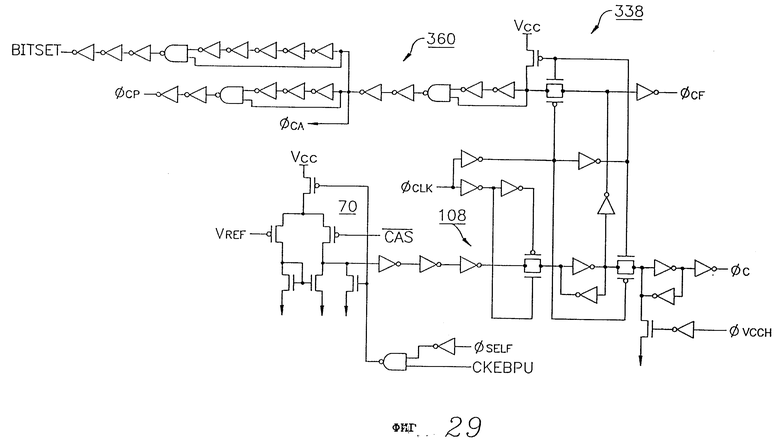

Фиг. 29 представляет собой схему  буфера в соответствии с настоящим изобретением.

буфера в соответствии с настоящим изобретением.

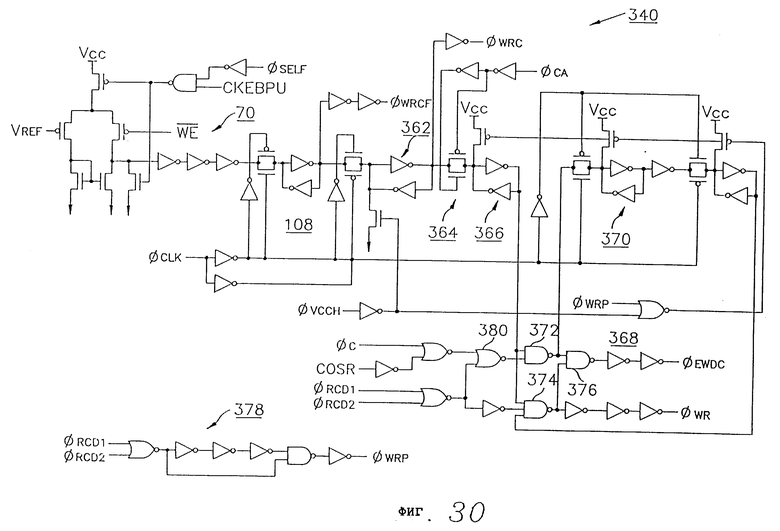

Фиг. 30 представляет собой схему буфера разрешения записи  в соответствии с настоящим изобретением.

в соответствии с настоящим изобретением.

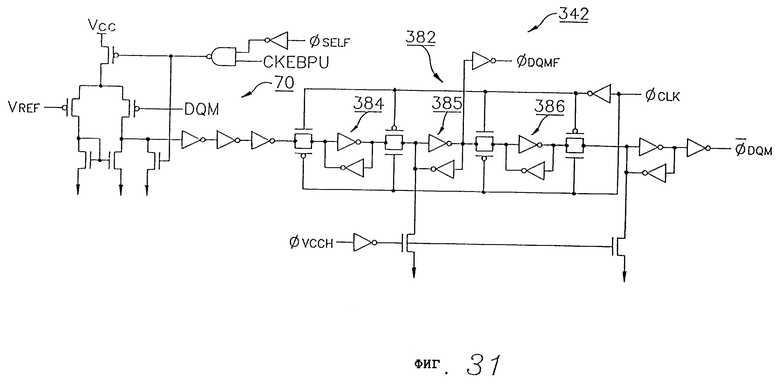

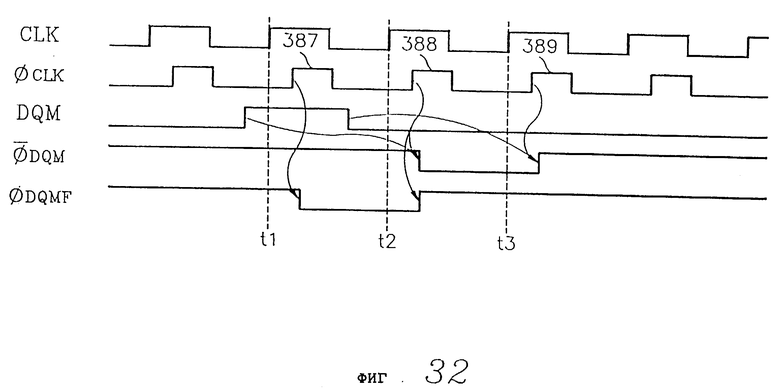

Фиг.31 представляет собой схему DQM (динамическая память с очередью) буфера в соответствии с настоящим изобретением.

Фиг.32 представляет собой временную диаграмму, иллюстрирующую работу DQM буфера на фиг.31.

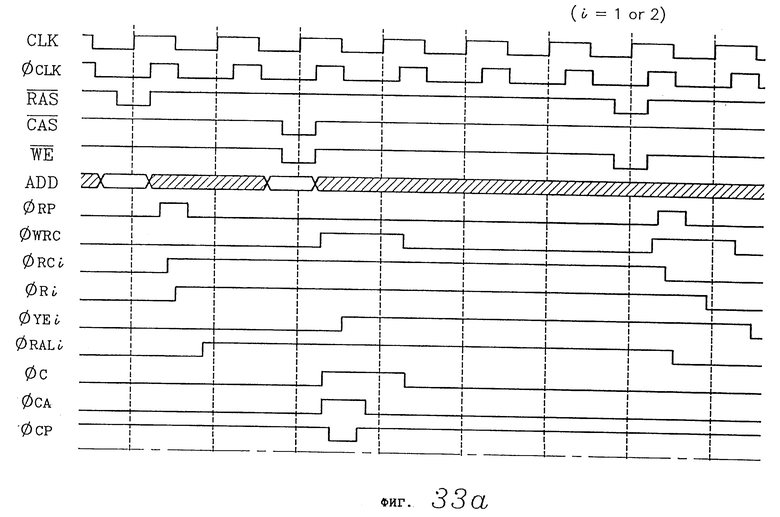

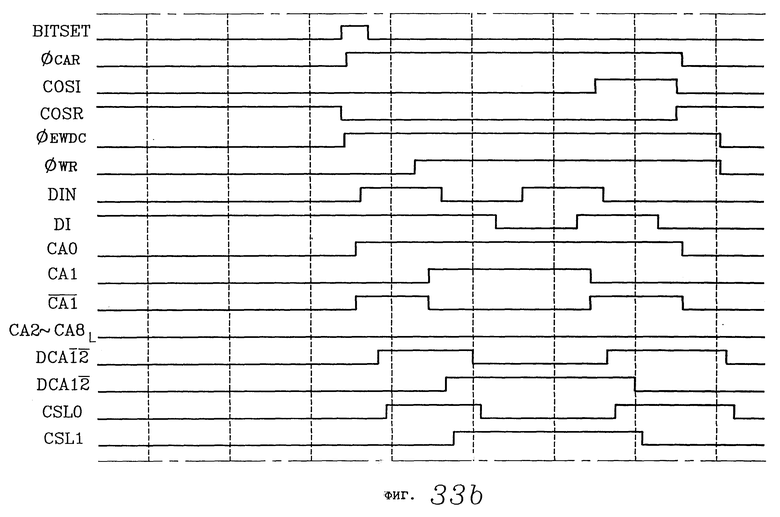

Фиг. 33, состоящая на фиг.33a-33c, представляют собой временные диаграммы, иллюстрирующие операцию записи, в соответствии с настоящим изобретением.

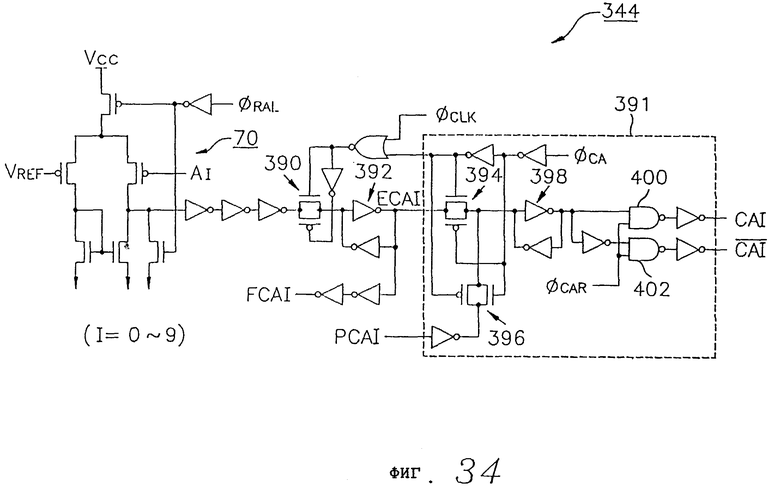

Фиг. 34 представляет собой схему буфера адреса столбцов в соответствии с настоящим изобретением.

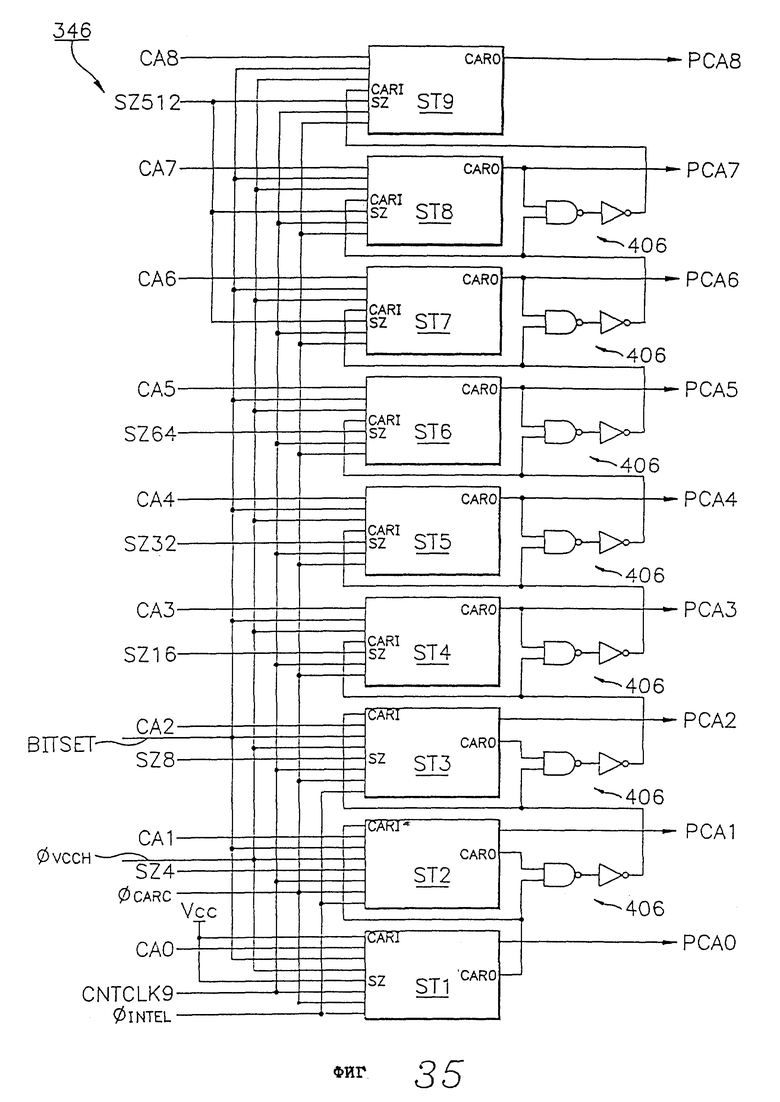

Фиг.35 представляет собой схему счетчика адреса столбца в соответствии с настоящим изобретением.

Фиг. 36a представляет собой схему каждого разряда, образующего первый счетный блок на фиг.35.

Фиг. 36b представляет собой схему каждого разряда, образующего второй счетный блок на фиг.33.

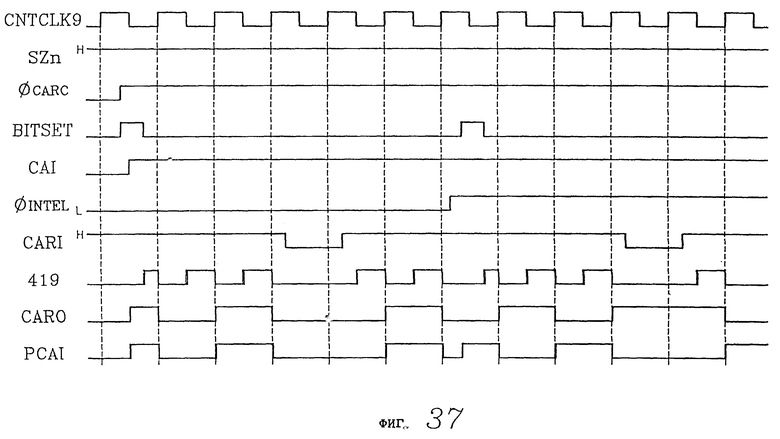

Фиг. 37 представляет собой временную диаграмму, иллюстрирующую работу схемы на фиг.36a.

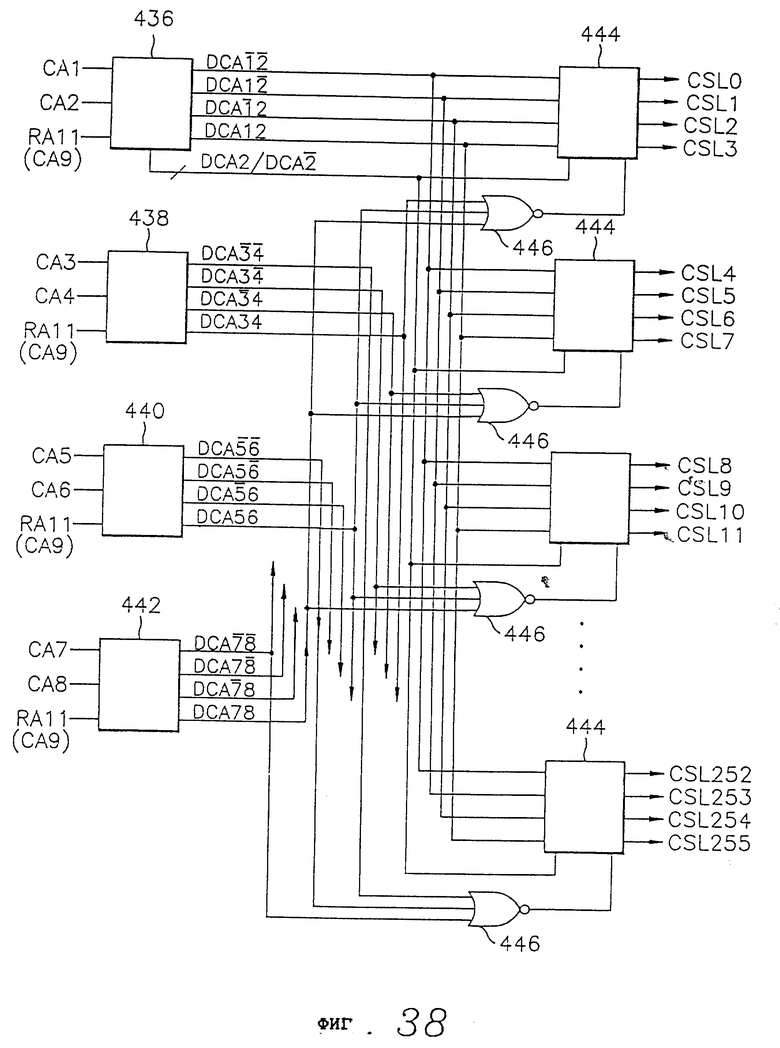

Фиг. 38 представляет собой схему дешифратора столбцов в соответствии с настоящим изобретением.

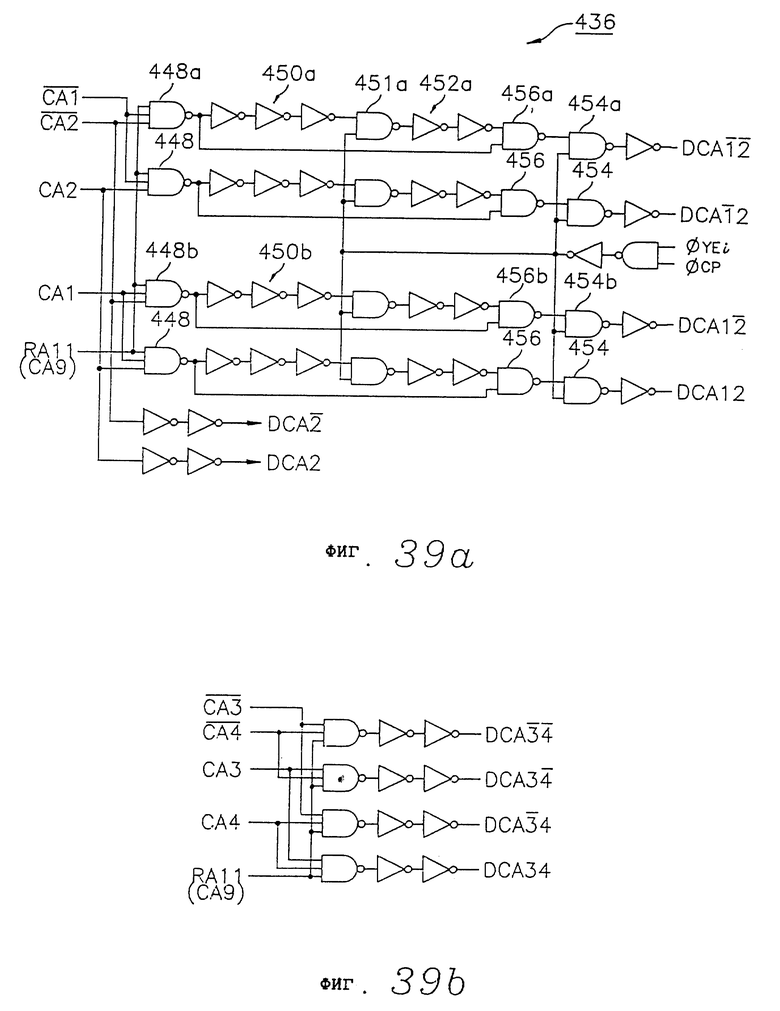

Фиг.39a представляет собой схему первого предешифратора на фиг.38.

Фиг.39b представляет собой схему второго предешифратора на фиг.38.

Фиг. 40 представляет собой схему одного из главных дешифраторов на фиг. 38.

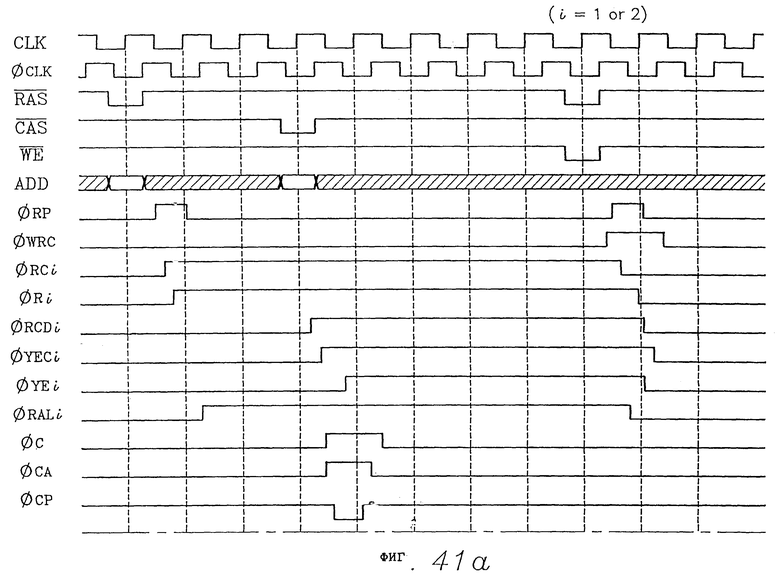

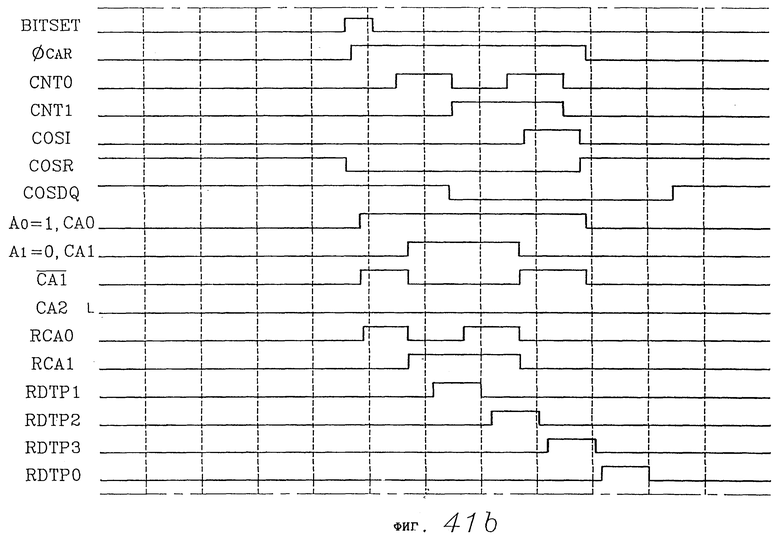

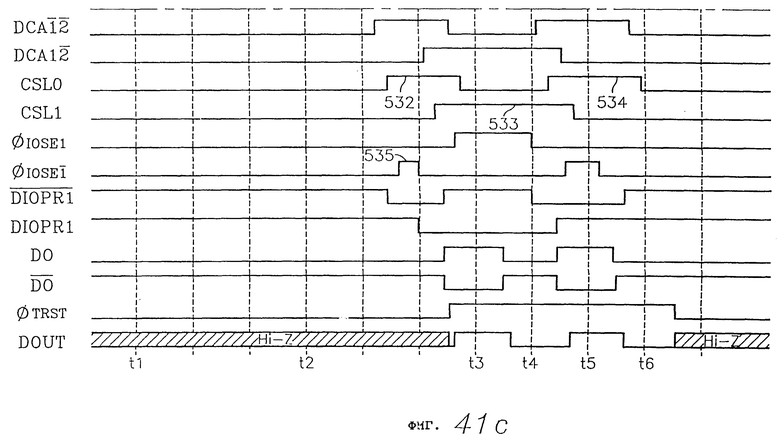

Фиг. 41, включающая 41a-41c, представляет собой временные диаграммы, иллюстрирующие операции считывания в соответствии с настоящим изобретением.

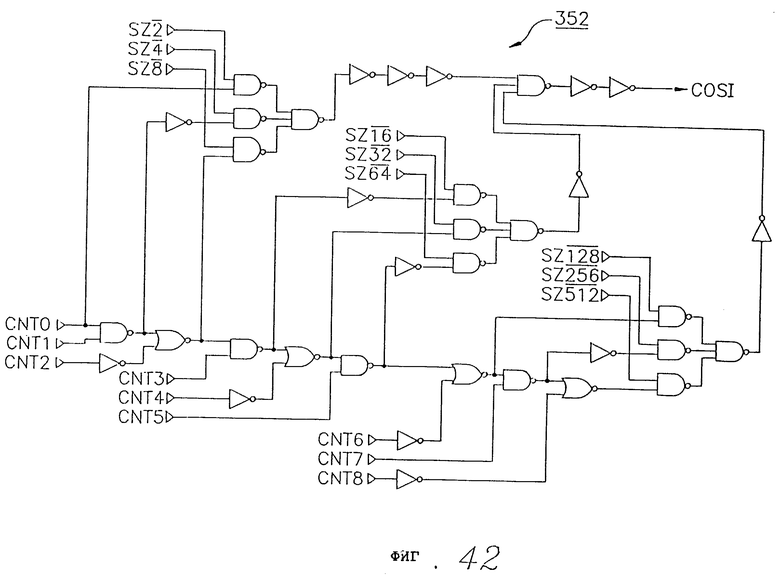

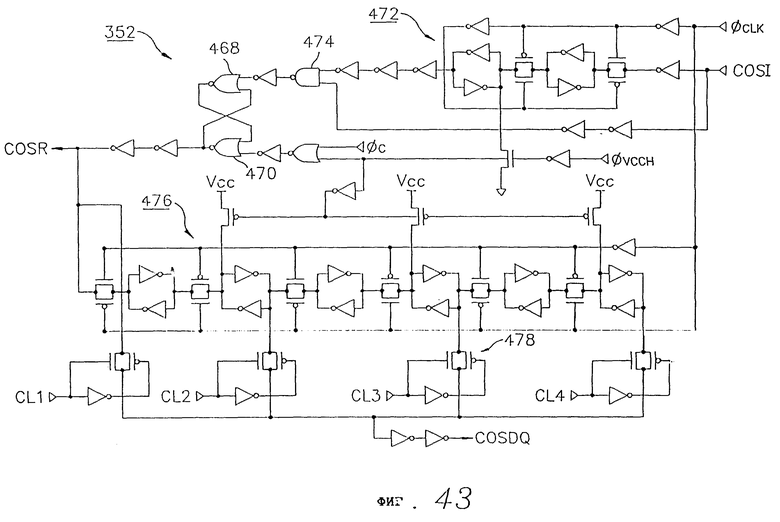

Фиг.42 и 43 представляет собой схемы устройства определения длины пакета на фиг.4.

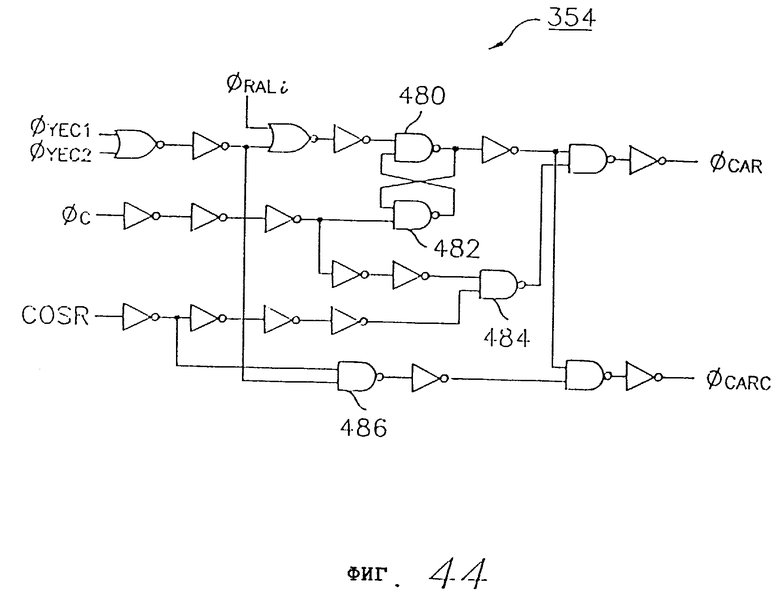

Фиг.44 представляет собой схему генератора сигнала сброса адреса столбца на фиг.4.

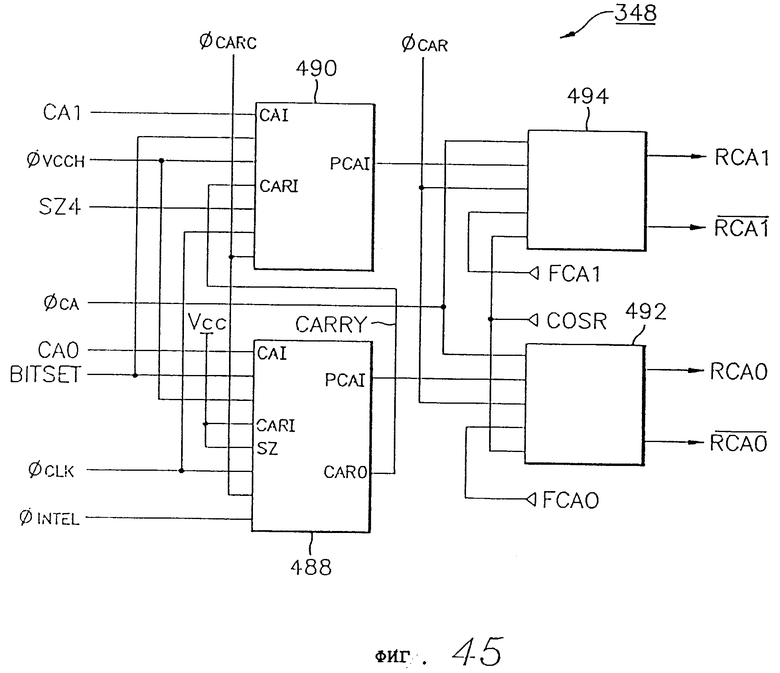

Фиг. 45 представляет собой схему управляющего счетчика пересылки на фиг. 4.

Фиг.46 представляет собой схему генератора синхроимпульсов для пересылки считанных данных.

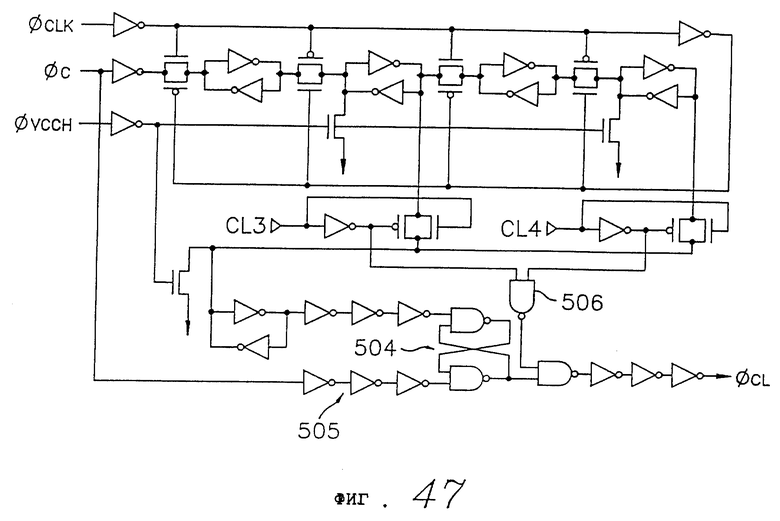

Фиг. 47 представляет собой схему устройства генерирования сигнала ⊘ CL, используемого в мультиплексоре вывода данных на фиг.25.

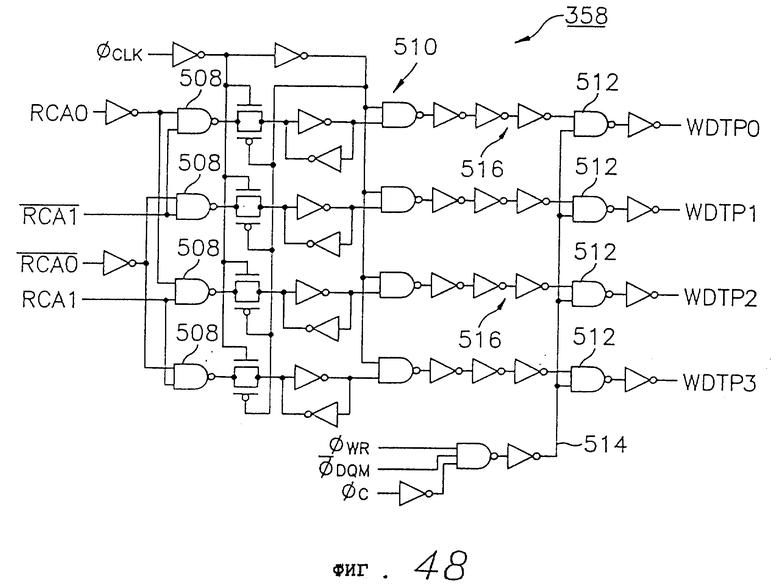

Фиг. 48 представляет собой схему генератора синхроимпульсов для передачи записываемых данных на фиг.4.

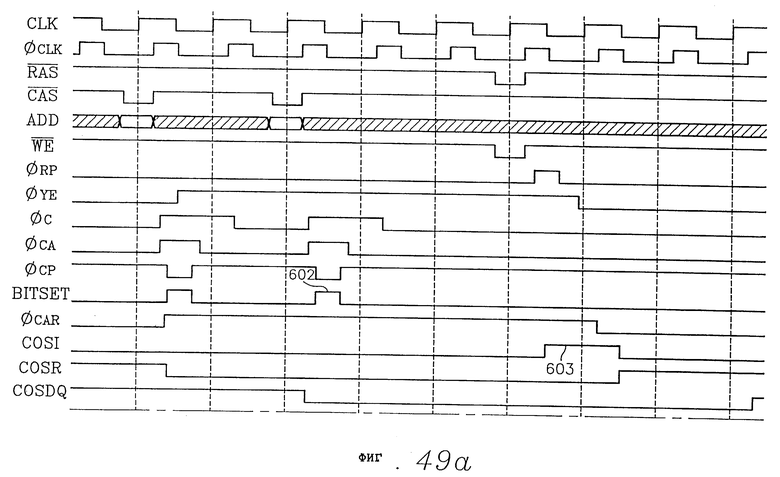

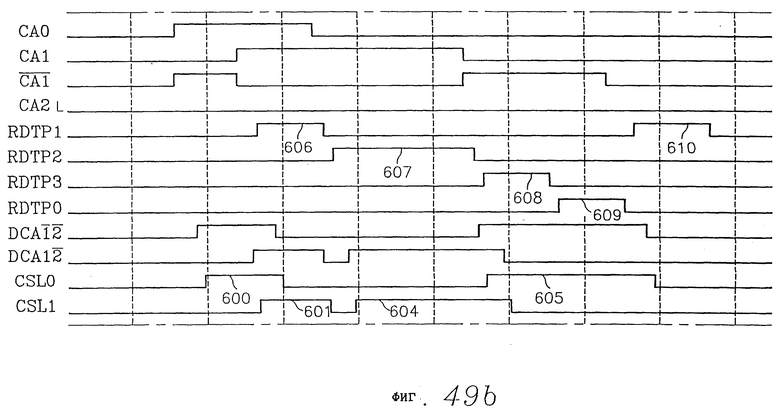

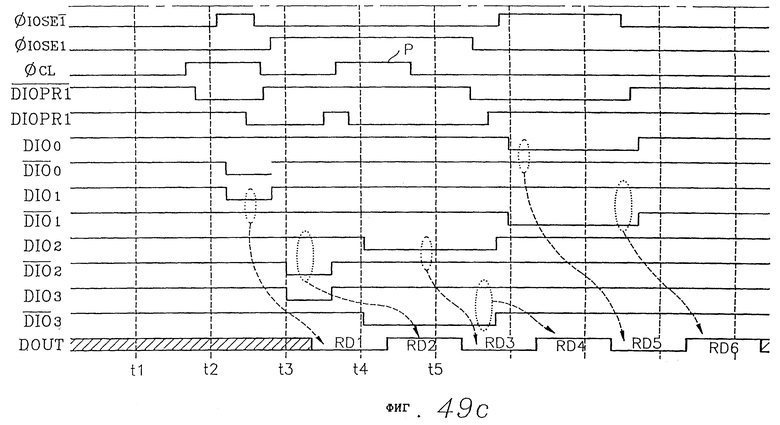

Фиг. 49, состоящая из 49a-49c, представляет собой временные диаграммы прерывания операции записи по сигналу  в соответствии с настоящим изобретением.

в соответствии с настоящим изобретением.

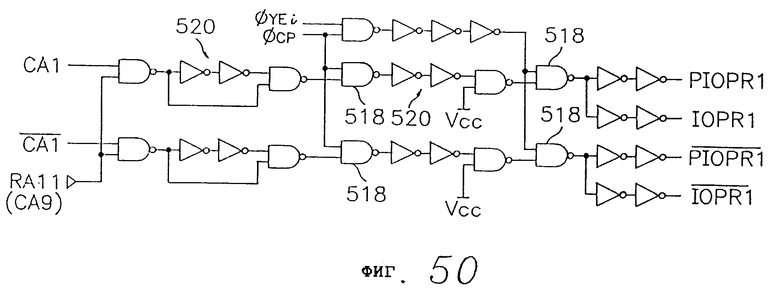

Фиг.50 представляет собой схему устройства генерирования управляющих сигналов, регенерирующих 1/0 шины и P10 шины в соответствии с настоящим изобретением.

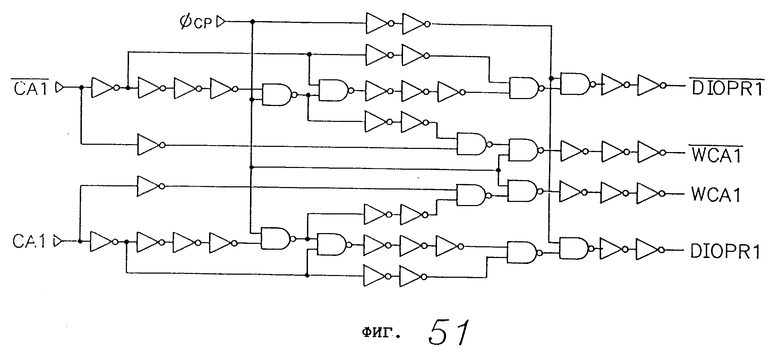

Фиг.51 представляет собой схему устройства для генерирования управляющих сигналов регенерирующих D10 (динамический ввод/вывод) шины в соответствии с настоящим изобретением.

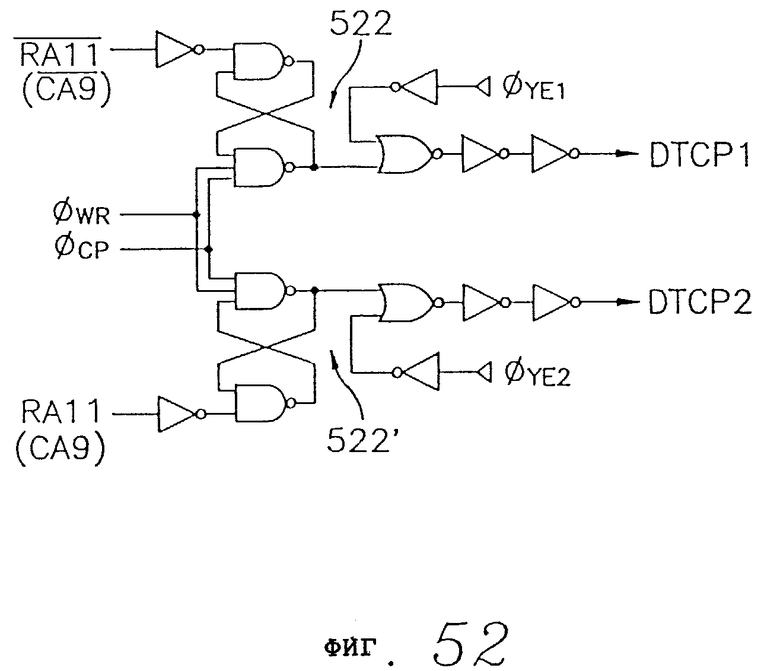

Фиг. 52 представляет собой схему устройства для генерирования сигналов выбора банка, используемых в драйвере P10 шин на фиг.28.

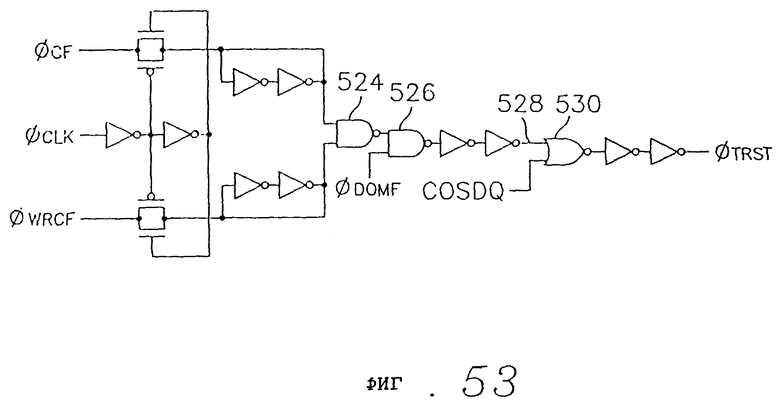

Фиг. 53 представляет собой схему управляющего устройства для генерирования управляющих сигналов, используемых в выходном буфере данных на фиг.26.

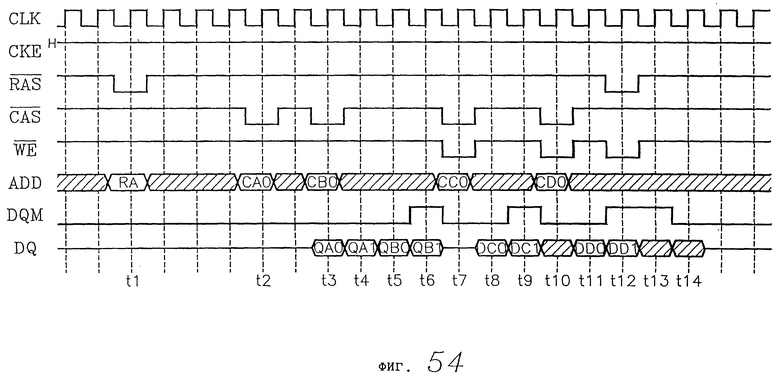

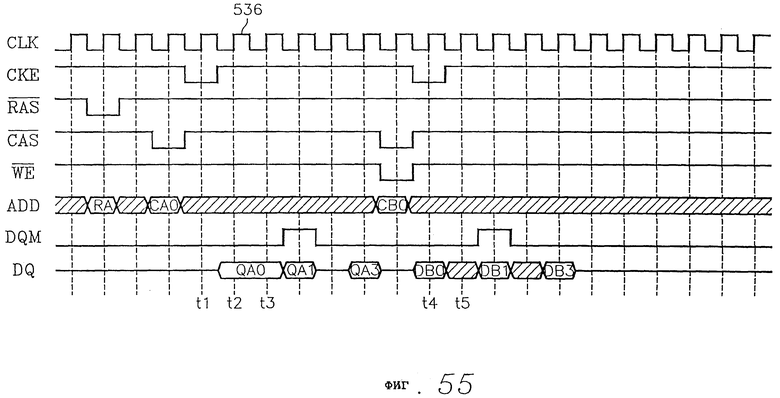

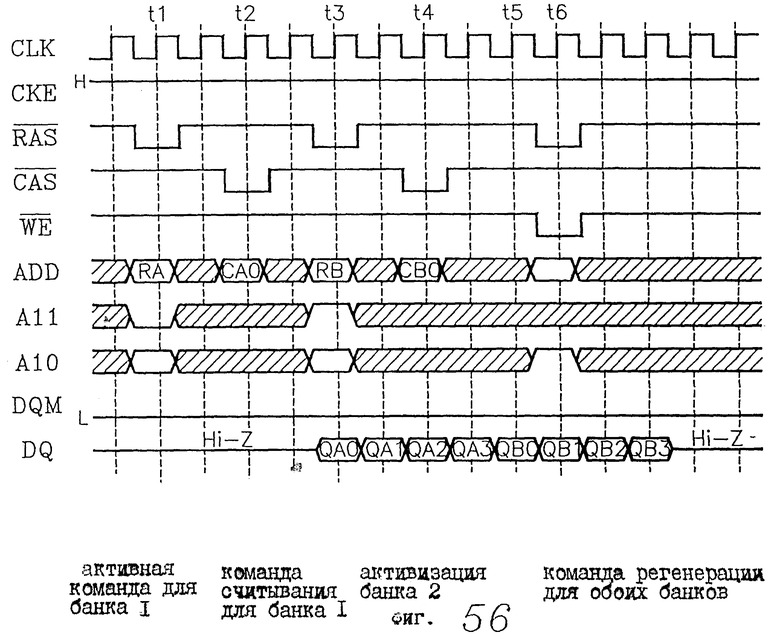

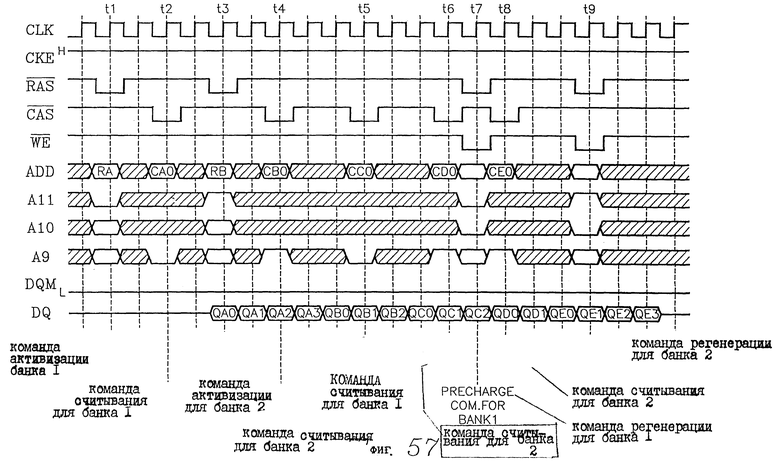

Фиг. 54-57 представляют собой временные диаграммы, иллюстрирующие временные связи в различных рабочих режимах в синхронной DRAM, использующей импульсный RAS сигнал.

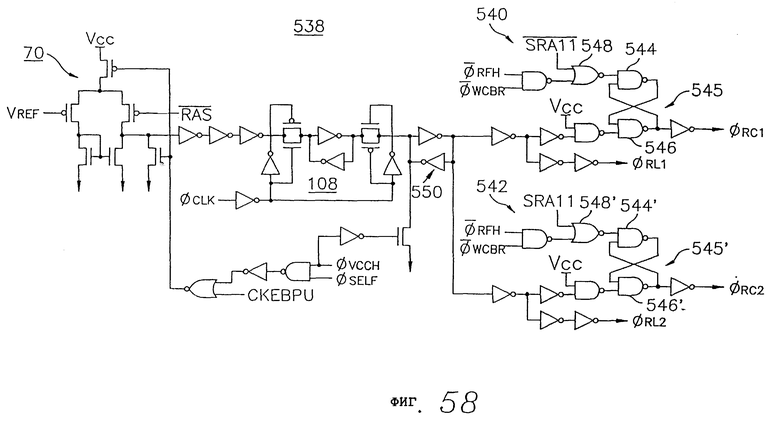

Фиг. 58 представляет собой схему  буфера, использующего уровневый

буфера, использующего уровневый  сигнал.

сигнал.

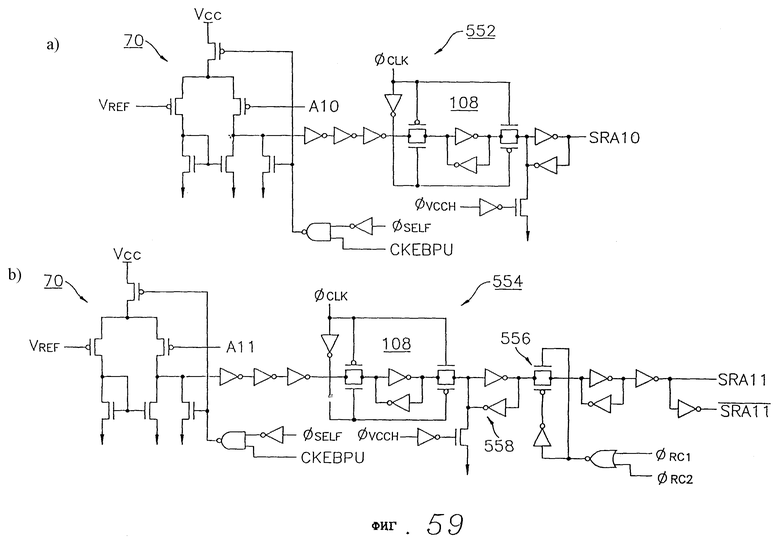

Фиг.59, a,b представляет собой схемы специальных адресных буферов в соответствии с настоящим изобретением.

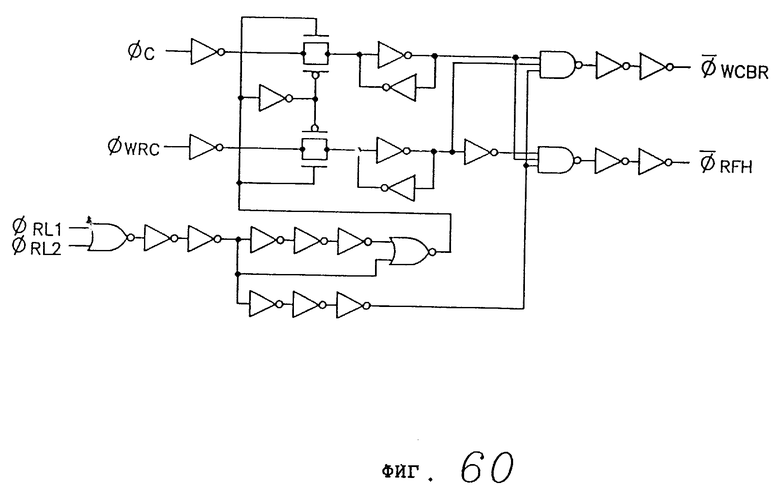

Фиг. 60 представляет собой схему устройства управления для генерирования главного синхромпульса установки режима и главного синхроимпульса восстановления, которые используется в уровневых

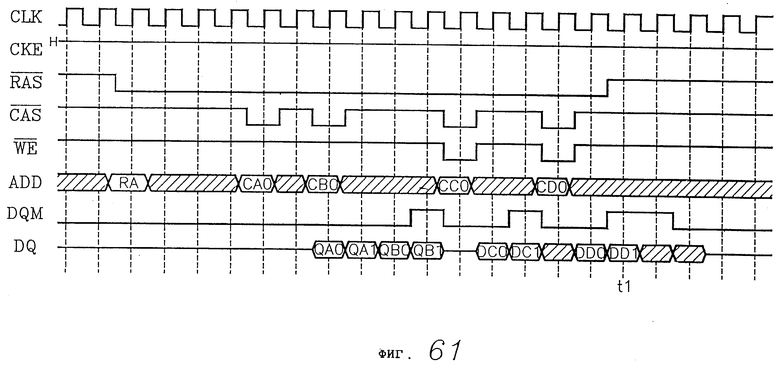

Фиг. 61 представляет собой временную диаграмму, иллюстрирующую временные связи в синхронной DRAM использующей уровневые  сигналы.

сигналы.

Фиг.62 представляет собой диаграмму, показывающую, каким образом объединены отдельные фрагменты чертежей на фигурах 1a и 1b, фигурах 33a-33c, фигурах 41a-41c и фигурах 49a-49c.

Предпочтительный вариант выполнения данного изобретения будет обсуждаться со ссылками на сопровождающие чертежи. Надо иметь в виду, что на чертежах подобные элементы представлены одинаковыми символами и цифровыми обозначениями, где это возможно. В последующем описании многочисленные отдельные детали пронумерованы так же, как номера ячеек памяти, матриц элементов памяти или банков памяти, отдельных потенциалов, отдельных частей или элементов схем и т.д. с целью обеспечить полное понимание настоящего изобретения. Для тех, кто является специалистом в этой области, будет очевидно, что изобретение может быть реализовано и без этих отдельных деталей.

Синхронная DRAM в данном предпочтительном варианте реализации основана на использовании двойной КМОП (CMOS) технологии и использует n-канальные МОП (MOS) транзисторы, имеющие пороговое напряжение от 0.6 до 0.65 В, p-канальные МОП-транзисторы, имеющие пороговое напряжение от -0.8 до -0.85 В и напряжение питания Vcc, составляющее приблизительно 3.3 В.

Архитектура кристалла

Обратимся к фиг.1, состоящей из фиг. 1a и 1b, которая иллюстрирует различные группы элементов, объединенные на одном и том же полупроводниковом кристалле синхронной DRAM в соответствии с настоящим изобретением. DRAM в рассматриваемом варианте реализации представляет собой 16777216-битовую (16-Мбитовую) синхронную DRAM, состоящую из 2097152 (2М) x 8 бит. Матрицы памяти разделены на первый банк 12 и второй банк 14, как показано соответственно на фигурах 1a и 1b, для увеличения скорости передачи данных. Каждый банк состоит из верхней матрицы ячеек памяти 16T и нижней матрицы ячеек памяти 16B, расположенных соответственно в верхней и нижней частях, каждая из которых содержит 4194304 бит ячеек памяти (4Мбит). Верхняя и нижняя матрицы ячеек памяти разделены соответственно на левые матрицы ячеек памяти 20TL и 20BL и правые матрицы ячеек памяти 20TR и 20BR, по 2 Мбита ячеек памяти каждая, касающиеся друг друга боковыми сторонами. На левые и правые матрицы ячеек памяти верхней матрицы ячеек памяти 16T каждого банка будем соответственно ссылаться как на верхнюю левую матрицу ячеек памяти, или первую матрицу ячеек памяти 20TL, и как на верхнюю правую матрицу ячеек памяти, или третью матрицу ячеек памяти, 20TR. Также, будем ссылаться на первую и правую матрицы ячеек памяти нижней матрицы ячеек памяти 16B каждого банка как на нижнюю левую матрицу ячеек памяти, или вторую матрицу ячеек памяти 20BL, и на нижнюю левую матрицу ячеек памяти, или четвертую матрицу ячеек памяти 20BR. Таким образом каждый банк делится на четыре матрицы ячеек памяти, содержащих с первой по четвертую матрицы ячеек памяти. Верхние левая и правая матрицу ячеек памяти и нижние левая и правая матрицы ячеек памяти разделены соответственно на восемь верхних левых субматриц ячеек памяти (или верхних левых субматриц) с 22TL1 по 22TL8, восемь верхних правых субматриц ячеек памяти (или верхних правых субматриц) с 22TR1 по 22TR8, восемь нижних левых субматриц ячеек памяти (или нижних левых субматриц) с 22BL1 по 22BL8 и восемь нижних правых субматриц ячеек памяти (или нижних правых субматриц) с 22BR1 по 22BR8. Каждая из субматриц имеет 256К-бит ячеек памяти, расположенных в матричном виде 256 строк на 1024 столбца. Каждая ячейка памяти представляет собой однотранзисторную одноконденсаторную ячейку известного типа.

В каждом банке строчный дешифратор 18 установлен между верхней матрицей ячеек памяти 16T и нижней матрицей ячеек памяти 16B. Строчный дешифратор 18 каждого банка соединен с 256 строчными шинами (словарными шинами) каждой субматрицы. Словарные шины соответствующей матрицы верхних и нижних пар субматриц 22TL1, 22BL1; 22TL2, 22BL2;...; 22TR8, 22BR8, организованные симметрично по отношению к выходам строчного дешифратора 18, расходятся параллельно друг другу в противоположных направлениях по вертикали. Строчный дешифратор 18, реагирующий на строчные адреса из буфера строчного адреса, выбирает одну из субматриц соответствующих матриц (с первой по четвертую матрицы ячеек памяти) и одну из словарных шин в выбранной субматрице, и подает строчный управляющий потенциал на каждую выбранную словарную шину. Таким образом в соответствии с выданными адресами строк в каждом банке строчный дешифратор 18 выбирает одновременно четыре словарных шины, одна словарная шина выбирается в одной на выбранных верхних левых субматриц 22TL1-22TL8, другая словарная шина выбирается в одной из выбранных нижних левых субматриц 22BL1-22BL8, третья словарная шина выбирается в одной из выбранных верхних правых субматриц 22TR1-22TR8 и последняя словарная шина выбирается в одной из выбранных нижних правых субматриц 22BR1-22BR8.

Дешифраторы столбцов 24 примыкают соответственно к правым краям верхних и нижних матриц ячеек памяти 16T и 16B в первом банке 12 и к левым краям верхних и нижних матриц ячеек памяти 16T и 16B во втором банке 14. Каждый из дешифраторов столбцов 24 подсоединен к 256 шинам выборки столбцов, которые направлены горизонтально и перпендикулярны словарным шинам, причем эти дешифраторы служат для выборки одной из шин столбцов в соответствии с адресом столбца.

1/0 магистрали 26 примыкают к обоим краям соответствующих субматриц 22TL, 22BL, 22TR и 22BR, расходясь параллельно словарным шинам. 1/0 магистрали 26, соединяющие противоположные края субматриц, совместно используются этими двумя смежными субматрицами. Каждая из 1/0 магистралей 26 состоит из четырех пар 1/0 шин, причем каждая пара, которая состоит из двух сигнальных дополняющих друг друга шин, подключена к соответствующей паре разрядов посредством ключа выбора столбца и усилителя считывания.

Для упрощения рассмотрим теперь фиг.2, которая иллюстрирует организацию одной из нечетных субматриц с 22TL1 по 22TL8 в верхней матрице ячеек памяти 16T и ту из 1/0 магистралей, которая ей соответствует. Первая, или левая, 1/0 магистраль 26L и вторая, или правая, 1/0 магистраль 26R соответственно идут параллельно словарным шинам WL0-WL225 по левому и правому краям субматрицы 22. Каждая из первых и вторых 1/0 магистралей 26L и 26R состоит из первой пары 1/0 шин, которая состоит из пар 1/00,  и 1/01,

и 1/01,  и второй 1/0 пары, которая состоит из пар 1/02,

и второй 1/0 пары, которая состоит из пар 1/02,  и 1/03

и 1/03  Субматрица 22 содержит 1024-битовые шинные пары 28, перпендикулярные словарным шинам WL0-WL255, которые устроены в виде свернутых битовых шин. Ячейки памяти 30 расположены на пересечении словарных и разрядных шин. Пара разрядных шин 28, подходящих к субматрице 22, разделена на множество групп разрядных шин с 28L1 по 28L256, расположенных на нечетных местах, и множество вторых групп разрядных шин с 28R1 по 28R256, установленных на четных местах. Каждая из групп разрядных шин имеет данный ей номер пары разрядных шин (две пары разрядных шин в рассматриваемом варианте реализации). Первые группы разрядных шин 28L чередуются со вторыми группами разрядных шин 28R. Нечетные пары разрядных шин (или первые подгруппы) 28L1, 28L3,..., 28L255 и четные пары разрядных шин (или вторые подгруппы) 28L2, 28L4,..., 28L256 первых групп разрядных 28L подсоединены соответственно к первым 1/0 парам и вторым 1/0 парам шин первой 1/0 магистрали 26L с помощью соответствующего усилителя считывания 32L и ключей выбора столбца 34L. Таким же образом нечетные пары разрядных шин (или первые подгруппы) 28R1, 28R3,..., 28R255 и четные пары разрядных шин (или вторые подгруппы) 28R2, 28R4,..., 28R256 вторых групп разрядных дин 28R соединены соответственно с первыми парами 1/0 шин и вторыми парами 1/0 шин второй 1/0 26R магистрали с помощью соответствующих усилителей 32R и ключей выбора столбцов 34R. Первые шины выбора столбцов L0, L2, . . . и L254, которые соединены с ключами выбора столбцов, связанными с первыми парами 1/0 шин 1/00,

Субматрица 22 содержит 1024-битовые шинные пары 28, перпендикулярные словарным шинам WL0-WL255, которые устроены в виде свернутых битовых шин. Ячейки памяти 30 расположены на пересечении словарных и разрядных шин. Пара разрядных шин 28, подходящих к субматрице 22, разделена на множество групп разрядных шин с 28L1 по 28L256, расположенных на нечетных местах, и множество вторых групп разрядных шин с 28R1 по 28R256, установленных на четных местах. Каждая из групп разрядных шин имеет данный ей номер пары разрядных шин (две пары разрядных шин в рассматриваемом варианте реализации). Первые группы разрядных шин 28L чередуются со вторыми группами разрядных шин 28R. Нечетные пары разрядных шин (или первые подгруппы) 28L1, 28L3,..., 28L255 и четные пары разрядных шин (или вторые подгруппы) 28L2, 28L4,..., 28L256 первых групп разрядных 28L подсоединены соответственно к первым 1/0 парам и вторым 1/0 парам шин первой 1/0 магистрали 26L с помощью соответствующего усилителя считывания 32L и ключей выбора столбца 34L. Таким же образом нечетные пары разрядных шин (или первые подгруппы) 28R1, 28R3,..., 28R255 и четные пары разрядных шин (или вторые подгруппы) 28R2, 28R4,..., 28R256 вторых групп разрядных дин 28R соединены соответственно с первыми парами 1/0 шин и вторыми парами 1/0 шин второй 1/0 26R магистрали с помощью соответствующих усилителей 32R и ключей выбора столбцов 34R. Первые шины выбора столбцов L0, L2, . . . и L254, которые соединены с ключами выбора столбцов, связанными с первыми парами 1/0 шин 1/00,  и 1/01,

и 1/01,  в левой и правой 1/0 магистралях 26L и 26R, расположены параллельно, чередуясь со вторыми шинами выбора столбцов L1, L3, . . ., L255, которые подсоединены к ключам выбора столбцов, связанным с вторыми 1/0 парами шин 1/02,

в левой и правой 1/0 магистралях 26L и 26R, расположены параллельно, чередуясь со вторыми шинами выбора столбцов L1, L3, . . ., L255, которые подсоединены к ключам выбора столбцов, связанным с вторыми 1/0 парами шин 1/02,  и 1/03,

и 1/03,  Таким образом, при операции считывания, после выбора одной из словарных шин, то есть, одной страницы с адресами строк, первые и вторые пары 1/0 шин в левой и правой 1/0 магистралях 26L и 26B выдают непрерывные данные, чередуя выдачу двухбитовых данных с последовательной выборкой шин выбора столбцов с L0 до L255. Шинная пара 36, которая соединена с соответствующими усилителями считывания 32L и 32R и распространяется поочередно в противоположных направлениях, связана с соответствующими группами разрядных шин 28L и 28R с помощью соответствующих усилителей считывания в субматрицах, смежных с первой и второй 1/0 магистралями 26L и 26R. Таким образом первые 1/0 шинные пары и вторые 1/0 шинные пары первой 1/0 магистрали 26L соединены соответственно с нечетными парами разрядных шин (или первыми подгруппами) и четными парами разрядных шин (или вторыми подгруппами) первых групп разрядных шин левой смежной субматрицы (не показана) с помощью соответствующих ключей выбора столбцов 32L и соответствующих усилителей считывания. Таким же образом первые пары 1/0 шин и вторые пары 1/0 шин второй 1/0 магистрали 26R подсоединены соответственно к нечетным парам разрядных шин (или первым подгруппам) и четным парам разрядных шин (или вторым подгруппам) вторых групп разрядных шин правой смежной субматрицы (не показана) с помощью ключей выбора столбцов 32R и соответствующих усилителей считывания. Таким образом, так как пары разрядных шин соответствующих субматриц разделены таким же образом, как первые и вторые группы разрядных шин субматрицы 22, как показано на фигуре 2, 1/0 магистрали, связанные с первыми группами разрядных шин, чередуются с 1/0 магистралями, связанными со вторыми группами разрядных шин. Таким образом каждая из первых 1/0 магистралей, расположенных на нечетных местах, связана с первой группой разрядных шин в двух смежных субматрицах, в то время как каждая из вторых 1/0 магистралей, расположенных на четных местах, связана со вторыми группами разрядных шин в смежных субматрицах. Что касается соответствующих субматриц на фиг.1, их связи с первыми и вторыми парами 1/0 шин первой и второй 1/0 магистралей будут включены в рассмотрение при объяснении, которое будет дано в связи с фиг 2. В качестве усилителя считывания 32L или 32R может быть использована известная схема, которая состоит из P-канального усилителя считывания, разделяющего транзисторы передачи, N-канального усилителя считывания и схемы выравнивания и регенерации. Таким образом 1/0 магистрали 26 между двумя смежными субматрицами являются общими 1/0 магистралями для считывания и записи данных из/в субматрицу, которая выбирается под управлением разделяющих транзисторов передачи.

Таким образом, при операции считывания, после выбора одной из словарных шин, то есть, одной страницы с адресами строк, первые и вторые пары 1/0 шин в левой и правой 1/0 магистралях 26L и 26B выдают непрерывные данные, чередуя выдачу двухбитовых данных с последовательной выборкой шин выбора столбцов с L0 до L255. Шинная пара 36, которая соединена с соответствующими усилителями считывания 32L и 32R и распространяется поочередно в противоположных направлениях, связана с соответствующими группами разрядных шин 28L и 28R с помощью соответствующих усилителей считывания в субматрицах, смежных с первой и второй 1/0 магистралями 26L и 26R. Таким образом первые 1/0 шинные пары и вторые 1/0 шинные пары первой 1/0 магистрали 26L соединены соответственно с нечетными парами разрядных шин (или первыми подгруппами) и четными парами разрядных шин (или вторыми подгруппами) первых групп разрядных шин левой смежной субматрицы (не показана) с помощью соответствующих ключей выбора столбцов 32L и соответствующих усилителей считывания. Таким же образом первые пары 1/0 шин и вторые пары 1/0 шин второй 1/0 магистрали 26R подсоединены соответственно к нечетным парам разрядных шин (или первым подгруппам) и четным парам разрядных шин (или вторым подгруппам) вторых групп разрядных шин правой смежной субматрицы (не показана) с помощью ключей выбора столбцов 32R и соответствующих усилителей считывания. Таким образом, так как пары разрядных шин соответствующих субматриц разделены таким же образом, как первые и вторые группы разрядных шин субматрицы 22, как показано на фигуре 2, 1/0 магистрали, связанные с первыми группами разрядных шин, чередуются с 1/0 магистралями, связанными со вторыми группами разрядных шин. Таким образом каждая из первых 1/0 магистралей, расположенных на нечетных местах, связана с первой группой разрядных шин в двух смежных субматрицах, в то время как каждая из вторых 1/0 магистралей, расположенных на четных местах, связана со вторыми группами разрядных шин в смежных субматрицах. Что касается соответствующих субматриц на фиг.1, их связи с первыми и вторыми парами 1/0 шин первой и второй 1/0 магистралей будут включены в рассмотрение при объяснении, которое будет дано в связи с фиг 2. В качестве усилителя считывания 32L или 32R может быть использована известная схема, которая состоит из P-канального усилителя считывания, разделяющего транзисторы передачи, N-канального усилителя считывания и схемы выравнивания и регенерации. Таким образом 1/0 магистрали 26 между двумя смежными субматрицами являются общими 1/0 магистралями для считывания и записи данных из/в субматрицу, которая выбирается под управлением разделяющих транзисторов передачи.

Вернемся к фиг.1. В каждом банке в верхней части первой и второй матриц ячеек памяти 20TL и 20TR размещены соответственно устройства выбора 1/0 шины и регенерации 38TL и 38TR усилители считывания 1/0 и шинные драйверы 40TL и 40TR, соединенные соответствующим образом, и аналогично, в нижней части второй и четвертой матриц ячеек памяти 20BL и 20BR размещены соответственно устройства выбора 1/0 шины и регенерации 38BL и 38BR усилители считывания 1/0 и шинные драйверы 40BL и 40BR, соединенные соответствующим образом. Устройства выбора 1/0 шин и регенерации 38TL, 38TR, 38BL и 38BR подсоединены соответственно к чередующимся 1/0 магистралям 26 в соответствующих матрицах ячеек памяти 20TL, 20TR, 20BL и 20BR. Таким образом устройства выбора 1/0 шин и регенерации, расположенные на нечетных местах, соединены соответственно с парами 1/0 магистралей, размещенных на нечетных местах в соответствующих матрицах ячеек памяти, а устройства выбора шин 1/0 и регенерации, расположенные на четных местах, подсоединены соответственно к парам 1/0 магистралей, расположенных на четных местах в соответствующих матрицах ячеек памяти. Следовательно, в каждом банке каждое из устройств, расположенных с краю устройств выбора 1/0 шин и регенерации, может иметь доступ к данным в ячейках памяти, которые соединены с первыми группами разрядных шин в третьих субматрицах, а нечетно расположенные устройства выбора 1/0 шин и регенерации и четно расположенные устройства выбора 1/0 шин и регенерации, исключая расположенные с краю устройства выбора 1/0 шин и регенерации, связаны соответственно с первыми группами разрядных шин и вторыми группами разрядных шин. Каждое из устройств выбора 1/0 шин и регенерации 38 состоит из устройства выбора 1/0 магистрали для выбора одной из пары подсоединенных к нему 1/0 магистралей и устройства регенерации 1/0 шин для регенерации другой пары 1/0 шин, когда любая из первых 1/0 винных пар 1/00,  и 1/01,

и 1/01,  и вторых 1/0 шинных пар 1/02,

и вторых 1/0 шинных пар 1/02,  и 1/03,

и 1/03,  образующих выбранную 1/0 магистраль, передает данные.

образующих выбранную 1/0 магистраль, передает данные.

Устройства выбора 1/0 шин и регенерации 38 соединены соответственно с усилителями считывания 1/0 и шинными драйверами 40 посредством P10 магистралей 44. Каждая P10 магистраль 44 соединена с 1/0 магистралью, выбранной соответствующим устройством выбора 1/0 магистрали. Таким образом P10 магистрали 44 состоят из четырех пар P10 шин аналогично 1/0 магистралям 26. Каждый усилитель считывания 1/0 и шинный драйвер 40 состоят из усилителя считывания 1/0 для усиления ввода данных с помощью соответствующего устройства выбора 1/0 магистрали и P10 магистрали в операции считывания, и шинного драйвера для управления 1/0 магистралью ввода данных, выбранной устройством выбора 1/0 магистрали с помощью соответствующего устройства выбора 1/0 магистрали и P10 магистрали в операции записи. Таким образом, как описано выше, если данные на любой из первых или вторых шинных пар вводятся в усилитель считывания через соответствующие P10 шинные пары, P10 шинные пары, связанные с другими 1/0 шинными парами, регенерируются совместно с 1/0 шинными парами. Кроме того, в операции записи, когда драйвер 40 направляет данные в соответствующие 1/0 шинные пары через выбранные P10 шинные пары, невыбранные P10 шинные пары и соответствующие им 1/0 шинные пары начинают регенерироваться.

К самым верхним и нижним краям кристалла синхронной DRAM подходят идущие горизонтально соответственно верхние магистрали данных 42T и нижние магистрали данных 42B. Каждая из верхних магистралей данных 42T и нижних магистралей данных 42B состоит из четырех магистралей данных, каждая из которых, в свою очередь, состоит из четырех пар шин данных, которые имеют те же номера, что и упомянутые выше 1/0 магистрали и P10 магистрали. Одни концы четырех магистралей данных DB0-DB3, образующих верхние магистрали данных 42T, и четырех магистралей данных DB4-DB7, образующих нижнюю магистраль данных, соединены соответственно с мультиплексорами ввода/вывода данных 46, которые соединены с контактами ввода/вывода (не показаны), с помощью шин ввода/вывода 47 и буферов ввода/вывода данных 48.

В каждом банке усилители считывания 1/0 и шинные драйверы 40TL, связанные с первой матрицей ячеек памяти 20TL, соединены поочередно с первой и второй магистралями данных DB0 и DB1, а усилители считывания 1/0 и шинные драйверы 40TR, связанные с третьей матрицей ячеек памяти 20TR, поочередно связаны с третьей и четвертой магистралями данных DB2 и DB3. Аналогично усилители считывания 1/0 и шинные драйверы 40BL, связанные со второй матрицей ячеек памяти 20BL, поочередно соединены с пятой и шестой магистралями данных DB4 и DB5, а усилители считывания 1/0 и шинные драйверы 40BR, связанные с четвертой матрицей ячеек памяти 20BR, поочередно связаны с седьмой и восьмой магистралями данных. Центральные усилители считывания 1/0 и драйверы 43T и 43B подсоединены соответственно к 1/0 магистралям между первой матрицей ячеек памяти 20TR и третьей матрицей ячеек памяти 20TR и между второй матрицей ячеек памяти 20BL и четвертой матрицей ячеек памяти 20BR каждом банке. В каждом банке центральный усилитель считывания 1/0 и шинный драйвер 43T в верхней части состоят из усилителя считывания 1/0 для усиления данных на соответствующей магистрали 1/0, чтобы связать данные с магистралью данных DB1 или DB3 в ответ на управляющий сигнал в операции считывания, и шинного драйвера для направления данных с магистрали данных DB1 или DB3 на 1/0 магистраль в ответ на управляющий сигнал в операции записи. Аналогично, центральный усилитель считывания 1/0 и шинный драйвер 43 в нижней части подсоединены к четвертой и восьмой магистралям данных DB5 и DB7.

Теперь допустим, что субматрицы 22TL3, 22BL3, 22TR3 и 22BR3 в первом банке 12 и одна словарная шина в соответствующих субматрицах выбраны строчным дешифратором 18 в ответ на строчный адрес. Тогда строчный дешифратор 18 выдает сигналы блочной информации, обозначающие соответствующие субматрицы 22TL3, 22BL3, 22TR3 и 22BR3. Затем в операции считывания устройство управления, как будет обсуждаться ниже, генерируют последовательные адреса столбцов в ответ на внешний адрес столбца, а дешифратор столбцов 24 генерирует последовательные сигналы выбора столбцов в ответ на этот поток адресов столбцов. Если допустить, что первый сигнал выбора столбцов должен выбрать шину выбора столбцов L0, то тогда открывается соответствующий ключ выбора столбцов 34, показанный на фиг.2, и данные, собранные на соответствующих парах разрядных шин, будут пересылаться к шинным парам 1/00,  и 1/01,

и 1/01,  левой и правой 1/0 магистралей, расположенных по обоим краям соответствующих выбранных субматриц. Устройства выбора 1/0 шин и регенерации 38TL, 38BL, 38TR, 38BR получают для обработки сигналы блочной информации, а устройства выбора 1/0 шин и регенерации, связанные с выбранными субматрицами 22TL3, 22BL3, 22TR3 и 22BR3, выбирают таким образом связанные с ними левые и правые 1/0 магистрали. Данные на первых парах 1/0 шин в левой и правой 1/0 магистралях пересылаются в соответствующие шинные пары соответствующих магистралей данных DB0-DB7 посредством соответствующих пар P10 шин и соответствующих усилителей считывания, включаемых во сигналу управления, который генерируется в ответ на сигналы блочной информации. Однако в это время, пары 1/0 шин, но пересылающие данные, то есть вторые пары 1/0 шин и подключенные к ним пары P10 шин удерживаются в состоянии регенерации посредством устройств 1/0 регенерации. Также, шинные пары данных, непересылающие данные, регенерируются мультиплексорами ввода/вывода данных 46, как будет объяснено ниже. Затем, если из-за второго сигнала выбора столбца CSL1 на шине столбцов L1 адресного потока столбцов соответствующие ключи выбора столбцов включены таким же образом, как обсуждалось выше, данные на соответствующих разрядных шинах передаются через вторые пары 1/0 шин в левой и правой 1/0 магистралях и через соответствующие пары P10 шин к парам шин данных, тогда как подсоединенные первые 1/0 шинные пары, P10 шинные пары и шинные пары данных регенерируются для дальнейшей передачи данных. Если сигналы выбора столбцов с CSL2 по CSL255 на шинах столбцов с L2 по L255, следующие за сигналом выбора столбцов CSL1 на шине столбцов L1, последовательно принимаются, такие операции, как пересылка данных, в случае наличия сигналов выбора столбцов CSL0 и CSL1 повторяются. Таким образом, все данные на парах разрядных шин, которые образовались от всех ячеек памяти, связанных с выбранными словарными шинами, могут быть считаны.

левой и правой 1/0 магистралей, расположенных по обоим краям соответствующих выбранных субматриц. Устройства выбора 1/0 шин и регенерации 38TL, 38BL, 38TR, 38BR получают для обработки сигналы блочной информации, а устройства выбора 1/0 шин и регенерации, связанные с выбранными субматрицами 22TL3, 22BL3, 22TR3 и 22BR3, выбирают таким образом связанные с ними левые и правые 1/0 магистрали. Данные на первых парах 1/0 шин в левой и правой 1/0 магистралях пересылаются в соответствующие шинные пары соответствующих магистралей данных DB0-DB7 посредством соответствующих пар P10 шин и соответствующих усилителей считывания, включаемых во сигналу управления, который генерируется в ответ на сигналы блочной информации. Однако в это время, пары 1/0 шин, но пересылающие данные, то есть вторые пары 1/0 шин и подключенные к ним пары P10 шин удерживаются в состоянии регенерации посредством устройств 1/0 регенерации. Также, шинные пары данных, непересылающие данные, регенерируются мультиплексорами ввода/вывода данных 46, как будет объяснено ниже. Затем, если из-за второго сигнала выбора столбца CSL1 на шине столбцов L1 адресного потока столбцов соответствующие ключи выбора столбцов включены таким же образом, как обсуждалось выше, данные на соответствующих разрядных шинах передаются через вторые пары 1/0 шин в левой и правой 1/0 магистралях и через соответствующие пары P10 шин к парам шин данных, тогда как подсоединенные первые 1/0 шинные пары, P10 шинные пары и шинные пары данных регенерируются для дальнейшей передачи данных. Если сигналы выбора столбцов с CSL2 по CSL255 на шинах столбцов с L2 по L255, следующие за сигналом выбора столбцов CSL1 на шине столбцов L1, последовательно принимаются, такие операции, как пересылка данных, в случае наличия сигналов выбора столбцов CSL0 и CSL1 повторяются. Таким образом, все данные на парах разрядных шин, которые образовались от всех ячеек памяти, связанных с выбранными словарными шинами, могут быть считаны.

Таким образом, возможно полное считывание страницы. В операции считывания первые пары 1/0 шин и вторые пары 1/0 шин пересылают множество данных, чередуя пересылку данных и регенерацию, а первые и вторые пары шин данных, связанные с первыми и вторыми парами 1/0 шин, также периодически повторяют пересылку данных и регенерацию. Мультиплексор вывода данных, подсоединенный к каждой магистрали данных, не только хранит множество данных, переданных параллельно с помощью любой из первых или вторых пар шин данных, но также регенерирует другие пары шин данных. Таким образом каждый мультиплексор вывода данных выдает непрерывно последовательные данные в ответ на сигналы выбора данных, предварительно выбирая множество данных на первых или вторых парах шин данных с заданным периодом. Последовательные данные выводятся с помощью соответствующего выходного буфера данных к контактам ввода/вывода данных синхронно с системным синхроимпульсом. Следовательно 8-битовые параллельные данные непрерывно выводятся в каждом цикле синхроимпульса.

Операции записи совершается в обратном порядке по отношению к операции считывания, которая обсуждалась выше. Как будет вкратце объяснено, последовательные входные данные выводятся синхронно с системным синхроимпульсом из входных буферов данных через чередующиеся контакты данных. Последовательные данные из входных буферов данных пересылаются, чередуясь, на первые и вторые пары шин данных соответствующих магистралей данных, в виде множества параллельных данных с каждым циклом системного синхроимпульса с помощью соответствующих демультиплексоров ввода данных. Данные на первых и вторых парах шин данных последовательно записываются в выбранные ячейки памяти с помощью соответствующих шинных драйверов, 1/0 магистралей, выбранных устройствами выбора 1/0 шин, и соответствующих пар разрядных шин. Пересылка данных и регенерация первых и вторых пар шин попеременно осуществляется в каждом цикле синхроимпульса таким же образом, как и в операции считывания.

Между первым и вторым банками установлено устройство управления 50 для управления операциями синхронной DRAM в соответствии с настоящим изобретением. Устройство управления 50 служит для генерирования управляющих синхроимпульсов или сигналов для управления дешифраторами строк и столбцов 18 и 24, устройствами выбора 1/0 шин и регенерации 38, усилителями считывания 1/0 и шинными драйверами 40 и 43, мультиплексорами ввода/вывода данных 46 и буферами ввода/вывода данных 48. Устройство управления 50 может рассматриваться как устройство управления строками и устройство управления столбцами. Устройство управления строками данных, пути данных и устройство управления столбцами будет описано ниже.

Устройство управления строками.

Общеизвестные DRAMы активизируются для выполнения операций считывания, записи и т. п. логическим уровнем  например низким уровнем. Ссылаясь на это, будем использовать термин "уровень

например низким уровнем. Ссылаясь на это, будем использовать термин "уровень  ". Уровень

". Уровень  несет определенную информацию, например, переключение

несет определенную информацию, например, переключение  с высокого на низкий уровень указывает на активное состояние, а переключение

с высокого на низкий уровень указывает на активное состояние, а переключение  с низкого уровня на высокий указывает на регенерацию. Однако так как синхронная DRAM должна работать синхронно с системными синхроимпульсами, вышеупомянутые команды, использующиеся в общеизвестной DRAM, не могут быть использованы в синхронной DRAM. Таким образом, поскольку для синхронной DRAM необходимо выбирать командную информацию по переднему или заднему фронту системного синхроимпульса (выборка командной информации в данном варианте реализации осуществляется по переднему фронту), то даже если в синхронной DRAM применяется уровень

с низкого уровня на высокий указывает на регенерацию. Однако так как синхронная DRAM должна работать синхронно с системными синхроимпульсами, вышеупомянутые команды, использующиеся в общеизвестной DRAM, не могут быть использованы в синхронной DRAM. Таким образом, поскольку для синхронной DRAM необходимо выбирать командную информацию по переднему или заднему фронту системного синхроимпульса (выборка командной информации в данном варианте реализации осуществляется по переднему фронту), то даже если в синхронной DRAM применяется уровень  команды известного уровня

команды известного уровня  не могут здесь быть использованы.

не могут здесь быть использованы.

На фиг. 5a и 5b представлены временные диаграммы команд, используемых в синхронной DRAM, описанной в настоящем изобретении. Фиг.5a представляет различные команды для случая, когда используется импульсный  сигнал (здесь и далее называемый импульсный

сигнал (здесь и далее называемый импульсный  , а фиг.5 представляет различные команды для случая использования уровня

, а фиг.5 представляет различные команды для случая использования уровня  Как можно видеть из чертежей, когда

Как можно видеть из чертежей, когда  низкий уровень, а

низкий уровень, а  сигнал разрешения записи

сигнал разрешения записи  имеют высокий уровень в момент переднего фронта системного синхроимпульса CLK, это означает активное состояние (активацию). После активации в момент переднего фронта системного синхроимпульса высокий уровень

имеют высокий уровень в момент переднего фронта системного синхроимпульса CLK, это означает активное состояние (активацию). После активации в момент переднего фронта системного синхроимпульса высокий уровень  низкий

низкий  и высокий уровень

и высокий уровень  указывают на команду считывания. Также после активации, в момент переднего фронта системного синхроимпульса CLK, высокий

указывают на команду считывания. Также после активации, в момент переднего фронта системного синхроимпульса CLK, высокий  низкий

низкий  и низкий уровень

и низкий уровень  представляет команду записи. Когда устанавливаются низкий уровень

представляет команду записи. Когда устанавливаются низкий уровень  высокий уровень

высокий уровень  и низкий уровень

и низкий уровень  в момент переднего фронта синхроимпульса CLK, выполняется операция регенерации. Команда установки рабочего режима в соответствии с особенностями настоящего изобретения устанавливается при низких уровнях

в момент переднего фронта синхроимпульса CLK, выполняется операция регенерации. Команда установки рабочего режима в соответствии с особенностями настоящего изобретения устанавливается при низких уровнях  в момент переднего фронта синхроимпульса CLK.

в момент переднего фронта синхроимпульса CLK.  - перед

- перед  (CBR) обновляет входы команд, когда

(CBR) обновляет входы команд, когда  держатся на низких уровнях, а WE держится на высоком уровне в момент переднего фронта синхроимпульса CLK. Команда самовосстановления, которая является вариацией CBP восстановления, когда

держатся на низких уровнях, а WE держится на высоком уровне в момент переднего фронта синхроимпульса CLK. Команда самовосстановления, которая является вариацией CBP восстановления, когда  находятся на низких уровнях, а WE на высоком в течение трех последовательных фронтов синхроимпульса CLK.

находятся на низких уровнях, а WE на высоком в течение трех последовательных фронтов синхроимпульса CLK.

Подобным образом, как и в общеизвестной DRAM, синхронная DRAM так же имеет временной промежуток между активацией  и активацией

и активацией  то есть время задержки

то есть время задержки  и период регенерации, предшествующий активации

и период регенерации, предшествующий активации  то есть время регенерации

то есть время регенерации  Для того, чтобы

Для того, чтобы

гарантировать правильность данных при считывании и записи, для разработчиков систем памяти очень минимальные значения  (соответственно 20 нс и 30 нс в синхронной DRAM настоящего изобретения). Для большего удобства разработчиков систем предпочтительно, чтобы минимальные значения

(соответственно 20 нс и 30 нс в синхронной DRAM настоящего изобретения). Для большего удобства разработчиков систем предпочтительно, чтобы минимальные значения  задавались количеством тактов системного синхроимпульса. Например, в случае, когда частота системных синхроимпульсов равна 100 MHz, а минимальные значения

задавались количеством тактов системного синхроимпульса. Например, в случае, когда частота системных синхроимпульсов равна 100 MHz, а минимальные значения  равны соответственно 20 нс и 30 нс, тогда

равны соответственно 20 нс и 30 нс, тогда  выраженные в циклах синхроимпульсов будут соответственно равны 2 и 3. Устройство управления строками является средством для генерирования сигналов или тактовых импульсов для выбора словарных шин в течение времени tRCD путем подачи на разрядные шины информационных данных из ячеек памяти операции считывания и осуществления регенерации в течение времени

выраженные в циклах синхроимпульсов будут соответственно равны 2 и 3. Устройство управления строками является средством для генерирования сигналов или тактовых импульсов для выбора словарных шин в течение времени tRCD путем подачи на разрядные шины информационных данных из ячеек памяти операции считывания и осуществления регенерации в течение времени

На фиг. 3 представлена блок-схема для генерирования синхроимпульсов или сигналов управления строками. Обращаясь к чертежу, отметим, что буфер синхроимпульса (здесь и далее называемый CLK буфер) 52 является буфером для преобразования внешнего системного синхроимпульса CLK уровня TTL (ТТЛ) во внутренний системный синхроимпульс уровня CMOS (КМОП). Синхронная DRAM выполняет различные внутренние операции, которые отбирают сигналы от внешнего кристалла либо посылают данные во внешний кристалл в момент переднего фронта синхроимпульса CLK. CLK буфер 52 генерирует синхроимпульс CLKA быстрее, чем измениться фаза вызвавшего его CLK.

Буфер разрешения синхроимпульса (CKE) 54 представляет собой устройство для генерирования сигнала маскирования синхроимпульса  для того чтобы маскировать генерацию синхроимпульса

для того чтобы маскировать генерацию синхроимпульса  в ответ на внешний сигнал разрешения синхроимпульса CKE и синхроимпульса CLKA. Как будет рассмотрено ниже, внутренний системный синхроимпульс

в ответ на внешний сигнал разрешения синхроимпульса CKE и синхроимпульса CLKA. Как будет рассмотрено ниже, внутренний системный синхроимпульс  запрещенный сигналом

запрещенный сигналом  вызовет операции "замораживания" внутренних операций кристалла, и входные и выходные данные посредством этого будут блокированы.

вызовет операции "замораживания" внутренних операций кристалла, и входные и выходные данные посредством этого будут блокированы.  буфер 56 принимает внешний сигнал

буфер 56 принимает внешний сигнал  сигналы адресов SRA10 и SRA11, сигнал

сигналы адресов SRA10 и SRA11, сигнал  буфера и сигнал

буфера и сигнал  буфера, генерируя таким образом синхроимпульс

буфера, генерируя таким образом синхроимпульс  для выборочной активации банков синхронно с синхроимпульсом

для выборочной активации банков синхронно с синхроимпульсом  выборочно или полностью регенерируя банки и автоматически регенерируя после восстановления или программирования рабочего режима. Здесь символом i обозначен банк. Также

выборочно или полностью регенерируя банки и автоматически регенерируя после восстановления или программирования рабочего режима. Здесь символом i обозначен банк. Также  буфер 56 генерирует сигнал ⊘RP, который активизирует

буфер 56 генерирует сигнал ⊘RP, который активизирует  по синхроимпульсу

по синхроимпульсу

Устройство установки рабочего режима 58 реагирует на команду установки рабочего режима, сигналы  и сигналы адреса RA0-RA6, для того чтобы устанавливать различные рабочие режимы, например, рабочие режимы для установки задержки по

и сигналы адреса RA0-RA6, для того чтобы устанавливать различные рабочие режимы, например, рабочие режимы для установки задержки по  длины пакета, представляющей количество непрерывных выходных данных, и адресный режим

длины пакета, представляющей количество непрерывных выходных данных, и адресный режим  представляющий зашифрованный внутренний адрес столбца. Устройство установки рабочего режима устанавливает по умолчанию рабочий режим, в котором заранее заданные задержка по

представляющий зашифрованный внутренний адрес столбца. Устройство установки рабочего режима устанавливает по умолчанию рабочий режим, в котором заранее заданные задержка по  длина пакета и адресный режим автоматически выбираются при отсутствии команды установки рабочего режима.

длина пакета и адресный режим автоматически выбираются при отсутствии команды установки рабочего режима.

Генератор главного синхроимпульса строки 62 реагирует на сигнал управления  и сигнал задержки CLj и генерирует главный синхроимпульс строки

и сигнал задержки CLj и генерирует главный синхроимпульс строки  который формируется в результате генерации синхроимпульсов или сигналов, связанных с

который формируется в результате генерации синхроимпульсов или сигналов, связанных с  цепью в выбранном банке. В соответствии с особенностями настоящего изобретения главный синхроимпульс строки

цепью в выбранном банке. В соответствии с особенностями настоящего изобретения главный синхроимпульс строки  имеет время задержки, зависящее от

имеет время задержки, зависящее от  задержки, величина которого гарантирует вывод двухбитовых данных синхронно с системным синхроимпульсом после команды регенерации.

задержки, величина которого гарантирует вывод двухбитовых данных синхронно с системным синхроимпульсом после команды регенерации.

Буфер строчного адреса 60 принимает главный синхроимпульс строки  сигналы внешних адресов A0-A11 и сигнал сброса строчного адреса

сигналы внешних адресов A0-A11 и сигнал сброса строчного адреса  для генерирования сигналов строчных адресов RA0-RA11 синхронно с синхроимпульсом

для генерирования сигналов строчных адресов RA0-RA11 синхронно с синхроимпульсом  Буфер 60 принимает счетный сигнал от счетчика восстановления в операции восстановления, с тем, чтобы выдать сигналы строчных адресов RA0-RA11 для восстановления.

Буфер 60 принимает счетный сигнал от счетчика восстановления в операции восстановления, с тем, чтобы выдать сигналы строчных адресов RA0-RA11 для восстановления.

Генератор управляющего сигнала строки 64 принимает главный синхроимпульс строки  и сигнал блочной информации BLS от строчного дешифратора 18 для генерирования дополнительного управляющего сигнала словарной шины ⊘X, стартового сигнала считывания ⊘S для активации выбранного усилителя считывания, сигнала сброса строчного адреса

и сигнал блочной информации BLS от строчного дешифратора 18 для генерирования дополнительного управляющего сигнала словарной шины ⊘X, стартового сигнала считывания ⊘S для активации выбранного усилителя считывания, сигнала сброса строчного адреса  для сброса буфера строчного адреса сигнала ⊘RAL для приведения в действие буфера адреса столбцов 344 и сигнала

для сброса буфера строчного адреса сигнала ⊘RAL для приведения в действие буфера адреса столбцов 344 и сигнала  для информирования о завершении синхроимпульсов или сигналов, относящихся к строкам.

для информирования о завершении синхроимпульсов или сигналов, относящихся к строкам.

Генератор разрешения синхроимпульсов столбцов 66 принимает сигнал  и главный синхроимпульс строки

и главный синхроимпульс строки  с тем чтобы генерировать сигналы

с тем чтобы генерировать сигналы  для разрешения работы устройств, связанных со столбцами.

для разрешения работы устройств, связанных со столбцами.

Высокочастотный генератор синхроимпульсов 68, в случая, когда частота внешних системных синхроимпульсов CLK низкая, а также требуется вывод двухбитовых данных в операции считывания после команды регенерации, генерирует синхроимпульс CNTCLK9 с большей частотой, чем частота синхроимпульса CLK, с тем, чтобы предотвратить уменьшение периода регенерации. Как будет обсуждено ниже, поскольку генератор адресов столбцов генерирует адреса столбцов по импульсу CNTCLK9, уменьшение периода регенерации будет предотвращено.

Ниже будет дано подробное объяснение по предпочтительным вариантам реализации элементов, образующих генератор синхроимпульсов  цепи.

цепи.

1. CLK буфер и CKE буфер

На фиг. 6 представлена схема CLK буфера 52, а на фиг.7 схема CKE буфера 54 в соответствии с настоящим изобретением. На фиг.8 изображена временная диаграмма для CLK буфера 52 и CKE буфера 54.

Рассмотрим фиг. 6. Дифференциальный усилитель 70 сравнивает внешний системный синхроимпульс CLK с опорным напряжением Vref (= 1.8 В) и таким образом преобразует внешний сигнал CLK уровня TTL во внутренний сигнал уровня CMOS, например, высокий уровень 3 В или низкий уровень 0 В. Вместо дифференциального усилителя 70 можно использовать другие входные буферы, которые могут переносить уровень TTL сигнала на CMOS сигнал. Как можно видеть на фиг. 8, синхроимпульс CLKA получается путем инвертирования системного синхроимпульса CLK с помощью входного буфера 70, такого как дифференциальный усилитель, и логических элементов то есть с помощью инверторов 76 и логического элемента NAND (И-НЕ) 78. Триггер или защелка 80, которая состоит из логических элементов NOP (ИЛИ-НЕ) 72 и 74, выдает системные синхроимпульсы уровня CMOS, когда сигнал маскирования синхроимпульса  низкий. Выходной синхроимпульс из триггера 80 подается в устройство регулирования ширины импульса 85, которое состоит из схемы задержки 82 и логического элемента И-НЕ 84. Хотя в схеме задержки 82 для простоты показаны только инверторы, может быть использована схема, содержащая инвертор и конденсатор или другие средства задержки. Таким образом, когда сигнал

низкий. Выходной синхроимпульс из триггера 80 подается в устройство регулирования ширины импульса 85, которое состоит из схемы задержки 82 и логического элемента И-НЕ 84. Хотя в схеме задержки 82 для простоты показаны только инверторы, может быть использована схема, содержащая инвертор и конденсатор или другие средства задержки. Таким образом, когда сигнал  низкий, из CLK буфера выводится внутренний системный синхроимпульс

низкий, из CLK буфера выводится внутренний системный синхроимпульс  как показано на фиг.8. Однако, когда сигнал

как показано на фиг.8. Однако, когда сигнал  высокий, сигнал на выходе триггера 80 становится низким, для того чтобы прекратить генерирование синхроимпульса

высокий, сигнал на выходе триггера 80 становится низким, для того чтобы прекратить генерирование синхроимпульса  На фиг. 6, инвертор 89, p-канальный МОП транзистор 90 и n-канальные МОП транзисторы 91 и 94 служат для обеспечения установки начального состояния для соответствующих режимов в ответ на сигнал включения питания

На фиг. 6, инвертор 89, p-канальный МОП транзистор 90 и n-канальные МОП транзисторы 91 и 94 служат для обеспечения установки начального состояния для соответствующих режимов в ответ на сигнал включения питания  от известного устройства включения питания. Сигнал включения питания

от известного устройства включения питания. Сигнал включения питания  держится на низком уровне до тех пор, пока напряжение источника питания Vcc не достигнет необходимого уровня после подачи питающего напряжения.

держится на низком уровне до тех пор, пока напряжение источника питания Vcc не достигнет необходимого уровня после подачи питающего напряжения.

Рассмотрим фиг. 7. Входной буфер 70 преобразует сигнал разрешения внешнего синхроимпульса CKE в сигнал CMOS уровня. Для уменьшения потребления мощности работа входного буфера 70 запрещается операцией самовосстановления. Входной буфер 70 выдает инверсный, по отношению к сигналу CKE, сигнал CMOS уровня на шину 90. Инвертированный сигнал CKE подается на сдвиговый регистр 86 для сдвига по синхроимпульсу CLKA, инверсным по отношению к синхроимпульсу CLK. Выход сдвигового регистра 86 подключен к выходу сигнала  с помощью триггера 88 на элементах ИЛИ-НЕ и инвертора. Выход сдвигового регистра 86 подсоединен к выходу сигнала CKEBPU через инверторы.

с помощью триггера 88 на элементах ИЛИ-НЕ и инвертора. Выход сдвигового регистра 86 подсоединен к выходу сигнала CKEBPU через инверторы.

Сигнал разрешения синхроимпульсов CKE запрещает генерацию системного синхроимпульса  с низким уровнем CKE для замораживания внутренней работы кристалла. Обратимся вновь к фиг.8. Иллюстрация сделана для сигнала CKE с низким уровнем импульса для маскирования синхроимпульса CLK 98. При помощи низкого уровня сигнала CKE, входная шина 90 сдвигового регистра 86 поддерживает высокий уровень сигнала. После того, как синхроимпульс CLKA 100 переходит на низкий уровень, выход сдвигового регистра 86 переходит на высокий уровень. Таким образом

с низким уровнем CKE для замораживания внутренней работы кристалла. Обратимся вновь к фиг.8. Иллюстрация сделана для сигнала CKE с низким уровнем импульса для маскирования синхроимпульса CLK 98. При помощи низкого уровня сигнала CKE, входная шина 90 сдвигового регистра 86 поддерживает высокий уровень сигнала. После того, как синхроимпульс CLKA 100 переходит на низкий уровень, выход сдвигового регистра 86 переходит на высокий уровень. Таким образом  и CKEBPU становятся сигналами с высоким и низким уровнем соответственно. Затем, после того, как следующий синхроимпульс CLKA 102 переходит на низкий уровень, выход сдвигового регистра 86 меняется на низкий уровень, таким образом заставляя сигнал CKEBPU перейти на высокий уровень. В это время, поскольку выход триггера 88 держится на низком уровне, сигнал

и CKEBPU становятся сигналами с высоким и низким уровнем соответственно. Затем, после того, как следующий синхроимпульс CLKA 102 переходит на низкий уровень, выход сдвигового регистра 86 меняется на низкий уровень, таким образом заставляя сигнал CKEBPU перейти на высокий уровень. В это время, поскольку выход триггера 88 держится на низком уровне, сигнал  поддерживается на высоком уровне. Однако после того как следующий синхроимпульс CLKA 104 переходит на высокий уровень, сигнал

поддерживается на высоком уровне. Однако после того как следующий синхроимпульс CLKA 104 переходит на высокий уровень, сигнал  переходит на низкий уровень. Таким образом, как обсуждалось в связи с фиг.6, синхроимпульс

переходит на низкий уровень. Таким образом, как обсуждалось в связи с фиг.6, синхроимпульс  связанный с синхроимпульсом 98, маскируется высоким уровнем сигнала

связанный с синхроимпульсом 98, маскируется высоким уровнем сигнала

Поскольку внутреннее функционирование синхронной DRAM происходит синхронно с синхроимпульсом  маскирование

маскирование  переводит процесс внутреннего функционирования в состояние ожидания. Таким образом, для предотвращения излишнего потребления мощности в состоянии ожидания, сигнал CKEBPU используется для запрещения синхронизации входных буферов по сигналу

переводит процесс внутреннего функционирования в состояние ожидания. Таким образом, для предотвращения излишнего потребления мощности в состоянии ожидания, сигнал CKEBPU используется для запрещения синхронизации входных буферов по сигналу  Соответственно, следует учесть, что сигнал CKE должен быть подан, по крайней мере, за один цикл по маскируемого синхроимпульса CLK, чтобы его промаскировать, и должен сохранять высокий уровень для выполнения нормальной работы.

Соответственно, следует учесть, что сигнал CKE должен быть подан, по крайней мере, за один цикл по маскируемого синхроимпульса CLK, чтобы его промаскировать, и должен сохранять высокий уровень для выполнения нормальной работы.

2.  буфер

буфер

Синхронная DRAM включает два банка памяти 12 и 14 на одном и том же кристалле для достижения высокоскоростной пересылки данных. Для достижения высоких характеристик синхронной DRAM необходимы устройства управления, которые выборочно управляют различными операциями в каждом банке. Соответственно,  буфер является входным буфером, выполняющим множество функций в соответствии с особенностями настоящего изобретения.

буфер является входным буфером, выполняющим множество функций в соответствии с особенностями настоящего изобретения.

На фиг. 9 представлена схема, показывающая многофункциональный входной буфер импульса  в соответствии с настоящим изобретением. Обратимся к фиг. 9. Аналогично тому, как обсуждалось выше, входной буфер 70 переводит внешний строб-сигнал адреса строки

в соответствии с настоящим изобретением. Обратимся к фиг. 9. Аналогично тому, как обсуждалось выше, входной буфер 70 переводит внешний строб-сигнал адреса строки  во внутренний сигнал CMOS уровня. Входной буфер 70 блокируется ключевой схемой 106 для переключения маскирования системных синхроимпульсов, сигналов самовосстановления и включения питания CKEBPU,

во внутренний сигнал CMOS уровня. Входной буфер 70 блокируется ключевой схемой 106 для переключения маскирования системных синхроимпульсов, сигналов самовосстановления и включения питания CKEBPU,  Сигнал CMOS уровня от входного буфера 70 подведен к входу 110 устройства синхронизации 108 для обеспечения выхода 112

Сигнал CMOS уровня от входного буфера 70 подведен к входу 110 устройства синхронизации 108 для обеспечения выхода 112  импульсом

импульсом  который синхронизирует сигнал CMOS уровня с внутренним системным синхроимпульсом

который синхронизирует сигнал CMOS уровня с внутренним системным синхроимпульсом  Таким образом, как показано на фиг.10, в моменты

Таким образом, как показано на фиг.10, в моменты  сигнал, находящийся на низком уровне, генерирует

сигнал, находящийся на низком уровне, генерирует  импульс

импульс  с высоким уровнем после заданной задержки на выходе 112.

с высоким уровнем после заданной задержки на выходе 112.

На фиг. 9 оставшееся устройство, исключая входной буфер 70, устройство синхронизации 108 и ключевую схему 106, является многофункциональным устройством управления 114, предназначенным для управления соответствующими банками. Поскольку n-канальные транзисторы 148 и 150 включены сигналом  , находящимся на низком уровне в момент включения напряжения питания, первый

, находящимся на низком уровне в момент включения напряжения питания, первый  синхроимпульс

синхроимпульс  для первого банка 12 и второй

для первого банка 12 и второй  синхроимпульс

синхроимпульс  для второго банка 14 зафиксированы оба в исходных состояниях, то есть на низких уровнях при помощи защелок 154 и 156.

для второго банка 14 зафиксированы оба в исходных состояниях, то есть на низких уровнях при помощи защелок 154 и 156.

Для активации первого банка 12 и одновременной деактивации второго банка 14 в момент  как показано на фиг.10, внешний сигнал адреса ADD совместно с адресом A11, находящимся на низком уровне, подводится к кристаллу. Тогда, адресный буфер, как будет обсуждаться ниже, генерирует адресный сигнал SRA11 низкого уровня (

как показано на фиг.10, внешний сигнал адреса ADD совместно с адресом A11, находящимся на низком уровне, подводится к кристаллу. Тогда, адресный буфер, как будет обсуждаться ниже, генерирует адресный сигнал SRA11 низкого уровня ( высокого уровня) с адресным сигналом ADD. С другой стороны, в момент

высокого уровня) с адресным сигналом ADD. С другой стороны, в момент

времени t1, поскольку оба  сигналы держатся на высоком уровне,

сигналы держатся на высоком уровне,  держат низкий уровень, как будет рассмотрено далее. Таким образом, логические элементы ИЛИ-НЕ 116 и 126 выдают низкий уровень, а логические элементы И-НЕ 122 и 124 выдают высокий уровень. Затем, логические элементы И-НЕ 128 и 130 выдают высокий и низкий уровень соответственно. Когда импульс

держат низкий уровень, как будет рассмотрено далее. Таким образом, логические элементы ИЛИ-НЕ 116 и 126 выдают низкий уровень, а логические элементы И-НЕ 122 и 124 выдают высокий уровень. Затем, логические элементы И-НЕ 128 и 130 выдают высокий и низкий уровень соответственно. Когда импульс  переходит на высокий уровень, логический элемент И-НЕ 132 переходит на низкий уровень, а логические элементы И-НЕ с 134 по 138 на высокий уровень. Затем p-канальный транзистор 140 открывается, а p-канальный транзистор 144 и n-канальные транзисторы 142 и 146 сохраняют выключенное состояние. Таким образом защелка 154 сохраняет низкий уровень. С другой стороны, когда

переходит на высокий уровень, логический элемент И-НЕ 132 переходит на низкий уровень, а логические элементы И-НЕ с 134 по 138 на высокий уровень. Затем p-канальный транзистор 140 открывается, а p-канальный транзистор 144 и n-канальные транзисторы 142 и 146 сохраняют выключенное состояние. Таким образом защелка 154 сохраняет низкий уровень. С другой стороны, когда  переходит на низкий уровень, все логические элементы И-НЕ с 132 по 138 переходят на высокий уровень, тем самым выключая транзисторы с 140 по 146. В результате первый

переходит на низкий уровень, все логические элементы И-НЕ с 132 по 138 переходят на высокий уровень, тем самым выключая транзисторы с 140 по 146. В результате первый  синхроимпульс

синхроимпульс  переходит на высокий уровень, а второй

переходит на высокий уровень, а второй  синхроимпульс

синхроимпульс  сохраняет низкий уровень посредством защелки 156, которая изначально сохраняет высокий уровень. Таким образом, первый банк 12 активизируется синхроимпульсом

сохраняет низкий уровень посредством защелки 156, которая изначально сохраняет высокий уровень. Таким образом, первый банк 12 активизируется синхроимпульсом  путем выполнения нормальной операции, такой как чтение или запись. При этом второй банк 14 не активизируется низким уровнем синхроимпульса

путем выполнения нормальной операции, такой как чтение или запись. При этом второй банк 14 не активизируется низким уровнем синхроимпульса

С другой стороны, для доступа к синхронной DRAM с высокой скоростью пересылки данных, второй банк может быть активизирован во время активации первого банка. Это можно сделать посредством активации второго банка, подавая адрес A11, находящийся на высоком уровне, после активизации первого банка. Затем адресный сигнал SRA11 переходит на высокий уровень (PA11 переходит на низкий уровень). Таким же образом, как было рассмотрено выше, логический элемент И-НЕ 136 выдает низкий уровень, а все логические элементы И-НЕ 132, 134 и 138 выдают высокий уровень. Таким образом  поддерживается в предыдущем состоянии, то есть на высоком уровне, а

поддерживается в предыдущем состоянии, то есть на высоком уровне, а  переходит на высокий уровень. В результате как первый, так и второй банки переходят в активное состояние.

переходит на высокий уровень. В результате как первый, так и второй банки переходят в активное состояние.

Во время операций считывания или записи во втором банке первый банк также может регенерироваться. В момент или до того, как выдана команда регенерации в момент  как показано на фиг.10, внешние адресные сигналы A10 и A11, имеющие низкий уровень, подводятся к соответствующим адресным контактам кристалла. Затем адресные сигналы SRA10 и SRA11 переходят на низкий уровень (