(54) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2110091C1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

| Множительно-делительное устройство | 1974 |

|

SU554540A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Множительно-делительное устройство | 1986 |

|

SU1361581A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU934493A1 |

| Множительно-делительное устройство | 1978 |

|

SU723596A1 |

Изобретение относится к аналоговой вычислительной технике, предназначено для умножения и деления медленно меняющихся аналоговых сигналов и может быть использовано в аналоговых вычислительных устройствах.

Известно устройство для умножения и деления медленно меняющихся сигналов, построенное по принципу время- импульсного преобразования, содержащее преобразователь аналог-временной интервал (АВИ|,блок управления и схему умножения,выполненную на интеграторе jt фиксаторе 1. Однако наличие в устройстве источника опорного напряжения и третьего компаратора (для разделения каждого шага умножения-деления на три интервалавремени - заряд, интегрирование и перенос) усложняет устройство и снижает его точность.

Известно также устройство для умножения и деления сигналов, содержащее преобразователь аналог-временной интегрвал, первый вход которого является входом первого сомножителя устройства, а второй вход - входом делителя устройства, триггер, два элемента И-НЕ, первый интегратор, содержащий операционный усилитель.

входной зарядный ключ и ключ сброса, вклю 1енный в цепь обратной связи операционного усилителя первого интегратора, и второй интегратор, содержащий операционный усилитель и входной зарядный ключ, выход преобразователя аналог-временной интервал подключен к входу триггера и к одному входу первого элемента И-НЕ

10 другой вход которого подключен к неинвертирующему выходу триггера, выход первого элемента И-НЕ подключен к одному входу второго элемента И-НЕ, к неинвертирующему выходу триггера,

15 выход второго элемента И-НЕ подключён к управляющему входу ключа сброса первого интегратора, вход первого интегратора является входом второго сомножителя устройства, выход второго

20 интегратора является выходом устройства 2.

Однако для умножения медленно мен,якнцихся сигналов это устройство яв25ляется сложным и, кроме того, необходимость обеспечения идентичности параметров интеграторов схемы умно;кения затрудняет наладку устройства.

Цель изобретения - упрощение мно30жительно-делительного устройства.

Поставленная цель достигается тем, что в известном множительноделительном устройстве инвертирующий вход триггера подключен к управляюще му входу входного зарядного ключа второго интегратора, а выход первого интегратора подключен ко входу второго.

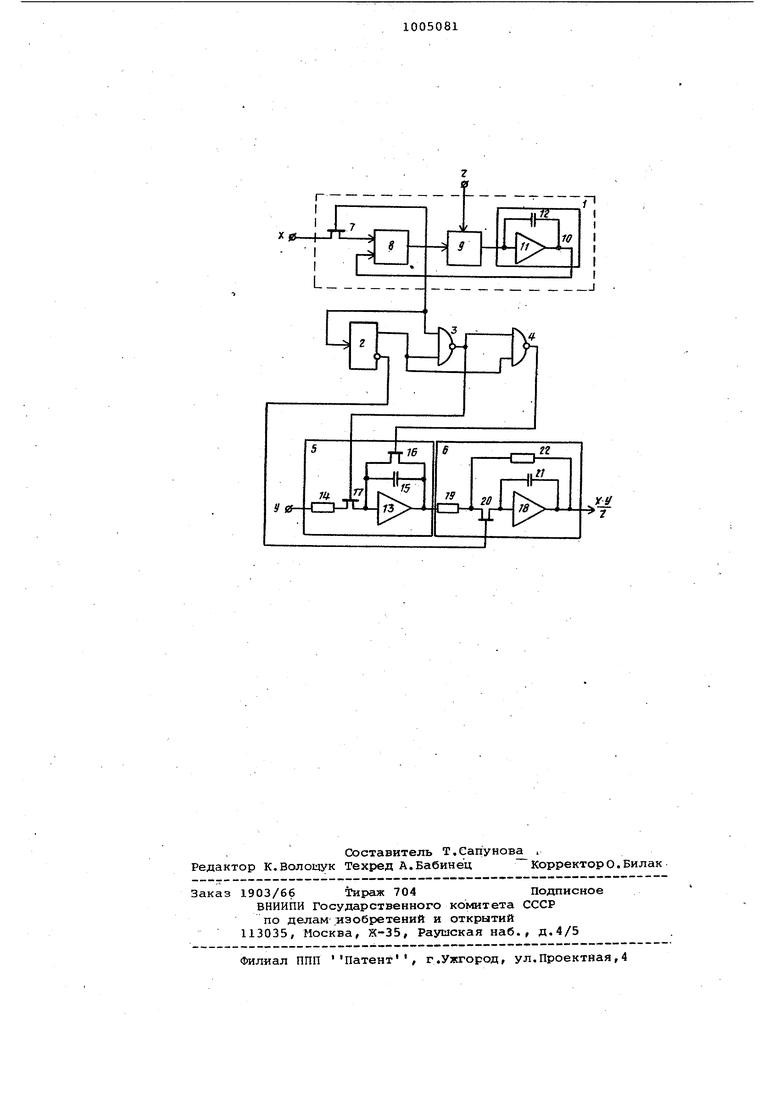

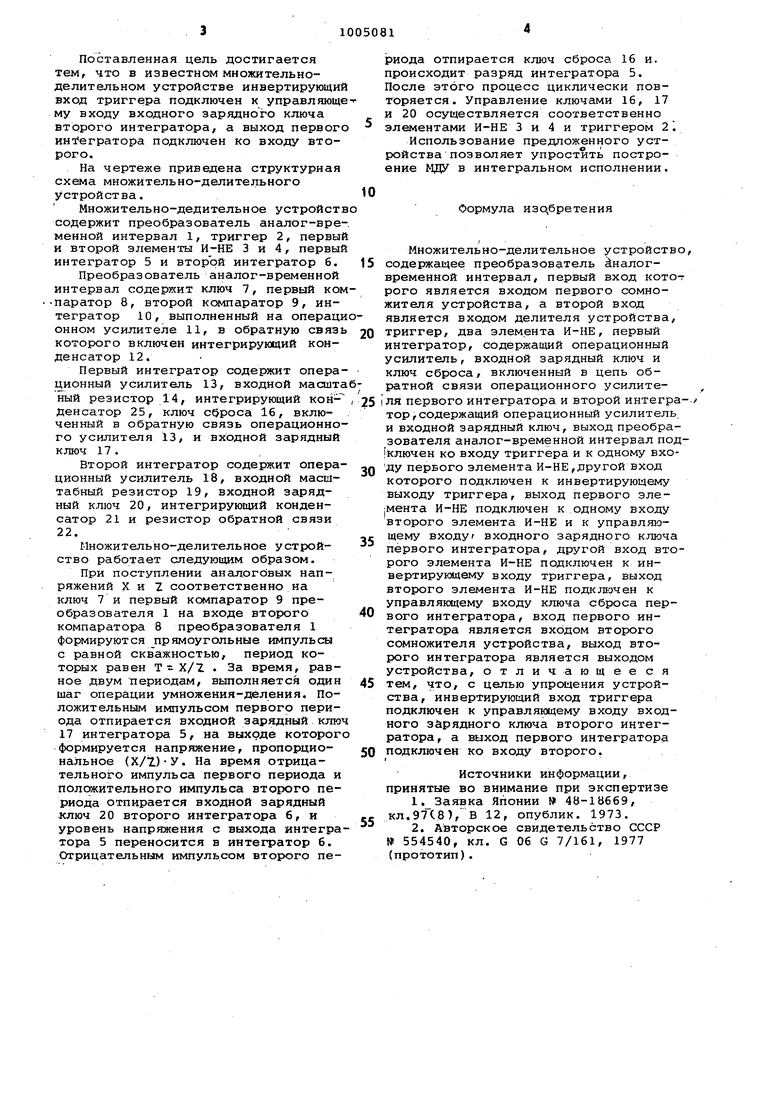

На чертеже приведена структурная схема множительно-делительного устройства.

Множительно-дедительное устройств содержит преобразователь аналог-временной интервал 1, триггер 2, первый и второй элементы И-НЕ 3 и 4, первый интегратор 5 и второй интегратор 6.

Преобразователь аналог-временной интервал содержит ключ 7, первый компаратор 8, второй компаратор 9, интегратор 10, выполненный на операционном усилителе 11, в обратную связь которого включен интегрирующий конденсатор 12.

Первый интегратор содержит операционный усилитель 13, входной масшта ный резистор 14, интегрирующий денсатор 25, ключ сброса 16, включенный в обратную связь операционного усилителя 13, и входной зарядный ключ 17.

Второй интегратор содержит операционный усилитель 18, входной масштабный резистор 19, входной зарядный ключ 20, интегрирующий конденсатор 21 и резистор обратной связи 22.

Множительно-делительное устройство работает следующим образом.

При поступлении аналогйвых напряжений X и 2 соответственно на ключ 7 и первый компаратор 9 преобразователя 1 на входе второго компаратора 8 преобразователя 1 формируются прямоугольные импульсы с равной ск1важностью, период которых равен Т - X/Z . За время, равное двум периодам, выполняется один шаг операции умножения-деления. Положительным импульсом первого периода отпирается входной зарядный.ключ 17 интегратора 5, на выходе которого формируется напряжение, пропорциональное (Х/7.)У. На время отрицательного импульса первого периода и положительного импульса второго периода отпирается входной зарядный ключ 20 второго интегратора б, и уровень напряжения с выхода интегратора 5 переносится в интегратор 6. Отрицательным импульсом второго периода отпирается ключ сброса 16 и. происходит разряд интегратора 5. После этого процесс циклически повторяется. Управление ключами 16, 17 и 20 осуществляется соответственно элементами И-НЕ 3 и 4 и триггером 2, Использование предложенного устройства позволяет упростить построение МДУ в интегральном исполнении.

Оормула изцбретения

Множительно-делительное устройств содержащее преобразователь Аналогвременной интервал, первый вход кото рого является входом первого сомножителя устройства, а второй вход является входом делителя устройства, триггер, два элемента И-НЕ, первый интегратор, содержащий операционный усилитель, входной зарядный ключ и ключ сброса, включенный в цепь обратной связи операционного усилите|ля первого интегратора и второй интегра тор, содержащий операционный усилитель и входной зарядный ключ, выход преобразователя аналог-временной интервал под ключен ко входу триггера и к одному входу первого элемента И-НЕ,другой вход которого подключен к инвертирующему выходу триггера, выход первого эле|мента И-НЕ подключен к одному входу второго элемента И-НЕ и к управляющему входуг входного зарядного ключа первого интегратора, другой вход второго элемента И-НЕ подключен к инвертирующему входу триггера, выход второго элемента И-НЕ подключен к управляющему входу ключа сброса первого интегратора, вход первого интегратора является входом второго сомножителя устройства, выход второго интегратора является выходом устройства, отличающееся тем, что, с целью упрощения устройства, инвертирующий вход триггера подключен к управляющему входу входного зйрядного ключа второго интегратора, а выход первого интегратора подключен ко входу второго.

Источники информации, принятые во внимание при экспертизе

1, Заявка Японии № 48-1Ь669, кл.971.8), В 12, опублик. 1973.

Авторы

Даты

1983-03-15—Публикация

1978-08-21—Подача