Изобретение относится к переменному коррелятору для системы связи с растянутым диапазоном части и, в частности, к коррелятору для осуществления операции корреляции путем переменного управления длиной корреляции.

В системе связи с растянутым диапазоном частот точная синхронизация в принципе является важным фактором при восстановлении исходного сигнала из сигнала с растянутым диапазоном частот. Приемник генерирует код, аналогичный коду расширения спектра, используемому для растягивания диапазона частот в передатчике, в котором используется код расширения спектра типа псевдошумовой последовательности и со скачкообразным изменением частоты. Чтобы обеспечить совпадение локально генерируемого кода расширения спектра с кодом в принимаемом сигнале используется синхронизация. Синхронизация предусматривает обнаружение и сопровождение сигнала с учетом его протяженности и используемой последовательности. В результате обнаружения код в принимаемом сигнале и локально генерируемый растянутый код расширения спектра совмещаются друг с другом с точностью до половины элемента кода. Сопровождение должно препятствовать потере синхронизации обнаруженного сигнала и уменьшить разность во времени между кодом в принимаемом сигнале и локально генерируемым кодом расширения спектра. В приемнике системы связи с растянутым диапазоном частот обнаружение кода должно предшествовать его сопровождению. Если синхронизация нарушается при выполнении сопровождения, то повторно выполняется обнаружение кода. Для осуществления обнаружения необходимо выполнить корреляционную обработку в процессе смешивания сигнала с растянутым диапазоном частот из передатчика с тем же самым кодом, что и использованный при передаче, чтобы восстановить первоначальный сигнал.

Известен вычислитель модуля (или квадрата модуля) корреляционного интеграла, содержащий средство для перемножения первых и вторых входных данных канала на первые и вторые опорные сигналы, средство для суммирования и возведения в квадрат накопленного сигнала [1].

Однако известный коррелятор при его использовании в схемах установления синхронизации в приемниках системы связи будет испытывать перегрузку при вычислениях, осуществляемых в соответствии с необходимой длиной корреляции. Ввиду того, однако, что длина корреляции является фиксированной независимо от условий применения, указанная схема должна заменяться в случае, когда значение корреляции должно будет изменяться с применением длины корреляции. В случае, если такой комплексный генератор реализуется на специализированной интегральной схеме, ориентированной на конкретное применение, такая интегральная схема должна заменяться на новую всякий раз при изменении длины корреляции.

Задачей изобретения является создание коррелятора, в котором устранены вышеуказанные недостатки известного коррелятора и который обеспечивает повышение эффективности обработки за счет управляемого изменения длины корреляции.

Указанный результат достигается тем, что коррелятор системы связи с растянутым диапазоном частот, содержащий средство для смешивания последовательных входных данных с опорными данными и средство накопления смешанных данных, содержит средство управления длиной корреляции для изменения предварительно установленной длины корреляции, при этом средство накопления выполнено с возможностью накопления смешанных данных до числа, соответствующего установленной длине корреляции.

Указанный технический результат достигается также тем, что коррелятор системы связи с растянутым диапазоном частот, содержащий средство для перемножения первых и вторых входных данных канала на первые и вторые опорные данные соответственно для получения данных перемножения, согласно изобретению, содержит средство для накопления упомянутых данных перемножения согласно числу бит, соответствующему предварительно установленной длине корреляции, для формирования накопленного сигнала, средство для суммирования и возведения в квадрат полученного накопленного сигнала для формирования данных корреляции и средство управления длиной корреляции для изменения упомянутого числа бит, соответствующего упомянутой предварительно установленной длине корреляции.

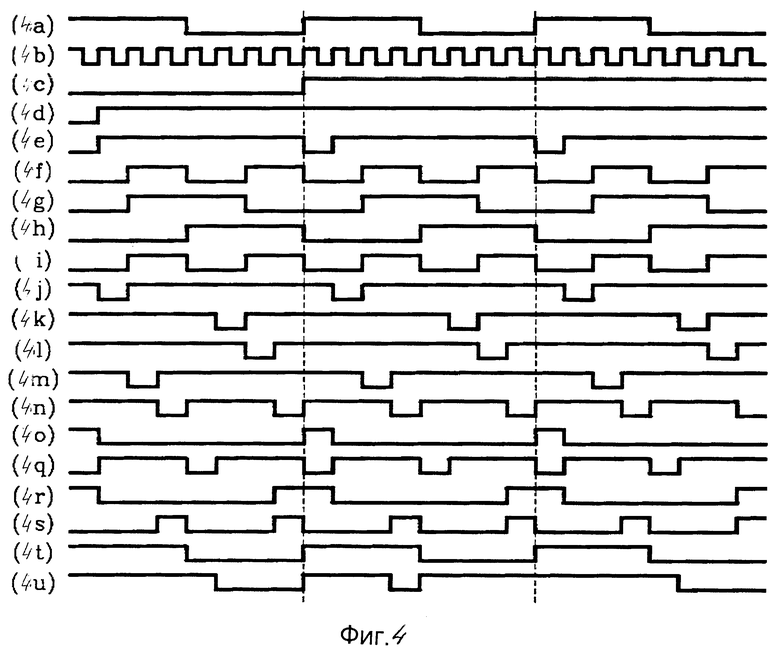

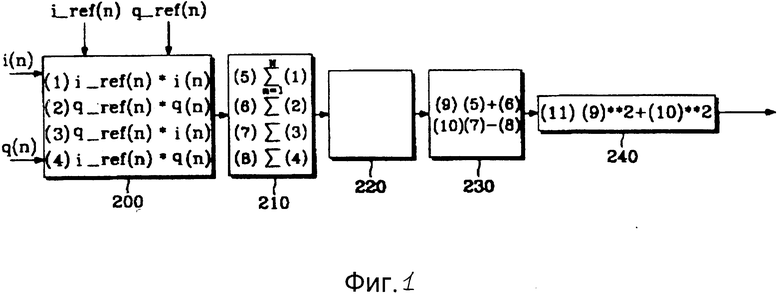

На фиг. 1 показана блок-схема цифрового комплексного коррелятора, соответствующего возможному варианту осуществления изобретения; на фиг. 2 - блок-схема цифрового комплексного коррелятора, соответствующего другому варианту осуществления изобретения; на фиг. 3 - подробная схема цифрового комплексного коррелятора, показанного на фиг. 2; на фиг. 4 - временные диаграммы синхронизации, показывающие различные сигналы, формируемые в цифровом комплексном корреляторе, показанном на фиг. 3.

Как показано на фиг. 1, цифровой комплексный коррелятор, соответствующий одному из вариантов осуществления изобретения, содержит перемножитель 200 входных данных на опорные данные, накопитель 210 выходных данных перемножителя 200, схему 200 управления длиной корреляции, предназначенную ля управления длиной N корреляции при вычислениях корреляции и осуществляющую управление длиной корреляции N в соответствии с конкретными условиями применения.

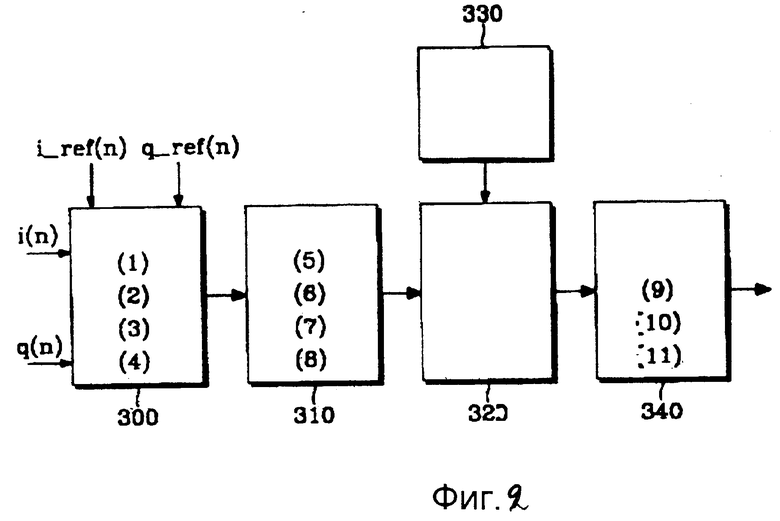

Показанный на фиг. 2 цифровой комплексный коррелятор, соответствующий другому варианту осуществления изобретения, содержит перемножитель 300, накопитель 310, контроллер 320 длины корреляции, генератор 330 сигналов управления длиной корреляции и схему 340 суммирования и возведения в квадрат.

Цифровой комплексный коррелятор работает следующим образом.

Пусть i(n) + jq(n) - входные данные, i_ref(n)+jq_ref(n) - опорные данные для вычисления комплексного значения корреляции с использованием указанных входных данных.

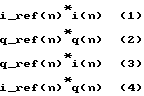

Затем перемножитель 300 умножает входные данные i(n) + jq(n) на опорные данные i_ref(n)+jq_ref(n) и формирует выходные сигналы вида .

.

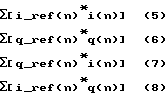

После этого, накопитель 310 накапливает выходные сигналы перемножителя 300 для формирования следующих сигналов: .

.

Выходные сигналы накопителя 310 подаются затем на схему 340 суммирования и возведения в квадрат для формирования выходных сигналов вида (9) и (10). Выражение (11) представляет собой квадрат выражения (10), как представлено ниже: .

.

Полученное в результате значение корреляции имеет вид .

.

Генератор 330 сигналов управления длинной корреляции генерирует сигнал управления длиной корреляции. В частности, длиной корреляции можно управлять в соответствии с конкретными условиями применения. Контроллер 320 длины корреляции управляет операцией корреляции в соответствии с сигналом управления длиной корреляции. А именно, накопитель 310 выдает результаты согласно формулам (5) - (8) в схему 340 суммирования и возведения в квадрат после завершения вычисления при n = N. В то время, как схема 340 суммирования и возведения в квадрат выполняет вычисление согласно выражениям (9) - (11), перемножитель 300 получает новые данные для повторного вычисления значения корреляции, начиная с n = 1.

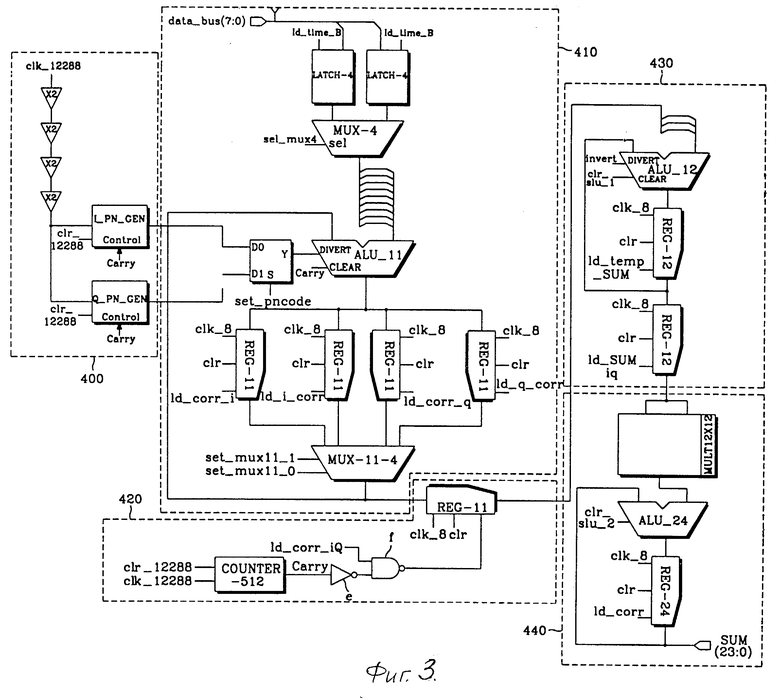

На фиг. 3 изображена подробная схема цифрового комплексного коррелятора, соответствующего предпочтительному варианту осуществления изобретения, обеспечивающего синхронизацию кода в устройстве диапазона модулирующих частот сотовой системы связи с множественным доступом с кодовым разделением каналов.

На фиг. 4 изображены различные сигналы, формируемые в цифровом комплексном корреляторе, представленном на фиг. 3.

Ниже, со ссылками на фиг. 3, 4 будут подробно описаны операции цифрового комплексного коррелятора, соответствующего изобретению

Генератор 400 опорных данных получает тактовый сигнал синхронизации clk_12288 (фиг. 4a) и генерирует опорные данные i_ref(n),jq_ref(n). .

Далее подробно описаны конфигурация и работа накопителя 410.

Мультиплексор MUX-4 выбирает один из сигналов входных данных i(n), jq(n) в ответ на сигнал синхронизации sel_mux4 (фиг. 4f) и подает выбранный сигнал входных данных на входной вывод арифметического устройства ALU_11. . В этот момент мультиплексор MUX-4 выбирает один из сигналов опорных данных i_ref(n), jq_ref(n) в ответ на сигнал синхронизации sel_pncode (фиг. 4g) и генерирует сигнал (фиг. 4r), подаваемый на инверсный вывод арифметического устройства ALU_11. . Арифметическое устройство ALU_11. подает опорные данные i_ref(n),jq_ref(n) на регистры с первого по четвертый a, b, c, d. Первый регистр "a" выводит опорные данные в соответствии с тактовыми сигналами clk_8, clr, ld_corr_i, , соответственно (4b), (4d), (4j) на фиг. 4. Второй регистр "b" выводит опорные данные в соответствии с тактовыми сигналами clk_8, clr и с тактовым сигналом ld_r_corr (фиг. 4m). Третий регистр "c" выводит опорные данные в соответствии с тактовыми сигналами clk8, clr и тактовым сигналом ld_corr_q (фиг. 4k). Наконец, четвертый регистр "d" выводит опорные данные в соответствии с тактовыми сигналами clk_8, , clr и тактовым сигналом ld_q_corr (фиг. 41). Мультиплексор MUX-11-4 выводит выходные сигналы от первого до четвертого регистров "a", "b", "c", "d" в ответ на тактовые сигналы set_mux11_1, set_mux11_0 соответственно (4h) и (4i) на фиг. 4.

Схема 420 управления длиной корреляции содержит генератор сигналов управления длиной корреляции и контроллер длины корреляции. Генератор сигналов управления длиной корреляции содержит счетчик COUNTER-512, принимающий тактовые сигналы clk_12288, clr_12288 соответственно (4a) и (4c) на фиг. 4, для подсчета 512 чисел в течение одного периода, инвертор для инвертирования выходного сигнала счетчика COUNTER-512 и формирования инверсного счетчика сигнала и логический элемент NAND "f", получающий инверсный счетный сигнал на одном входном выводе и тактовый сигнал (фиг. 4n) на его другом входном выводе для формирования сигнала управления длиной корреляции. Контроллер длины корреляции содержит регистр REG-11, получающий сигнал управления длиной корреляции и тактовые сигналы clk_8 и clr для подачи выходного сигнала накопителя 410 на сумматор 430. Сумматор 430 суммирует (или накапливает) выходной сигнал накопителя 410 и подает суммированное значение в схему 440 возведения в квадрат. Схема 440 возведения в квадрат возводит в квадрат выходной сигнал сумматора 430 для получения значения корреляции.

Из изложенного выше ясно, что длина корреляции может легко изменяться в соответствии с конкретными условиями использования посредством простой замены числа бит "N" генератора сигналов управления длиной корреляции (то есть, отсчета N счетчика COUNTER-512) комплексного коррелятора.

Изобретение обеспечивает управляемое изменение длиной корреляции для получения требуемой длины корреляции, что позволяет решить проблемы известных из предшествующего уровня техники устройств, в которых для изменения длины корреляции следовало изменять или дополнять схему, либо в случае использования специализированной интегральной схемы заменять такую интегральную схему на новую.

Изобретение относится к средствам обработки сигналов и может быть использовано в системах связи. Переменный коррелятор выполняет вычисления при управляемом изменении длины корреляции. Последовательные входные данные, смешанные с опорными, накапливаются согласно числу, соответствующему предварительно установленной длине корреляции, причем длина корреляции может изменяться при вычислениях. 2 с.п. ф-лы, 4 ил.

| Проектирование радиолокационных приемных устройств./Под ред | |||

| Соколова М.А | |||

| - М.: Высшая школа, 1984, с.40 - 41, 60 - 61, рис.1.32, 1.33, 1.34, 2.8. |

Авторы

Даты

1998-05-20—Публикация

1996-12-27—Подача