Группа изобретений относится к электронике и может быть использована в субмикронных МОП интегральных схемах (ИС) обработки сигналов.

Современные субмикронные КМОП технологии ИС характеризуются пониженными пороговыми напряжениями и повышенным уровнем утечек сток-исток. Проблему утечек усугубляет разброс пороговых напряжений МОП транзисторов (Vth) из-за девиации параметров технологического процесса при изготовлении ИС, а также дрейфа пороговых напряжений в процессе эксплуатации ИС при изменениях температуры и воздействиях, приводящих к генерации заряда в окисле. Повышенные значения пороговых напряжений приводят к снижению быстродействия схем, а пониженные - к повышеным утечкам сток-исток. Для аналоговых ИС разброс пороговых напряжений и их изменение в процессе эксплуатации может приводить к деградации точностных параметров и нарушениям функционирования ИС еще задолго до проявления проблемы токов утечки, поэтому одним из важнейших направлений повышения надежности аналоговых схем является стабилизация пороговых напряжений, то есть компенсация технологического разброса и дрейфа пороговых напряжений при эксплуатации ИС.

Цель изобретения - уменьшение тока утечки сток-исток субмикронных МОП транзисторов, а также стабилизация пороговых напряжений в МОП ИС.

Известно, что обратное смещение подложки относительно истоков повышает пороговое напряжение МОП транзисторов и, тем самым, уменьшает ток утечки сток-исток, см. например, С. Зи «Физика полупроводниковых приборов», Москва, изд-во «Мир», 1984 г., т.2, стр.18-19. Также обратное смещение подложки уменьшает ток утечки сток-исток МОП транзисторов в подпороговой области, резко уменьшая так называемое характерное напряжение затвор-исток S, требующееся для уменьшения на порядок тока утечки сток-исток в подпороговой области (С. Зи «Физика полупроводниковых приборов», Москва, изд-во «Мир», 1984 г., т.2, стр.23).

Известны схемы, формирующие обратное смещение подложки для уменьшения тока утечки МОП транзисторов в ИС, например, схемы по патентам США US 4401897, US 4581546, US 5909140, US 7504876B1, US 7746160B1 и заявке US 20080191791, A1.

Основой всех этих схем является устройство накачки заряда, генерирующее пульсирующее напряжение, либо выше напряжения источника питания для n-подложки p-канальных МОП транзисторов, либо ниже напряжения общей шины (земли) для p-подложки n-канальных МОП транзисторов. Это пульсирующее напряжение подается на подложку, формируя ее обратное смещение относительно истоков МОП транзисторов. Обычно это смещение используетя в пассивном (stby) режиме ИС для снижения тока потребления за счет утечек транзисторов, при этом пульсирующий характер напряжения смещения подложки некритичен. Однако пульсирующее напряжение смещения подложки в активном режиме ИС может вызывать проблемы, особенно в аналоговых ИС, критичных к помехам от пульсирующего напряжения подложки.

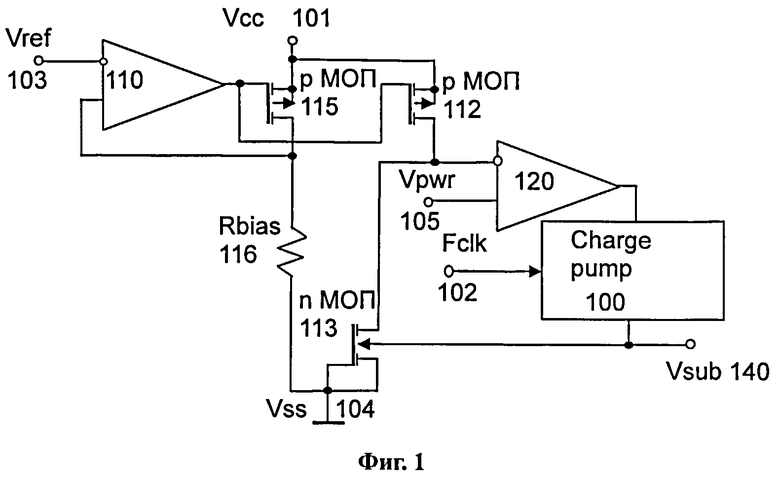

Наиболее близким к заявляемому является источник обратного смещения подложки по патенту США «Substrate Bias Feedback Scheme to Reduce Chip Leakage Power» №8085085B1, M.Кл. G05F 1/10, пр. 28.06.2010 г., опубл. 27.12.2011 г., представленный на Фиг.1. Известный источник обратного смещения подложки включает устройство накачки заряда (charge pump) 100, формирующее пульсирующее напряжение смещения подложки МОП транзисторов Vsub 140, и два операционных усилителя (ОУ) 110 и 120. Первый ОУ 110 совместно с транзистором 115 и резистором Rbias 116 формирует опорный ток, величина которого определяется опорным напряжением Vref 103 и резистором Rbias 116. Ток транзистора 112, пропорциональный опорному току, сравнивается с током утечки сток-исток эталонного n-канального МОП транзистора 113, с закороченным на исток и общий вывод 104 затвором. Если ток утечки тразистора 113 больше тока транзистора 112, то напряжение на инвертирующем входе второго ОУ 120 уменьшается и становится ниже напряжения Vpwr 105, заданного на неинвертирующем входе. Выходное напряжение ОУ 120 возрастает, обуславливая увеличение абсолютной величины отрицательного выходного напряжения Vsub 140 устройства накачки. Таким образом, ОУ 120 регулирует выходное напряжение устройства накачки заряда, обеспечивая усредненный ток утечки эталонного МОП тразистора на уровне тока, задаваемого транзистором 112.

Описанный источник обратного смещения может быть использован как в пассивном, так и в активном режиме, уменьшая влияние тока утечки на параметры ИС при вариациях техпроцесса, температуры и напряжения питания (в литературе и далее эти условия: process - Р, voltage - V, temperature - Т обозначаются «PVT»). Однако этот источник имеет уже упомянутый недостаток, связанный с пульсирующим характером напряжения обратного смещения, формируемого устройством накачки заряда, что делает его неприемлимым в аналоговых схемах. Недостатком этого источника обратного смещения является также невозможность адекватной компенсации технологического разброса порогового напряжения и его дрейфа, вызванного условиями эксплуатации. Последнее обусловлено тем, что токовый компаратор, активизирующий накачку заряда, является пороговым устройством, настроенным на одно конкретное значение тока утечки МОП транзистора-датчика с закороченным на исток затвором, и не может адекватно реагировать на изменение тока утечки в подпороговой области с экспоненциальной зависимостью от напряжения затвор-исток. Третий недостаток обусловлен наличием жестких ограничений максимального напряжения сток-подложка МОП транзисторов. Очевидно, что максимальное значение пульсирующего напряжения обратного смещения подложки не должно превышать разности максимального напряжения сток-подложка и максимального напряжения питания. При этом минимального значения пульсирующего напряжения обратного смещения может оказаться недостаточным для достижения поставленной цели - устранения утечек с учетом зависимости эффективности накачки заряда от PVT. Кроме того, для предотвращения возможного отказа ИС из-за превышения максимального напряжения сток-подложка МОП транзисторов с обратным смещением на подложке, в известном источнике обратного смещения используется дополнительное устройство ограничения напряжения обратного смещения, что ведет к усложнению и повышению собственного тока потребления источника (на Фиг.1 устройство ограничения уровня, с целью упрощения, не показано).

Целью изобретения является уменьшение тока утечки сток-исток и стабилизация пороговых напряжений МОП транзисторов в МОП ИС.

Поставленные цели достигаются тем, что в способе уменьшения утечки сток-исток и стабилизации пороговых напряжений МОП транзисторов в ИС, включающем формирование устройством накачки заряда пульсирующего напряжения и формирование напряжения обратного смещения подложки МОП транзисторов, пульсирующее напряжение выхода устройства накачки заряда с абсолютной величиной, большей абсолютной величины напряжения обратного смещения подложки МОП транзисторов преобразуют в стабилизированное напряжение обратного смещения подложки МОП транзисторов, увеличивающееся с уменьшением порогового напряжения МОП транзистора-датчика.

Поставленные цели достигаются также тем, что в схеме уменьшения утечки сток-исток и стабилизации пороговых напряжений МОП транзисторов в ИС, включающей источник обратного смещения подложки относительно истоков, содержащий устройство накачки заряда и операционный усилитель, устройство накачки заряда формирует пульсирующее напряжение с абсолютной величиной большей абсолютной величины напряжения обратного смещения подложки, неинвертирующий вход операционного усилителя подключен к выходу датчика порогового напряжения МОП транзисторов, инвертирующий вход к выходу резистивного делителя, включенного между выводами опорного напряжения и выхода усилителя, а выход усилителя образует выход источника напряжения обратного смещения и подключен к подложке МОП транзисторов, причем выходной каскад операционного усилителя запитан от выхода устройства накачки заряда.

В частном случае в схеме уменьшения утечки сток-исток и стабилизации пороговых напряжений n-канальных МОП транзисторов поставленные цели достигаются тем, что устройство накачки заряда формирует пульсирующее отрицательное напряжение с абсолютной величиной, большей абсолютной величины напряжения обратного смещения подложки, неинвертирующий вход операционного усилителя подключен к выходу датчика порогового напряжения n-канальных МОП транзисторов, инвертирующий вход к выходу резистивного делителя, включенного между выводами опорного напряжения и выхода усилителя, а выход усилителя образует выход источника напряжения отрицательного смещения и подключен к p-подложке n-канальных МОП транзисторов, причем исток и подложка n-канального МОП транзистора выходного каскада операционного усилителя подключены к выходу устройства накачки заряда.

В частном случае в схеме уменьшения утечки сток-исток и стабилизации пороговых напряжений p-канальных МОП транзисторов поставленные цели достигаются тем, что устройство накачки заряда формирует пульсирующее напряжение с величиной большей суммы напряжений питания и положительного смещения n-подложки, неинвертирующий вход операционного усилителя подключен к выходу датчика порогового напряжения p-канальных МОП транзисторов, инвертирующий вход к выходу резистивного делителя, включенного между выводами земли и выхода усилителя, а выход усилителя образует выход источника напряжения положительного смещения и подключен к n-подложке p-канальных МОП транзисторов, причем исток и подложка p-канального МОП транзистора выходного каскада операционного усилителя подключены к выходу устройства накачки заряда.

В частном случае в схеме уменьшения утечки сток-исток и стабилизации пороговых напряжений n-канальных МОП транзисторов поставленные цели достигаются тем, что датчик порогового напряжения n-канальных МОП транзисторов включает токозадающий резистор, включенный между выводом опорного напряжения и стоком n-канального МОП транзистора, исток которого соединен с его подложкой и выводом земли, а затвор, соединенный со стоком, образует выход датчика, причем соотношение тока, задаваемого токозадающим резистором, и крутизны МОП транзистора-датчика определяет крутизну зависимости обратного смещения подложки от порогового напряжения.

В частном случае в схеме уменьшения утечки сток-исток и стабилизации пороговых напряжений p-канальных МОП транзисторов поставленные цели достигаются тем, что датчик порогового напряжения р-канальных МОП транзисторов включает токозадающий резистор, включенный между выводом земли и стоком p-канального МОП транзистора, исток, которого соединен с его подложкой и выводом питания, а затвор, соединенный со стоком, образует выход датчика, причем соотношение тока, задаваемого токозадающим резистором, и крутизны МОП транзистора-датчика определяет крутизну зависимости обратного смещения подложки от порогового напряжения.

Поставленная цель уменьшения тока утечки сток-исток МОП транзисторов в заявляемых способе и схемах достигается за счет обратного смещения подложки МОП транзисторов относительно их истоков. Эффект уменьшения тока утечки достигается, как за счет повышения порогового напряжения пропорционально квадратному корню из напряжения обратного смещения (см., например, С. Зи «Физика полупроводниковых приборов», Москва, изд-во «Мир», 1984 г., т.2, стр.18-19), так и за счет уменьшения характерного напряжения затвор-исток S, требующегося для уменьшения на порядок тока утечки сток-исток в подпороговой области (С. Зи «Физика полупроводниковых приборов», Москва, изд-во «Мир», 1984 г., т.2, стр.23). Известно, что обратное смещение подложки МОП транзисторов повышает пороговое напряжение МОП транзисторов тем больше, чем толще затворный диэлектрик и выше концентрация примеси в подложке, поэтому обратное смещение подложки еще более эффективно устраняет утечки по паразитным каналам под толстым диэлектриком, которые могут возникнуть, например, в результате воздействия эксплуатационных факторов, генерирующих заряд в окисле. В отличие от известных, в заявляемых способе и схеме напряжение обратного смещения подложки не импульсное, а стабилизированное, что дает возможность их использования в аналоговых ИС, без ухудшения точностных параметров.

Поставленная цель стабилизации пороговых напряжений достигается тем, что в заявляемых схемах источник обратного смещения подложки формирует напряжение обратного смещения, увеличивающееся с уменьшением порогового напряжения МОП транзистора с закороченным на подложку истоком, выделяемого МОП транзистором-датчиком. При этом пороговое напряжение МОП транзистора-датчика соответствует технологическому углу процесса изготовления (полученным в процессе изготовления значениям толщины затворного диэлектрика, концентрации примеси в подложке и т.д.) и зависит от текущих условий эксплуатации и внешних воздействий (например, уменьшается с ростом температуры, изменяется при изменении заряда в окисле). Таким образом, если по каким-либо технологическим или эксплуатационным причинам, эффективное пороговое напряжение МОП транзистора-датчика уменьшилось или увеличилось относительно заданного значения, напряжение обратного смещения соответственно увеличится или уменьшится, тем самым уменьшая величину изменения эффективного порогового напряжения МОП транзисторов с обратным смещением на их подложке.

Сущность изобретения поясняется чертежами.

На Фиг.1 представлена схема уменьшения тока утечки сток-исток МОП транзисторов в ИС с известным по прототипу источником обратного смещения подложки МОП транзисторов.

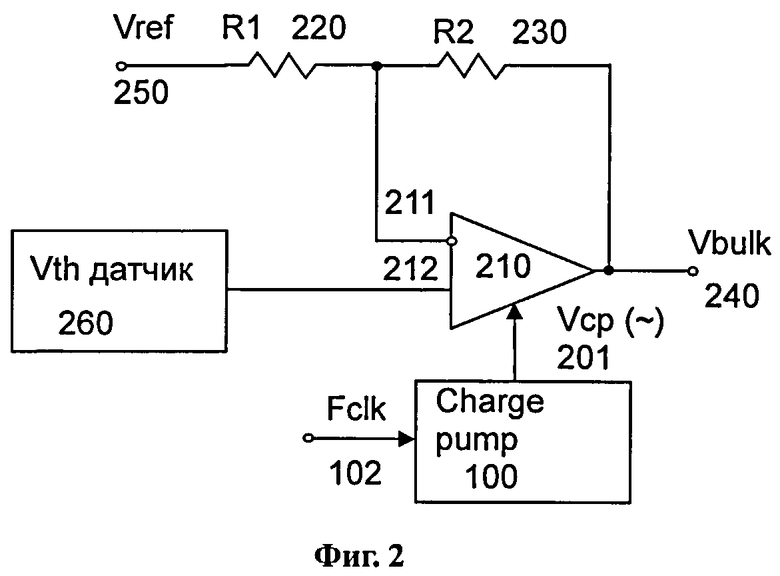

На Фиг.2 представлена схема уменьшения тока утечки сток-исток и стабилизации пороговых напряжений МОП транзисторов транзисторов в ИС с заявляемым источником обратного смещения подложки МОП транзисторов по пп.1 и 2 Формулы.

На Фиг.3 представлена схема уменьшения тока утечки сток-исток и стабилизации пороговых напряжений n-канальных МОП транзисторов транзисторов в ИС с заявляемым источником обратного смещения p-подложки и датчиком порогового напряжения n-канальных МОП транзисторов по пп.3 и 4 Формулы.

На Фиг.4 представлена схема уменьшения тока утечки сток-исток и стабилизации пороговых напряжений p-канальных МОП транзисторов транзисторов в ИС с заявляемым источником обратного смещения n-подложки и датчиком порогового напряжения p-канальных МОП транзисторов по пп.5 и 6 Формулы.

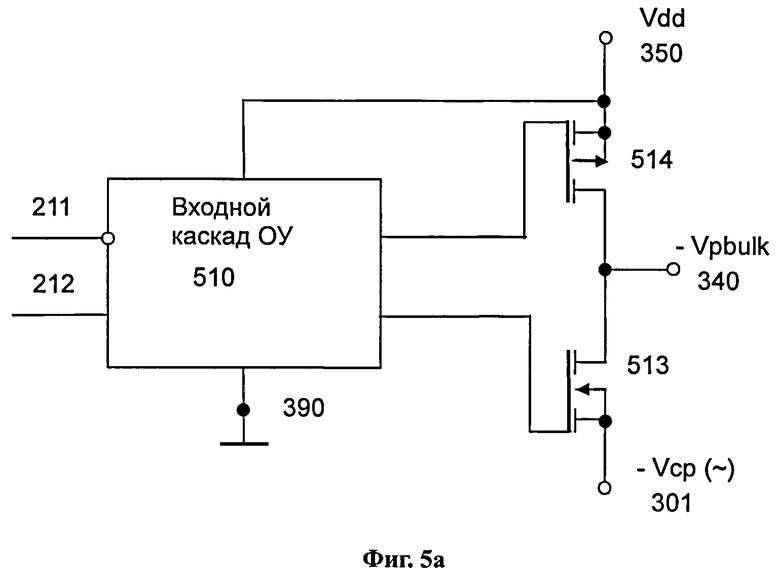

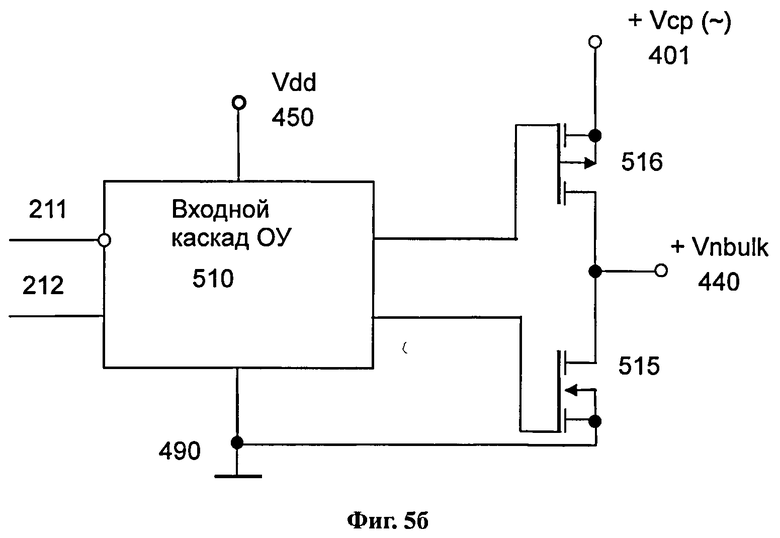

На Фиг.5 транзисторов в ИС представлены схемы подключения операционного усилителя в заявляемых источниках обратного смещения подложки по пп.3 и 5 Формулы.

Ниже, на примере чертежей, приведено описание устройства и работы заявляемых схем источников обратного смещения подложки МОП транзисторов.

На Фиг.2 представлена схема уменьшения тока утечки сток-исток и стабилизации пороговых напряжений МОП транзисторов с заявляемым источником обратного смещения подложки МОП транзисторов относительно истоков по пп.1 и 2 Формулы. Схема источника обратного смещения включает устройство накачки заряда 100, формирущее на его выходе 201 пульсирующее с частотой входной тактовой частоты 102 (Fclk) напряжение с абсолютной величиной, большей абсолютной величины требуемого напряжения обратного смещения подложки и подаваемое на выходной каскад операционного усилителя 210. Неинвертирующий вход 212 усилителя 210 подключен к выходу датчика порогового напряжения МОП транзисторов 260, инвертирующий вход 211 к выходу резистивного делителя из резисторов 220 (R1) и 230 (R2), включенного между выводами опорного напряжения 250 и выхода усилителя 240. Выход 240 усилителя является также выходом источника напряжения обратного смещения и подключен к подложке МОП транзисторов, ток утечки которых требуется уменьшать.

На Фиг.3 представлена схема уменьшения тока утечки сток-исток и стабилизации пороговых напряжений n-канальных МОП транзисторов с заявляемыми по пп.3 и 4 Формулы источником обратного смещения p-подложки и датчиком порогового напряжения n-канальных МОП транзисторов. Приведенная схема источника обратного смещения включает устройство накачки заряда 100, формирущее на его выходе 301 пульсирующее с частотой входной тактовой частоты 102 (Fclk) отрицательное напряжение с абсолютной величиной, большей абсолютной величины требуемого напряжения обратного смещения p-подложки и подаваемое на выходной каскад операционного усилителя 310. Неинвертирующий вход 212 усилителя 310 подключен к выходу датчика порогового напряжения n-канальных МОП транзисторов 360, инвертирующий вход 211 к выходу резистивного делителя из резисторов 220 (R1) и 230 (R2), включенного между выводами опорного напряжения 350 и выхода усилителя 340. Выход 340 усилителя является также выходом источника отрицательного напряжения обратного смещения (- Vpbulk) и подключен к p-подложке n-канальных МОП транзисторов, ток утечки которых требуется уменьшать. Датчик порогового напряжения n-канальных МОП транзисторов 360 в соответствии с п.3 Формулы включает токозадающий резистор 370, включенный между выводом опорного напряжения 350 и стоком n-канального МОП транзистора 380, исток, которого соединен с его подложкой и выводом земли 390, а затвор, соединенный со стоком, образует выход датчика, причем соотношение тока, задаваемого токозадающим резистором, и крутизны МОП транзистора-датчика 380 определяет крутизну зависимости обратного смещения подложки от порогового напряжения.

На Фиг.4 представлена схема уменьшения тока утечки сток-исток и стабилизации пороговых напряжений p-канальных МОП транзисторов с заявляемыми по пп.5 и 6 Формулы источником обратного смещения n-подложки и датчиком порогового напряжения p-канальных МОП транзисторов. Приведенная схема источника обратного смещения включает устройство накачки заряда 100, формирущее на его выходе 401 пульсирующее с частотой входной тактовой частоты 102 (Fclk) положительное напряжение, большее суммы напряжения питания и требуемого напряжения положительного смещения n-подложки и подаваемое на выходной каскад операционного усилителя 410. Неинвертирующий вход 212 усилителя 410 подключен к выходу датчика порогового напряжения p-канальных МОП транзисторов 460, инвертирующий вход 211 к выходу резистивного делителя из резисторов 220 (R1) и 230 (R2), включенного между выводами земли 490 и выхода усилителя 440. Выход 440 усилителя является также выходом источника напряжения обратного смещения (Vnbulk) и подключен к n-подложке p-канальных МОП транзисторов, ток утечки которых требуется уменьшать. Датчик порогового напряжения p-канальных МОП транзисторов 460 в соответствии с п.5 Формулы включает токозадающий резистор 470, включенный между выводом земли 490 и стоком p-канального МОП транзистора 480, исток которого соединен с его подложкой и выводом питания 450, а затвор, соединенный со стоком, образует выход датчика, причем соотношение тока, задаваемого токозадающим резистором, и крутизны МОП транзистора-датчика 480 определяет крутизну зависимости обратного смещения подложки от порогового напряжения.

На Фиг.5 представлены схемы подключения операционного усилителя в заявляемых источниках обратного смещения подложки по пп.3 и 5 Формулы. На Фиг.5а представлена схема подключения операционного усилителя в заявляемом по п.3 Формулы источнике обратного (отрицательного) смещения p-подложки n-канальных МОП транзисторов. Входной каскад 510 усилителя с неинвертирующим 212 и инвертирующим 211 входами подключен к выводам напряжения питания 350 и земли 390. Выходной каскад усилителя состоит из управляемой выходами входного каскада комплементарной пары n- и p-канальных МОП транзисторов 5 13 и 5 14, объединенные стоки которых образуют выход усилителя 340, подключаемый к смещаемой p-подложке n-канальных МОП транзисторов. Исток и подложка выходного p-канального транзистора подключены к выводу напряжения питания 350, а исток и подложка выходного n-канального транзистора подключены к выходу устройства накачки заряда 301 с пульсирующим отрицательным напряжением, абсолютная величина которого больше абсолютной величины требуемого смещения p-подложки. При этом на выходе усилителя формируется стабилизированное отрицательное напряжение (-Vpbulk) обратного смещения p-подложки требуемой величины и с существенно уменьшенной величиной пульсаций.

На Фиг.5б представлена схема подключения операционного усилителя в заявляемом по п.5 Формулы источнике обратного (положительного) смещения n-подложки p-канальных МОП транзисторов. Входной каскад 510 усилителя с неинвертирующим 212 и инвертирующим 211 входами подключен к выводам напряжения питания 450 и земли 490. Выходной каскад усилителя состоит из управляемой выходами входного каскада комплементарной пары n- и p-канальных МОП транзисторов 515 и 516, объединенные стоки которых образуют выход усилителя 440, подключаемый к смещаемой n-подложке p-канальных МОП транзисторов. Исток и подложка выходного n-канального транзистора подключены к выводу земли 490, а исток и подложка выходного p-канального транзистора подключены к выходу устройства накачки заряда 401 с пульсирующим положительным напряжением большим суммы напряжения питания и требуемого напряжения положительного смещения n-подложки. При этом на выходе усилителя формируется стабилизированное положительное напряжение (Vnbulk) обратного смещения n-подложки требуемой величины и с существенно уменьшенной величиной пульсаций.

Рассмотрим работу заявляемой по пп.3 и 4 Формулы схемы уменьшения тока утечки сток-исток n-канальных МОП транзисторов с источником обратного смещения p-подложки и датчиком порогового напряжения n-канальных МОП транзисторов, приведенной на Фиг.3. Устройство накачки заряда 100 формирует на его выходе 301 пульсирующее с частотой входной тактовой частоты 102 (Fclk) отрицательное напряжение с абсолютной величиной, большей абсолютной величины требуемого напряжения обратного смещения p-подложки. Пульсирующий характер и большое по абсолютной величине выходное напряжение устройства накачки заряда не позволяют подавать его непосредственно на подложку n-канальных МОП транзисторов в аналоговых ИС из-за его влияния на параметры через паразитные емкости сток-подложка, канал-подложка и затвор-подложка, а также из-за превышения допустимого напряжения сток-подложка n-канальных МОП транзисторов. Отметим, что величина напряжения затвор-подложка некритична, поскольку при напряжении на затворе n-канального МОП транзистора выше порогового, затвор экранируется от подложки областью канала и обедненным слоем p-n перехода между n-каналом и p-подложкой. Операционный усилитель 310 в инвертирующем включении выполняет функцию формирования на своем выходе 340 стабилизированного отрицательного напряжения обратного смещения p-подложки n-канальных МОП транзисторов, с абсолютной величиной, увеличивающейся с уменьшением порогового напряжения n-канального МОП транзистора-датчика с истоком, закороченным с подложкой. Для выполнения этой функции неинвертирующий вход 212 усилителя 210 подключен к выходу датчика порогового напряжения n-канальных МОП транзисторов 360, инвертирующий вход 211 к выходу резистивного делителя из резисторов 220 (R1) и 230 (R2), включенного между выводами опорного напряжения 350 и выхода усилителя 340. Выход 340 усилителя является выходом источника напряжения обратного смещения и подключен к p-подложке n-канальных МОП транзисторов, ток утечки которых требуется уменьшать.

Датчик порогового напряжения n-канальных МОП транзисторов 360 в соответствии с п.3 формирует на своем выходе напряжение Vgsn, равное напряжению затвор-исток транзистора 380 при токе, определяемому по формулам (1) и (2)

,

,

где Idsn - ток стока МОП транзистора-датчика, задаваемый сопротивлением токозадающего резистора Rt, от источника опорного напряжения Vref;

Kn - крутизна n-канального МОП транзистора-датчика;

Vthn - пороговое напряжение n-канального МОП транзистора-датчика.

Из (1) видно, что выходное напряжение датчика Vgsn в общем случае зависит от порогового напряжения Vthn и крутизны Kn МОП транзистора датчика. Однако уменьшением тока датчика Idsn, задаваемого сопротивлением токозадающего резистора Rt и увеличением крутизны Kn можно практически исключить влияние крутизны Kn, на выходное напряжение датчика, тогда при Idsn много меньше Kn можно считать, что Vthn равно Vgsn.

Выбором малой величины отношения Idsn/Kn можно ввести МОП транзистор-датчика в подпороговую область с экспоненциальной зависимостью тока стока от напряжения затвор-исток, при этом выходное напряжение датчика Vgsn меньше порогового напряжения и его зависимость от величины тока существенно слабее. В то же время в подпороговой области малые изменения порогового напряжения приводят к большим изменениям выходного напряжения датчика и, соответственно, к более сильной зависимости величины обратного смещения от порогового напряжения.

Уравнение состояния инвертирующего усилителя 340 можно записать в виде (3)

где Vin - напряжение на инвертирующем входе ОУ, приближенно равное Vgsn;

R1 и R2 - сопротивления резисторов делителя;

Vbulk - напряжение выхода ОУ, используемое для обратного смещения p-подложки.

Пренебрегая смещением нуля усилителя выражения (3) и учитывая, что Vgsn равно Vthn, можно записать в виде (4):

Из выражения (4), зная величины Vthn, Vref и требуемое значение Vbulk, можно определить требуемую величину отношения сопротивлений резисторов делителя R2/R1.

Аналогичным образом работает и описывается симметричная схема источника обратного смещения n-подложки p-МОП транзисторов по пп.5, 6 Формулы, приведенная на Фиг.4.

Для проверки реализуемости и оценки параметров разработана схема источника отрицательного обратного смещения p-подложки 5 В n-канальных МОП транзисторов по 180 нм КМОП технологии для использования в ИС прецизионных цифроаналоговых и аналого-цифровых преобразователей. Схема источника смещения включает блок накачки заряда на переключаемых конденсаторах, работающий с входной тактовой частотой Fclk=2МГц, операционный усилитель с малым энергопотреблением, поликремниевый резистивный делитель и датчик порогового напряжения на МОП тразисторе с шириной и длиной канала 8 мкм и 0,5 мкм соответственно и закороченным на подложку истоком. Датчик порогового напряжения работает при типовом токе 3,6 мкА, задаваемым поликремниевым резистором. Вся схема источника выполнена на 5B МОП транзисторах и рассчитана на работу в диапазоне напряжений питания от 3В до 5,5В. При этом схема источника разработана с учетом гаранитии отсутствия превышения допустимых рабочих напряжений сток-подложка, исток-подложка, затвор-исток и затвор-сток МОП транзисторов 5,5В, заданных предприятием-изготовителем.

Результаты моделирования разработанной схемы источника отрицательного обратного смещения p-подложки 5 В n-канальных МОП транзисторов в диапазоне напряжений питания представлены в Таблице 1.

В столбцах 1 и 2 приведены условия моделирования: технологический корнер (wp-worst power, typ-типовой процесс, ws-worst speed) и температура. Следует отметить, что напряжение питания схемы в диапазоне 3В-5,5В практически не влияет на результаты. В столбцах 3, 4 и 5, 6 приведены средние напряжения на выходе устройства накачки заряда и выходе источника (выходе усилителя) и амплитуды их пульсаций. В столбцах 7 и 8 приведены пороговые напряжения n-канального МОП транзистора-датчика с закороченным на подложку истоком (Vbulk=0) и такого же МОП транзистора с поданным на подложку смещением (Vbulk<0). В столбцах 9 и 10 приведены токи утечки сток-исток n-канального МОП транзистора с закороченным на подложку истоком (Vbulk=0) и такого же МОП транзистора с поданным на подложку смещением (Vbulk<0).

Как видно из данных таблицы, заявляемая схема источника обратного смещения p-подложки n-канальных МОП транзисторов уменьшает максимальный ток утечки сток-исток 5 В МОП транзисторов с минимальной длиной канала 0,5 мкм в 37 раз с 48пА до 1,3пА на микрон ширины канала, уменьшает разброс эффективного порогового напряжения более, чем в 2 раза с 0,31 В до 0,15 В, снижает амплитуду пульсаций на выходе источника в 76 раз с 56 мВ до 0,74 мВ. Отметим, что максимальное по абсолютной величине обратное смещение 588 мВ получено в условиях (wp, 125°С) с минимальным пороговым напряжением 0,74 В. В этих же условиях абсолютная величина напряжения на выходе устройства накачки заряда существенно больше: 748 мВ, что обеспечивает возможность дальнейшего увеличения обратного смещения на p-подложке в случае уменьшения порогового напряжения n-канального МОП транзистора-датчика при эксплуатации, и тем самым, частичной компенсации этого уменьшения.

Таким образом, заявляемые способ и схема уменьшения утечек и стабилизация пороговых напряжений МОП транзисторов обладают новизной, могут быть реализованы и позволяют существенно уменьшить ток утечки МОП транзисторов, а также снизить разброс и дрейф пороговых напряжений при эксплуатации ИС.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНЫЙ N-РАЗРЯДНЫЙ ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ (ЦАП) (ВАРИАНТЫ) | 1995 |

|

RU2113055C1 |

| ПРЕЦИЗИОННЫЙ КМОП УСИЛИТЕЛЬ | 2005 |

|

RU2310270C1 |

| КМОП-усилитель с чоппер-стабилизацией и способ калибровки | 2022 |

|

RU2809617C1 |

| КМОП усилитель с чоппер стабилизацией и способ калибровки | 2019 |

|

RU2724989C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ КАЛИБРОВКИ СМЕЩЕНИЯ НУЛЯ | 2013 |

|

RU2520427C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2010 |

|

RU2442279C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КМОП КОМПАРАТОР НАПРЯЖЕНИЯ | 1992 |

|

RU2019913C1 |

| Прецизионный преобразователь напряжения в частоту | 2022 |

|

RU2819791C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2013 |

|

RU2520421C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ИС БАЗОВЫХ МАТРИЧНЫХ КРИСТАЛЛОВ (БМК) | 1996 |

|

RU2124252C1 |

Группа изобретений относится к электронике и может быть использована в микроэлектронных системах обработки сигналов на субмикронных МОП транзисторах. Техническим результатом является уменьшение тока утечки и стабилизация пороговых напряжений субмикронных МОП транзисторов с низкими пороговыми напряжениями в МОП ИС. Устройство включает источник обратного смещения подложки МОП транзисторов относительно их истоков, формирующий стабилизированное напряжение обратного смещения, увеличивающееся с уменьшением порогового напряжения МОП транзистора-датчика с закороченным на подложку истоком. Устройство включает устройство накачки заряда, формирующее пульсирующее напряжение с абсолютной величиной, большей абсолютной величины напряжения обратного смещения подложки, датчик порогового напряжения МОП транзисторов, операционный усилитель, резистивный делитель. 2 н. и 4 з.п. ф-лы, 6 ил., 1 табл.

1. Способ уменьшения утечки сток-исток и стабилизации пороговых напряжений МОП транзисторов в ИС, включающий формирование устройством накачки заряда пульсирующего напряжения и формирование напряжения обратного смещения подложки МОП транзисторов, отличающийся тем, что пульсирующее напряжение с абсолютной величиной, большей абсолютной величины напряжения обратного смещения подложки МОП транзисторов преобразуют в стабилизированное напряжение обратного смещения подложки МОП транзисторов, увеличивающееся с уменьшением порогового напряжения МОП транзистора-датчика.

2. Схема уменьшения утечки сток-исток и стабилизации пороговых напряжений МОП транзисторов в ИС, включающая источник обратного смещения подложки относительно истоков, содержащий устройство накачки заряда и операционный усилитель, и отличающаяся тем, что устройство накачки заряда формирует пульсирующее напряжение с абсолютной величиной, большей абсолютной величины напряжения обратного смещения подложки, неинвертирующий вход операционного усилителя подключен к выходу датчика порогового напряжения МОП транзисторов, инвертирующий вход к выходу резистивного делителя, включенного между выводами опорного напряжения и выхода усилителя, а выход усилителя образует выход источника напряжения обратного смещения и подключен к подложке МОП транзисторов, причем выходной каскад операционного усилителя запитан от выхода устройства накачки заряда.

3. Схема уменьшения утечки сток-исток и стабилизации пороговых напряжений n-канальных МОП транзисторов в ИС по п.2, включающая источник отрицательного смещения p-подложки относительно истоков, и отличающаяся тем, что устройство накачки заряда формирует пульсирующее отрицательное напряжение с абсолютной величиной большей абсолютной величины напряжения обратного смещения подложки, неинвертирующий вход операционного усилителя подключен к выходу датчика порогового напряжения n-канальных МОП транзисторов, инвертирующий вход к выходу резистивного делителя, включенного между выводами опорного напряжения и выхода усилителя, а выход усилителя образует выход источника напряжения отрицательного смещения и подключен к p-подложке n-канальных МОП транзисторов, причем исток и подложка n-канального МОП транзистора выходного каскада операционного усилителя подключены к выходу устройства накачки заряда.

4. Схема уменьшения утечки сток-исток и стабилизации пороговых напряжений n-канальных МОП транзисторов в ИС по п.3, отличающаяся тем, что датчик порогового напряжения n- канальных МОП транзисторов включает токозадающий резистор, включенный между выводом опорного напряжения и стоком n-канального МОП транзистора, исток которого соединен с его подложкой и выводом земли, а затвор, соединенный со стоком, образует выход датчика, причем соотношение тока, задаваемого токозадающим резистором, и крутизны МОП транзистора-датчика определяет крутизну зависимости обратного смещения подложки от порогового напряжения.

5. Схема уменьшения утечки сток-исток и стабилизации пороговых напряжений p-канальных МОП транзисторов в ИС по п.2, включающая источник положительного смещения n-подложки относительно истоков, и отличающаяся тем, что устройство накачки заряда формирует пульсирующее напряжение с величиной большей суммы напряжений питания и положительного смещения n-подложки, неинвертирующий вход операционного усилителя подключен к выходу датчика порогового напряжения p-канальных МОП транзисторов, инвертирующий вход к выходу резистивного делителя, включенного между выводами земли и выхода усилителя, а выход усилителя образует выход источника напряжения положительного смещения и подключен к n-подложке p-канальных МОП транзисторов, причем исток и подложка p-канального МОП транзистора выходного каскада операционного усилителя подключены к выходу устройства накачки заряда.

6. Схема уменьшения утечки сток-исток и стабилизации пороговых напряжений p-канальных МОП транзисторов в ИС по п.5, отличающаяся тем, что датчик порогового напряжения p-канальных МОП транзисторов включает токозадающий резистор, включенный между выводом земли и стоком p-канального МОП транзистора, исток которого соединен с его подложкой и выводом питания, а затвор, соединенный со стоком, образует выход датчика, причем соотношение тока, задаваемого токозадающим резистором, и крутизны МОП транзистора-датчика определяет крутизну зависимости обратного смещения подложки от порогового напряжения.

| US 8085085 B1, 27.12.2011 | |||

| US 2010097129 A1, 22.04.2010 | |||

| US 7863968 B1, 04.01.2011 | |||

| US 7649402 B1, 19.01.2010 | |||

| Стабилизатор напряжения питания часовой интегральной схемы | 1987 |

|

SU1453378A1 |

| Импульсный стабилизатор напряжения с защитой активно-индуктивной нагрузки | 1984 |

|

SU1288666A1 |

Авторы

Даты

2014-06-27—Публикация

2013-01-15—Подача