Изобретение относится к области измерительной техники и может быть использовано для измерения отклонений мгновенной частоты от номинального значения, для демодуляции ЧМ-сигналов в радиоизмерительных, радиоприемных устройствах, в цифровых телевизионных декодерах СЕКАМ, в радиолокации.

Известно значительное число устройств демодуляции дискретного ЧМ-сигнала, измерения частоты гармонических колебаний, подробный обзор которых приведен, например, в [1].

Среди них прежде всего следует указать электронно-счетные частотомеры, которые характеризуются недостаточной точностью измерений и не подходят для оценивания мгновенной частоты, так как требуют определенного времени для подсчета эталонных импульсов. С учетом этого более серьезного внимания заслуживают цифровые частотные детекторы, выполненные в виде системы ФАПЧ [2]. Однако данные устройства сложны для реализации, требуют определенного времени для вхождения в синхронизм, а также предполагают выполнение преобразования Гильберта над входным сигналом.

Более простыми в техническом исполнении являются частотные детекторы, хотя и основанные на гильбертовской фильтрации, но определяющие частоту расчетным путем. В их числе можно назвать устройства [3]. Однако существует довольно много приложений, для которых и такой уровень аппаратурных затрат остается чрезмерным.

В числе близких аналогов изобретения заслуживает внимания частотный детектор с вычислителем арккосинуса [4], содержащий два регистра, сумматор, сдвиговый регистр, ПЗУ, быстродействующий делитель. Устройство использует три последовательные выборки сигнала, например A1, A2 и A3, на основании которых определяется частота в соответствии с выражением ,

,

где

T - период дискретизации.

Можно показать, что данный частотный детектор является оптимальным с точки зрения минимума среднеквадратической ошибки измерения. Используемая в нем операция деления на выборку A2 уменьшает зависимость выходного сигнала от амплитуды несущей, что в определенной степени заменяет амплитудный ограничитель и особенно важно для демодуляции ЧМ-сигналов.

Вместе с тем, наличие операции деления в рассматриваемом устройстве является его недостатком, поскольку при A2 = 0 выполнить ее невозможно.

Наиболее близким по технической сущности к изобретению является цифровой частотный детектор [5], содержащий последовательно соединенные первый и второй регистры, а также постоянное запоминающее устройство, выход первого регистра, вход которого является входом цифрового частотного детектора, подключен к входу одной из переменных адресного входа постоянного запоминающего устройства, управляющие входы первого и второго регистров, являются тактовым входом цифрового частотного детектора.

Детектор-прототип, реализующий процедуру (1), подобно [4], оптимален с точки зрения обеспечения минимума среднеквадратической ошибки измерения и, в отличие от него, технически проще.

Однако возможности по упрощению схемного решения в нем использованы не до конца. Кроме того, отказы в работе прототипа возможны не только вследствие его технической сложности, но и при обнулении второго отсчета триады (A2 = 0).

Задача изобретения заключается в упрощении схемного решения цифрового частотного детектора и увеличении надежности его функционирования.

Достигаемый при этом технический результат состоит в повышении технологичности серийного изготовления цифрового частотного детектора, росте отказоустойчивости устройств, изготавливаемых на его основе.

Сущность изобретения заключается в том, что операция суммирования, усложняющая техническое решение цифрового частотного детектора, и вычисление арккосинуса, реализуются в рамках одного ПЗУ путем использования цифровых отсчетов сигнала непосредственно в качестве кода адреса. При этом вход цифрового частотного детектора и выход второго регистра подключены к входам других соответствующих переменных адресного входа постоянного запоминающего устройства. В роли последнего могут быть использованы ПЗУ с произвольным количеством строк и столбцов.

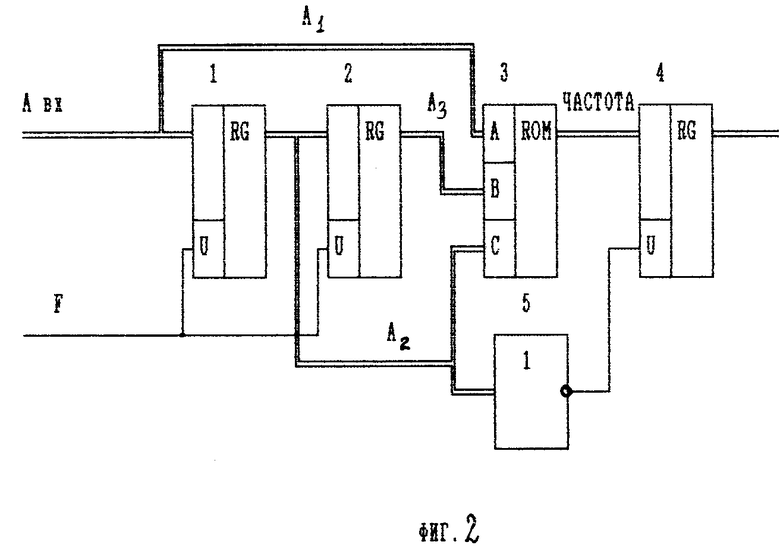

Такой вариант схемного решения существенно упрощает аппаратурную реализацию устройства, в подтверждение чему можно сослаться на фиг. 1, где приведена структурная схема заявляемого изобретения: 1 - первый регистр; 2 - второй регистр; 3 - ПЗУ; F - тактовый вход устройства.

При использовании 4-х, 5-разрядных АЦП описанный вариант детектора предполагает сравнительно небольшой объем ПЗУ, а именно: 211 ячеек и 214 соответственно (2 кБ и 16 кБ при 8-разрядном коде частоты).

В статическом состоянии вход цифрового частотного детектора является входом первого регистра 1 и подключен к входу одной из переменных адресного входа постоянного запоминающего устройства (ПЗУ) 3, выход первого регистра 1 подключен ко входу второго регистра 2, выходы первого регистра 1 и второго регистра 2 подключены к входам других соответствующих переменных адресного входа постоянного запоминающего устройства 3, выход которого является выходом цифрового частотного детектора, управляющие входы первого и второго регистров 1, 2 являются тактовым входом F цифрового частотного детектора.

Значения частоты в соответствии с выражением (1) предварительно рассчитывают для всего возможного набора комбинаций триад отсчетов АЦП A1, A2 и A3 и записывают в ПЗУ 3 по адресу, составными элементами которого являются указанные коды АЦП A1, A2 и A3. Такой прием позволяет в последующем отказаться от выполнения вычислительных операций непосредственно в момент измерения. Таким образом, в ПЗУ 3 в отличие от прототипа защита функция ,

,

где

T - период дискретизации;

A1, A2 и A3 - отсчеты АЦП, являющиеся фрагментами составного адреса ПЗУ 3.

Принцип работы данного варианта заявляемого устройства сводится к следующему.

Поступающие на вход цифрового частотного детектора цифровые коды АЦП по сигналам такта на управляющих входах первого и второго регистров 1, 2 последовательно записываются в регистры 1, 2 и далее по их выходам используются вместе с вновь поступившим отсчетом в качестве триады составных элементов адреса для выборки из ПЗУ 3 искомых значений частоты. С очередным импульсом такта происходит перезапись новой информации в регистры 1, 2, и код частоты по выходу ПЗУ 3 обновляется.

Предложенный вариант цифрового частотного детектора лишен основного недостатка, присущего прототипу и заключающегося в сложности аппаратурной реализации Имеющиеся в них отличия в техническом решении носят существенный характер, поскольку, следуя терминологии [6], представляют собой качественный скачок в направлении "свертывания" устройства, сводящийся к устранению в нем излишних узлов и связей.

Однако следует отметить, что указанное схемное решение не позволяет устранить второй недостаток прототипа, а именно возможность сбоев в его работе при нулевом значении второго отсчета триады A2. Одним из путей решения проблемы может быть использование при A2 = 0 в качестве выходного значения частоты результата, полученного на предыдущем шаге, когда A2 отличался от нуля.

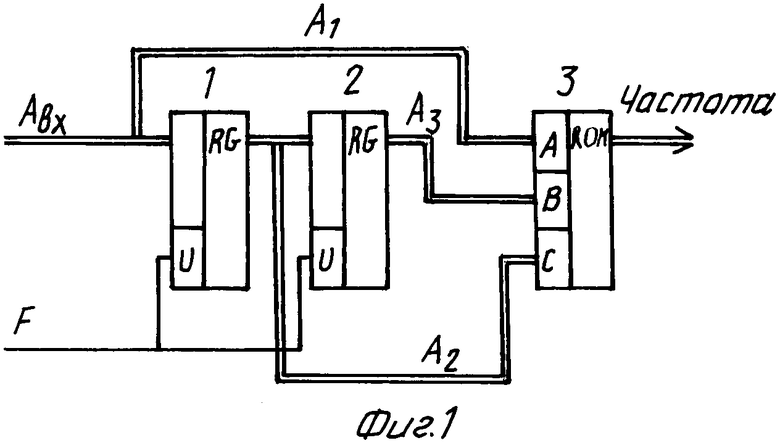

При этом в состав устройства, представленного на фиг. 1, следует дополнительно ввести регистр-защелку и формирователь сигнала управления, выполненного в виде элемента ИЛИ-НЕ, входы которого подключены к выходу первого регистра, а его выход - к управляющему входу регистра-защелки, вход регистра-защелки подключен к информационным выходам ПЗУ, выход регистра-защелки является выходом детектора.

На фиг. 2 приведен доработанный с учетом сказанного вариант цифрового частотного детектора, причем цифрами обозначены: 1 - первый регистр; 2 - второй регистр; 3 - ПЗУ; 4 - регистр-защелки; 5 - формирователь сигнала управления, выполненный в виде элемента ИЛИ-НЕ.

В статическом состоянии вариант цифрового частотного детектора (фиг. 2) отличается от основного варианта тем, что он также содержит регистр-защелку 4 и формирователь сигнала управления 5, выполненный в виде элемента ИЛИ-НЕ, входы которого подключены к выходу первого регистра 1, а его выход - к управляющему входу регистра-защелки 4, вход регистра-защелки 4 подключен к информационным выходам ПЗУ 3, выход регистра-защелки 4 является выходом детектора.

Принцип работы устройства в данном случае сводится к тому, что при A2 ≠ 0 на управляющем входе регистра-защелки 4 присутствует нулевой потенциал, позволяющий сигналу с выхода ПЗУ 3 беспрепятственно транслироваться на выход детектора. При обнулении отсчета A2 по выходу формирователя сигнала управления 5 должен установиться высокий потенциал, переводящий регистр-защелку 4 из режима трансляции входных данных в режим хранения предыдущего результата. Эту функцию и реализует элемент ИЛИ-НЕ 5.

Таким образом, запоминание результата предыдущих измерений на момент A2 = 0 позволяет устранить перерывы в поступлении информации от частотного детектора. Для многих приложений данный подход отказывается вполне приемлемым.

Что касается возможности осуществления заявляемого устройства, то она всецело определяется диапазоном измеряемых частот и допустимой ценой младшего разряда цифрового кода искомой частоты. Например, для частот дискретизации, меньших 10-15 МГц, вполне могут быть использованы регистры ТТЛ - серии и ТТЛШ (555, 1533), ПЗУ КР1656 PEI, КР1656 РЕ4, КР556 РТ7, КР556 РТ16, КР556 РТ20.

При более высоких частотах квантовая можно перейти к использованию микросхем ЭСЛ-серии (500, 1500). В случае необходимости в разрыв цепи прохождения сигнала такта на управляющие входы регистров следует включить элемент задержки.

Литература:

1. Хохлов Б.Н. Декодирующие устройства цветных телевизоров. - М.: Радио и связь, 1992, с. 88 - 101.

2. Хохлов Б.Н. Декодирующие устройства цветных телевизоров. - М.: Радио и связь, 1992, с. 95 - 96.

3. Хохлов Б.Н. Декодирующие устройства цветных телевизоров. - М.: Радио и связь, 1992, с. 90 - 94.

4. Хохлов Б.Н. Декодирующие устройства цветных телевизоров. - М.: Радио и связь, 1992, с. 89.

5. Патент США N 4737729, кл. H 03 D 1/00, 1988 - прототип.

6. Альтшуллер Г. С. Найти идею. Введение в теорию решения изобретательских задач. - Новосибирск, Наука, 1986, с. 91 - 92.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ ГАРМОНИЧЕСКИХ КОЛЕБАНИЙ | 1992 |

|

RU2111496C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| СПОСОБ ОБРАБОТКИ НЕКОГЕРЕНТНОГО ПАКЕТА РАДИОИМПУЛЬСОВ | 1992 |

|

RU2054691C1 |

| ЦИФРОВОЙ СПОСОБ ОПТИМАЛЬНОГО ПРИЕМА ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ ИМПУЛЬСОВ | 1992 |

|

RU2042956C1 |

| СПОСОБ КОРРЕКЦИИ АМПЛИТУДНО-ФАЗОВЫХ ХАРАКТЕРИСТИК ПЕРВИЧНЫХ КАНАЛОВ ПЛОСКОЙ ЦИФРОВОЙ АНТЕННОЙ РЕШЕТКИ | 1992 |

|

RU2103768C1 |

| Цифровое силоизмерительное устройство | 1987 |

|

SU1509604A1 |

| СПОСОБ ИЗМЕРЕНИЯ АМПЛИТУДНО-ЧАСТОТНЫХ ХАРАКТЕРИСТИК | 1992 |

|

RU2054684C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2012 |

|

RU2522039C1 |

| Быстродействующий селективный измеритель амплитуды ВЧ-сигнала | 1990 |

|

SU1780029A1 |

| Цифровой фазовый детектор | 2018 |

|

RU2723445C2 |

Использование: в измерительной технике для измерения мгновенной частоты, демодуляции ЧМ-сигналов, в цифровых телевизионных декодерах СЕКАМ. Сущность изобретения: все операции, усложняющие техническое решение частотного детектора, реализуются в одном ПЗУ путем использования триады цифровых отсчетов сигнала непосредственно в качестве кода адреса. При этом в цифровом частотном детекторе, содержащем последовательно соединенные первый и второй регистры, а также постоянное запоминающее устройство, причем выход первого регистра, чей вход является входом цифрового частотного детектора, подключен к входу одной из переменных адресного входа постоянного запоминающего устройства, а управляющие входы первого и второго регистров являются тактовым входом цифрового частотного детектора, вход цифрового частотного детектора и выход второго регистра подключены к входам других соответствующих переменных адресного входа постоянного запоминающего устройства. В качестве варианта предложен детектор, который для исключения сбоев при обнулении второй выборки в триаде отсчетов также содержит регистр-защелку и формирователь сигнала управления, выполненный в виде элемента ИЛИ-НЕ, входы которого подключены к выходу первого регистра, а его выход - к управляющему входу регистра-защелки, вход регистра-защелки подключен к информационным выходам ПЗУ, выход регистра-защелки является выходом детектора. 1 з.п.ф-лы, 2 ил.

| Хохлов Б.Н Декодирующие устройства цветных телевизоров | |||

| -М.: Радио и связ ь, 1992, с | |||

| Шланговое соединение | 0 |

|

SU88A1 |

| US, патент, 4737729, H 03 D 1/00, 1988. | |||

Авторы

Даты

1998-06-20—Публикация

1992-09-29—Подача