Изобретение относится к области передачи сообщений и может быть использовано в системах телеизмерения, телеуправления, связи и в вычислительной технике.

Известны аналоговые способы декодирования кодов и декодеры (устройства) для их осуществления, содержащие операции получения выборок демодулированного сигнала (соответствующих символам кодового слова), их запоминания и принятия решений о значениях оценкой символов и блоки: аналого-цифрового преобразования, управления, решающий, памяти и коммутации (коммутатор) [1, 3, 4, 6, 7].

Наиболее близкими по технической сути к заявляемому способу и устройству его реализации являются способ аналогового декодирования групповых кодов и устройство для его осуществления, выбранные в качестве прототипа [1].

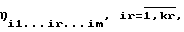

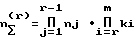

Способ состоит в том, что из входного отрезка сигнала Uвх(t), соответствующего кодовому слову, получают и запоминают  множество выборок (значений сигнала, соответствующих кодовым символам

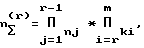

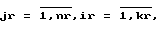

множество выборок (значений сигнала, соответствующих кодовым символам  (nr - количество бинарных символов r-того уровня (ступени) кодирования, m - количество уровней кодирования). Выборки подвергают преобразованиям, имеющим итеративный характер, в результате получают соответствующую каждому информационному символу

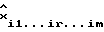

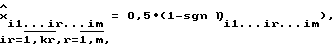

(nr - количество бинарных символов r-того уровня (ступени) кодирования, m - количество уровней кодирования). Выборки подвергают преобразованиям, имеющим итеративный характер, в результате получают соответствующую каждому информационному символу  решающую функцию ηi1...ir...im, по знаку (+ или -) последней определяют значение (0 или 1) соответствующей оценки информационного символа

решающую функцию ηi1...ir...im, по знаку (+ или -) последней определяют значение (0 или 1) соответствующей оценки информационного символа  [2] . Это соответствует частному случаю прототипа [1], когда M-й символ является двоичным.

[2] . Это соответствует частному случаю прототипа [1], когда M-й символ является двоичным.

Недостаток известного способа заключается в том, что при использовании всех проверочных соотношений кода его реализация сложна, а при ее упрощении происходит снижение помехоустойчивости декодирования и возникает необходимость в количестве итерации 1, много большем количества уровней кодирования m [2] , что ведет к снижению скорости передачи информации. Это аналогично случаю в [3].

Известный декодер, реализующий способ аналогового декодирования бинарных итеративных кодов, содержит аналого-цифровой преобразователь, два блока памяти, коммутатор, решающий блок, блок вывода информации и блок управления, вход которого соединен с синхронизирующим входом декодера, а выходы соединены с управляющими входами: первый и второй - соответственно с входами первого и второго блока памяти; третий - с входом аналого-цифрового преобразователя; четвертый - с входом решающего блока; пятый - с входом коммутатора; шестой - с входом блока вывода информации, выход которого соединен с выходом декодера, а вход - с выходом решающего блока, вход которого соединен с третьим выходом коммутатора, а его первый и второй выходы соединены соответственно с входами первого и второго блоков памяти, вторые входы которых соединены с выходом аналого-цифрового преобразователя, а выходы - соответственно с первым и вторым входами коммутатора, вход декодера соединен с входом аналого-цифрового преобразователя.

Недостатками известного декодера являются либо его сложность, либо снижение помехоустойчивости и увеличение времени декодирования. Последнее ведет к снижению скорости передачи информации [2, 3].

Заявляемый способ декодирования итерационных бинарных кодов и декодер для его осуществления обеспечивают повышение помехоустойчивости передачи сообщений за счет использования оптимального метода декодирования наиболее помехоустойчивого и эффективного класса кодов [2, 7] и уменьшение времени декодирования за счет меньшего количества итераций декодирования при относительно небольших аппаратурных затратах.

Отмеченный технический результат достигается тем, что в известный способ аналогового декодирования групповых кодов, состоящий в том, что из входного сигнала Uвх(t) получают и запоминают  выборок

выборок  и по знакам решающих функций

и по знакам решающих функций  определяют значения оценок

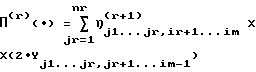

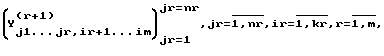

определяют значения оценок  соответствующих информационных символов xi1...ir...im, введены следующие существенные признаки: производят итеративно m раз неполное (далее просто аналоговое декодирование) аналоговое декодирование (т.е. без принятия решений о значениях оценок символов кода) соответственно m уровням декодирования, начиная с декодирования m-го уровня кодирования, так, что в результате аналогового декодирования r-го уровня кодирования получают

соответствующих информационных символов xi1...ir...im, введены следующие существенные признаки: производят итеративно m раз неполное (далее просто аналоговое декодирование) аналоговое декодирование (т.е. без принятия решений о значениях оценок символов кода) соответственно m уровням декодирования, начиная с декодирования m-го уровня кодирования, так, что в результате аналогового декодирования r-го уровня кодирования получают

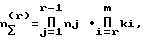

где ki, nj - количества информационных и кодовых символов i-го и j-го уровней кодирования)

значений сигнала (достаточных статистик) η

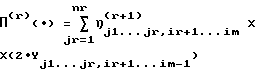

1) скалярным произведениям  между сигналами (векторами статистик)

между сигналами (векторами статистик)  полученными в предшествующей итерационной обработке сигналов, и возможными сигналами (2•yj1. . .jr,ir+1...im-1) кодовых слов (соответствующих векторам статистик)

полученными в предшествующей итерационной обработке сигналов, и возможными сигналами (2•yj1. . .jr,ir+1...im-1) кодовых слов (соответствующих векторам статистик)  r-го уровня кодирования;

r-го уровня кодирования;

2) экспоненциальным функциям exp[П(r)(•)] скалярных произведений П(r)(•);

3) суммам ∑0=∑

экспоненциальных функций соответственно для значений символов Yj1... jr-1,ir...im, равных 0 и 1;

4) логарифмам полученных сумм ∑0, ∑1;

5) разностям сумм η

При этом в декодер, содержащий аналого-цифровой преобразователь, два блока памяти, коммутатор, решающий блок, блок вывода информации и блок управления, вход которого соединен с синхронизирующим входом декодера, а выходы соединены с управляющими входами (первый и второй - соответственно с входами первого и второго блока памяти, третий - с входом аналого-цифрового преобразователя, четвертый - с входом решающего блока, пятый - с входом коммутатора, шестой - с входом блока вывода информации, выход которого соединен с выходом декодера, а вход - с выходом решающего блока, вход которого соединен с третьим выходом коммутатора, первый и второй выходы которого соединены соответственно с входами первого и второго блоков памяти, вторые входы которых соединены с выходом аналого-цифрового преобразователя, а выходы - соответственно с первым и вторым входами коммутатора), вход декодера соединен с входом аналого-цифрового преобразователя, введены генератор сигналов кодовых слов, блок вычитания, третий блок памяти и два идентичных блока вычисления логарифмов правдоподобия, каждый из которых состоит из последовательно соединенных коррелятора, устройства потенцирования, сумматора и логарифматора, при этом выходы блока управления соединены с управляющими входами (седьмой - с входами корреляторов, восьмой - с входами устройств потенцирования, девятый - с входами сумматоров, десятый - с входами логарифматоров), входы обоих корреляторов соединены с входами блоков вычисления логарифмов правдоподобия и с пятым выходом коммутатора, четвертый выход которого соединен с входом третьего блока памяти, второй вход которого соединен с выходом аналого-цифрового преобразователя, а выход - с четвертым входом коммутатора, пятый вход которого соединен с выходом блока вычитания, первый и второй входы которого соединены соответственно с выходами первого и второго блоков вычисления логарифмов правдоподобия; второй вход коррелятора, входящего в первый блок вычисления логарифмов правдоподобия, соединен с первым выходом генератора сигналов кодовых слов, а второй вход коррелятора, входящего во второй блок вычисления логарифмов правдоподобия, соединен с вторым выходом генератора сигналов кодовых слов; вход решающего блока соединен с вторым входом блока вывода информации, второй выход которого соединен с вторым выходом декодера.

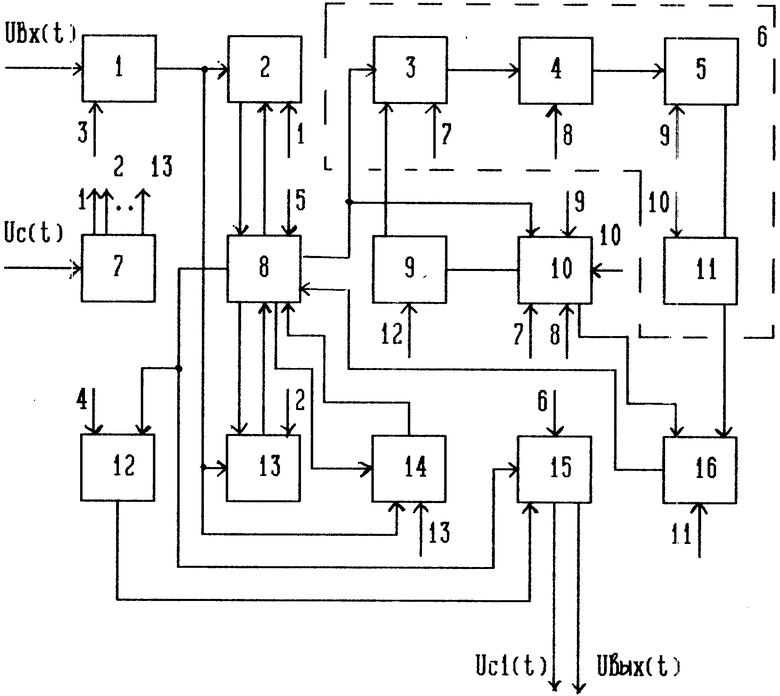

На чертеже представлена структурная схема декодера.

Декодер содержит аналого-цифровой преобразователь 1, первый, второй и третий блоки памяти 2, 13, 14 соответственно, первый и второй идентичные блоки вычисления логарифма правдоподобия 6 и 10 соответственно, блок управления 7, коммутатор 8, генератор сигналов кодовых слов 9, решающий блок 12, блок вывода информации 15 и блок вычисления 16, при этом блок вычисления логарифма правдоподобия 6 содержит последовательно соединенные коррелятор 3, устройство потенцирования 4, сумматор 5 и логарифматор 11, выход которого соединен с выходом блока вычисления логарифма правдоподобия 6 и с входом блока вычитания 16, второй вход которого соединен с выходом второго блока вычисления логарифма правдоподобия 10, а выход - с пятым входом коммутатора 8, первый, второй и четвертый входы и выходы которого соединены с выходами и входами первого 2, второго 13 и третьего 14 блоков памяти соответственно, пятый выход коммутатора 8 соединен с первым входом коррелятора 3, являющимся и первым входом блока вычисления логарифма правдоподобия 6, второй вход которого, являющийся и вторым входом коррелятора 3, соединен с первым выходом генератора сигналов кодовых слов 9, второй выход которого соединен с вторым входом блока вычисления логарифма правдоподобия 10, первый вход которого соединен с пятым выходом коммутатора 8, третий выход которого соединен с входом решающего блока 12 и вторым входом блока вывода информации 15, вход которого соединен с выходом решающего блока 12, а второй и первый выходы - с синхронизирующим и информационным выходами декодера, информационный вход которого соединен с входом аналого-цифрового преобразователя 1, выход которого соединен с вторыми входами первого 2, второго 13 и третьего 14 блоков памяти, синхронизирующий вход декодера соединен с блоком управления 7, выходы которого соединены с управляющими входами; первый, второй и тринадцатый - первого 2, второго 13 и третьего 14 блоков памяти; третий - аналого-цифрового преобразователя 1; четвертый - решающего блока 12; пятый - коммутатора 8; шестой - блока вывода информации 15; седьмой - обоих корреляторов; восьмой - обоих устройств потенцирования; девятый - обоих сумматоров; десятый - обоих логарифматоров; одиннадцатый - блока вычитания 16; двенадцатый - генератора сигналов кодовых слов 9.

Работает декодер в соответствии с предложенным способом декодирования следующим образом.

Из входного сигнала Uвх(t) в аналого-цифровом преобразователе 1, работающем как и все блоки под воздействием блока управления 7, получают множество выборок  соответствующих множеству кодовых символов кодового слова

соответствующих множеству кодовых символов кодового слова  итеративного кода. Полученные выборки записываются в тот блок памяти 2, 13, 14, который в данный момент не используется в итерационном процессе декодирования. По окончании декодирования предыдущего кодового слова через коммутатор 8 запомненные выборки поступают в первый и второй блоки вычисления логарифмов правдоподобия 6 и 10. В блоках 6, 10, 2, 13, 14, 8, 9, 16 производится итерационно m раз аналоговое декодирование соответственно m уровням кодирования, начиная с декодирования m-го уровня кодирования, так, что в результате аналогового декодирования r-го уровня кодирования получают

итеративного кода. Полученные выборки записываются в тот блок памяти 2, 13, 14, который в данный момент не используется в итерационном процессе декодирования. По окончании декодирования предыдущего кодового слова через коммутатор 8 запомненные выборки поступают в первый и второй блоки вычисления логарифмов правдоподобия 6 и 10. В блоках 6, 10, 2, 13, 14, 8, 9, 16 производится итерационно m раз аналоговое декодирование соответственно m уровням кодирования, начиная с декодирования m-го уровня кодирования, так, что в результате аналогового декодирования r-го уровня кодирования получают  сигналов (являющихся достаточными статистиками), несущих всю информацию о значениях (0 или 1) кодовых символов Y

сигналов (являющихся достаточными статистиками), несущих всю информацию о значениях (0 или 1) кодовых символов Y

По знакам (+ или -) сигналов (статистик), полученных при декодировании 1-го уровня кодирования, определяют в решающем блоке 12 значения (0 или 1) оценок информационных символов:

где sgnx=x/  - знаковая функция.

- знаковая функция.

При этом в процессе аналогового декодирования r-го уровня кодирования получают величины, равные:

1) скалярным произведениям  между сигналами (векторами статистик)

между сигналами (векторами статистик)  полученными в предшествующей итерационной обработке сигналов, и возможными сигналами (2•yj1...jr, ir+1...im-1) кодовых слов (соответствующих векторам статистик)

полученными в предшествующей итерационной обработке сигналов, и возможными сигналами (2•yj1...jr, ir+1...im-1) кодовых слов (соответствующих векторам статистик)  r-го уровня кодирования;

r-го уровня кодирования;

2) экспоненциальным функциям exp[П(r)(•)] скалярных произведений П(r)(•);

3) суммам ∑0=∑

экспоненциальных функций соответственно для значений кодовых символов yj1...jr-1,ir...im, равных 0 и 1;

4) логарифмам полученных сумм ∑0, ∑1;

5) разностям сумм η

Получаемые таким образом сигналы являются достаточными статистиками [4]. Поэтому здесь отсутствует потеря информации (в процессе любой итерационной обработки сигналов) относительно значений кодовых символов [4]. Это позволяет использовать эти сигналы в качестве исходной информации для следующей итерационной обработки сигналов и получать таким образом оптимальный способ декодирования.

В процессе итерационной обработки сигналов двуполярные сигналы генерируются в генераторе сигналов кодовых слов 9, скалярные произведения вычисляются в корреляторе 3, экспоненциальные функции получаются в устройстве потенцирования 4, суммирование производится в сумматоре 5, логарифмирование - в логарифматоре 11, вычитание - в блоке вычитания 16, (промежуточные) значения сигналов, полученные в блоке вычитания, запоминаются и хранятся в двух из трех (свободных в данный момент времени от процесса запоминания выборок) блоках памяти 2, 13, 14.

Для возможности использования декодера в целом для отмеченного неполного декодирования здесь предусмотрен вывод входного сигнала решающего блока в качестве выходного сигнала декодера. В этом случае (режиме работы) модуль сигнала несет информацию о надежности, а знак - о значении оценки соответствующего символа. Дополнительная информация о надежности может быть полезна в некоторых случаях.

Как следует из изложенного, обработка сигналов может быть цифровой и поэтому может быть реализована на цифровой элементной базе (микросхемы, микропроцессоры).

Подсчет общего количества операций NΣ, которым характеризуется сложность реализации декодера, определяется формулой

NΣ < a0•nΣ • logkrnΣ, (1)

где a0 - независимый от nΣ коэффициент, kr=const.

Формула (1) показывает хороший результат [3, 6].

Изложенное свидетельствует о новизне достижений указанного технического результата, подтверждает возможность осуществления изобретения, которое может быть использовано в области связи, телеуправления, телеизмерения и вычислительной техники.

Источники информации

1. Бронников В.Н. Заявка на изобретение (патент), зарегистрированная в НДЦПЕ ДП Украины за N 93005930 с приоритетом от 28.04.93 г. по вх. N 3402924 (2/579). - Промислова власнiсть. Оф. бюл. 1995, N 4.

2. Бронников В.Н., Крыжановский В.А. Помехоустойчивость и эффективность передачи сообщений с помощью m-уровневых итеративных кодов. - Радиоэлектроника, 1993, N 7.

3. Кларк Дж., Кейн Дж. Кодирование с исправлением ошибок в системах цифровой связи.

4. Форни Д. Каскадные коды. - М.: Мир, 1970.

Бронников В.Н., Денищенко И.Я. Применение метода декомпозиции при декодировании. - Тезисы доклада на 2-й Международной конференции UkrTeleCom-95. г. Одесса, 1995.

6. Питерсон У., Уэлдон Э. Коды, исправляющие ошибки. - М.: Мир, 1976.

7. Бородин Л.Ф. Введение в теорию помехоустойчивого кодирования. - М.: Сов. радио, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2007 |

|

RU2344556C1 |

| СПОСОБ ИТЕРАТИВНОГО ПРИЕМА И ДЕКОДИРОВАНИЯ ИНФОРМАЦИОННЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ РАЗЛИЧНЫХ ПОЛЬЗОВАТЕЛЕЙ В СИСТЕМЕ МНОГОПОЛЬЗОВАТЕЛЬСКОГО ДОСТУПА С КОДОВЫМ РАСШИРЕНИЕМ КАНАЛА | 2004 |

|

RU2312463C2 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ СТИРАНИЙ | 2008 |

|

RU2379841C1 |

| АРХИТЕКТУРА ПАМЯТИ ДЛЯ ДЕКОДЕРА МАКСИМАЛЬНОЙ АПОСТЕРИОРНОЙ ВЕРОЯТНОСТИ | 1999 |

|

RU2236085C2 |

| ДЕТЕКТИРОВАНИЕ И ДЕКОДИРОВАНИЕ С УМЕНЬШЕННОЙ СЛОЖНОСТЬЮ ДЛЯ ПРИЕМНИКА В СИСТЕМЕ СВЯЗИ | 2006 |

|

RU2414062C2 |

| СПОСОБ И УСТРОЙСТВО ПОМЕХОУСТОЙЧИВОГО ДЕКОДИРОВАНИЯ СИГНАЛОВ, ПОЛУЧЕННЫХ С ИСПОЛЬЗОВАНИЕМ КОДА ПРОВЕРКИ НА ЧЕТНОСТЬ С НИЗКОЙ ПЛОТНОСТЬЮ | 2013 |

|

RU2522299C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА | 2012 |

|

RU2485683C1 |

| Способ декодирования LDPC-кодов и устройство для его осуществления | 2016 |

|

RU2628459C1 |

| Кодек блочных кодов | 1988 |

|

SU1640829A1 |

| ИТЕРАТИВНОЕ ОЦЕНИВАНИЕ И ДЕКОДИРОВАНИЕ КАНАЛОВ И ПОМЕХ | 2005 |

|

RU2322762C1 |

Использование: в области передачи сообщений, в частности в системах телеизмерения, телеуправления, связи и в вычислительной технике. Сущность изобретения: повысить помехоустойчивость и скорость передачи сообщений при ограничениях на сложность реализации декодера. Способ декодирования содержит операции получения выборок сигнала кодового слова значений символов кодовых слов итерационно m раз соответственно m уровням итерационного кодирования, принятия решений о значениях информационных символов по знакам кодовых символов, полученных в последней итерации. Достижению технического результата способствует введение операций итеративного получения значений символов кодовых слов и введение блоков вычисления логарифмов правдоподобия, вычитания, памяти и генератора сигналов кодовых слов. Декодер, содержащий аналого-цифровой преобразователь 1, первый, второй и третий блоки памяти 2, 13, 14, первый и второй блоки вычисления логарифма правдоподобия 6, 10, блок управления 7, решающий блок 12, блок выбора информации 15, блок вычитания 16, коммутатор 8, генератор сигналов кодовых слов 9. 2 с.п.ф-лы, 1 ил.

соответствующих кодовым символам Yj1... jr...jm кодового слова, по знакам решающих функции ηi1...ir...im определяют значения оценок соответствующих информационных символов

соответствующих кодовым символам Yj1... jr...jm кодового слова, по знакам решающих функции ηi1...ir...im определяют значения оценок соответствующих информационных символов  отличающийся тем, что производят итерационно m раз аналоговое декодирование соответственно m уровням итерационного кодирования, начиная с m-го уровня кодирования, так, что в результате аналогового декодирования r-го уровня кодирования получают

отличающийся тем, что производят итерационно m раз аналоговое декодирование соответственно m уровням итерационного кодирования, начиная с m-го уровня кодирования, так, что в результате аналогового декодирования r-го уровня кодирования получают

где Ki, nj - количества информационных и кодовых символов i-го и j-го уровней кодирования, сигналов η полученные сигналы используют в качестве входных информационных сигналов для декодирования предыдущего (r-1)-го уровня кодирования, для декодирования m-го уровня кодирования используют выборки входного сигнала Uвх(t), выходные сигналы декодирования 1-го уровня кодирования тождественно определяют значения решающих функций ηi1...ir...im, в процессе декодирования r-го уровня кодирования получают величины, равные скалярным произведениям П(r)(•) между сигналами η

полученные сигналы используют в качестве входных информационных сигналов для декодирования предыдущего (r-1)-го уровня кодирования, для декодирования m-го уровня кодирования используют выборки входного сигнала Uвх(t), выходные сигналы декодирования 1-го уровня кодирования тождественно определяют значения решающих функций ηi1...ir...im, в процессе декодирования r-го уровня кодирования получают величины, равные скалярным произведениям П(r)(•) между сигналами η

| Кипятильник для воды | 1921 |

|

SU5A1 |

| -М.: Связь, 1970 | |||

| Бронни ков В.Н., Крыжановский В.В | |||

| Помехоустойчивость и эффективность передачи со общений с помощью m уровневых итеративных кодов | |||

| -Радиоэлектроника, N7, 19 93 | |||

| Кларк Дж., Кейн Дж | |||

| Кодирование с исправлением ошибок в системе связи | |||

| Форни В.Д | |||

| Каскадные коды | |||

| -М.: Мир, 1970 | |||

| Бронников В.Н., Денищенко И.Я | |||

| Применение метода декомпозиции при декодировании | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Одесса, 1995 | |||

| Питерсон У., Уэл дон Э | |||

| Коды, исправляющие ошибки | |||

| Мир, 1976 | |||

| Бородин Л.Ф | |||

| Введение в теори ю помехоустойчивого декодирования | |||

| -М.: Сов | |||

| радио, 1961. | |||

Авторы

Даты

1998-06-20—Публикация

1995-09-06—Подача