Изобретение относится к вычислительной технике и технике связи и может быть использовано в цифровых сис- темах передачи информации.

Цель изобретения - повышение помехоустойчивости декодирования.

Блок-схема кодека блочных кодов приведена на фиг.1; на фиг.2 и 3 даны схемы промежуточной и оконечной ступеней декодирования, фиг.4 и 5 иллюстрируют принцип действия кодека.

Кодек блочных кодов состоит из передающей стороны 1, приемной стороны 2 и канала 3 связи.

Передающая сторона 1 выполнена аналогично прототипу и содержит кодеры 4 и цифроаналоговый преобразователь 5 (ЦАП).

Приемная сторона 2 содержит аналого-цифровой преобразователь 6 (АЦП) и ступени 7 декодирования. Первая ступень 7 декодирования включает в себя блок 8 памяти, фазовращатель 9, логический анализатор 10, первый и второй декодеры 11 и 12, первый и второй элементы 13, 14 памяти, первый и второй счетчики 15, 16 импульсов, элемент 17 сравнения, коммутатор 18, элемент НЕ 19, блок 20 задержки, первый и второй сумматоры 21, 22 по модулю два.

На фиг. 1 обозначены входы 23 и выходы 24. Канал 3 связи состоит из фазового модулятора 25, линии 26 связи и фазового демодулятора 27.

Каждая из второй - М-1-ой ступеней декодирования (М-крато

ь

О 00

to

СО

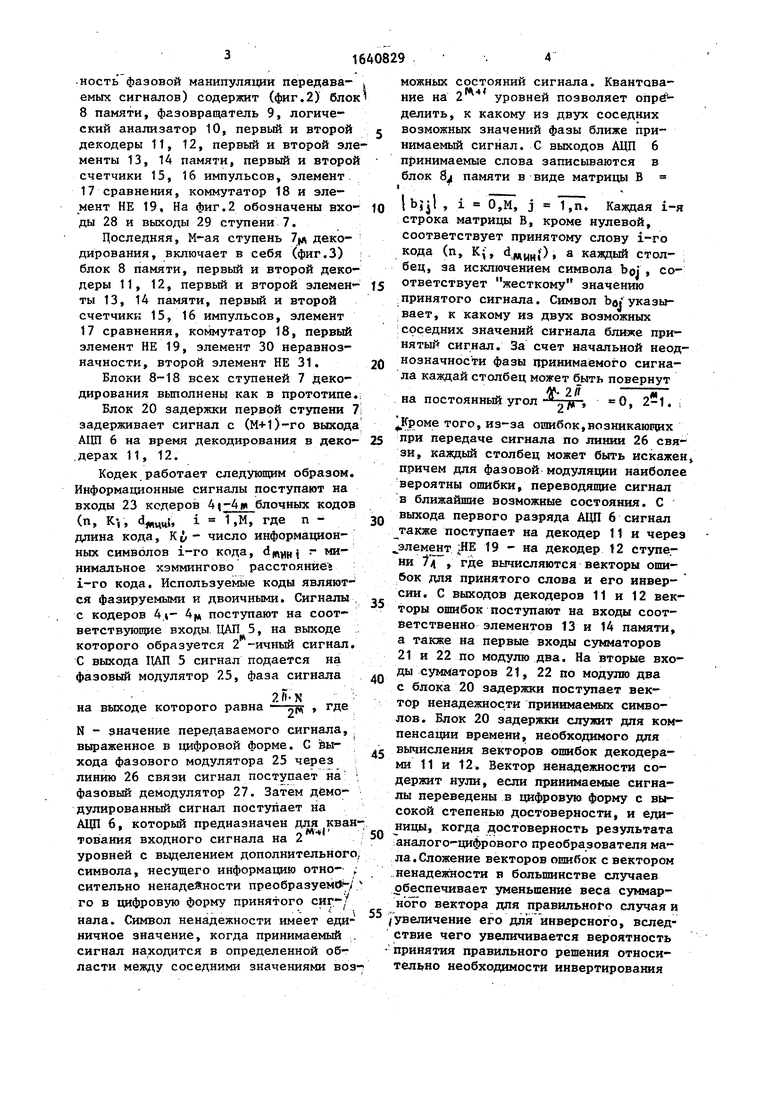

ность фазовой манипуляции передана- емых сигналов) содержит (фиг.2) блок 8 памяти, фазовращатель 9, логический анализатор 10, первый и второй декодеры 11, 12, первый и второй элементы 13, 14 памяти, первый и второй счетчики 15, 16 импульсов, элемент 17 сравнения, коммутатор 18 и элемент НЕ 19, На фиг.2 обозначены входы 28 и выходы 29 ступени 7.

Последняя, М-ая ступень 7цц декодирования, включает в себя (фиг.З) блок 8 памяти, первый и второй декодеры 11, 12, первый и второй элементы 13, 14 памяти, первый и второй счетчики 15, 16 импульсов, элемент 17 сравнения, коммутатор 18, первый элемент НЕ 19, элемент 30 неравнозначности, второй элемент НЕ 31.

Блоки 8-18 всех ступеней 7 декодирования выполнены как в прототипе. Блок 20 задержки первой ступени 7 задерживает сигнал с (М-Н)-го выхода АЦП 6 на время декодирования в декодерах 11, 12.

Кодек работает следующим образом. Информационные сигналы поступают на входы 23 кодеров блочных кодов (n, K-,, dW4Wj, i 1 ,М, где n - длина кода, К Ј, - число информационных символов 1-го кода, d г мк нимальное хэммингово расстояние 1-го кода. Используемые коды являются фазируемыми и двоичными. Сигналы с кодеров 4ц поступают на соответствующие входы ЦАП 5, на выходе которого образуется 2 -ичный сигнал. С выхода ЦАП 5 сигнал подается на фазовый модулятор 25, фаза сигнала

2 ft- N на выходе которого равна -ж , где

N - значение передаваемого сигнала, выраженное в цифровой форме. С выхода фазового модулятора 25 через линию 26 связи сигнал поступает на фазовый демодулятор 27. Затем демо- дулированный сигнал поступает на АЦП 6, который предназначен для кван2М | г .

уровней с выделением дополнительного, символа, несущего информацию отно- , сительно ненадежности преобразуем 1-/ го в цифровую форму принятого сигнала. Символ ненадежности имеет единичное значение, когда принимаемый сигнал находится в определенной области между соседними значениями воз0

5

0

5

0

5

0

5

0

5

можных состояний сигнала. Квантование на уровней позволяет делить, к какому из двух соседних возможных значений фазы ближе принимаемый сигнал. С выходов АЦП 6 принимаемые слова записываются в

блок 8,л памяти в виде матрицы В i

bjji , i 0,М, j 1,п. Каждая i-я строка матрицы В, кроме нулевой, соответствует принятому слову 1-го кода (n, К}, dWHK{), а каждый столбец, за исключением символа boi , соответствует жесткому значению принятого сигнала. Символ be указывает, к какому из двух возможных соседних значений сигнала ближе принятый сигнал. За счет начальной неоднозначности фазы принимаемого сигнала каждай столбец может быть повернут

. # 2ff 1ST на постоянный угол jTF 2-1.

Кроме того, из-за ошибок,возникающих при передаче сигнала по линии 26 связи, каждый столбец может быть искажен, причем для фазовой модуляции наиболее вероятны ошибки, переводящие сигнал в ближайшие возможные состояния. С выхода первого разряда АЦП 6 сигнал также поступает на декодер 11 и через элемент -НЕ 19 - на декодер 12 ступени 1ц , где вычисляются векторы ошибок для принятого слова и его инвер- сии, С выходов декодеров 11 и 12 векторы ошибок поступают на входы соответственно элементов 13 и 14 памяти, а также на первые входы сумматоров 21 и 22 по модулю два. На вторые входы сумматоров 21, 22 по модулю два с блока 20 задержки поступает вектор ненадежности принимаемых символов. Блок 20 задержки служит для компенсации времени, необходимого для вычисления векторов ошибок декодерами 11 и 12. Вектор ненадежности содержит нули, если принимаемые сигналы переведены в цифровую форму с высокой степенью достоверности, и единицы, когда достоверность результата аналого-цифрового преобразователя мала. Сложение векторов ошибок с вектором ненадежности в большинстве случаев обеспечивает уменьшение веса суммарного вектора для правильного случая и /увеличение его для инверсного, вследствие чего увеличивается вероятность принятия правильного решения относительно необходимости инвертирования

принятого слова путем определения суммарного вектора с минимальным весом. Вес получаемых суммарных векторов подсчитывается счетчиками 15 и 16 импульсов, на входы которых подаются сигналы с сумматоров 21, 22 по модулю два. Со счетчиков 15 и 16 импульсов результаты вычисления весо суммарных векторов подаются на соответствующие входы элемента 17 сравнения . В случае необходимости инвертирования принятого слова, т.е., если вес суммарного вектора оказывается меньше для инверсии принятого слова, с элемента 17 сравнения на управляющий вход .коммутатора 18 и первый вход логического анализатора 10 подается единичный сигнал. В противном случае единичный сигнал на выходе элемента 17 сравнения отсутствует. При поступлении на управляющий вход коммутатора 18 нулевого (единичного) сигнала на второй вход логического анализатора 10 через коммутатор 18 подается вектор ошибок принятого слова (его инверсии). На третий вход логического анализатора 10 с первого выхода блока 8 памяти поступают символы Ъ0 , используемые для определения ближайшего из возможных сигналов, в который переводится принятый сигнал при определении ошибки в соответствующем символе принятого слова. С выходов логического анализатора 10 на управляющие входы фазовращателя 9 подается сигнал коррекции, возможные значения которого в зависимости от сигналов на входах логического анализатора 10 приведены в таблице.

-,«

Суммирование сигналов по модулю , поступающих с блока 8 памяти и

логического анализатора 10, которое реализует фазовращатель 9, обеспечивает необходимое изменение номера сигнала. Так как фазовращатель 9 осуществляет необходимую коррекцию принятого сигнала, то отпадает необходимость использования элемента неравнозначности для коррекции ошибок путем сложения по модулю два принятого слова и вектора ошибок. При этом элемент неравнозначности инвертирует символ принятого слова, если соответствующий символ вектора ошибок равен единице. Фазовращатель 9 первой ступени 7j , изменяя в случае .

5

ошибки принятый сигнал на сосепний, номер которого отличается точно на единицу, реализует ту же самую функцию для первого кодового слова. Поэтому для упрощения кодека блочных кодов выходами ступеней 7 декодирования, содержащих логический анализатор 10 и фазовращатель 9 служат соответствующие выходы фазовращателя 9 , откуда сигнал подается на входы блока памяти следующей ступени. i

Дальнейшее декодирование на 1-й ступени 7 (, М-1) производится аналогично. С выходов фазо0

5

0

5

0

5

С

5

вращателя 9g ступени 7р.,, сигнал поступает на М+2-1 входов блока 8 памяти 1-й ступени 7Ј. Одновременно сигнал, поступающий на второй вход блока 8 памяти, подается на декодер 11 и через элемент НЕ 19 - на декодер 12, где вычисляются векторы ошибок для принятого слова и его инверсии. С декодеров 11 и 12 векторы ошибок поступают соответственно на элементы 13 и 14 памяти, а также счетчики 15, 16 импульсов, вычисляющие веса соответствующих векторов ошибок. Вычисленные значения поступают на входы элемента 17 сравнения, определяющего, какое из двух значений меньше. В зависимости от результата с элемента 17 сравнения на управляющий вход коммутатора 18 и первый вход логического анализатора 10 подается либо нулевой (если вес вектора ошибок принятого слова меньше веса вектора ошибок его инверсии), либо единичный сигнал. Соответственно с коммутатора 18 на второй вход логического анализатора 10 поступает тот вектор ошибок, вес которого меньше. Третий вход логического анализатора 10 соединен с первым выходом блока 8 памяти. Вычисляемое значение сигнала коррекции с выходов логического анализатора 10 поступает на управляющие входы фазовращателя 9. Сигнал, поступающий на фазовращатель 9 с выходов блока 8 памяти, за исключением первого выхода, суммируется с сигналом коррекции по модулю 2 а затем с выходов фазовращателя 9 поступает на входы следующей ступени деколи- рования. Выходом 1-й ступени 7j декодирования является первый выход фазовращателя 9.

i

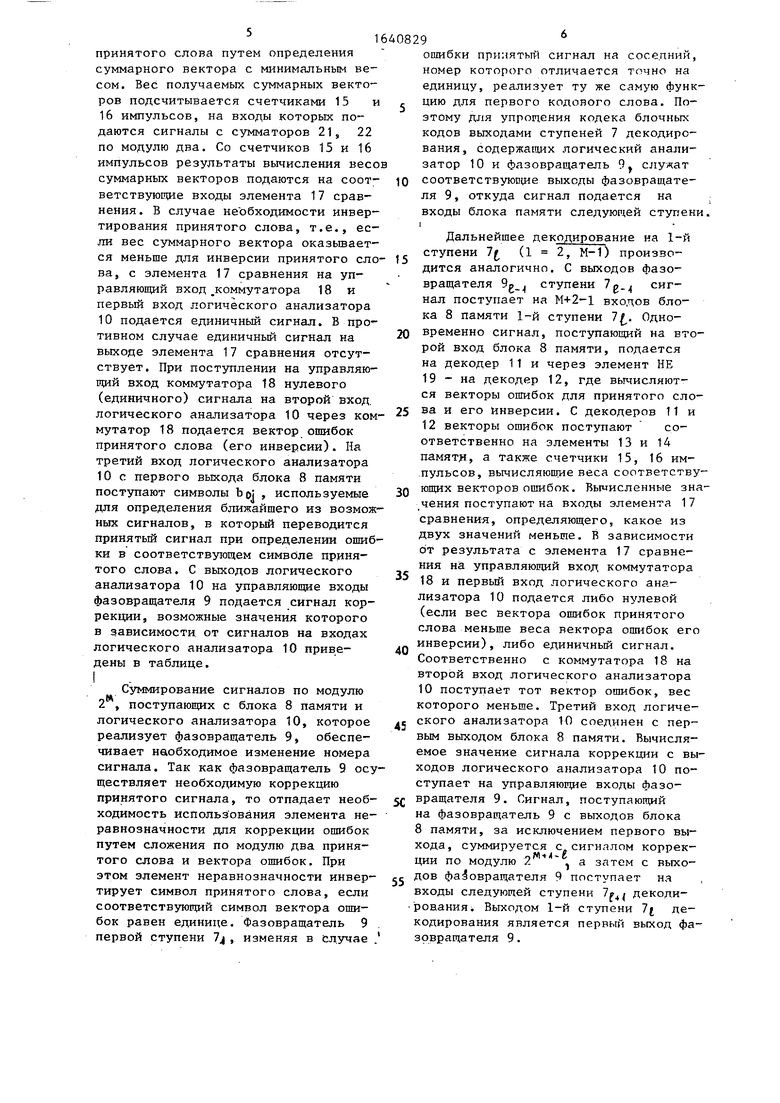

Рассмотрим фрагмент сигнальной диаграммы многопозиционной фазовой модуляции, приведенный на фиг.4. Пе- редаваемые сигналы обозначены точками А и В на единичной окружности. Принимаемые решения на выходе анало- но-цифрового преобразователя 6 о значении принятого сигнала обозначе

На последней, М-й, ступени 7 декодирования необходимость использования фазовращателя 9 и логического анализатора /10 отпадает, так как коррекции подлежит только последнее М-е слово bflj , j 1, n.i Поэтому блок 8 памяти этой ступени 7цл имеет один вход, на который с соответствующего выхода фазовращателя 9щ ступени 7. подаются символы с учетом изменений, внесенных в результате коррекций на предыдущих ступенях 7. Одновременно эти символы поступают на де кодер 11 и через элемент НЕ 19 - надекодер 12. С декодеров 11 и 12 вычисленные значения векторов ошибок для принятого слова и его инверсии поступают соответственно на элементы 13 и 14 памяти, а также на счетчики 15, 16 импульсов, вычисляющие веса соответствующих векторов ошибок. Вычисленные значения поступают на входы элемента 17 сравнения, с выхода которого в зависимости от полученного результата на управляющий вход коммутатора 18 поступает либо нулевой, либо единичный сигнал. Первый вход коммутатора 18 соединен с выходом элемента 13 памяти, а второй вход - через элемент НЕ 31 - с выходом элемента 14 памяти. С коммутатора 18 сигнал поступает на первый вход элемента 30 неравнозначности, на второй вход которого с блока 8 памяти поступают символы Ь«м . Эле- мент 30 неравнозначности исправляет ошибки путем посимвольного сложения вектора ошибок, и.принятого слова по модулю два. Сложение принятого слова с инвертированным вектором ошибок, выделенных декодером 12, приводит к одновременному исправлению ошибок и инвертированию кодового слова.

Положительный эффект состоит в повышении помехоустойчивости декодирования всей кодовой конструкции за счет того, что при принятии решения учитывается степень надежности значения полученных символов.

0

0

5

5

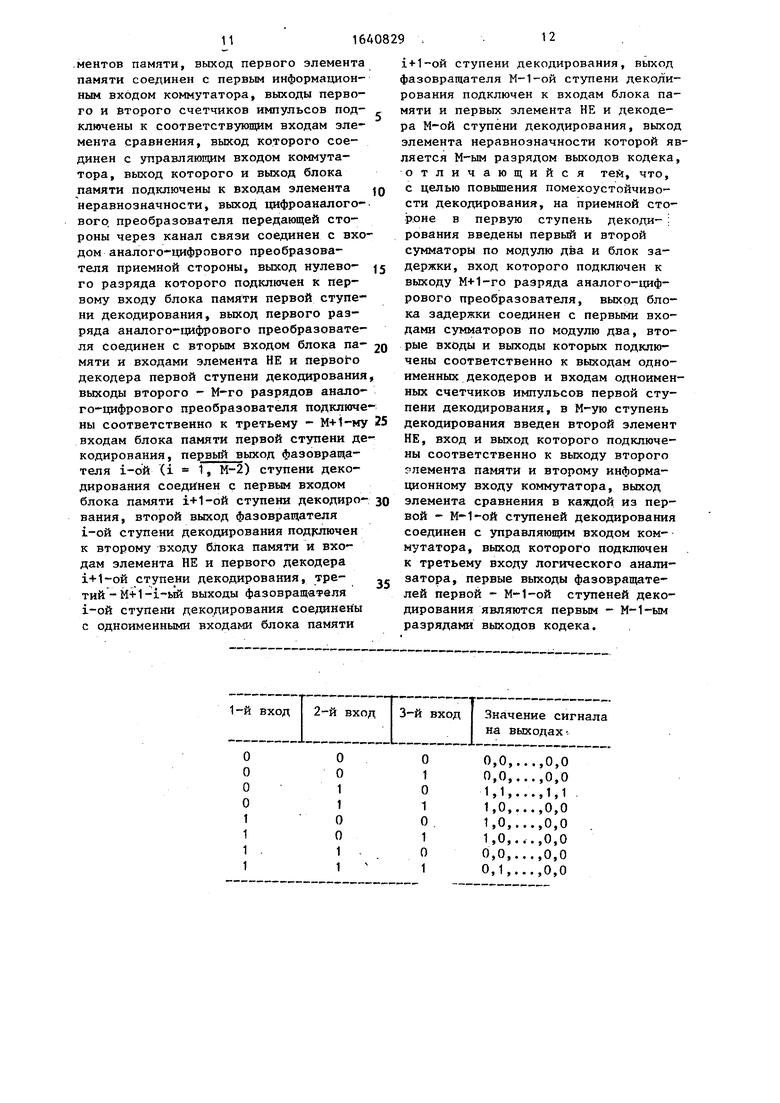

ны окружностями. При этом каждому передаваемому сигналу соответствуют два возможных значения: сигналу А - точки АО и Ал, сигналу В - точки Во и В к. Использование при приеме двух возможных значений для каждого передаваемого сигнала позволяет определить направление отклонения принятого сигнала от ближайшей сигнальной точки передаваемого сигнала. Так как отклонения принимаемого сигнала в обе стороны равновероятны, в дальнейшем будем определять вероятность ошибочного решения при отклонении принимаемого сигнала только в одну сторону. В прототипе при попадании принятого сигнала на отрезки дуги (зоны) единичной окружности, ограничивающие секторы 1 и 2, значение на выходах аналого-цифрового преобразователя 6 соответствует точке А, а при попадании принятого сигнала в зоны 3 и 4 - точке В.

В данном кодеке блочных кодов значение на выходах аналого-цифрового преобразователя 6 определяется аналогично прототипу. Значение же на дополнительном выходе определяется следующим образом. При попадании принятого сигнала в зоны 1 и 4 значение символа ненадежности, снимае- мого с дополнительного выхода АПП 6. равно нулю, а при попадании в зоны

2 и 3 - единице. Иными словами, при э - л

0

0

5

0

5

небольших отклонениях принятого сигнала от сигнальной точки фазового модулятора 25 значение сигнала на выходах АЦП 6 полагается надежным, а при больших отклонениях - ненадежным.

При безошибочном приеме вес вектора ошибок правильно принятого слова равен нулю, а для ближайшего из инвертированных кодовых слов - равен

d, если dЈ -- . Если в принятом

слове искажен тот символ, который одинаков у ближайшего кодового слова и ближайшего инвертированного кодового слова, то и в том и в другом случаях вес векторов ошибок увеличивается одинаково, а их разность по-прежнему равна d. При искажении /различающихся символов ближайшего к принятому кодового слова и инвертированного кодового слова веса векторов ошибок изменяются следующим образом: вес вектора ошибки для правильно принятого слова увеличивается

на количество искаженных символов, а для инверсии принятого слова - уменьшается на такое же число. Если искажается один символ, разность весов векторов ошибок d - Ad d-2. Пусть передается точка А. Будем полагать, что отношение сигнал/шум таково, что вероятность отклонения принятой точкии дальше точки В мала и ею можно пренебречь. Без учета степени надежности принятых символов, т.е. для прототипа, математическое ожидание изменения разности весов векторов ошибок при передаче и приеме одного различающегося сим- вола М| - О (Р + Pft) + 2 (Р3 +Р4) 2Р$ +2Рд, где Р -Р$- соответственно вероятности попадания в зоны 1-4. При сложении вычисленных векторов ошибок с вектором символов ненадежностиимеют место следующие ситуации:

1.Принятая точка попадает в зону 1. При этом значение символа ненадежности равно нулю, и изменение разности суммарных векторов также равно нулю, так как символ принят безошибочно.

2.Принятая точка попадает в зону 2. Тогда значение символа ненадежности равно единице. В этом случае вес суммарного вектора принятого слова увеличивается на единицу,

а инверсии принятого слова уменьшается на единицу. Следовательно, разность суммарных векторов уменьшается на два.

3.Принятая точка попадает в зону 3. Значение символа ненадежности равно единице. Вес суммарного вектора для принятого слова не изменяется, так как вектор ошибок также содержит единицу в позиции, соответствующей этой точке. Вес суммарного вектора для инверсии принятого слова увеличивается на единицу.

4.Принятая точка попадает в зону 4. Так как символ принят с ошибкой, но считается надежным, то разность суммарных векторов уменьшается на два.

Для каждого значения отношения сигнал/шум существует оптимальный угол If (фиг.4), при котором помехоустойчивость декодирования максимальна.

0

5

0

5

0

5

0

5

0

5

На. фиг.5 приведена сигнальная диаграмма восьмипозиционной фазовой модуляции.

Формула изобретения

Кодек блочных кодов, состоящий из передающей и приемной сторон и канала связи, передающая сторона содержит М кодеров (М - кратность фазовой манипуляции передаваемых сигналов) , входы которых являются входами кодека, а выходы соединены с входами цифроаналогового преобразователя, приемная сторона содержит аналого-цифровой преобразователь и М ступеней декодирования, каладая из первой - М-1-ой ступеней декодирования включает в себя блок памяти, фазовращатель, логический анализатор, первый и второй декодеры, первый и второй элементы памяти, первый и второй счетчики импульсов, коммутатор, элемент НЕ и элемент сравнения, первый выход блока памяти соединен с первым входом логического анализатора, остальные выходы блока памяти и выходы логического анализатора подключены соответственно к информационным и управляющим входам фазовращателя, выход элемента НЕ соединен с входом второго декодера, выходы первого и второго элементов памяти соединены с первым и вторым информационными входами коммутатора, управляющий вход которого объединен с вторым входом логического анализатора, выходы первого и второго счетчиков импульсов подключены к соответствующим входам элемента сравнения, выходы первого и второго декодеров первой ступени декодирования подключены к входам одноименных элементов памяти, выходы первого и второго декодеров второй - М-1-ой ступеней декодирования соединены с входами одноименных элементов памяти и счетчиков импульсов, М-ая ступень декодирования включает блок-памяти, первый и второй декодеры, первый и второй элементы памяти, первый и второй счетчики импульсов, элемент неравнозначности, коммутатор, элемент сравнения и первый элемент НЕ, выход которого соединен с входом второго декодера, выходы первого и второго декодеров подключены к входам одноименных счетчиков импульсов и эле

ментов памяти, выход первого элемента памяти соединен с первым информационным входом коммутатора, выходы первого и второго счетчиков импульсов подключены к соответствующим входам элемента сравнения, выход которого соединен с управляющим входом коммутатора, выход которого и выход блока памяти подключены к входам элемента неравнозначности, выход цифроаналого- вого преобразователя передающей стороны через канал связи соединен с входом аналого-цифрового преобразователя приемной стороны, выход нулевого разряда которого подключен к первому входу блока памяти первой ступени декодирования, выход первого разряда аналого-цифрового преобразователя соединен с вторым входом блока па- мяти и входами элемента НЕ и первого декодера первой ступени декодирования выходы второго - М-го разрядов аналого-цифрового преобразователя подключены соответственно к третьему - М+1-му входам блока памяти первой ступени декодирования, первый выход фазовращателя i-ой (, M-2) ступени декодирования соединен с первым входом блока памяти i+1-ой ступени декодиро- вания, второй выход фазовращателя i-ой ступени декодирования подключен к второму входу блока памяти и входам элемента НЕ и первого декодера i+1-ой ступени декодирования, третий -M+l-i-ый выходы фазовращателя i-ой ступени декодирования соединены с одноименными входами блока памяти

0

5

0 5 0

35

i+1-ой ступени декодирования, выход фазовращателя М-1-ой ступени декодирования подключен к входам блока памяти и первых элемента НЕ и декодера М-ой ступени декодирования, выход элемента неравнозначности которой является М-ым разрядом выходов кодека, отличающийся тем, что, с целью повышения помехоустойчивости декодирования, на приемной стороне в первую ступень декодирования введены первый и второй сумматоры по модулю два и блок задержки, вход которого подключен к выходу М-Н-го разряда аналого-цифрового преобразователя, выход блока задержки соединен с первыми входами сумматоров по модулю два, вторые входы и выходы которых подключены соответственно к выходам одноименных декодеров и входам одноименных счетчиков импульсов первой ступени декодирования, в М-ую ступень декодирования введен второй элемент НЕ, вход и выход которого подключены соответственно к выходу второго лемента памяти и второму информационному входу коммутатора, выход элемента сравнения в каждой из первой - М-1-ой ступеней декодирования соединен с управляющим входом коммутатора, выход которого подключен к третьему входу логического анализатора, первые выходы фазовращателей первой - М-1-ой ступеней декодирования являются первым - М-1-ым разрядами выходов кодека.

---i

Ч . . . 2:-э

7(

47

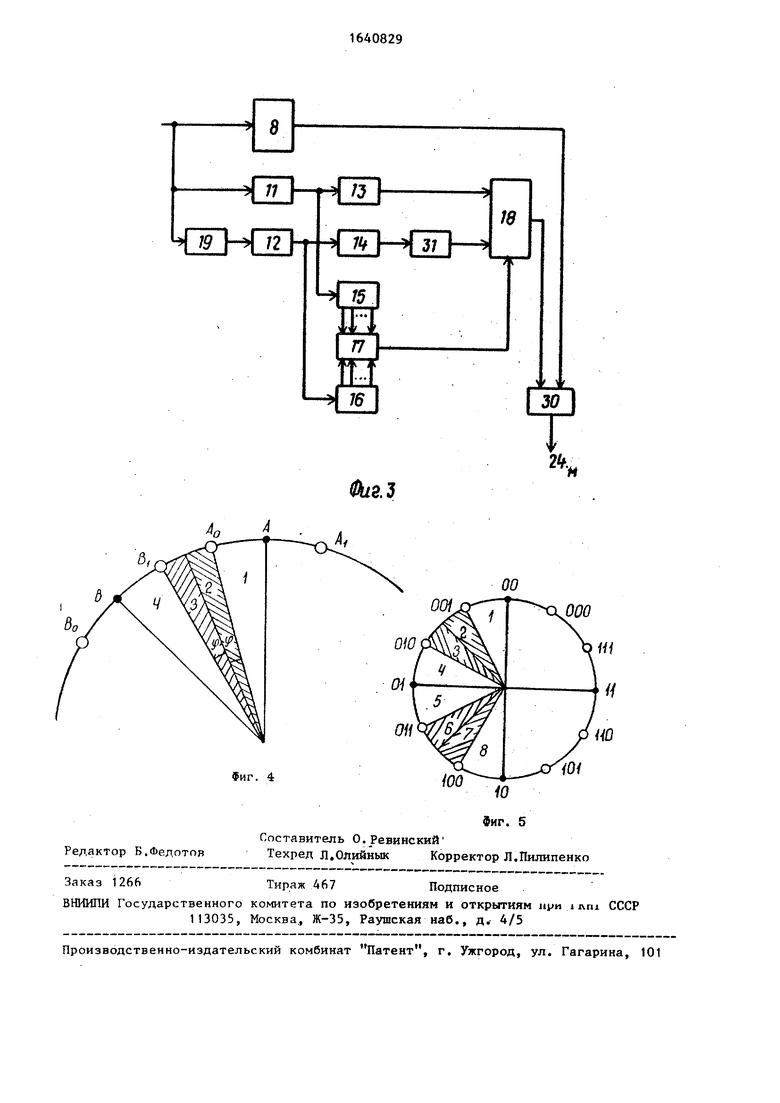

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Кодек каскадного мажоритарного кода | 1984 |

|

SU1185613A1 |

| Устройство для декодирования итеративного кода | 1988 |

|

SU1547080A1 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Кодек блочных кодов | 1987 |

|

SU1473088A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

Изобретение относится к вычислительной технике и технике связи. Его использование в цифровых системах передачи информации позволяет повысить помехоустойчивость декодирования. Кодек содержит на передающей стороне 1 кодеры 4 и цифроана- логовый преобразователь 5, канал 3 связи, а на приемной стороне 2 - аналого-цифровой преобразователь 6 и ступени декодирования, каждая из которых включает блок 8 памяти, фазовращатель 9, логический анализатор 10, декодеры 11, 12, элементы 13, 14 памяти, счетчики 15, 16 импульсов, элемент 17 сравнения, коммутатор 18 и элемент НЕ 19. Цель достигается благодаря введению в пер-м вую ступень 7 блока 20 задержки и сумматоров 21, 22 по модулю два. 1 табл., 5 ил. (Л

.

0

АО А

ft

Фиг. 4

&8.3

оо

000

№

/Of

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кодек блочных кодов | 1984 |

|

SU1270899A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-04-07—Публикация

1988-05-06—Подача