Изобретение относится к радиотехнике и может использоваться в радионавигации, в частности при пеленговании радиоизлучений.

Известен двухканальный автоматический радиопеленгатор c визуальным отсчетом пеленга [1], содержащий антенный блок, радиоприемные устройства вертикального и горизонтального каналов, смесители и электронно-лучевую трубку. Данный радиопеленгатор обеспечивает раздельное пеленгование сигналов, отличающихся по частоте и попадающих в полосу пропускания приемников. Однако данный пеленгатор имеет низкую точность пеленгования, что обусловлено неиспользованием информации о количестве мод и характере поляризации каждого из пеленгуемых сигналов.

Известен цифровой пеленгаторный радиоприемник [2], содержащий антенный блок и аналого-цифровые преобразователи.

Однако известный радиоприемник имеет низкую точность пеленгования, что обусловлено неиспользованием информации о количестве мод и характере поляризации пеленгуемого сигнала.

Известен также цифровой пеленгаторный радиоприемник [3], содержащий антенный блок, два широкополосных усилителя, два аналого-цифровых преобразователя, два анализатора амплитудного спектра и блок вычисления пеленгов. Данное устройство позволяет определять пеленг на источник радиосигнала при более низком отношении сигнал/шум, а также разделение по частоте сигналов, попадающих в полосу пропускания широкополосных усилителей. Однако этот пеленгаторный приемник имеет низкую точность пеленгования, что обусловлено неиспользованием информации о количестве мод и характере поляризации пеленгуемого сигнала.

Наиболее близким по своей сущности к заявляемому цифровому радиопеленгатору является ВЧ-пеленгатор [4], содержащий антенный блок, антенный коммутатор, последовательно соединенные первый радиоприемник, первый аналого-цифровой преобразователь и первый цифровой фильтр, последовательно соединенные опорную антенну, второй радиоприемник, второй аналого-цифровой преобразователь и второй цифровой фильтр, генератор опроса антенн и блок вычисления пеленгов, причем сигнальный выход антенного коммутатора подключен к входу первого радиоприемника, а управляющий вход антенного коммутатора соединен с выходом генератора опроса антенн, тактовые входы аналого-цифровых преобразователей подключены к выходу генератора тактовых импульсов, входящего в состав блока вычисления пеленгов, выходы цифровых фильтров подключены к сигнальным входам блока вычисления пеленгов, а управляющие входы цифровых фильтров подключены также к выходу генератора опроса антенн.

Данный ВЧ-пеленгатор использует эффект Доплера, что позволяет упростить блок вычисления пеленга и снизить уровень ошибок. Кроме того, при пеленговании узкополосных сигналов, либо сигналов с известной структурой пеленгатор на основе эффекта Доплера позволяет решить задачу раздельного пеленгования сигналов одного источника излучения, пришедших в точку приема по разным траекториям, в частности земной и пространственной волной, либо при отражении от разных слоев ионосферы.

Однако на практике нередко возникает необходимость пеленговать модулированные радиосигналы, занимающие определенную полосу частот и имеющие в общем случае непрерывный спектр. Структура таких сигналов, как правило, неизвестна. При пеленговании таких сигналов известный ВЧ-радиопеленгатор не обеспечивает высокую точность пеленгования. Кроме того, в диапазоне ВЧ нередко имеет место многолучевое распространение радиоволн. При этом электромагнитное поле в месте приема образуется в результате интерференции двух или значительно реже трех и более сигналов одного источника радиоизлучения, пришедших в пункт приема по разным траекториям. При пеленговании интерферирующих модулированных радиосигналов с известной структурой, пришедших в точку приема от одного источника радиоизлучения, прототип имеет низкую точность измерения параметра линии положения, что обусловлено неиспользованием информации о количестве мод и характере поляризации пеленгуемого сигнала.

Целью изобретения является повышение точности пеленгования неизвестных модулированных сигналов и решение задачи раздельного пеленгования компонент двухмодового поля.

Поставленная цель достигается тем, что в известный цифровой радиопеленгатор, содержащий антенный блок, первый и второй радиоприемники, первый и второй аналого-цифровые преобразователи, первый и второй буферные накопители, первый и второй блоки дискретного преобразования Фурье, блок весовой обработки, блок опорных частот и блок вычисления пеленгов, причем сигнальные выходы первого и второго радиоприемников подключены к входам соответствующих аналого-цифровых преобразователей, выходы первого и второго буферных накопителей соединены с входами соответствующих блоков дискретного преобразования Фурье, сигнальные выходы которых соединены с соответствующими входами блока весовой обработки, гетеродинные входы первого и второго радиоприемников подключены к гетеродинному выходу блока опорных частот, а тактовые входы первого и второго аналого-цифровых преобразователей, буферных накопителей и блоков дискретного преобразования Фурье соединены с выходом тактовой частоты блока опорных частот, причем выход блока вычисления пеленга является выходом радиопеленгатора, дополнительно введены блок управления, третий радиоприемник, третий аналого-цифровой преобразователь, третий буферный накопитель, третий блок дискретного преобразования Фурье, третий блок весовой обработки, блок ковариационной матрицы, блок матричной обработки и блок весовых коэффициентов. Антенный блок состоит из первой, второй и третьей антенн, подключенных к сигнальным входам соответствующих радиоприемников. Сигнальный выход третьего радиоприемника соединен с сигнальным входом третьего аналого-цифрового преобразователя, гетеродинный вход третьего радиоприемника подключен к гетеродинному выходу блока опорных частот, тактовые входы третьего аналого-цифрового преобразователя, третьего буферного накопителя и третьего блока дискретного преобразования Фурье подключены к выходу тактовой частоты блока опорных частот. Сигнальные выходы первого, второго и третьего аналого-цифровых преобразователей подключены к соответствующим сигнальным входам блока управления, а его первый, второй и третий сигнальные выходы подключены к сигнальным входам соответствующих буферных накопителей. Счетный вход блока управления соединен с синхронизирующим выходом первого буферного накопителя, а установочный вход подключен к установочному выходу блока весовых коэффициентов. Первый управляющий выход блока управления соединен с управляющими входами блока весовой обработки, ковариационной матрицы и блока весовых коэффициентов. Выход "Разрешение" блока управления подключен к одноименному входу блока весовых коэффициентов. Выход третьего буферного накопителя соединен с сигнальным входом третьего блока дискретного преобразования Фурье, сигнальный выход которого подключен к третьему сигнальному входу блока весовой обработки. Синхронизирующие и тактовые выходы первого, второго и третьего блоков дискретного преобразования Фурье соединены с соответствующими входами блока весовой обработки. Первый, второй и третий выходы блока весовой обработки подключены к соответствующим сигнальным входам блока ковариационной матрицы, установочный вход которого соединен с установочным выходом блока весовых коэффициентов. Выходы блока ковариационной матрицы соединены с входами блока матричной обработки, первый и второй выходы которого подключены к двум сигнальным входам блока вычисления пеленгов три взвешивающих, четыре информационных, синхронизирующий и установочный входы которого соединены с соответствующими выходами блока весовых коэффициентов. Тактовый вход блока весовых коэффициентов соединен с тактовым выходом блока опорной частоты.

Благодаря указанной совокупности признаков повышается точность пеленгования модулированных радиосигналов с известной структурой и обеспечивается возможность раздельного определения направлений прихода компонент двухмодового поля.

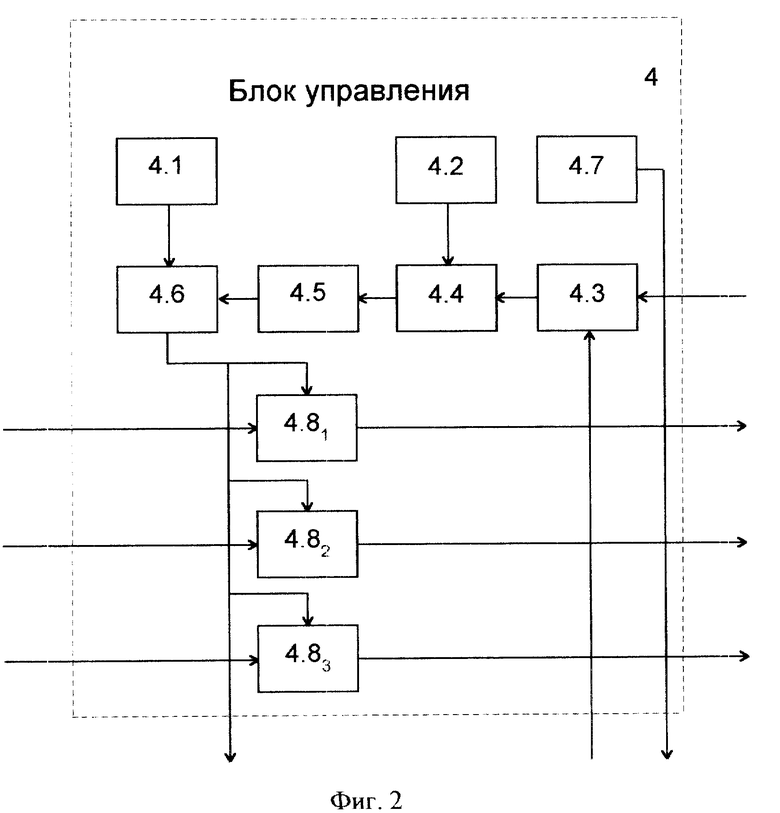

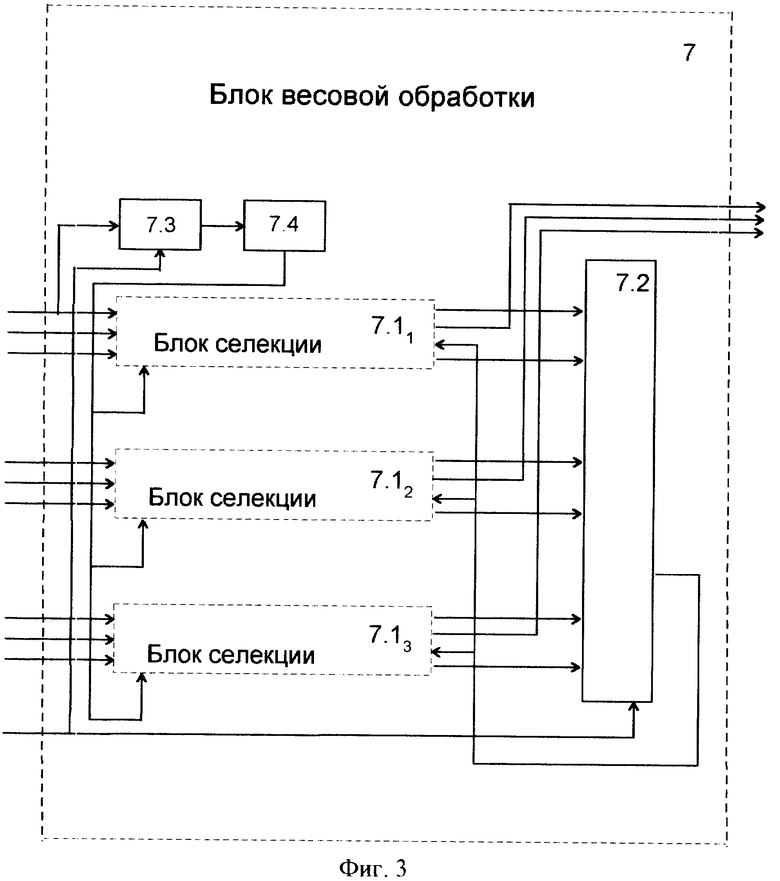

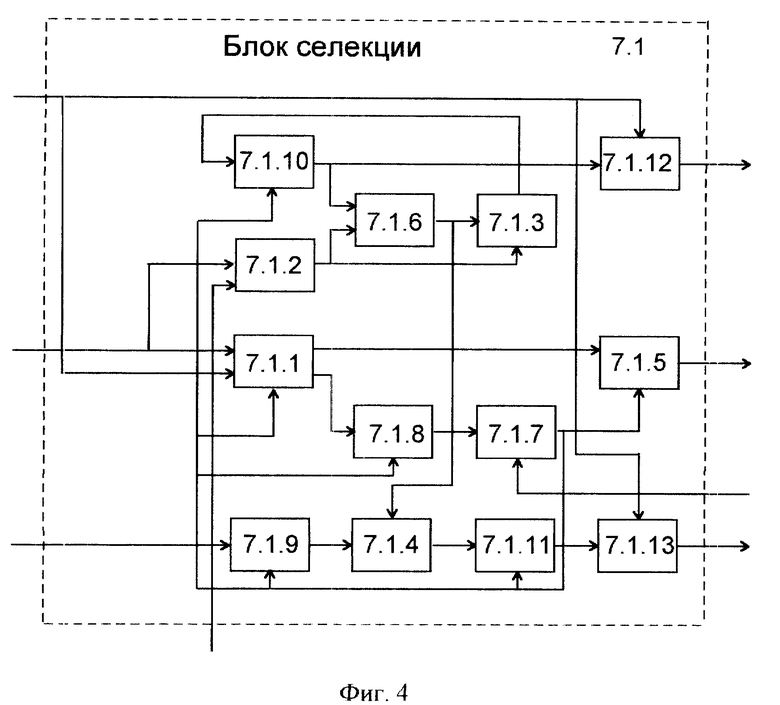

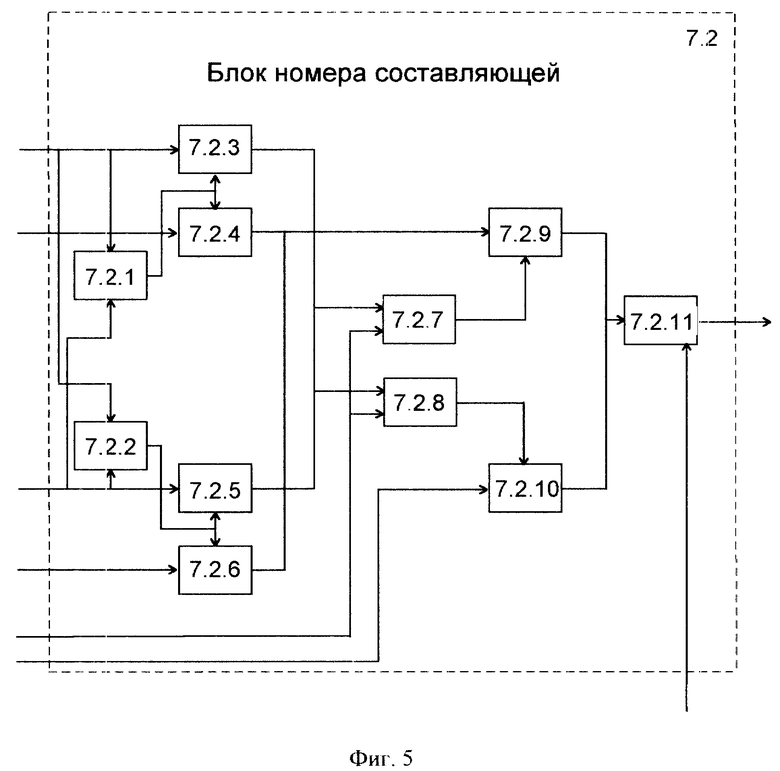

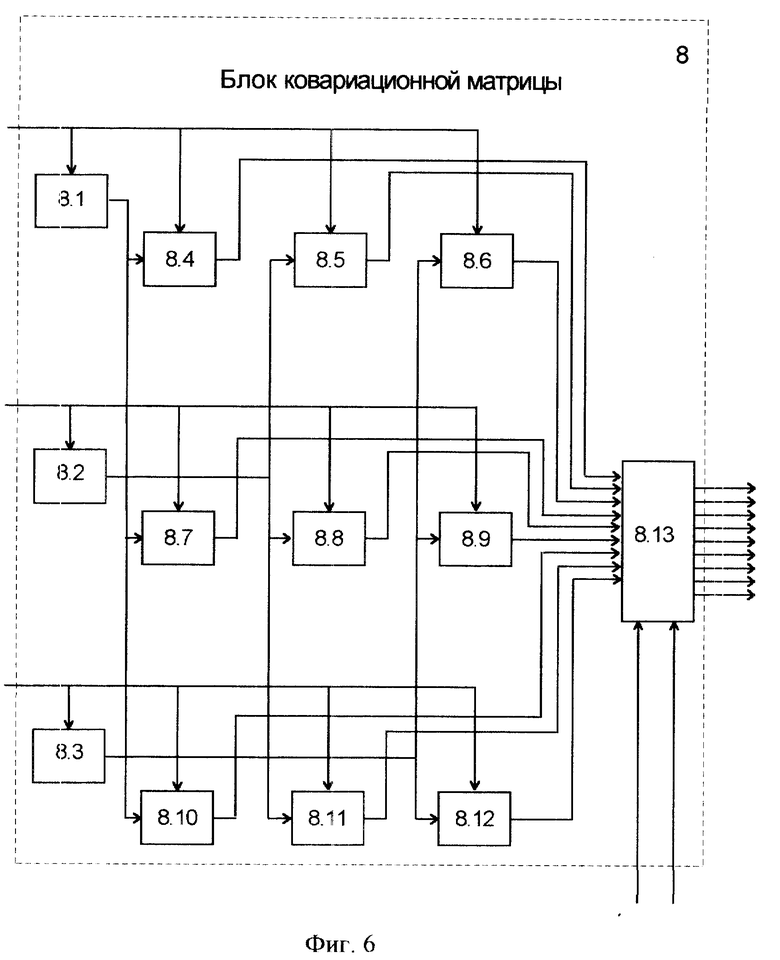

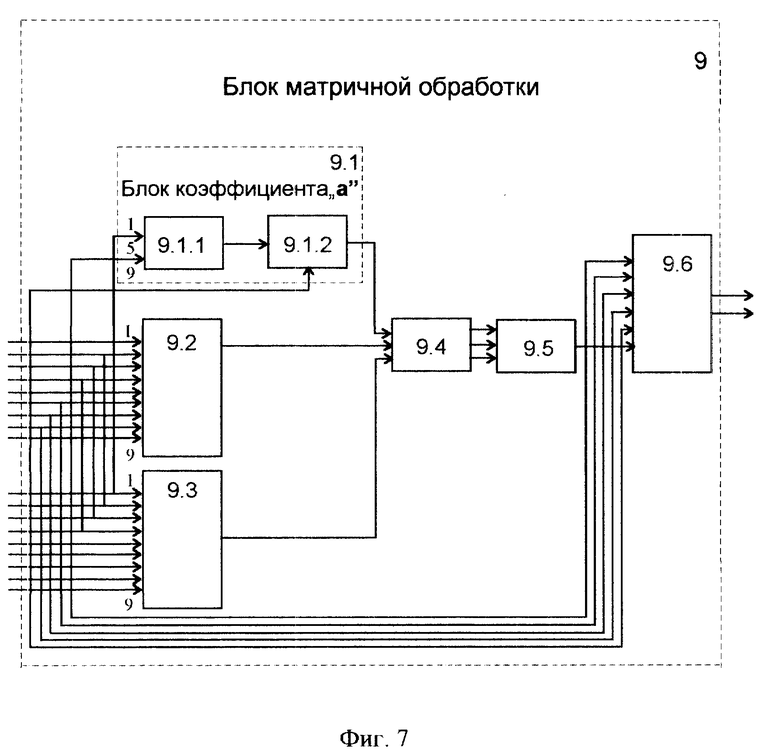

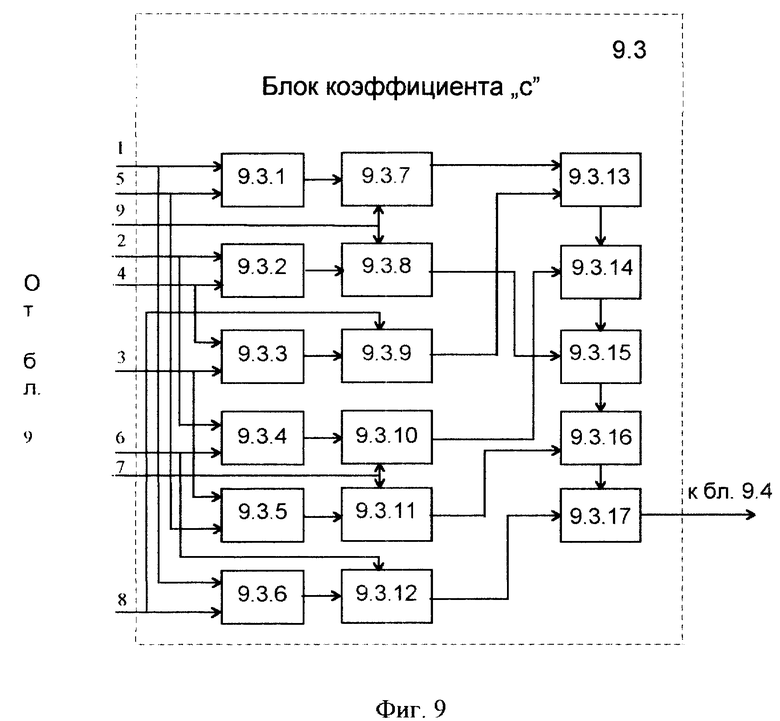

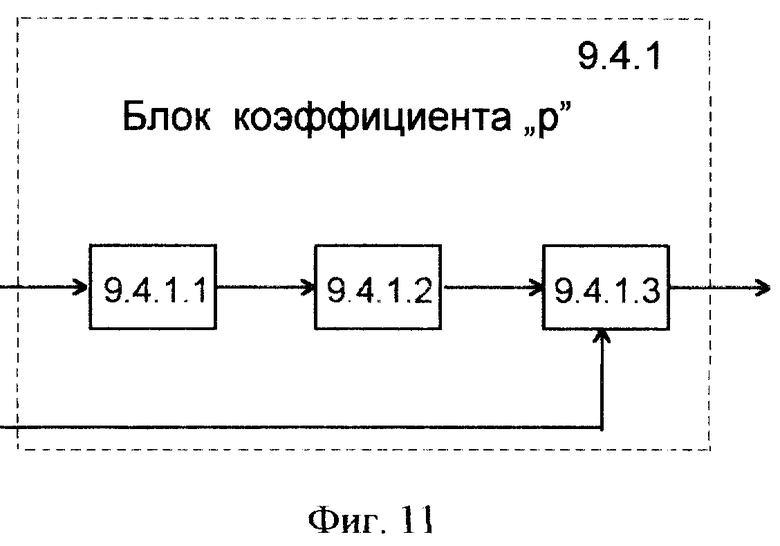

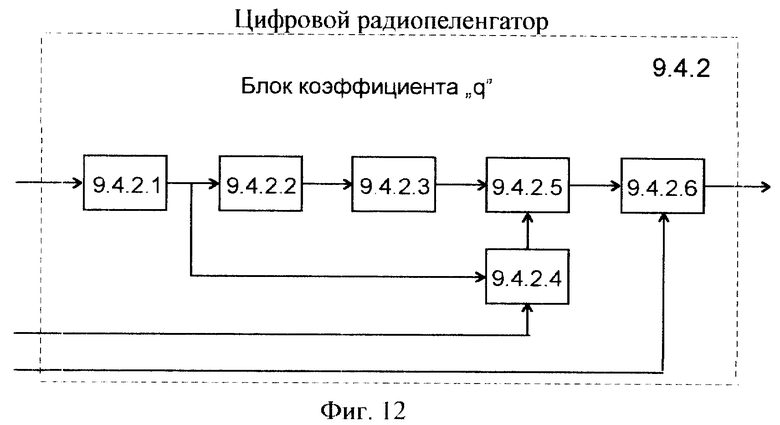

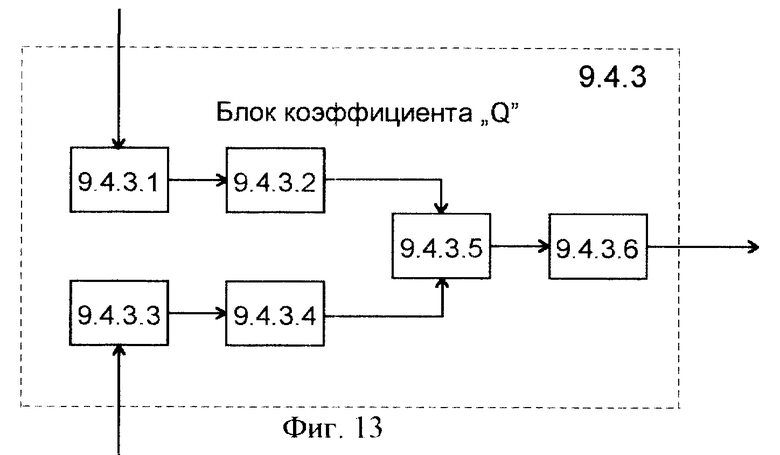

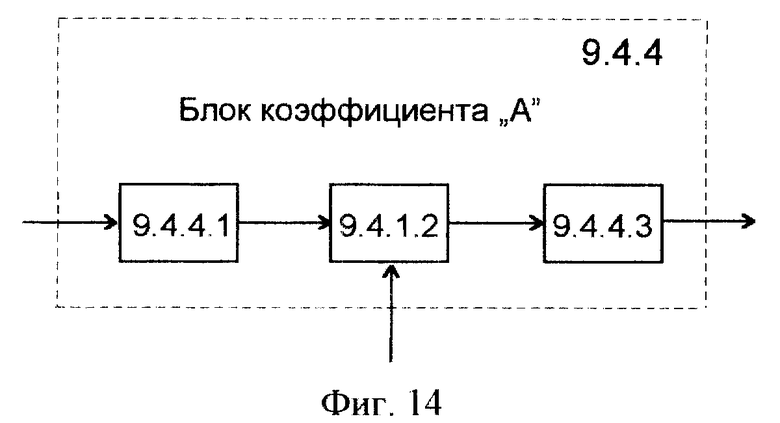

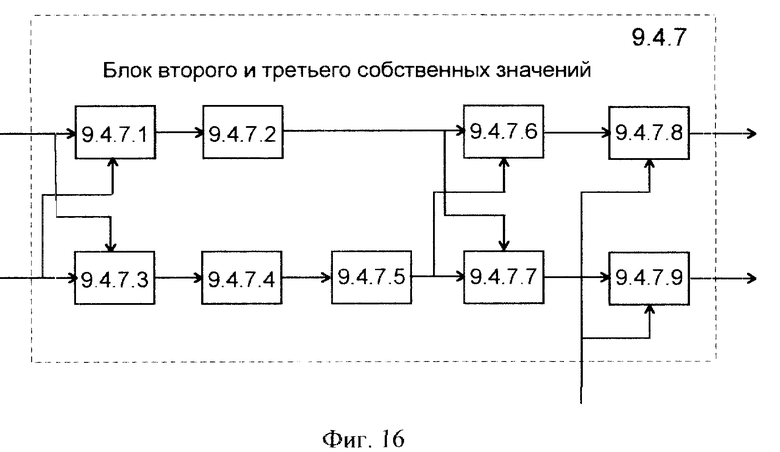

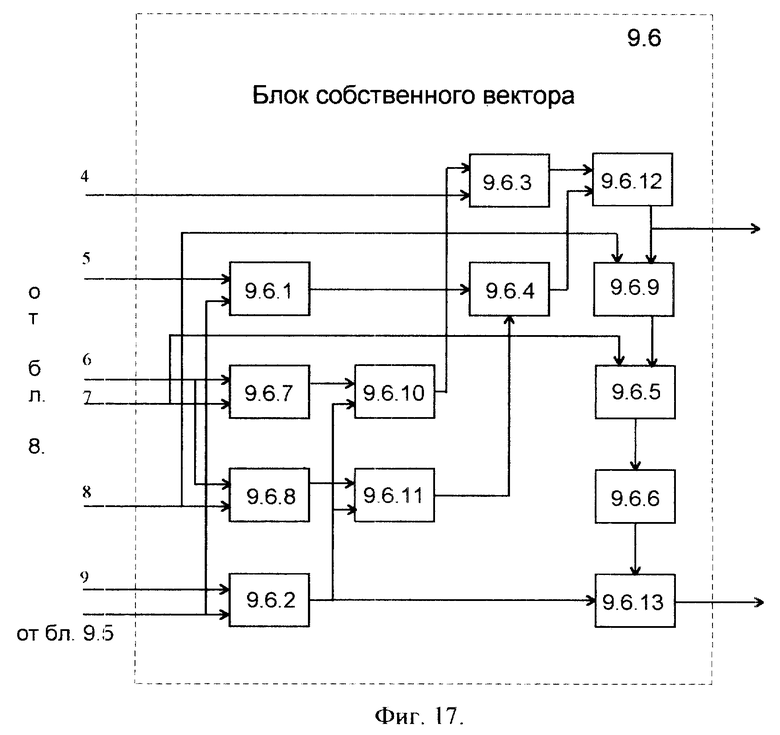

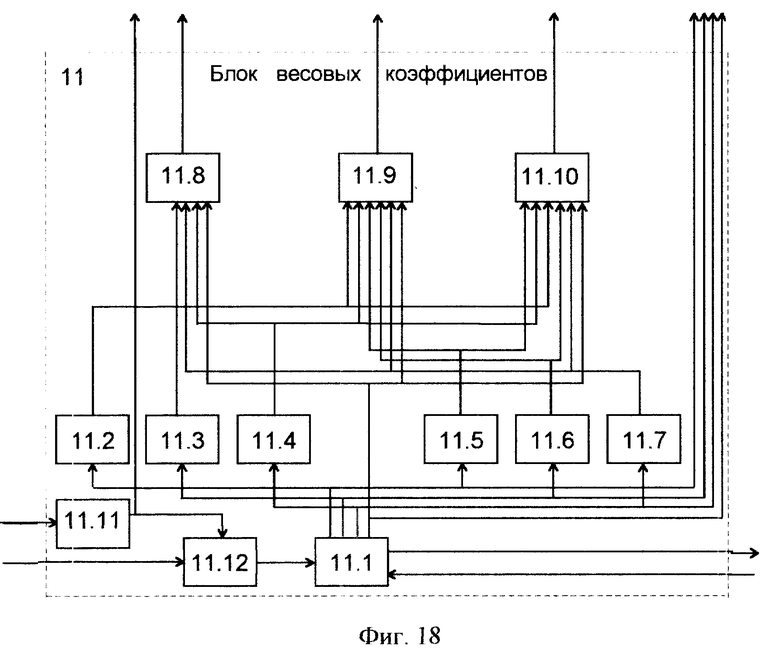

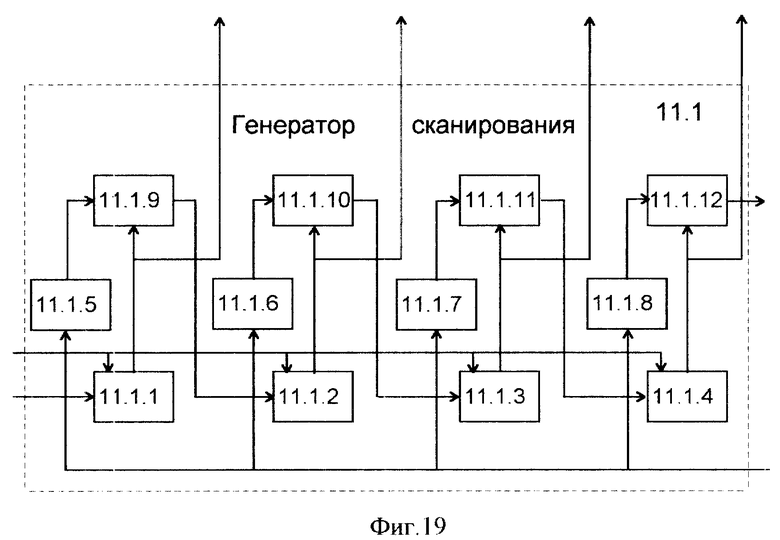

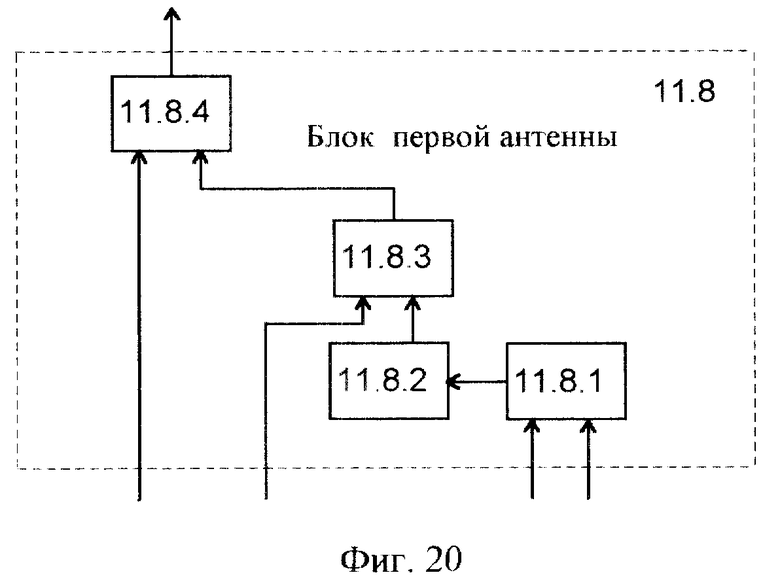

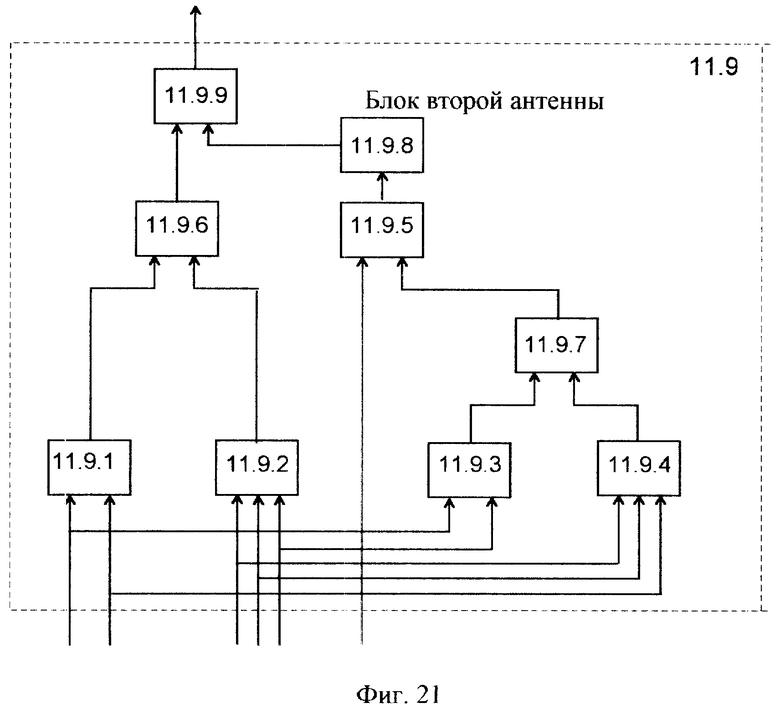

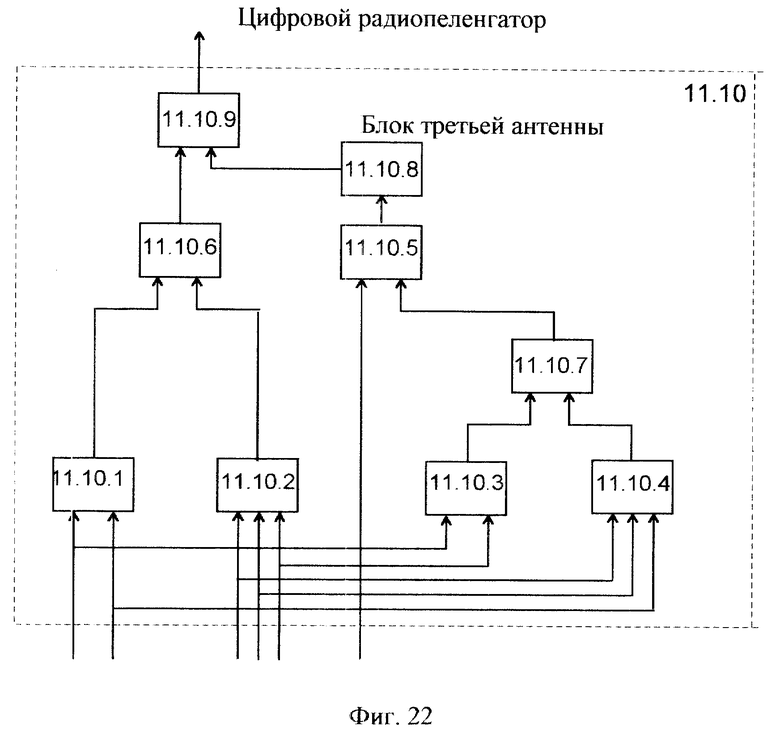

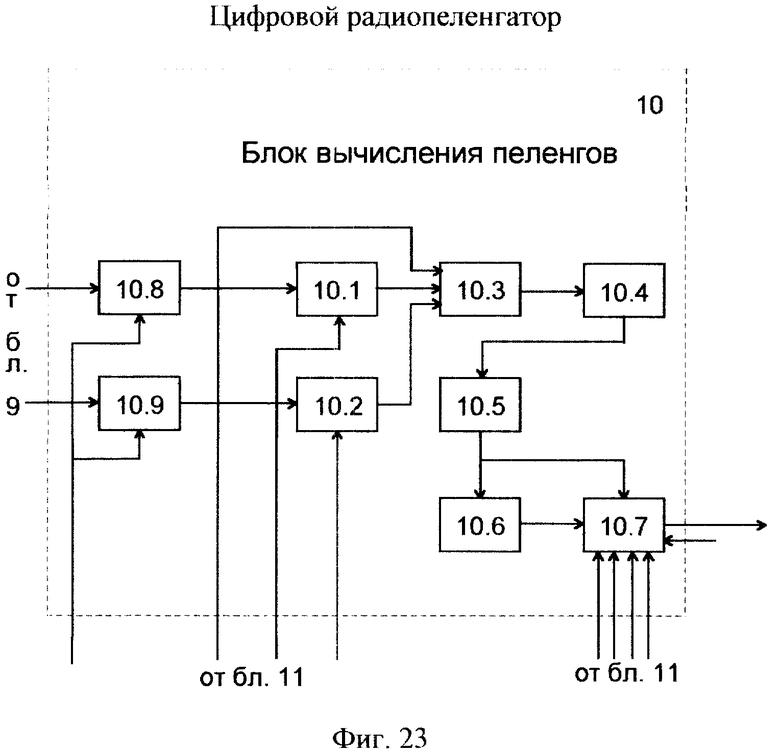

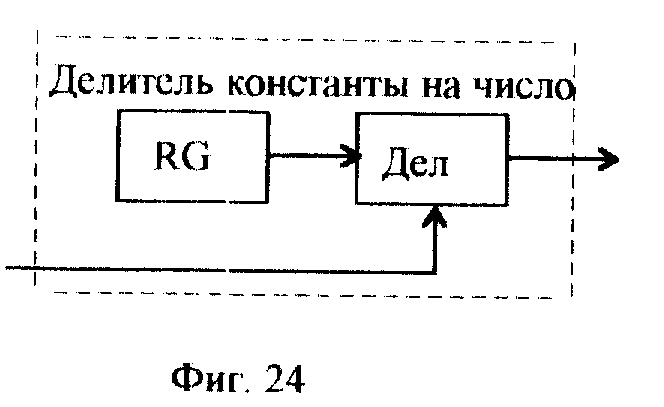

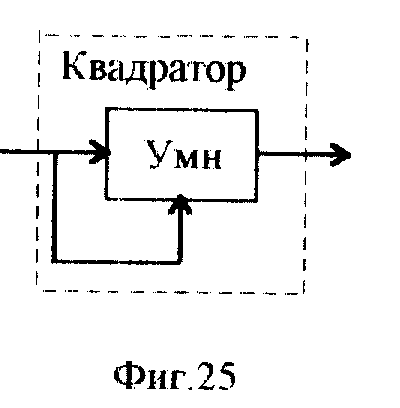

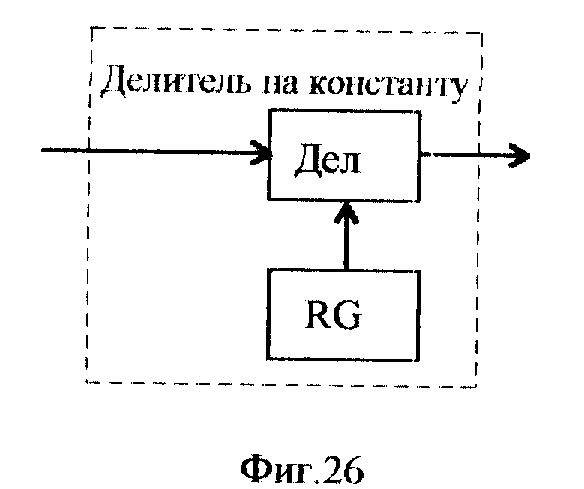

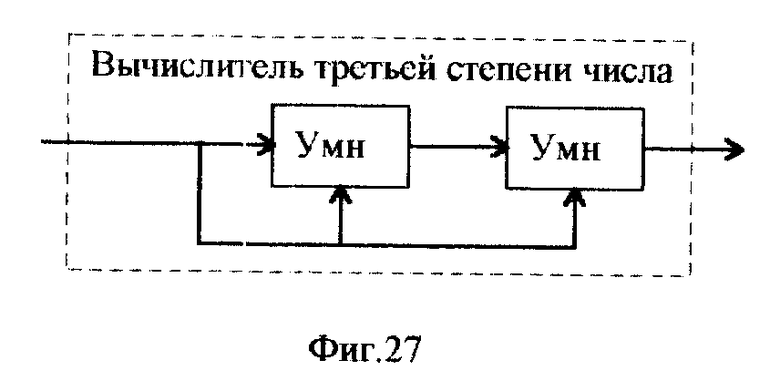

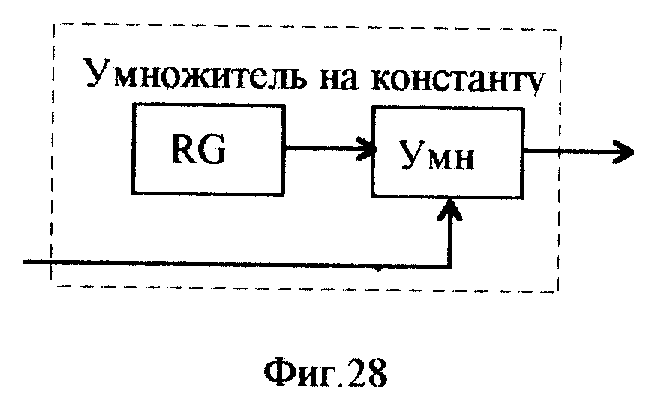

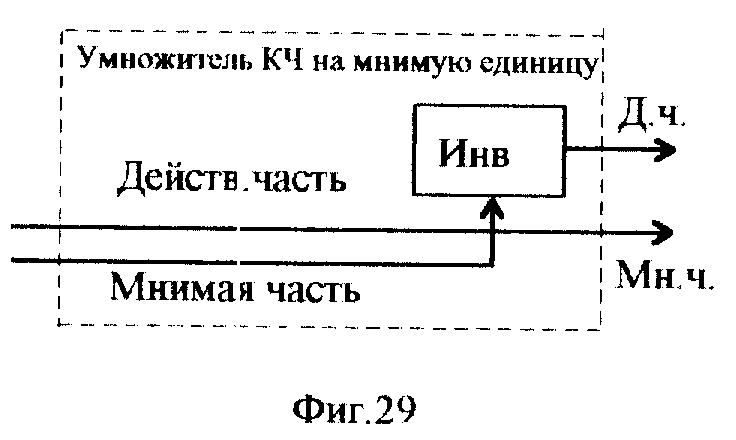

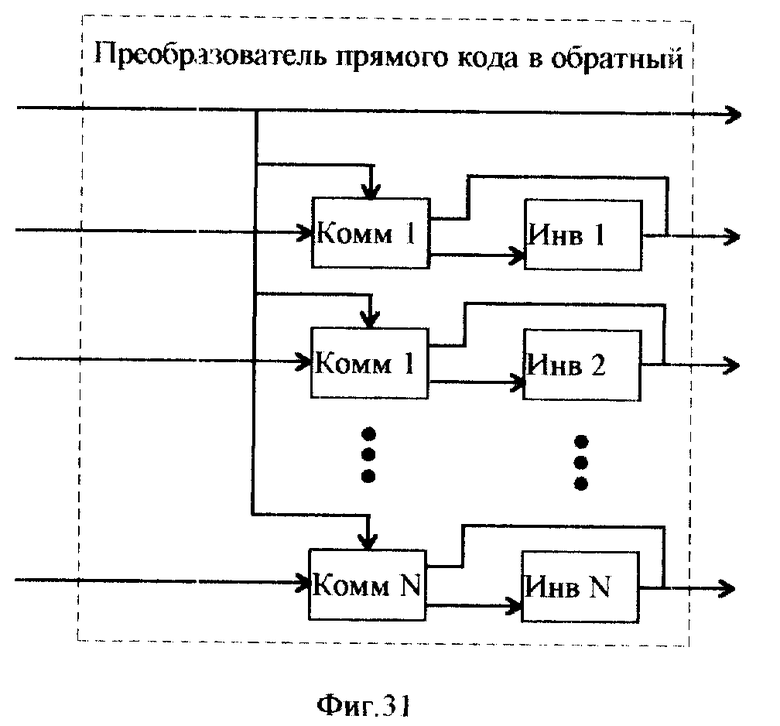

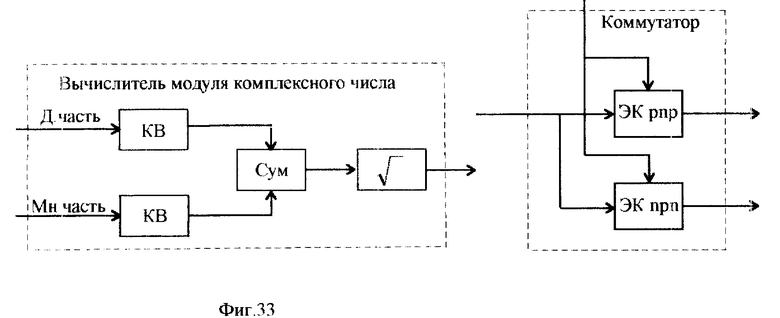

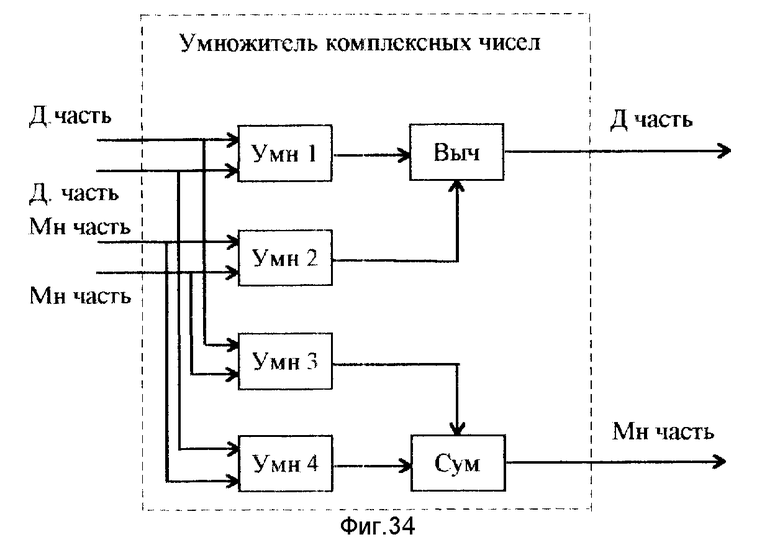

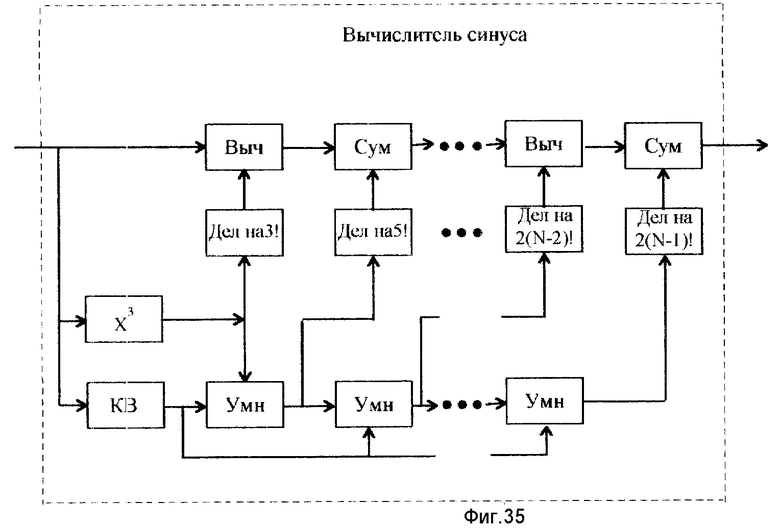

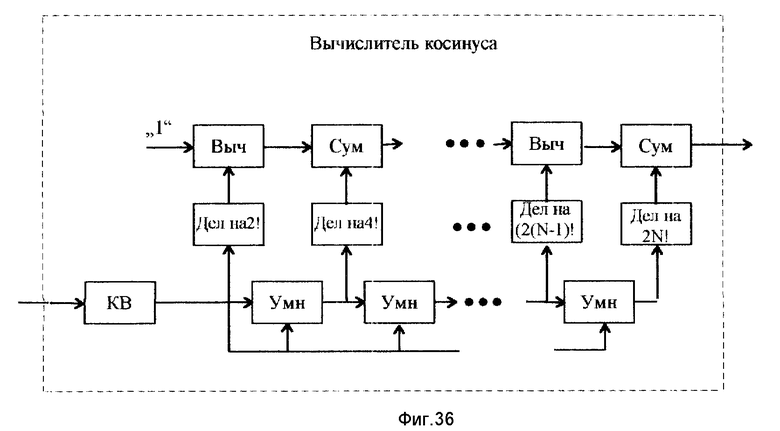

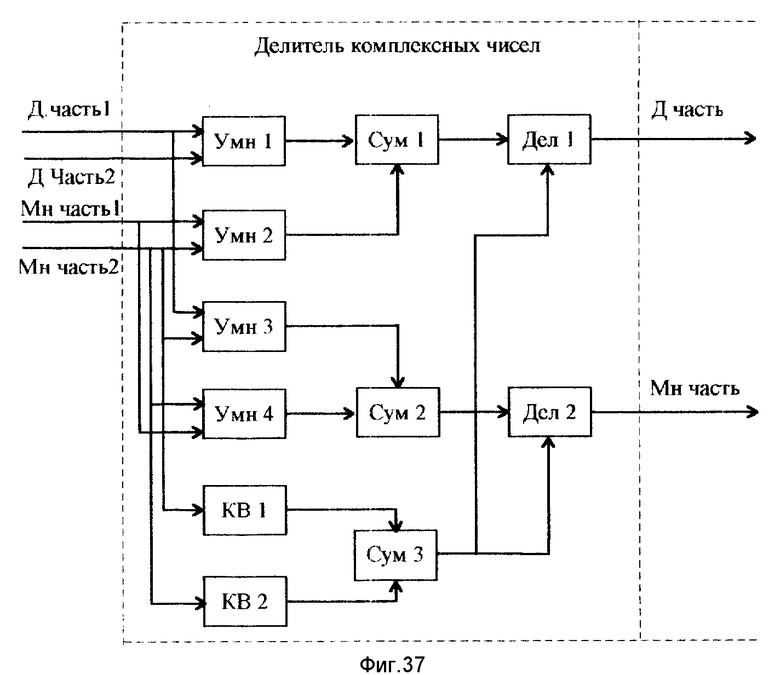

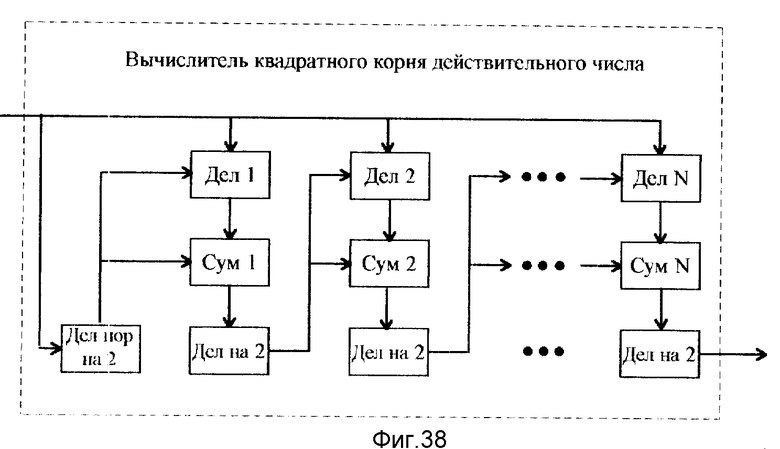

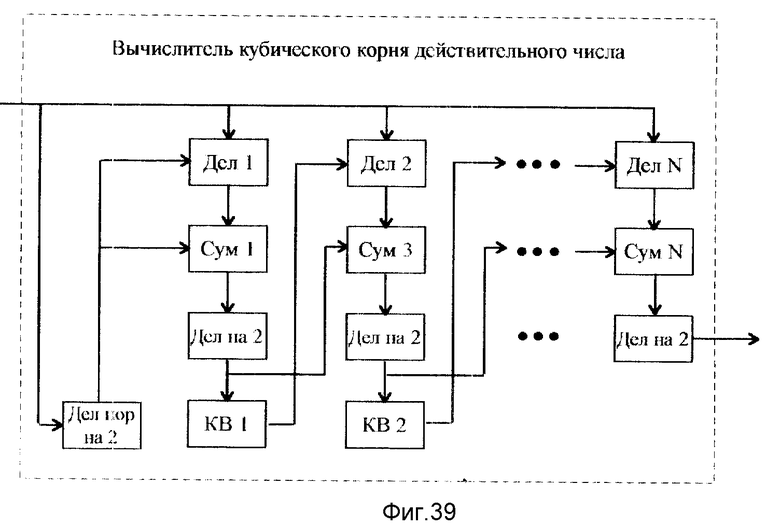

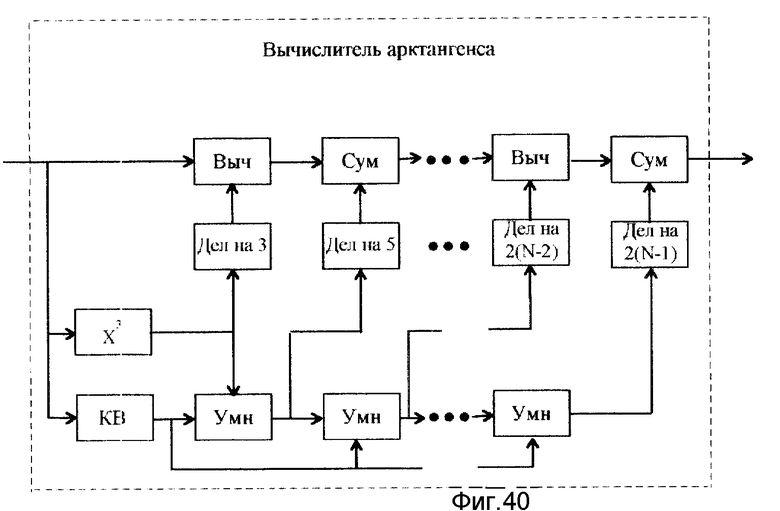

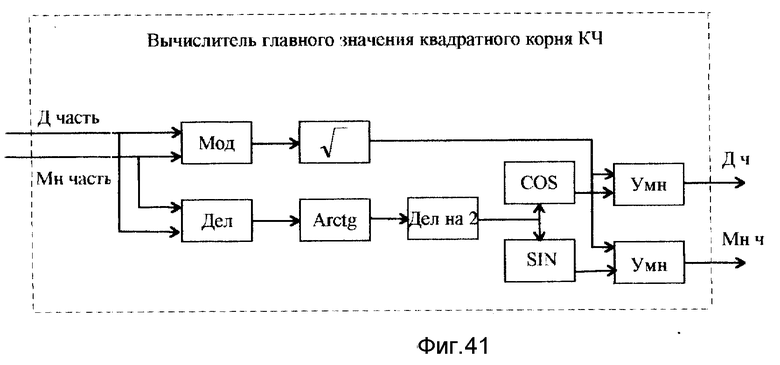

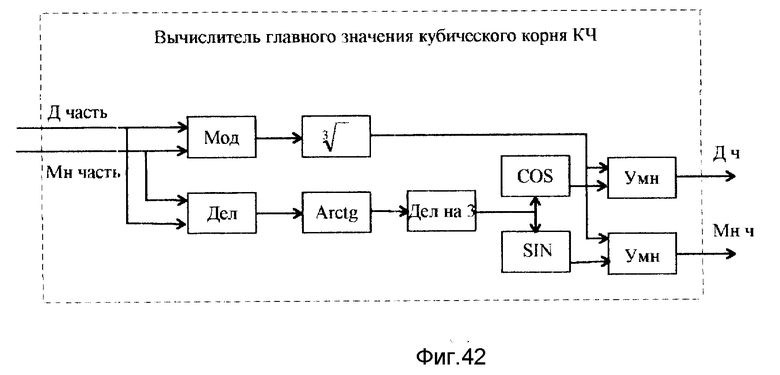

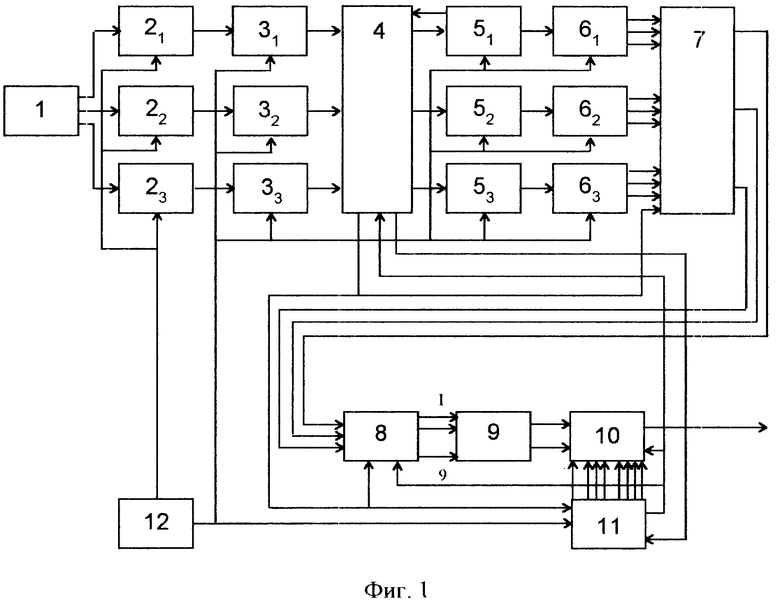

На фиг. 1 показано структурная схема цифрового радиопеленгатора; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема блока весовой обработки; на фиг. 4 - структурная схема блока селекции; на фиг. 5 - структурная схема блока номера составляющей; на фиг. 6 - структурная схема блока ковариационной матрицы; на фиг. 7 - структурная схема блока матричной обработки; на фиг. 8 - структурная схема блока коэффициента "b"; на фиг. 9 - структурная схема блока коэффициента "c"; на фиг. 10 - структурная схема блока характеристического уравнения; на фиг. 11 - структурная схема блока коэффициента "p"; на фиг. 12 - структурная схема блока коэффициента "g"; на фиг. 13 - структурная схема блока коэффициента "Q"; на фиг. 14 - структурная схема блока коэффициента "A"; на фиг. 15 - структурная схема блока коэффициента "B"; на фиг. 16 - структурная схема блока второго и третьего собственных значений; на фиг. 17 - структурная схема блока собственного вектора; на фиг. 18 - структурная схема блока весовых коэффициентов; на фиг. 20 - структурная схема первой антенны; на фиг. 21 - структурная схема блока второй антенны; на фиг. 22 - структурная схема блока третьей антенны; на фиг. 23 - структурная схема блока вычисления пеленгов; на фиг. 24 - пример реализации делителя константы на число; на фиг. 25 - пример реализации квадратора; на фиг. 26 - пример реализации делителя на константу; на фиг. 27 - пример реализации вычислителя третьей степени числа; на фиг. 28 - пример реализации умножителя на константу; на фиг. 29 - пример реализации умножителя на мнимую единицу; на фиг. 30 - пример реализации сумматора комплексных чисел; на фиг. 31 - пример реализации преобразователя прямого кода в обратный; на фиг. 32 - пример реализации вычитателя; на фиг. 33 - пример реализации вычислителя модуля комплексного числа; на фиг. 34 - пример реализации умножителя комплексных чисел; на фиг. 35 - пример реализации вычислителя синуса; на фиг. 36 - пример реализации вычислителя косинуса; на фиг. 37 - пример реализации делителя комплексных чисел; на фиг. 38 - пример реализации вычислителя квадратного корня действительного числа; на фиг. 39 - пример реализации вычислителя кубического корня действительного числа; на фиг. 40 - пример реализации вычислителя арктангенса; на фиг. 41 - пример реализации вычислителя квадратного корня комплексного числа; на фиг. 42 - пример реализации вычислителя кубического корня комплексного числа.

Заявленный цифровой радиопеленгатор, представленный на фиг. 1, состоит из антенного блока 1, включающего три взаимно ортогональные антенны, например, несимметричный вибратор, установленный на оси пересечения двух ортогональных вертикальных рамочных антенн, первого, второго и третьего радиоприемников 21 - 23, первого, второго и третьего N-канальных аналого-цифровых преобразователей 31 - 33, блока управления 4, первого, второго и третьего буферных накопителей 51- 53, первого, второго и третьего блоков дискретного преобразования Фурье 61-63, блока весовой обработки 7, блока ковариационной матрицы 8, блока матричной обработки 9, блока вычисления пеленгов 10, блока весовых коэффициентов 11 и блока опорных частот (БОЧ) 12. Сигнальные входы первого, второго и третьего радиоприемников 21 - 23 подключены к соответствующим антеннам антенного блока 1, их гетеродинные входы подключены к гетеродинному выходу блока опорных частот 12, а сигнальные выходы соединены соответственно с сигнальными входами первого, второго и третьего аналого-цифровых преобразователей (АЦП) 31 - 33. Тактовые входы АЦП 33 - 33, буферных накопителей 51-53 и блоков дискретного преобразования Фурье 61 - 63 подключены к выходу тактовой частоты БОЧ 12, а сигнальные выходы АЦП 31 - 33 соединены с соответствующими сигнальными входами блока управления (БУ) 4. Первый, второй и третий сигнальные выходы БУ 4 подключены к входам соответствующих буферных накопителей (БН) 51 - 53 причем синхронизирующий выход первого БН 51 подключен к счетному входу БУ 4. Установочный вход БУ 4 подключен к установочному выходу блока весовых коэффициентов 11. Запускающий (управляющий) выход БУ 4 соединен с управляющими входами блока весовой обработки 7, блока ковариационной матрицы (БКМ) 8 и блока весовых коэффициентов 11, а выход "Разрешение" БУ 4 подключен к одноименному входу блока весовых коэффициентов 11. Сигнальные выходы БН 51-53 подключены к входам соответственно первого, второго и третьего блоков дискретного преобразования Фурье (ДПФ) 61-63, синхронизирующий, сигнальный и тактовый выходы которых соединены с соответствующими входами блока весовой обработки (БВО) 7. Его первый, второй и третий выходы подключены соответственно к первому, второму и третьему входам БКМ 8, установочный вход которого подключен к установочному выходу блока весовых коэффициентов 11, в сигнальные выходы БКМ 8 соединены с входами блока матричной обработки (БМО) 9. Первый и второй выходы БМО 9 подключены к сигнальным входам блока вычисления пеленга (БПВ) 10, три взвешивающих, четыре информационных входа которого соединены с соответствующими выходами блока весовых коэффициентов (БВК) 11, тактовый вход которого соединен с выходом тактовой частоты БОЧ 12. Синхронизирующий и установочный выходы БВК 11 подключены к соответствующим входам БВП 10, выход которого является выходом цифрового радиопеленгатора.

Блок управления 4, показанный на фиг. 2, предназначенный для управления работой радиопеленгатора БУ, включает кнопку "Измерение" 4.1, датчик количества реализаций спектра 4.2, счетчик 4.3, компаратор 4.4, элемент задержки 4.5, триггер 4.6, датчик "Разрешение" 4.7 и первый, второй и третий электронные ключи (ЭК) 4.81 - 4.83. Выход датчика "Разрешение" 4.7 является одноименным выходом блока управления 4. Счетный вход счетчика 4.3 подключен к синтезирующему выходу первого БН 51, установочный вход соединен с управляющим выходом БКВ 11, а выход соединен с первым входом компаратора 4.4, второй вход которого подключен к выходу датчика количества реализаций спектра 4.2. Выход компаратора 4.4 через элемент задержки 4.5 соединен с входом R RS-триггера 4.6, вход S которого подключен к кнопке "Измерение" 4.1. Выход триггера 4.6 соединен с управляющими входами первого, второго и третьего электронных ключей 4.81 - 4.83. Их сигнальные входы являются сигнальными входами БУ 4 и соединены с выходами первого, второго и третьего АЦП 31 - 33, а выходы являются сигнальными выходами БУ 4 и подключены к сигнальным входам соответственно первого, второго и третьего БН 51 - 53. Кроме того, выход триггера 4.6 является запускающим выходом БУ 4.

Блок весовой обработки (БВО) предназначен для выделения максимальной составляющей из первой реализации спектра в трех каналах и последующего выделения этой составляющей в каждом канале в течение всего цикла накопления сигнала. Схема БВО 7 показана на фиг. 3 и состоит из первого, второго и третьего блока селекции 7.11 - 7.13, блока номера составляющей 7.2, счетчика 7.3 и компаратора 7.4. Первый вход каждого блока селекции 7.1 является соответствующим синхронизирующим входом БВО 7 и соединен с синхронизирующим выходом соответствующего блока ДПФ 6, второй его вход является соответствующим сигнальным входом БВО 7 и подключен к сигнальному выходу соответствующего блока ДПФ 6, а третий вход является соответствующим тактовым входом БВО 7 и соединен с тактовым выходом соответствующего блока ДПФ 6, четвертый вход подключен к выходу компаратора 7.4, вход которого соединен с выходом счетчика 7.3, сигнальный выход которого подключен к синхронизирующему выходу первого блока ДПФ 61, а установочный вход соединен с запускающим входом БУ 4. Пятый вход каждого блока селекции 7.1 соединен с информационным выходом номера составляющей 7.2. Амплитудные выходы блоков селекции 7.1 подключены соответственно к первому, второму и третьему амплитудным входам блока 7.2, сигнальные выходы блоков селекции 7.1 являются соответствующими выходами БВО 7, а информационные выходы блоков селекции 7.1 соединены соответственно с первым, вторым и третьим информационными входами блока номера составляющей 7.2, управляющий вход которого подключен к запускающему выходу БУ 4.

Блок селекции 7.1 предназначен для поиска максимальной спектральной составляющей и определения ее номера в каждом канале обработки, выдачи результата поиска в блок номера составляющей 7.2 и на основе результатов работы блока номера составляющей 7.2 выделения из спектра сигнала составляющей с номером, соответствующем максимальной составляющей из первой реализации спектра во всех каналах в течение цикла накопления сигнала. Структурная схема блока селекции 7.1 представлена на фиг. 4. Она состоит из буферного накопителя 7.1.1, первого и второго компараторов 7.1.6 и 7.1.7, шести электронных ключей (ЭК) 7.1.2 - 7.1.5 и 7.1.12 - 7.1.13, первого и второго счетчиков 7.1.8 и 7.1.9 и первого и второго регистров 7.1.10 и 7.1.11. Сигнальные входы буферного накопителя 7.1.1 и ЭК 7.1.2 соединены с сигнальным выходом соответствующего блока ДПФ 6, управляющие входы которых подключены к синхронизирующему выходу соответствующего блока ДПФ 6. Управляющий вход ЭК 7.1.2 подключен к выходу компаратора 7.4, а выход 7.1.2 подключен ко второму входу первого компаратора 7.1.6 и сигнальному входу ЭК 7.1.3. Первый вход компаратора 7.1.6 соединен с выходом первого регистра 7.1.10, а выход подключен к управляющему входу ЭК 7.1.3 и ЭК 7.1.4. Выход ЭК 7.1.3 соединен с сигнальным входом первого регистра 7.1.10, выход которого подключен также к сигнальному входу ЭК 7.1.12. Его управляющий вход соединен с синхронизирующим выходом соответствующего блока ДПФ 6, а выход ЭК 7.1.12 является амплитудным выходом блока 7.1. Счетный вход второго счетчика 7.1.9 является тактовым входом БВО 7 и подключен к тактовому выходу соответствующего блока ДПФ 6, а выход соединен с сигнальным входом ЭК 7.1.4, выход которого подключен к входу второго регистра 7.1.11. Его выход соединен с сигнальным входом ЭК 7.1.13, управляющий вход которого соединен с синхронизирующим выходом соответствующего блока ДПФ 6, а выход является информационным выходом блока селекции 7.1. Тактовый выход БН 7.1.1 подключен к входу первого счетчика 7.1.8, выход которого соединен с первым входом второго компаратора 7.1.7, второй вход которого подключен к выходу блока номера составляющей 7.2, а выход соединен с управляющим входом ЭК 7.1.5, установленными входами первого и второго регистров 7.1.10 и 7.1.11, первого и второго счетчиков 7.1.8 и 7.1.9 и БН 7.1.1. Сигнальный вход ЭК 7.1.5 подключен к сигнальному выходу БН 7.1.1, а выход является сигнальным выходом блока селекции 7.1.

Блок номера составляющей 7.2 предназначен для определения номера максимальной составляющей спектра из предварительно отобранных в блоках селекции 7.11 - 7.13 максимальных составляющих спектра в каналах. Его структурная схема представлена на фиг. 5 и состоит из первого, второго, третьего и четвертого компараторов 7.2.1, 7.2.2, 7.2.7, 7.2.8, шести ЭК 7.2.3-7.2.6, 7.2.9 и 7.2.10 и регистра 7.2.11. Первые входы первого и второго компараторов 7.2.1 и 7.2.2, а также сигнальный вход ЭК 7.2.3 соединены с амплитудным выходом блока селекции 7.11. Вторые входы первого и второго компараторов 7.2.1 и 7.2.2, а также сигнальный вход ЭК 7.2.5 подключены к амплитудному выходу второго блока селекции 7.12. Выход первого компаратора 7.2.1 соединен с управляющими входами ЭК 7.2.3 и 7.2.4, а выход второго компаратора 7.2.2 подключен к управляющим входам ЭК 7.2.5 и 7.2.6. Сигнальные входы ЭК 7.2.4 и 7.2.6 соединены с информационными выходами соответственно первого 7.11 и второго 7.12 блоков селекции. Выходы ЭК 7.2.3 и 7.2.5 объединены и подключены соответственно к первым входам третьего и четвертого компараторов 7.2.7 и 7.2.8. Выходы ЭК 7.2.4 и 7.2.6 также объединены и подключены к сигнальному входу ЭК 7.2.9, управляющий вход которого соединен с выходом третьего компаратора 7.2.7. Вторые входы третьего и четвертого компараторов 7.2.7 и 7.2.8 соединены с амплитудным выходом третьего блока селекции 7.13, информационный выход которого подключен к сигнальному входу ЭК 7.2.10. Его управляющий вход соединен с выходом четвертого компаратора 7.2.8. Выходы ЭК 7.2.9 и 7.2.10 объединены и подключены к входу регистра 7.2.11, установочный вход которого соединен с запускающим выходом БУ 4, а выход является выходом блока номера составляющей 7.2.

Блок ковариационной матрицы (БКМ) 8 показан на фиг. 6 и предназначен для формирования из отсчетов спектра сигналов матрицы ковариации. БКМ состоит из первого, второго и третьего инверторов мнимой части комплексного числа 8.1-8.3, девяти умножителей 8.4-8.12 и сумматора-накопителя 8.13. Выход первого инвертора мнимой части комплексного числа 8.1 и первые входы умножителей (Умн) 8.4-8.6 соединены с первым выходом БВО 7, а вторые входы Умн 8.4-8.6 подключены к выходам соответственно первого, второго и третьего инверторов мнимой части комплексного числа 8.1-8.3. Выходы Умн 8.4-8.6 соединены соответственно с первым, вторым и третьим сигнальными входами сумматора-накопителя 8.13. Вход второго инвертора мнимой части комплексного числа 8.2 и первые входы Умн 8.7-8.9 соединены с вторым выходом БВО 7, вторые входы Умн 8.7-8.9 подключены к выходам соответственно первого, второго и третьего инверторов мнимой части комплексного числа 8.1-8.3, а выходы Умн 8.7-8.9 соединены соответственно с четвертым, пятым и шестым сигнальными входами сумматора-накопителя 8.13. Вход третьего инвертора 8.3 мнимой части комплексного числа и первые входы Умн 8.10-8.12 соединены с третьим выходом БВО 7, вторые входы Умн 8.10-8.12 подключены к выходам соответственно первого, второго и третьего инверторов мнимой части комплексного числа 8.1-8.3, а выходы Умн 8.10-8.12 соединены соответственно с седьмым, восьмым и девятым сигнальными входами сумматора-накопителя 8.13. Управляющий вход сумматора-накопителя 8.13 соединен с запускающим выходом БК 4, а установочный вход - с установочным выходом БВК 11, причем девять выходов сумматора-накопителя 8.13 являются выходами БКМ 8.

Блок матричной обработки (БМО) 9 предназначен для вычисления собственного вектора (СВ) ковариационной матрицы (КМ), соответствующего минимальному собственному значению (СЗ) при условии, что его первая координата равна 1. БМО (фиг. 7) включает в себя блок коэффициента "а" 9.1 в составе первого и второго сумматоров (Сум) 9.1.1 и 9.1.2, блок коэффициента "b" 9.2, блок коэффициента "с" 9.3, блок характеристического уравнения 9.4, компаратор 9.5 и блок СВ 9.6. Первый и второй входы первого Сум 9.1.1 блока коэффициента "а" 9.1 подключены к первому и пятому выходам БВК 8, а выход подключен к первому входу второго Сум 9.1.2, второй вход которого подключен к девятому выходу БКМ 8. Выход второго Сум 9.1.2 является выходом блока вычисления коэффициента "а" 9.1 и подключен к первому входу блока характеристического уравнения 9.4. второй и третий входы которого соединены с выходами соответственно блока коэффициента "b" 9.2 и блока коэффициента "c" 9.3, имеющих по девять входов и подключенных к соответствующим девяти выходам БКМ 8. Первый, второй и третий выходы блока характеристического уравнения 9.4 соединены с соответствующими входами компаратора 9.5, выход которого подключен к входу собственного значения блока СВ 9.6, первый, второй, третий, четвертый, пятый и шестой входы которого соединены соответственно с четвертым, пятым, шестым, седьмым, восьмым и девятым выходами БКМ 8, а первый и второй выходы являться выходами блока матричной обработки.

Блок вычисления коэффициента "b" 9.2 предназначен для расчета величины коэффициента "b" и представлен на фиг. 8. В его состав входят пять Умн 9.2.1-9.2.6, четыре Сум 9.2.7-9.2.10 и вычитатель (Выч) 9.2.11. Входы Умн являются входами блока коэффициента "b" и соединены с выходами БКМ 8 следующим образом: первый и второй входы Умн 9.2.1 соединены соответственно с первым и пятым, первый и второй входы Умн 9.2.2 соединены соответственно с первым и девятым, первый и второй входы Умн 9.2.3 соединены соответственно с пятым и девятым, первый и второй входы Умн 9.2.4 соединены соответственно с вторым и четвертым, первый и второй входы Умн 9.2.5 соединены соответственно с третьим и седьмым, первый и второй входы Умн 9.2.6 соединены соответственно с шестым и восьмым выходами БКМ 8. Выходы Умн 9.2.1 и 9.2.2 подключены к первому и второму входам Сум 9.2.7, выход которого соединен с первым входом Сум 9.2.10, второй вход которого подключен к выходу Умн 9.2.3, а выход подключен ко второму входу Выч 9.2.11. Его первый вход соединен с выходом Сум 9.2.9, первый вход которого подключен к выходу Сум 9.2.8, первый вход которого соединен с выходом Умн 9.2.4, а второй вход подключен к выходу Умн 9.2.5, причем второй вход Сум 9.2.9 соединен с выходом Умн 9.2.6, а выход Выч является выходом блока коэффициента "b".

Блок коэффициента "c" 9.3 предназначен для расчета величины свободного члена характеристического уравнения и представлен на фиг. 9. Он состоит из двенадцати Умн 9.3.1-9.3.12, первого и второго Сум 9.3.13 и 9.3.14, первого, второго и третьего Выч 9.3.15, 9.3.16, 9.3.17. Первый вход Умн 9.3.1. подключен к первому выходу БКМ 8, второй вход соединен с пятым выходом БКМ 8, а выход подключен к первому входу Умн 9.3.7, второй вход которого соединен с девятым выходом БКМ 8, а выход подключен к первому входу Сум 9.3.13. Его выход подключен к первому входу Сум 9.3.14, а второй вход Сум 9.3.13 соединен с выходом Умн 9.3.9. Первый вход Умн 9.3.9 подключен к выходу Умн 9.3.3, а второй вход соединен с восьмым выходом БКМ 8, причем первый вход Умн 9.3.3 подключен к четвертому выходу БКМ 8, а второй его вход соединен с третьим выходом БКМ 8. Первый и второй входы Умн 9.3.4 подключены соответственно к второму и шестому выходам БКМ 8, а выход подключен к первому входу Умн 9.3.10, второй вход которого соединен с седьмым выходом БКМ 8. Его выход подключен ко второму входу Сум 9.3.14, выход которого соединен с первым входом Выч 9.3.15, выход которого подключен к первому входу Выч 9.3.16, а второй вход Выч 9.3.15 подключен к выходу Умн 9.3.8. Его первый вход соединен с выходом Умн 9.3.2, а второй вход подключен к девятому выходу БКМ 8, причем первый вход Умн 9.3.2 подключен ко второму выходу БКМ 8, а второй его вход соединен с четвертым выходом БКМ 8. Первый вход Умн 9.3.5. подключен к третьему выходу БКМ 8, второй его вход соединен с пятым выходом БКМ 8, а выход подключен к первому входу Умн 9.3.11, второй вход которого соединен с седьмым выходом БКМ 8, а его выход подключен ко второму входу Выч 9.3.16. Его выход соединен с первым входом Выч 9.3.17, второй вход которого подключен к выходу Умн 9.3.12, первый вход которого соединен с выходом Умн 9.3.6, а второй вход подключен к шестому выходу БКМ 8. Первый вход Умн 9.3.6 соединен с первым выходом БКМ 8, его второй вход подключен к восьмому выходу БКМ 8, а выход Выч.9.3.17 является выходом блока коэффициента "с".

Блок характеристического уравнения 9.4 предназначен для нахождения С3 КМ. Его структурная схема (фиг. 10) включает блоки коэффициента "p" 9.4.1, коэффициента "q" 9.4.2. коэффициента "Q" 9.4.3, коэффициента "А" 9.4.4, коэффициента "B" 9.4.5. Сум 9.4.6, второго и третьего C3 9.4.7, делитель (Дел) на три 9.4.8 и Выч 9.4.9. Первый вход блока коэффициента "p" 9.4.1 и вход Дел на три 9.4.8 подключены к выходу блока коэффициента "а", второй вход блока коэффициента "p" соединен с выходом блока коэффициента "b" 9.2. Его выход подключен к первому входу блока коэффициента "Q" 9.4.3, второй вход которого соединен с выходом блока коэффициента "q"9.4.2. Его первый вход подключен к выходу блока коэффициента "а", второй вход соединен с выходом блока коэффициента "b"9.2., а третий вход подключен к выходу блока коэффициента "с" 9.3. Выход блока коэффициента "Q" 9.4.3 соединен с первыми входами блоков коэффициентов "А" 9.4.4 и "В" 9.4.5, вторые входы которых подключены к выходу блока коэффициента "q" 9.4.2. Выходы блоков коэффициентов "А" 9.4.4.и "В" 9.4.5 подключены соответственно к первым и вторым входам Сум 9.4.6 и блока второго и третьего С3 9.4.7, третий вход которого соединен с выходом Дел на три 9.4.8. Выход Сум 9.4.6 соединен с первым входом Выч 9.4.9, второй вход которого подключен к выходу Дел на три 9.4.8. Выход Выч 9.4.9, первый и второй выходы блока второго и третьего С3 9.4.7 являются соответственно первым, вторым и третьим выходами блока характеристического уравнения 9.4.

Блок коэффициента "р" 9.4.1 предназначен для получения вспомогательной величины при решении характеристического уравнения. Структурная схема блока (фиг. 11) состоит из квадратора 9.4.1.1, Дел на 3.9.4.1.2 и Выч 9.4.1.3. Вход квадратора 9.4.1.1 подключен к выходу блока 9.1, а выход соединен с входом Дел на 3.9.4.1.2, выход которого подключен к первому входу Выч 9.4.1.3, второй вход которого соединен с выходом блока 9.2, а выход является выходом блока вычисления коэффициента "p" 9.4.1.

Блок коэффициента "q" 9.4.2. также предназначен для получения вспомогательной величины при решении характеристического уравнения. Структурная схема блока показана на фиг. 12 и состоит из Дел на три 9.4.2.1, вычислителя третьей степени числа (Bx3) 9.4.2.2, Умн на два 9.4.2.3, Умн 9.4.2.4, Выч 9.4.2.5 и Сум 9.4.2.6. Вход Дел на 3.9.4.2.1 подключен к выходу блока 9.1, а выход соединен с входом Bx3 9.4.2.2. Его выход через Умн на 2 9.4.2.3 соединен с первым входом Выч 9.4.2.5, второй вход которого подключен к выходу Умн 9.4.2.4, первый вход которого также соединен с выходом Дел на три 9.4.2.1, а второй вход подключен к выходу блока 9.2. Выход Выч 9.4.2.5 подключен к первому входу Сум 9.4.2.6, второй вход которого соединен с выходом блока 9.3, а выход является выходом блока вычисления коэффициента "q" 9.4.2.

Блок коэффициента "Q" 9.4.3 также предназначен для получения вспомогательной величины при решении характеристического уравнения. Структурная схема блока показана на фиг. 13 и состоит из Дел на три 9.4.3.1, Bx3 9.4.3.2, Дел на два 9.4.3.3, квадратора 9.4.3.4, Сум 9.4.3.5 и вычислителя квадратного корня  9.4.3.6. Вход Дел на три 9.4.3.1 подключен к выходу блока 9.4.1, а выход через Bx39.4.3.2 соединен с первым входом Сум 9.4.3.5, второй вход которого подключен к выходу квадратора 9.4.3.4. Его вход соединен с выходом Дел на два , вход которого подключен к выходу блока 9.4.2. Выход Сум 9.4.3.5 соединен с входом

9.4.3.6. Вход Дел на три 9.4.3.1 подключен к выходу блока 9.4.1, а выход через Bx39.4.3.2 соединен с первым входом Сум 9.4.3.5, второй вход которого подключен к выходу квадратора 9.4.3.4. Его вход соединен с выходом Дел на два , вход которого подключен к выходу блока 9.4.2. Выход Сум 9.4.3.5 соединен с входом  9.4.3.6, выход которого является выходом блока коэффициента "Q" 9.4.3.

9.4.3.6, выход которого является выходом блока коэффициента "Q" 9.4.3.

Блок коэффициента "А" 9.4.4. также предназначен для получения вспомогательной величины при решении характеристического уравнения. Структурная схема блока показана на фиг. 14 и состоит из последовательно соединенных Дел на два 9.4.4.1, Выч 9.4.4.2, и вычислителя кубического корня  9.4.4.3. Вход Дел на 2.9.4.4.1 соединен с выходом блока 9.4.2, первый вход Выч 9.4.4.2 соединен с выходом блока 9.4.3, а выход

9.4.4.3. Вход Дел на 2.9.4.4.1 соединен с выходом блока 9.4.2, первый вход Выч 9.4.4.2 соединен с выходом блока 9.4.3, а выход  9.4.4.4 является выходом блока коэффициента "А" 9.4.4.

9.4.4.4 является выходом блока коэффициента "А" 9.4.4.

Блок коэффициента "В" 9.4.5 также предназначен для получения вспомогательной величины при решении характеристического уравнения. Структурная схема блока показана на фиг. 15 и состоит из последовательно соединенных Дел на два 9.4.5.1. Сум 9.4.5.2, инвертора 9.4.5.3 и  9.4.5.4. Вход Дел на 2 9.4.5.1 соединен с выходом блока 9.4.2, второй вход Сум 9.4.5.2 соединен с выходом блока 9.4.3, а выход

9.4.5.4. Вход Дел на 2 9.4.5.1 соединен с выходом блока 9.4.2, второй вход Сум 9.4.5.2 соединен с выходом блока 9.4.3, а выход  9.4.5.4 является выходом блока коэффициента "А" 9.4.5.

9.4.5.4 является выходом блока коэффициента "А" 9.4.5.

Блок второго и третьего С3 9.4.7 предназначен для нахождения соответствующих корней характеристического уравнения. Структурная схема блока (фиг. 16) состоит из первого Сум 9.4.7.1, Дел на (-2) 9.4.7.2, первого Выч 9.4.7.3, Умн на  9.4.7.4, Умн на мнимую единицу 9.4.7.6, второго, третьего и четвертого Выч 9.4.7.7-9.4.7.9. Первый вход Сум 9.4.7.1 соединен с выходом блока 9.4.4, второй его вход соединен с выходом блока 9.4.5, а выход через Дел на (-2) 9.4.7.2 подключен к первым входам второго Сум 9.4.7.6 и второго Выч 9.4.7.7, вторые входы которых соединены с выходом Умн на мнимую единицу 9.4.7.5. Его вход подключен к выходу Умн на

9.4.7.4, Умн на мнимую единицу 9.4.7.6, второго, третьего и четвертого Выч 9.4.7.7-9.4.7.9. Первый вход Сум 9.4.7.1 соединен с выходом блока 9.4.4, второй его вход соединен с выходом блока 9.4.5, а выход через Дел на (-2) 9.4.7.2 подключен к первым входам второго Сум 9.4.7.6 и второго Выч 9.4.7.7, вторые входы которых соединены с выходом Умн на мнимую единицу 9.4.7.5. Его вход подключен к выходу Умн на  9.4.7.4, вход которого соединен с выходом первого Выч 9.4.7.3, его первый вход подключен к выходу блока 9,4,5, а второй вход соединен с выходом блока 9.4.5. Выходы же вторых Сум 9.4.7.6 и Выч. 9.4.7.7 подключены к первым входам соответственно третьего и четвертого Выч 9.4.7.8 и 9.4.7.9, вторые входы которых соединены с выходом Дел на три 9.4.8, выходы которых являются соответственно первым и вторым выходами блока второго и третьего С3 9.4.7.

9.4.7.4, вход которого соединен с выходом первого Выч 9.4.7.3, его первый вход подключен к выходу блока 9,4,5, а второй вход соединен с выходом блока 9.4.5. Выходы же вторых Сум 9.4.7.6 и Выч. 9.4.7.7 подключены к первым входам соответственно третьего и четвертого Выч 9.4.7.8 и 9.4.7.9, вторые входы которых соединены с выходом Дел на три 9.4.8, выходы которых являются соответственно первым и вторым выходами блока второго и третьего С3 9.4.7.

Блок CB 9.6 предназначен для вычисления второго и третьего элементов CB, соответствующего минимальному (шумовому) С3 при условии, что его первый элемент равен 1. Структурная схема блока представлена на фиг. 17 и включает первый, второй, третий и четвертый Выч 9.6.1-9.6.4, Сум 9.6.5, инвертор 9.6.6, первый, второй и третий Умн 9.6.7-9.6.9 и первый, второй, третий и четвертый Дел 9.6.10 - 9.6.13. Первый вход Выч 9.6.1 подключен к пятому выходу БКМ 8, второй его вход соединен с выходом компаратора 9.5, а выход подключен к первому входу Выч 9.6.4. Его второй вход соединен с выходом Дел 9.6.11, первый вход которого подключен к выходу Умн 9.6.8, первый и второй входы которого соединены соответственно с шестым и восьмым выходами БКМ 8, а второй вход Дел 9.6.11 подключен к выходу Выч 9.6.2. Его первый вход соединен с девятым выходом БКМ 8, второй вход также подключен к выходу компаратора 9.5. Выход Выч 9.6.4 подключен ко второму входу Дел 9.6.12, первый вход которого соединен с выходом Выч 9.6.3, второй вход которого подключен к четвертому выходу БКМ 8, а первый его вход соединен с выходом Дел 9.6.10. Его первый вход подключен к выходу Умн 9.6.7, а второй вход также соединен с выходом Выч 9.6.2. Первый и второй входы Умн 9.6.7 подключены соответственно к шестому и седьмому выходам БКМ 8. Выход Дел 9.6.12 является первым выходом блока собственного вектора 9.6 и, кроме того, подключен ко второму входу Умн 9.6.9, первый вход которого соединен с восьмым выходом БКМ 8, а выход подключен ко второму входу Сум 9.6.5. Его первый вход соединен с седьмым выходом БКМ 8, а выход подключен к инвертору 9.6.6. Его выход подключен к первому входу Дел 9.6.13, второй вход которого также соединен с выходом Дел 9.6.2, а выход является вторым выходом блока собственного вектора 9,6.

Блок весовых коэффициентов 11 предназначен для моделирования вектора, ортогонального вектору ковариационной матрицы и вывода значений углов, соответствующих сформированному вектору. Структурная схема БВК приведена на фиг. 18 и состоит из генератора сканирования (ГС) 11.1, первого, второго и третьего блоков вычисления косинуса (В cos(x) 11.2 -11.4, первого, второго и третьего блоков вычисления синуса (B sin(x) 11,5-11,7 и блоков первой, второй и третьей антенн 11.8, 11.9, 11.10, элемента задержки 11.11 и ЭК 11.12. Сигнальный вход ЭК 11.12 подключен к выходу тактовой частоты БОЧ 12, его управляющий вход соединен с выходом элемента задержки 11.11, являющегося также синхронизирующим выходом БВК 11, вход которого соединен с запускающим выходом БУ 4. Тактовый вход ГС 11.1 подключен к выходу ЭК 11.12, а вход "Разрешение" соединен с соответствующим выходом БУ4, первый, второй и третий информационные выходы ГС 11.1 соединены с входами соответствующих B sin(x) 11.5 - 11.7 и B cos(x) 11.2 - 11.4 и кроме того, являются соответствующими информационными выходами БВК 11, его четвертый информационный выход подключен к соответствующим входам блоков первой, второй и третьей антенн 11,8, 11.9. 11.10 и, кроме того, является четвертым информационным выходом БВК 11, а управляющий выход ГС 11.1 - установочным выходом БВК 11. Первый и второй входы блока первой антенны 11.8 подключены соответственно к выходам блоков B cos(x) 11.2 и B sin(x) 11.7, а третий и четвертый входы - к четвертому информационному выходу ГС 11.1 и B cos(x) 11.4. Первый и второй входы блока второй антенны 11.9 подключены соответственно к выходам блоков B cos(x) 11.2 и 11.4, его третий, четвертый и пятый входы соответственно подключены к выходам блоков B sin(x) 11,5 - 11,7, а шестой вход соединен с четвертым информационным выходом ГС 11.1. Первый и второй входы блока третьей антенны 11.9 подключены соответственно к выходам блоков B sin(x) 11.5 и B cos(x) 11.4, его третий, четвертый и пятый входы соответственно подключены к выходам блоков B cos(x) 11.2, B sin(x) 11,6 и 11.7, а шестой вход соединен с четвертым информационным выходом ГС 11.1. Выходы блоков первой, второй и третьей антенн 11.2, 11.3, 11.4 являются взвешивающими выходами БВК 11.

Генератор сканирования 11.1 предназначен для последовательного переброса аргументов компонент весовых коэффициентов первой, второй и третьей антенн. Схема ГС показана на фиг. 19 и включает первый, второй, третий и четвертый десятичные N-разрядные счетчики 11.1.1-11.1.4, первый, второй, третий и четвертый Дел константы на число 11.1.5-11.1.8, первый, второй, третий и четвертый компараторы 11.1.9-11.1.12. Счетный вход первого десятичного N-разрядного счетчика 11.1.1 подключен к выходу тактовой частоты генератора опорных частот 12, а выход соединен со вторым входом первого компаратора 11.1.9, первый вход которого соединен с выходом первого Дел константы на число 11.1.5, вход которого подключен к выходу "Разрешение" БУ 4. Выход компаратора 11.1.5 подключен к счетному входу второго счетчика 11.1.2, выход которого соединен со вторым входом второго компаратора 11.1.10. Его первый вход соединен с выходом второго Дел константы на число 11.1.6, вход которого также подключен к выходу "Разрешение" БУ 4. Выход компаратора 11.1.6 подключен к счетному входу третьего счетчика 11.1.3, выход которого соединен со вторым входом третьего компаратора 11.1.11. Его первый вход соединен с выходом третьего Дел константы на число 11.1.6, вход которого также подключен к выходу "Разрешение" БУ 4. Выход компаратора 11.1.7 подключен к счетному входу четвертого счетчика 11.1.4, выход которого соединен со вторым входом четвертого компаратора 11.1.12. Его вход соединен с выходом четвертого Дел константы на число 11.1.7, вход которого также подключен к выходу "Разрешение" БУ 4. Установочные входы первого, второго, третьего и четвертого счетчиков 11.1.1-11.1.4 соединены с выходом элемента задержки 11.11. При этом выходы первого, второго, третьего и четвертого счетчиков также являются информационными выходами, а выход четвертого компаратора - установочным выходом ГС 11.1.

Блоки первой, второй и третьей антенн 11.8, 11.9, 11.10 предназначены для вычисления по определенным законам весовых коэффициентов соответствующих антенн из формируемого на каждом такте ГС 11.1 и первым, вторым и третьим В cos(x) 11.2 - 11.4, первым, вторым и третьим B sin(x) 11.5 - 11.7 и четвертым информационным выходом ГС 11.1 набора чисел. Структура блоков 11.8, 11.9, 11.10 зависит от типа антенн и их ориентации. В частности, структура этих блоков для триортогонального "точечного" антенного блока, состоящего из вертикальных ортогональных рамочных антенн и несимметричного вибратора, установленного на оси пересечения рамок, показана на фиг. 20, 21 и 22.

Блок первой антенны 11.8 включают первый 11.8.1 и второй 11.8.4 Умн, Умн на мнимую единицу 11.8.2 и Сум 11.8.3. причем первый вход первого Умн 11 81.1 соединен с четвертым информационным выходом ГС 11.1, второй его вход подключен к выходу третьего B cos(x) 11.4, а выход соединен с входом Умн на мнимую единицу 11.8.2. Его выход подключен ко второму входу Сум 11.8.3, первый вход которого соединен с выходом третьего B sin(x) 11.7, а выход подключен ко второму входу второго Умн 11.8.4. Его первый вход соединен с выходом первого B cos(x) 11.2, а выход является выходом блока первой антенны 11.8.

Блок второй антенны 11.9 включает первый, второй, третий, четвертый и пятый Умн 11.9.1-11.9.5, первый и второй Выч 11.9.6 и 11.9.9, Сум 11.9.7 и Умн на мнимую единицу 11.9.8. Первый вход первого Умн 1.9.1 соединен с выходом первого B cos(x) 11.2, второй его вход подключен к выходу третьего B cos(x) 11.4, а выход соединен с первым входом первого Выч 11.9.6. Его второй вход подключен к выходу второго Умн 11.9.2, первый вход которого соединен с выходом первого B sin(x) 11,5, второй вход - с выходом второго B sin(x) 11.6, а третий - с выходом третьего B sin(x) 11.7, а выход Сум 11.9.6 подключен к первому входу вычитателя 11.9.9. Его второй вход соединен с выходом Умн на мнимую единицу 11.9.8, вход которого подключен к выходу Умн 11.9.5, первый вход которого соединен с четвертым информационным выходом ГС 11.1, а второй вход подключен к выходу Сум 11.9.7. Первый вход Сум 11.9.7 соединен с выходом Умн 11.9.3, его первый вход подключен к выходу первого B cos(x) 11.2, а второй вход - к выходу третьего B sin(x). Второй вход Сум 11.9.7 соединен с выходом Умн 11.9.4, первый вход которого подключен к выходу первого B sin(x) 11.5, второй его вход соединен с выходом второго B sin(x) 11.6, а третий вход - с входом третьего B cos(x) 11.4. Выход второго Выч 11.9.9 является выходом блока второй антенны 11.9.

Блок третьей антенны 11.10 включает первый, второй, третий, четвертый и пятый Умн 11.10.1-11.10.5, первый и второй Выч 11.10.7 и 11.10.5, первый и второй Выч 11.10.7 и 11.10.9, Сум 11.10.6 и Умн на мнимую единицу 11.10.8. Первый вход первого Умн 11.10.1 соединен с выходом первого B sin(x) 11.5, второй его вход подключен к выходу третьего B cos(x) 11,4, а выход соединен с первым входом Сум 11.10.6. Его второй вход подключен к выходу второго Умн 11.10.2, первый вход которого соединен с выходом первого B cos(x) 11.5, второй вход - с выходом второго B sin(x) 11.6, а третий - с выходом третьего B sin(x) 11.7, а выход Сум 11.10.6 подключен к первому входу Выч 11.10.9. Его второй вход соединен с выходом Умн на мнимую единицу 11.10.8, вход которого подключен к выходу Умн 11.10.5, первый вход которого соединен с четвертым информационным выходом ГС 11.1, а второй вход подключен к выходу Выч 11.10.7. Первый вход Сум 11.9.7 соединен с выходом Умн 11.9.3, его первый вход подключен к выходу первого B cos(x) 11.2, а второй вход - к выходу B sin(x) 11.7. Второй вход Выч 11.10.7 соединен с выходом Умн 11.10.4, первый вход которого подключен к выходу первого B cos(x) 11.2, второй его вход соединен с выходом второго B sin(x) 11.6, а второй вход - с входом третьего B cos(x) 11.4. Выход второго Выч 11.10.9 является выходом блока второй антенны 11.9.

Блок вычисления пеленгов 10 предназначен для определения углов прихода радиоволн. Структурная схема блока показана на фиг. 23 и состоит из первого и второго Умн 1.1 и 10.2, Сум 10.3, вычислителя обратной величины 10.4, вычислителя модуля комплексного числа 10,5, порогового обнаружителя 10.6, блока памяти 10.7, а также первого 10.8 и второго 10.9 регистров. Вход первого регистра 10.8 подключен к первому выходу БМО 9, второй выход которого соединен с входом второго регистра 10.9. Управляющие входы первого и второго регистров 10.8 и 10.9 подключены к синхронизирующему выходу БВК 11. Выход первого регистра 10.8 подключен к первому входу Умн 10.1, второй вход которого соединен со вторым взвешивающим выходом БВК 11, а выход подключен ко второму входу Сум 10.3. Его первый вход соединен с первым взвешивающим выходом БВК 11, а третий вход подключен к выходу второго Умн 10.2. Его первый вход подключен к выходу второго регистра 10.9, а второй вход соединен с третьим взвешивающим выходом БВК 11. Выход Сум 10.3 подключен к входу вычитателя обратной величины 10.4, выход которого соединен с входом вычислителя модуля комплексного числа 10,5, выход которого соединен с входом порогового обнаружителя 10.6. Его выход подключен к первому управляющему входу блока памяти 10,7, первый информационный вход которого также соединен с выходом вычислителя модуля комплексного числа 10.5. Второй, третий, четвертый и пятый информационные входы блока памяти 10.7 подключены соответственно к первому, второму, третьему и четвертому информационным выходам БВК 11. Его установочный вход соединен с установочным выходом БВК 11, а выход является выходом БВП 10.

Ряд блоков цифрового радиопеленгатора по назначению и выполняемым функциям идентичны одноименным блокам прототипа, а именно радиоприемники 21 - 23 и АЦП 31- 33. Отличаются составом, но не выполняемыми функциями цифровые фильтры (в составе буферного накопителя, блока ДПФ, блока весовой обработки и блока обратного ДПФ), из состава которых исключены блоки обратного ДПФ. таким образом, данные блоки могут быть реализованы так же, как и блоки прототипа [4].

Примеры реализации на базе известных логических элементов сумматора счетчика, компаратора приведены в [5 на с 115, 129, 113 соответственно], ЭК [10, с. 61,62]. Примеры реализации Умн и Дел приведены в [6, с 83 и 94 соответственно] . Операция вычитания выполняется при помощи Сум, при этом вычитаемое представляется в обратном или дополнительном коде [6, с.43]. Известно, что на основе сумматора, преобразователей основного кода двоичных чисел в обратный или дополнительный коды и регистров [5, с. 124] в соответствии с известными правилами [6,7,8] могут быть синтезированы коммутатор, Умн на константу, Умн на мнимую единицу, Дел на константу, квадратор, вычислитель третьей степени числа, квадратного и кубического корня, в том числе и для комплексных чисел, сумматор, умножитель, делитель и вычислитель модуля комплексных чисел, а также синуса и косинуса аргумента. Примеры реализации перечисленных элементов приведены на фиг. 24-43.

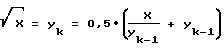

Вычисление квадратного корня производится методом итерации по формуле [7, с. 656]

причем для ускорения сходимости y0 определяется как, число X с поделенным на два порядком. Вычисление y0 упрощается благодаря представлению чисел в цифровых узлах пеленгатора в полулогарифмической форме [6]. Таким образом, уже при шестой итерации погрешность вычисления не превышает 10-8.

Аналогичным образом производится вычисление кубического корня действительного числа по итерационной формуле, выведенной по правилам [7, с. 656]

Погрешность вычисления не превышает 10-5 после пятнадцати итераций.

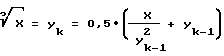

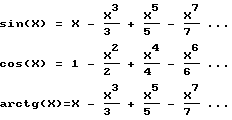

Вычисление синуса, косинуса и арктангенса производится по формулам разложения в степенные ряды [8, ст. 624]

Цифровой радиопеленгатор работает на основе алгоритма гармонического разложения Писаренко [9] . Его основу составляет определение собственного вектора подпространства шума автокорреляционной матрицы с последующим нахождением неизвестных составляющих сигнального собственного вектора. При значительном количестве составляющих сигнального вектора их определение возможно либо методом последовательного перебора, либо одним из известных [8] методов наискорейшего спуска. При этом мерой нахождения сигнального собственного вектора является равенство нулю произведения комплексно-сопряженного транспонированного модулируемого вектора и шумового собственного вектора. Автокорреляционная матрица сигнала как правило неизвестна. Однако ковариационные матрицы обладают аналогичными свойствами, что позволяет использовать алгоритм Писаренко на практике.

Цифровой радиопеленгатор работает следующим образом. Наведенная в первой, второй и третий антеннах триортогонального антенного блока ЭДС поступает на входы соответствующих радиоприемников 21 - 23, настроенных на одну частоту, где решается задача усиления и выделения полезного сигнала. С выхода промежуточной частоты радиоприемников 21 - 23 сигналы поступают на входы соответствующих АЦП 31 - 33, где аналоговые сигналы преобразуются в последовательность N-разрядных отсчетов, появляющихся синхронно на выходах всех АЦП с периодом τ . Для повышения быстродействия пеленгатора все сигнальные связи АЦП выполняются параллельными шинами с разрядностью не менее количества разрядов АЦП, а для передачи комплексных данных разрядность шин данных удваивается. Соответственно, N-канальными являются и все элементы схемы: Сум, ЭК, инверторы и т.п. Сформированные в АЦП последовательности отсчетов поступают на входы соответствующих ЭК 4.8 БУ 4, нормально закрытых. При нажатии кнопки "Измерение" БУ 4 на управляющие входы ЭК 4.8 поступает сигнал логической единицы. Кроме того, сигнал логической единицы поступает на входы БВО 7, подготавливая его к работе, БКМ 8, запрещая считывание информации с сумматора-накопителя 8.13 и БВК 11, устанавливая ЭК 11.12 в состояние "Закрыто" и счетчики ГС 11.1 в выходное (нулевое) состояние. ЭК 4.81 - 4.83 открываются и на входы соответствующих БН 51 - 53 начинают поступать последовательности отсчетов. После накопления реализации фиксированного количества M отсчетов в буферных накопителях формируется сигнал "Считывание реализации", разрешающий выдачу данных для дальнейшей обработки. Синхронность работы АЦП определяет одновременность накопления и, следовательно, считывания реализаций отсчетов. Поэтому подсчет количества считанных реализаций в БУ 4 производится по данным одного БН. Сформированные реализации сигналов поступают на входы соответствующих блоков дискретного преобразования Фурье 61 - 63, где производится вычисление амплитудных спектров сигналов, причем время вычисления спектра не должно превышать время накопления реализации. Вычисленные реализации спектра поступают на сигнальные входы блоков весовой обработки 7, где производится выделение спектральной составляющей с максимальной амплитудой. Определение номера спектральной составляющей с максимальной амплитудой производится по всем трем первым реализациям один раз в течение цикла накопления сигнала. После этого в течение времени накопления сигнала все блоки весовой обработки выделяют только эту составляющую. Амплитуда составляющей спектра описывает комплексным числом. Передача комплексных данных между блоками пеленгатора может осуществляться либо по параллельным линиям, либо последовательно, после передачи действительной части числа. Комплексные числа с выхода блоков весовой обработки поступают соответственно на первый, второй и третий входы БКМ 8. В БКМ 8 производится формирование комплексно-сопряженных чисел и, далее перемножение чисел каждой поступающей реализации в порядке, соответствующем векторному произведению строки на столбец. В результате из каждых трех поступивших на вход БКМ 8 чисел (элементов вектора сигнала) формируется матрица размерностью 3х3. Известно, что сигналы одного источника радиоизлучений, пришедшие в точку приема по разным траекториям в значительной степени коррелированы, что не позволяет разделить их по одной реализации КМ, Для решения задачи раздельного пеленгования коррелированных источников применяют способ усреднения по времени нескольких (не менее трех) матриц. Эта задача решается при помощи сумматора-накопителя 8.13. После накопления заданного в БУ 4 количества КМ, по сигналу логического нуля с выхода триггера 4.6, ЭК 4.8 закрываются т производится считывание сформированной в БКМ 8 матрицы. Она поступает на вход блока матричной обработки (БМО) 9, где производится составление характеристического КМ в блоках коэффициентов "a", "b" и "c" 9.1-9.3 в соответствии с выражением

det(A-λ•l) = 0, (1)

где

A-KM сигнала, λ - C3, I - единичная матрица.

Его корни, являющиеся собственными значениями КМ, вычисляются решением кубичного уравнения по методу Кардано [8] в блоке 9.4, а СВ, соответствующий минимальному C3 (шумового CB) при условии, что его первый элемент равен 1 - решая уравнение вида

(A-λ•l)•x = 0, (2)

где

x - собственный вектор КМ А.

в блоке 9.6. При этом задача выделения минимального C3 решается в компараторе 9.5. БМО работает следующим образом. В блоке коэффициента "a" 9.1 производится суммирование первого, пятого и десятого элементов КМ, что эквивалентно коэффициенту при x2 кубичного уравнения. В блоке коэффициента "b" 9.2 производится вычисление соответствующих произведений поступающих на входы умножителей 9.2.1-9.2.6 девяти элементов КМ (фиг. 8), суммирование первого, второго и третьего, четвертого, пятого и шестого произведений и нахождение разности второй и первой сумм. В блоке коэффициента "c" производится вычисление произведений первого, пятого и девятого, второго, четвертого и девятого, третьего, четвертого и восьмого, второго, шестого и седьмого, третьего, пятого и седьмого, первого, восьмого и шестого элементов КМ в умножителях 9.3.1-9.3.12. После этого в сумматорах 9.3.13 и 9.3.14 определяется сумма первого, третьего и четвертого произведений, из которой в Выч 9.3.15-9.3.17 отнимаются второе, пятое и шестое произведение. В блоке характеристического уравнения 9.4 на основе вычисленных коэффициентов кубичного уравнения производится нахождение его корней по алгоритму Кардано [8]. В блоке 9.4.1 вычисляется квадрат коэффициента "a", поделенный на три и из результата отнимается коэффициента "b". В блоке 9.4.2 вычисляется величина "a"/3 (9.4.2.1), далее вычисляется половина ее третьей степени (9.4.2.2 и 9.4.2.3) и произведение величины "a"/3 на коэффициент "b" (9.4.2.4). В Выч 9.4.2.5 находится из разность, к которой в Сум 9.4.2.6 прибавляется коэффициент "c". Вычисленные в блоках 9.4.1 и 9.4.2 вспомогательные величины "p" и "q" поступают на входы блока 9.4.3. В Дел на три 9.4.3.1 и блоке 9.4.3.2 последовательно вычисляется третья степень одной трети величины "p", а в делителе на два 9.4.3.3 и квадраторе 9.4.3.4 - квадрат половины величины "q". В сумматоре 9.4.3.5 находится их сумма, а в вычислителе квадратного корня определяется вспомогательная величина "Q". Далее в блоках 9.4.4 и 9.4.5 производится вычисление вспомогательный величин "A" и "B" (фиг. 14 и фиг. 15). Полученные величины непосредственно используются для вычисления корней характеристического уравнения в Выч. 9.4.9. (первое C3) и в блоке 9.4.7. В Сум 9.4.7. и делители на минус два 9.4.7.2 последовательно вычисляется полусумма, а в Выч 9.4.7.3 и умножителе на  9.4.7.3 - полуразность величины "A" и "B", домноженная на

9.4.7.3 - полуразность величины "A" и "B", домноженная на  . Далее полуразность величин "A" и "B", домноженная на

. Далее полуразность величин "A" и "B", домноженная на  , умножается на мнимую единицу. Полученные величины поступают соответственно на первый и второй входы сумматора 9.4.7.7 и вычитателя 9.4.7.8. На их выходах формируются соответственно второй и третий корни неполного кубического уравнения, после вычитания из которых одной трети коэффициента "a" на выходах Выч 9.4.7.8 и 9.4.7.9 получаются соответствующие C3. Вычисленные в блоке 9.4 C3 поступают на входы компаратора 9.5, где определяется минимальное (шумовое) C3, которое поступает на седьмой вход блока CB 9.6.

, умножается на мнимую единицу. Полученные величины поступают соответственно на первый и второй входы сумматора 9.4.7.7 и вычитателя 9.4.7.8. На их выходах формируются соответственно второй и третий корни неполного кубического уравнения, после вычитания из которых одной трети коэффициента "a" на выходах Выч 9.4.7.8 и 9.4.7.9 получаются соответствующие C3. Вычисленные в блоке 9.4 C3 поступают на входы компаратора 9.5, где определяется минимальное (шумовое) C3, которое поступает на седьмой вход блока CB 9.6.

В блоке 9.6 в Выч 9.6.2 определяется разность девятого элемента КМ и шумового C3, в Умн 9.6.7 и 9.6.8 - произведения соответственно шестого и седьмого, шестого и восьмого элемента КМ и в делителях 9.6.10 и 9.6.11 - частное полученных произведений и разности. В Выч 9.6.3 из частного первого произведения и разности вычитается четвертый элемент КМ. Частное этой разности и разности (9.6.4) пятого элемента Км, шумового C3 (9.6.1) и частного второго произведения и разности (9.6.10) образует второй элемент шумового СВ, при условии, что его первый элемент равен единице. Третий элемент этого вектора определяется следующим образом. Вычисленный второй элемент СВ умножается на восьмой элемент КМ в Умн 9.6.9, складывается с седьмым элементом КМ в Сум 9.6.5 и после смены знака в инверторе 9.6.6 делится на разность девятого элемента КМ и шумового C3 с выхода Выч. 9.6.2.

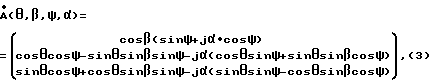

С выхода блока матричной обработки 9 вычисленные второй и третий элементы СИ поступают на сигнальные входы первого и второго регистров 10.8 и 10.9 блока вычисления пеленгов 10. На три взвешивающих входа блока 10 поступает моделируемый СИ, а на четыре его информационных входа поступают значения аргументов величин, образующих этот вектор. Определение направлений прихода радиоволн осуществляется на использовании свойства ортогональности собственных векторов шумового и сигнального подпространств, т.е. равенства нулю их произведения. Умножение векторов выполняется в два шага. На первом шаге вычисляется произведение вторых и третьих элементов векторов в Умн 10.1 и 10.2, а на втором - полученные произведения складываются друг с другом и с первым элементом моделируемого вектора в трехвходовом Сум 10.3. Поскольку сигнальные векторы матрицы определяются сложным нелинейным выражением, содержащим четыре переменные, решить его аналитическим способом не представляется возможным. Поэтому для определения углов прихода излучений производится моделирование сигнального вектора подпространства сигнала методом последовательного перебора, либо одним из методов наискорейшего спуска (градиентного поиска). Следует отметить, что на практике применение методов наискорейшего спуска приводит к возрастанию вероятности ошибок. Функцию последовательного перебора аргументов моделируемого вектора решает ГС 11.1, работающий от тактового выхода блока опорных частот, причем шаг сканирования устанавливается в блоке управления 4 датчиком "Разрешение" 4.7. Сканирование осуществляется следующим образом. На вход первого счетчика 11.11 через ЭК 11.12, открывающийся при поступлении на его управляющий вход через элемент задержки 11.11 сигнала логического нуля с первого выхода БУ 4, поступают тактовые импульсы с выхода блока опорных частот 12. Элемент задержки выбирается таким образом, чтобы в течение интервала задержки БМР 9 произвел вычисление координат шумового СП и запись их значений в регистры 10.8 и 10.9 БВП 10. Это обеспечивает одновременный запуск 10 и ГС 11.1. С выхода первого счета 11.1.1 на второй вход первого компаратора 11.1.9 и на входы первых B cos(x) 11.2 и B sin(x) 11.5 - номер текущего такта в цикле сканирования. На первый же вход первого компаратора 11.1.9 подается частное сектора сканирования в азимутальной плоскости и установленного в блоке управления разрешения (количество шагов). При совпадении показаний счетчика 11.1.1 с определенным в делителе количеством шагов на выходе компаратора 11.1.9 появляется сигнал, поступающий на счетный вход второго счетчика 11.1.2 (сканирование по углу места), увеличивая его выходное состояние на 1 и установочный вход первого счетчика, сбрасывая его в исходное (нулевое) состояние. Цикл сканирования по углу места проходит аналогично сканированию по азимуту и завершается увеличением состояния третьего счетчика 11.1.3 (сканирование по углу поляризации) на единицу и обнулением второго счетчика 11.1.2. При этом выход второго счетчика подключен ко второму входу второго компаратора и к входам вторых B cos(x) 11.3 и синуса 11.6. После завершения сканирования по углу поляризации, которое происходит аналогично рассмотренным выше циклам, (причем выход третьего счетчика подключен ко второму входу третьего компаратора и к входам третьих B cos(x) 11.4 и B sin(x) 11.7) начинается цикл сканирования по соотношению осей эллипса поляризации, окончание которого совпадает с окончанием всех циклов сканирования по параметру и, следовательно, всего суперцикла сканирования. При этом сигнал с выхода четвертого компаратора обнуляет четвертый счетчик 11.1.4 и поступает на управляющий вход блока вычисления пеленгов 10. Вычисленные в соответствующих блоках косинусы и синусы углов азимута, места и поляризации, а также значения соотношения осей эллипса поляризации поступают на входы блоков коэффициентов первой, второй и третьей антенн. В рассматриваемом варианте они формируют координаты СВ (весовые коэффициенты) в соответствии с выражениями, определяющими диаграммы направленности несимметричного вибратора и ортогональных рамочных антенн:

где θ -азимут, β -угол места, ψ -угол поляризации, α - соотношение осей эллипса поляризации сигнала.

Критерием определения сигнального вектора является равенство нулю произведения комплексно-сопряженного сигнального вектора, моделируемого в БВК 11 и шумового СВ, вычисленного в блоке матричной обработки 9. Отличие реальных условий от идеальных приводит к тому, что это произведение стремится к нулю, не обращаясь в него никогда. Для упрощения процедуры установления факта превышения порога и большей наглядности в блоке 10.4 производится вычисление обратной величины (1/х). Установление факта совпадения моделируемого сигнального вектора с параметрами сигнала производится в пороговом обнаружителе 10.6. Следует отметить, что произведение векторов является комплексным числом. Поэтому для реализации процедуры сравнения с порогом необходимо выполнить процедуру вычисления модуля комплексного числа. Эта задача решается в блоке 10.5. При превышении порога блок 10.5 вырабатывает сигнал, по которому информационные входы блока памяти 7 открывается для записи значений аргументов углов моделируемого вектора с выхода блока 11 и уровня отклика с выхода блока вычисления модуля комплексного числа 10.5. По завершении цикла сканирования блок 11 вырабатывает сигнал, разрешающий считывание данных с выхода блока памяти 10.7.

БВО 7 работает следующим образом. На счетный вход счетчика 7.3 поступают сигналы "Коней реализации" с выхода первого блока ДПФ 61. Определенное счетчиком 7.3 количество реализаций сравнивается в компараторе 7.4 с нулем. Таким образом, после прочтения первой реализации спектра на выходе компаратора 7.4 формируется сигнал логической единицы, поступающий на управляющие входы ЭК 7.1.2, устанавливая их в состояние "Закрыто". Этим обеспечивается определение максимальной спектральной составляющей по первой реализации спектра. Установка счетчика 7.4 в исходное состояние производится сигналом логического нуля с запускающего выхода БУ 4. На входы канальных блоков взвешивания 7.1 поступают вычисленные в соответствующих блоках ДПФ 6 спектральные коэффициенты, тактовые импульсы и управляющие сигналы от соответствующих блоков ДПФ 6. При обработке первой реализации спектра спектральные коэффициенты с сигнального выхода соответствующего блока ДПФ 6 одновременно поступают на входы буферного носителя 7.1.1 и через 7.1.2 нормально открытый на второй вход компаратора 7.1.6 и сигнальный вход электронного ключа 7.1.3, нормально закрытого. В компараторе 7.1.6 производится сравнение поступающего на второй его вход спектрального коэффициента с хранящимся в регистре 7.1.10 значением. Выход компаратора 7.1.6 устанавливается в состояние логической единицы, если поступившее на его второй вход значение больше хранящегося в регистре 7.1.10. Появляющаяся на выходе компаратора 7.1.6 логическая единица открывает электронный ключ 7.1.3 и спектральный коэффициент, значение которого превосходит хранящееся в регистре 7.1.10, поступает на его вход и записывается вместо хранившегося ранее. При поступлении на вход компаратора 7.1.6 следующего отсчета спектра его значение будет сравниваться с сохраненным в регистре 7.1.10. Если его величина окажется меньше хранящейся в регистре 7.1.10, то на выходе компаратора установится логический ноль, электронный ключ 7.1.3 установится в состояние "Закрыто" и этот отсчет не будет записан в регистр 7.1.10. На вход счетчика 7.1.9, определяющего номер текущего отсчета спектра, поступают тактовые импульсы с тактового выхода соответствующего блока ДПФ 6. Номера отсчетов с выхода счетчика 7.1.9 поступают на вход электронного ключа 7.1.4, нормально закрытого. При поступлении на управляющий выход электронного ключа 7.1.4 сигнала логической единицы с выхода компаратора 7.1.6 ключ 7.1.4 открывается и номер текущего максимального отсчета спектра записывается в регистр 7.1.11. Такой алгоритм работы сохраняется до конца первой последовательности спектральных коэффициентов. По окончании считывания первой из накапливаемых реализаций спектра с синхронизирующего выхода блока ДПФ 6 поступает сигнал "Конец реализации", который открывает электронные ключи 7.1.12 и 7.1.13. Сигнал "Конец реализации" оканчивается с началом считывания следующей реализации. Через открытые электронные ключи 7.1.12 и 7.1.13 на соответствующие входы блока номера составляющей 7.2 поступают определенные, как показано выше, максимальный спектральный коэффициент из регистра 7.1.10 и его номер из регистра 7.1.11. В блоке 7.2 производится определение максимальной составляющей спектра из трех, поступивших с выхода блоков 7.1, и ее номера. По окончании цикла работы блока 7.2 на его выходе формируется номер максимальной составляющей из первых реализаций спектра в трех каналах. Сигнал логической единицы с выхода компаратора 7.37.2 поступает на управляющие входы электронных ключей 7.1.2, закрывая их и исключая последующие реализации из обработки, а определенный в блоке 7.2 номер максимальной составляющей - на вторые входы компараторов 7.1.7 соответствующих блоков 7.1. При поступлении сигнала "Конец реализации" на выходы "Считывание" буферных накопителей 7.1.1 начинается процесс последовательного считывания накопленной в нем реализации спектра. При этом спектральные коэффициенты с сигнального выхода БН 7.1.1 поступают на сигнальный выход электронного ключа 7.1.5, нормально закрытого, а тактовые импульсы - на вход счетчика 7.1.8. Текущие номера считанных спектральных коэффициентов поступают на первый вход компаратора 7.1.7, выход которого устанавливается в состояние логической единицы при совпадении сигналов на его входах. Сигнал логической единицы на выходе компаратора 7.1.7 открывает электронный ключ 7.1.5 и спектральный коэффициент, соответствующий определенному ранее номеру максимальной составляющей из первых реализаций спектра в трех каналах, поступает на соответствующий выход блока весовой обработки 7 и далее - на соответствующий вход блока ковариационной матрицы 8. Кроме того, сигнал логической единицы на выходе компаратора 7.1.7 поступает на вход "Cброс" БН 7.1.1 и регистров 7.1.10 и 7.1.11, обнуляя их, а также на входы "Сброс" счетчиков 7.1.8 и 7.1.9, устанавливая их в исходное состояние.

Блок номера составляющей 7.2 работает следующим образом. Выделенные в канальных блоках селекции 7.11 - 7.13 коэффициенты спектральных составляющих поступают на входы компараторов 7.2.1, 7.2.2, 7.2.7 и 7.2.8 и на сигнальные входы ЭК 7.2.3 и 7.2.5, а их номера - на сигнальные входы соответствующих ЭК 7.2.4, 7.2.6 и 7.2.10. Все ЭК 7.2.3 - 7.2.5, 7.2.9 и 7.2.10 нормально закрыты. Спектральный коэффициент с выхода первого блока селекции 7.11 поступает на первые входы компараторов 7.2.1, 7.2.2 и сигнальный выход электронного ключа 7.2.3; спектральный коэффициент с выхода второго блока селекции 7.12 поступает на вторые входы компаратора 7.2.1, 7.2.2 и сигнальный вход электронного ключа 7.2.4; спектральный коэффициент с выхода третьего блока селекции 7.13 поступает на вторые входы компараторов 7.2.7 и 7.2.8.Сигналы с выходов компараторов 7.2.1 и 7.2.2 поступают на управляющие входы соответственно ЭК 7.2.3 и 7.2.4, 7.2.5 и 7.2.6. Таким образом, если величина спектрального коэффициента, выделенного в первом блоке селекции 7.11 превышает величину во втором блоке селекции 7.12, то на выходе компаратора 7.2.1 появляется сигнал логической единицы, открывающий ЭК 7.2.3 и 7.2.4, а на выходе компаратора 7.2.2 - сигнал логического нуля. С выхода ЭК 7.2.3 и 7.2.4 на первые входы компараторов 7.2.7 и 7.2.8 и на сигнальный вход ЭК 7.2.9 поступают соответственно коэффициент спектральной составляющей и ее номер из первого блока селекции 7.11. В противном случае, если величина спектрального коэффициента, выделенного в первом блоке селекции 7.11, меньше величины во втором блоке 7.12, то ЭК 7.2.3 и 7.2.4 будут закрыты, а ЭК 7.2.5 и 7.2.6 открыты и на первые входы компараторов 7.2.7 и 7.2.8 и на сигнальный выход ЭК 7.2.9 поступят соответственно коэффициент спектральной составляющей и ее номер из второго блока селекции 7.12. Таким образом, на первые входы компараторов 7.2.7 и 7.2.8 поступает большее из значений спектральных коэффициентов с выхода блоков селекции 7.11 и 7.12, а на сигнальный вход электронного ключа 7.2.9 - его номер. В компараторах 7.2.7 и 7.2.8 аналогичным образом производится определение максимальной составляющей по первой реализации спектра в трех каналах. Логические сигналы с выхода компараторов 7.2.7 и 7.2.8 поступают на управляющие входы ЭК 7.2.9 и 7.2.10. На сигнальные входы ЭК 7.2.9 и 7.2.10 поступают номер максимальной составляющей по результатам сравнения первого и второго каналов и номер максимальной составляющей третьего канала соответственно. Таким образом, на объединенных выводах ЭК 7.2.9 и 7.2.10 будет номер максимальной составляющей спектра по результатам обработки всех трех каналов. Этот номер записывается в регистр 7.2.12 и хранится до поступления сигнала с выхода БУ 4, обнуляющего регистр и является выходным сигналом блока номера составляющей 7.2.

Следующие реализации спектра, таким образом, поступают на входы блока весовой обработки 7, находящегося в следующем состоянии ЭК 7.1.2 блоков 7.1 под воздействием сигнала логической единицы с выхода компаратора 7.3 находятся в состоянии "Закрыто". При этом исключается поступление последовательности отсчетов спектра на входы компаратора 7.1.6 и электронного ключа 7.1.3 в регистре 7.1.10 хранится 0, а электронные ключи 7.1.12 и 7.1.13 находятся в состоянии "Закрыто". На все входы блока 7.2 поступает сигнал логического нуля. На выходе компаратора 7.1.6 - логический ноль, закрывающий электронные ключи 7.1.3 и 7.1.4. БН 7.1.1, готов к записи очередной реализации спектра. Счетчики 7.1.8 и 7.1.9 находятся в исходном состоянии, на второй вход компаратора 7.1.7 поступает номер составляющей спектра, которую необходимо выделить, а электронный ключ 7.1.5 закрыт. При таком состоянии блока 7 поступающая на вход блоков 7.1 реализация спектра записывается в буферные накопители. По сигналу "Конец реализации", поступающему с выхода соответствующих блоков ДПФ 6, начинается последовательное считывание данных. На такте считывания, соответствующем определенному ранее номеру, хранящемуся в регистре 7.2.8 блока номера составляющей 7.2, на выходе компараторов 7..17 формируется логическая единица, открывающая электронные ключи 7.1.5. При этом на первый, второй и третий сигнальные выходы блока 7 поступают спектральные коэффициенты, соответствующие определенному ранее номеру максимальной составляющей из первых реализаций спектра в трех каналах. Такой режим работы блока весовой обработки продолжается до окончания накопления реализаций спектра. При этом сигналом логического нуля с запускающего выхода блока управления 4 регистр 7.2.11 блока 7.2 и счетчик 7.3 устанавливаются в исходное состояние. БВО 7 готов к следующему циклу работы.

Блок управления 4 работает следующим образом. Нажатием кнопки "Изменение" 4.1 на вход S триггера 4.6 подается логическая единица, устанавливающая его выход в состояние "1". Сигнал логической единицы закрывает электронные ключи 4.81 - 4.83, нормально открытые, и информационные последовательности с выхода АЦП начинают поступать на входы буферных накопителей 51 - 53. Датчиком 4.2, например ручным переключателем, задается необходимое для решения задачи разделения лучей количество реализаций спектра. Опытным путем установлено, что для этого необходимо иметь не менее трех реализаций. Максимальное количество не ограничивается, однако чрезмерное увеличение их количества малоэффективно. Для решения большинства практических задач достаточно ограничиться 20 - 30 реализациями. Заданное количество реализаций спектра в двоичном коде поступает на второй вход компаратора 4.4, где с ним сравнивается поступающее на первый вход определенное в счетчике 4.3 текущее количество реализаций. При совпадении чисел на входах компаратора он вырабатывает сигнал логической единицы, поступающей на второй вход (R) триггера 4.6 через интервал времени Δt , определяемый параметрами элемента задержки. Элемент задержки выбирается таким образом, чтобы за время Δt все реализации отсчетов сигналов, считанные из буферных накопителей, прошли все стадии обработки и поступили бы в регистры сумматора-накопителя 8.13. Поступающая на вход R триггера логическая единица устанавливает на его выходе логический ноль, при этом электронные ключи 4.81 - 4.83 устанавливаются в исходное состояние и тем самым разрывают цепь накопления сигнала. Кроме того, логический ноль поступает на управляющий вход БКМ 8, разрешая считывание матрицы, а также на управляющий вход БВК 11. По окончании цикла сканирования в блоке весовых коэффициентов 11 вырабатывается сигнал логической единицы. "Конец сканирования" который поступает на управляющий вход блока вычисления пеленгов и на установочный вход счетчика 4.3, а также сумматора-накопителя 8.13, обнуляя их. RS-триггер находится в состоянии ожидания ввода (логический ноль из обоих входах). Тем самым цифровой радиопеленгатор в целом переводится в состояние ожидания.

Источники информации

1. Кукес И.С., Старик М.Е. Основы радиопеленгации . - М.: Советское радио, 1964, с.428-458.

2. Патент США N 4062015, кл. G 01 S 3/20, 1977.

3. Патент ФРГ N 2242790, кл. G 01 S 3/14, 1976.

4. Патент ФРГ N 4014407, кл. G 01 S 3/14, 1991.

5. Вениаминов В.Н. и др. Микросхемы и их применение. М.: Радио и связь, 1989, с. 98-152.

6. Поспелов Д.А. Арифметические основы вычислительных машин дискретного действия. М.: Высшая школа, 1970, с. 127-147, 200-214.

7. Бронштейн И.Н., Семендяев К.А. Справочник по математике для инженеров и учащихся ВТУЗов. М.: Наука, 1981, с. 466-469, 684.

8. Корн Г. , Корн Т. Справочник по математике для научных работников и инженеров. М.: Наука, 1968, с. 47, 570-572.

9. Марпл-мл С.Л. Цифровой спектральный анализ и его приложения. М.: Мир, 1990, с. 430-445.

10. Батушев В. А. и др. Микросхемы и их применение. М.: Радио и связь, 1983.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| АДАПТИВНАЯ АНТЕННАЯ СИСТЕМА | 1995 |

|

RU2099837C1 |

| СПОСОБ И УСТРОЙСТВО АДАПТИВНОЙ ПРОСТРАНСТВЕННОЙ ФИЛЬТРАЦИИ СИГНАЛОВ | 1998 |

|

RU2141706C1 |

| СПОСОБ ПЕЛЕНГОВАНИЯ ИСТОЧНИКОВ РАДИОИЗЛУЧЕНИЙ В УСЛОВИЯХ МНОГОЛУЧЕВОСТИ | 1997 |

|

RU2141675C1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| АДАПТИВНАЯ АНТЕННАЯ РЕШЕТКА | 1995 |

|

RU2099838C1 |

| МНОГОКАНАЛЬНОЕ АДАПТИВНОЕ РАДИОПРИЕМНОЕ УСТРОЙСТВО | 1994 |

|

RU2107394C1 |

| СПОСОБ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА УСИЛЕНИЯ АНТЕНН И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1995 |

|

RU2104561C1 |

| АДАПТИВНАЯ АНТЕННАЯ РЕШЕТКА | 1991 |

|

RU2014681C1 |

| АДАПТИВНАЯ АНТЕННАЯ РЕШЕТКА | 1994 |

|

RU2090960C1 |

Изобретение относится к радиотехнике, в частности к радионавигации и может использоваться при пеленговании радиоизлучений. Целью изобретения является повышение точности пеленгования модулированных радиосигналов с неизвестной структурой в диапазоне коротких волн, в том числе и в условиях двухмодового распространения радиоволн. Поставленная цель достигается тем, что в известный цифровой радиопеленгатор, содержащий антенный блок 1, первый и второй радиоприемники 21 и 22, аналого-цифровые преобразователи 31 и 32, буферные накопители 51 и 52, блоки дискретного преобразования Фурье 61 и 62, блок весовой обработки 7, блок вычисления пеленгов 10 и блок опорных частот 12 дополнительно введены третий радиоприемник 23, третий аналого-цифровой преобразователь 33, третий буферный накопитель 55, третий блок дискретного преобразования Фурье 63, блоки управления 4, ковариационной матрицы 8, матричной обработки 9 и весовых коэффициентов 11, причем антенный блок включает первую, вторую и третью антенны. В предлагаемом пеленгаторе изменен способ получения информации о параметрах линии положения. Повышение помехоустойчивости пеленгатора достигнуто за счет выделения максимальной составляющей спектра сигнала. Возможность раздельного пеленгования компонент двухмодового поля обеспечивается временным усреднением ковариационных матриц сигнала и применением метода Писаренко для определения углов прихода радиосигналов. 42 ил.