Изобретения объединены единым изобретательским замыслом, относятся к области радиотехники и могут использоваться в радионавигации и при контроле за использованием диапазона частот, в частности при пеленговании источников радиоизлучений, а также в системах радиосвязи с пространственной обработкой радиосигналов.

Известен двухканальный автоматический радиопеленгатор с визуальным отсчетом пеленга [1] , содержащий антенный блок, радиоприемные устройства вертикального и горизонтального каналов, смесители и электронно-лучевую трубку. Данный радиопеленгатор обеспечивает раздельное пеленгование сигналов, отличающихся по частоте и попадающих в полосу пропускания приемников. Однако данный пеленгатор имеет низкую точность пеленгования, что обусловлено значительным уровнем станционных помех и не позволяет идентифицировать измеренные пеленги с интерферирующими сигналами.

Известен цифровой пеленгаторный радиоприемник [2], содержащий антенный блок, два широкополосных усилителя, два аналого-цифровых преобразователя, два анализатора амплитудного спектра и блок вычисления пеленгов. Данное устройство позволяет определять пеленг при более низком отношении сигнал/шум, в том числе сигналов, частично перекрывающихся по частоте. Однако этот пеленгаторный приемник имеет низкую точность пеленгования, что обусловлено дискретным характером оценок спектров сигналов, влиянием эффекта "перетекания" энергии составляющих спектра, высоким уровнем станционных помех и не позволяет идентифицировать измеренные пеленги с интерферирующими сигналами.

Известен также ВЧ пеленгатор [3], содержащий антенный блок, антенный коммутатор, последовательно соединенные первый радиоприемник, первый аналого-цифровой преобразователь и первый цифровой фильтр, последовательно соединенные опорную антенну, второй радиоприемник, второй аналого-цифровой преобразователь и второй цифровой фильтр, генератор опроса антенн и блок вычисления пеленгов. Данный ВЧ пеленгатор использует эффект Доплера, что упрощает блок вычисления пеленга. При пеленговании узкополосных сигналов с известной структурой пеленгатор на основе эффекта Доплера обеспечивает высокую точность пеленгования при наличии станционных (соканальных) помех. Однако на практике нередко возникает необходимость пеленговать модулированные радиосигналы, занимающие определенную полосу частот и имеющих, в общем случае, непрерывный спектр. Структура таких сигналов, как правило, неизвестна. При их пеленговании известный ВЧ радиопеленгатор не обеспечивает высокую точность пеленгования, что обусловлено отсутствием информации о структуре полезного сигнала, количестве мешающих сигналов, наличии интерференционных явлений в пределах апертуры антенной системы и соотношении мощностей полезного и мешающих сигналов, что определяет увеличение ошибки измерения пеленга и не позволяет идентифицировать измеренные пеленги с интерферирующими сигналами.

Наиболее близким по своей сущности к заявляемому цифровому радиопеленгатору является цифровой радиопеленгатор [4] , содержащий антенный блок, включающий первую, вторую и третью антенны, соединенные с сигнальными входами соответственно первого, второго и третьего радиоприемников, гетеродинные входы которых соединены с гетеродинным выходом блока опорных частот, а выходы подключены к сигнальным входам соответственно первого, второго и третьего аналого-цифровых преобразователей, тактовые входы которых соединены с выходом тактовой частоты блока опорных частот, а выходы подключены соответственно к первому, второму и третьему сигнальным входам блока управления, счетный вход которого соединен с синхронизирующим выходом первого буферного накопителя, установочный вход блока управления подключен к установочному выходу блока весовых коэффициентов, первый управляющий выход соединен с управляющими входами блока весовой обработки, блока ковариационной матрицы и блока весовых коэффициентов, а выход "Разрешение" подключен к одноименному входу блока весовых коэффициентов, первый, второй и третий сигнальные выходы блока управления подключены к сигнальным входам соответствующих буферных накопителей, сигнальные выходы которых соединены с сигнальными входами соответственно первого, второго и третьего блоков дискретного преобразования Фурье, сигнальные, синхронизирующие и тактовые выходы которых подключены соответственно к первым, вторым и третьим сигнальным, синхронизирующим и тактовым входам блока весовой обработки, первый, второй и третий сигнальные выходы которого подключены к соответствующим входам блока ковариационной матрицы, установочный вход которого соединен с установочным выходом блока весовых коэффициентов, а выходы соединены с входами блока матричной обработки, первый и второй выходы которого подключены к двум сигнальным входам блока вычисления пеленгов, три взвешивающих и четыре информационных входа которого соединены с соответствующими выходами блока весовых коэффициентов, синхронизирующий вход подключен к синхронизирующему выходу блока весовых коэффициентов, установочный вход блока вычисления пеленгов подключен к установочному выходу блока весовых коэффициентов, тактовый вход которого соединен с тактовым выходом блока опорной частоты, причем выход блока вычисления пеленгов является выходом цифрового радиопеленгатора.

Этот цифровой радиопеленгатор работает на основе метода MUSIC и обеспечивает высокую точность измерения углов прихода двух сигналов, в том числе и при двухлучевом распространении радиоволн либо, в условиях однолучевого распространения радиоволн, при наличии соканальной помехи.

Однако прототип не обеспечивает возможность получения даже приблизительных оценок углов прихода при интерференции более чем двух сигналов, в условиях односигнального воздействия при отличии параметров шума от модельных предположений (шум - пространственно белый), прототип не обеспечивает высокой точности пеленгования. Кроме того, прототип не позволяет идентифицировать полученные оценки углов прихода и интерферирующих сигналов.

Целью изобретений является обеспечение возможности оценивания углов прихода по меньшей мере одного сигнала при интерференции более чем двух сигналов без увеличения количества антенных элементов, повышение точности пеленгования при отклонении параметров шума от модельных и идентификация полученных оценок углов прихода и интерферирующих сигналов. Кроме того, дополнительной целью второго варианта устройства является обеспечение возможности функционирования пеленгатора при интерференции частично коррелированных сигналов и устранение ошибок оценивания азимута пространственных радиоволн за счет измерения углов места.

Поставленная цель в первом варианте заявляемого цифрового радиопеленгатора достигается тем, что в известный цифровой радиопеленгатор, содержащий антенный блок, первый и второй выходы которого соединены с сигнальными входами соответственно первого и второго радиоприемников, гетеродинные входы которых подключены к гетеродинному выходу блока опорных частот, а выходы соединены с сигнальными входами соответственно первого и второго аналого-цифровых преобразователей, тактовые входы которых подключены к тактовому выходу блока опорных частот, а выходы соединены соответственно с первым и вторым сигнальными входами блока управления, и блок матричной обработки, дополнительно введены первый и второй накопители, первый и второй блоки квадратурного преобразования, блок кумулянтной матрицы, блок фаз, первый и второй элементы задержки и блок дискриминации. Выход кода частоты второго радиоприемника соединен с одноименным входом блока дискриминации. Первый и второй сигнальные выходы блока управления соединены с сигнальными входами соответственно первого и второго накопителей. Счетный вход блока управления подключен к тактовому выходу блока опорных частот, кадровый выход блока управления соединен с кадровыми входами первых и вторых накопителей, установочный выход соединен с установочным входом блока кумулянтной матрицы, выход "База" подключен к одноименному входу блока дискриминации, а выход "Количество" подключен к одноименным входам первого и второго блоков квадратурного преобразования и блока кумулянтной матрицы. Выходы первого и второго накопителей соединены с сигнальными входами соответственно первого и второго блоков квадратурного преобразования, сигнальные выходы которых соединены соответственно с первым и вторым сигнальными входами блока кумулянтной матрицы и входами первого и второго элементов задержки. Выходы первого и второго элементов задержки соединены с соответствующими сигнальными входами блока дискриминации. Синхронизирующий выход первого блока квадратурного преобразования подключен к синхронизирующему входу блока кумулянтной матрицы, девять выходов которого подключены к соответствующим входам блока матричной обработки, первый и второй выходы которого подключены соответственно к первому и второму входам блока фаз. Первый и второй выходы блока фаз соединены с первым и вторым фазовыми входами блока дискриминации. Тактовые входы первых и вторых накопителей и блоков квадратурного преобразования и блока кумулянтной матрицы подключены к выходу тактовой частоты блока опорных частот. Попарно сгруппированные первые и вторые сигнальный и азимутальный выходы которого являются соответствующими выходами цифрового радиопеленгатора.

Блок кумулянтной матрицы предназначен для расчета по реализациям сигналов, принимаемых двухэлементной антенной таких кумулянтных функций 4-го порядка, значения которых с точностью до постоянного коэффициента совпадают со значениями соответствующих элементов ковариационной матрицы трехэлементной антенной системы. Он включает первый, второй, третий, четвертый и пятый инверторы мнимой части, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы задержки и первый, второй, третий, четвертый, пятый и шестой кумулянтные блоки. Входы первого и второго элементов задержки соединены с входами соответственно первого и второго инверторов мнимой части, являющихся соответственно первым и вторым сигнальными входами блока кумулянтной матрицы. Выход первого инвертора мнимой части подключен к первым и третьим сигнальным входам первого, второго и третьего кумулянтных блоков и к первым сигнальным входам четвертого и пятого кумулянтных блоков. Выход первого элемента задержки подключен ко вторым сигнальным входам первого, второго и четвертого кумулянтных блоков и к четвертому сигнальному входу первого кумулянтного блока. Выход второго инвертора мнимой части соединен с третьими сигнальными входами четвертого, пятого и шестого кумулянтных блоков и с первым сигнальным входом шестого кумулянтного блока. Выход второго элемента задержки подключен к четвертым сигнальным входам второго, третьего, четвертого, пятого и шестого кумулянтных блоков и ко вторым сигнальным входам третьего, пятого и шестого кумулянтных блоков. Тактовые входы первого, второго, третьего, четвертого и пятого кумулянтных блоков соединены с тактовым входом шестого кумулянтного блока, являющегося тактовым входом блока кумулянтной матрицы. Входы "Количество" первого, второго, третьего, четвертого и пятого кумулянтных блоков соединены с входом "Количество" шестого кумулянтного блока, являющегося входом "Количество" блока кумулянтной матрицы. Установочные входы первого, второго, третьего, четвертого и пятого кумулянтных блоков соединены с установочным входом шестого кумулянтного блока, являющегося установочным входом блока кумулянтной матрицы. Синхронизирующие входы второго, третьего, четвертого, пятого и шестого кумулянтных блоков соединены с синхронизирующим входом первого кумулянтного блока, являющегося синхронизирующим входом блока кумулянтной матрицы. Выход первого кумулянтного блока подключен к входу третьего элемента задержки. Выход второго кумулянтного блока соединен с входами четвертого элемента задержки и третьего инвертора мнимой части. Выход третьего кумулянтного блока соединен с входами пятого элемента задержки и четвертого инвертора мнимой части. Выход четвертого кумулянтного блока соединен с входом шестого элемента задержки. Выход пятого кумулянтного блока соединен с входами седьмого элемента задержки и пятого инвертора мнимой части. Выход шестого кумулянтного блока соединен с входом восьмого элемента задержки. Выходы третьего элемента задержки, четвертого элемента задержки, третьего инвертора мнимой части, пятого элемента задержки, четвертого инвертора мнимой части, шестого и седьмого элементов задержки, пятого инвертора мнимой части и восьмого элемента задержки являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами блока кумулянтной матрицы.

Поставленная цель в первом варианте заявляемого цифрового радиопеленгатора достигается тем, что в известный цифровой радиопеленгатор, содержащий антенный блок, первый, второй и третий выходы которого соединены с сигнальными входами соответственно первого, второго и третьего радиоприемников, гетеродинные входы которых подключены к гетеродинному выходу блока опорных частот, а выходы соединены с сигнальными входами соответственно первого, второго и третьего аналого-цифровых преобразователей, тактовые входы которых подключены к тактовому выходу блока опорных частот, а выходы соединены соответственно с первым, вторым и третьим сигнальными входами блока управления, первый, второй и третий буферные накопители и блок матричной обработки, дополнительно введены первый, второй и третий накопители, первый, второй и третий блоки квадратурного преобразования, блок кумулянтной матрицы, сумматор-накопитель скользящего окна, блок фаз и блок дискриминации. Выход кода частоты третьего радиоприемника соединен с одноименным входом блока дискриминации. Счетный вход блока управления подключен к тактовому выходу блока опорных частот, кадровый выход блока управления соединен с кадровыми входами первого, второго и третьего накопителей, его установочный выход соединен с одноименными входами блока кумулянтной матрицы, сумматора-накопителя скользящего окна и первого, второго и третьего буферных накопителей, выход блока управления "База" подключен к одноименному входу блока дискриминации, выход "Количество" подключен к одноименным входам первого, второго и третьего блоков квадратурного преобразования и блока кумулянтной матрицы, а выход "Длина окна" подключен к одноименным входам сумматора-накопителя скользящего окна и первого, второго и третьего буферных накопителей. Первый, второй и третий сигнальные выходы блока управления соединены с сигнальными входами соответственно первого, второго и третьего накопителей, выходы которых соединены с сигнальными входами соответственно первого, второго и третьего блоков квадратурного преобразования, сигнальные выходы которых соединены соответственно с первыми, вторыми и третьими сигнальными входами блоков кумулянтной матрицы и первого, второго и третьего буферных накопителей. Синхронизирующий выход первого блока квадратурного преобразования подключен к одноименным входам сумматора-накопителя скользящего окна, первого, второго и третьего буферных накопителей и блока кумулянтной матрицы. Девять выходов блока кумулянтной матрицы подключены к соответствующим девяти входам сумматора-накопителя скользящего окна, девять выходов которого соединены соответственно с девятью сигнальными входами блока матричной обработки. Первый выход блока матричной обработки соединен шиной комплексных данных с первым входом собственного вектора блока дискриминации и с первым и вторым входами блока фаз, причем к первому входу блока фаз подключена часть шины комплексных данных, по которой передается действительная часть комплексного числа, а ко второму его входу подключена часть шины данных, по которой передается мнимая часть комплексного числа. Второй выход блока матричной обработки соединен шиной комплексных данных со вторым входом собственного вектора блока дискриминации и с третьим и четвертым входами блока фаз, причем к третьему входу блока фаз подключена часть шины комплексных данных, по которой передается действительная часть комплексного числа, а к четвертому его входу подключена часть шины данных, по которой передается мнимая часть комплексного числа. Первый и второй выходы "Север-юг" блока фаз соединены с первым и вторым одноименными входами блока дискриминации, первый и второй выходы "Восток-запад" блока фаз соединены с первым и вторым одноименными входами блока дискриминации. Выходы первого, второго и третьего буферных накопителей подключены к соответствующим сигнальным входам блока дискриминации. Тактовые входы первых, вторых и третьих накопителей, блоков квадратурного преобразования и буферных накопителей, кумулянтной матрицы и сумматора-накопителя скользящего окна подключены к выходу тактовой частоты блока опорных частот. Сгруппированные по три первые и вторые сигнальный, азимутальный и угломестные выходы блока дискриминации являются соответствующими выходами цифрового радиопеленгатора.

Блок кумулянтной матрицы предназначен для расчета по реализациям сигналов, принимаемых трехэлементной антенной таких кумулянтных функций 4-го порядка, значения которых с точностью до постоянного коэффициента совпадают со значениями соответствующих элементов ковариационной матрицы трехэлементной антенной системы. Блок кумулянтной матрицы состоит из первого, второго, третьего, четвертого, пятого и шестого инверторов мнимой части, первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого элементов задержки и первого, второго, третьего, четвертого, пятого и шестого кумулянтных блоков. Входы первого, второго и третьего элементов задержки соединены с входами соответственно первого, второго и третьего инверторов мнимой части, являющихся соответственно первым, вторым и третьим сигнальными входами блока кумулянтной матрицы. Выход первого инвертора мнимой части соединен с первыми сигнальными входами первого, второго, третьего, четвертого, пятого и шестого кумулянтных блоков и с третьими сигнальными входами первого, второго и третьего кумулянтных блоков. Выход первого элемента задержки подключен ко вторым сигнальным входам первого, второго, третьего, четвертого, пятого и шестого кумулянтных блоков и к четвертому сигнальному входу первого кумулянтного блока. Выход второго инвертора мнимой части соединен с третьими сигнальными входами четвертого и пятого кумулянтных блоков, а выход второго элемента задержки подключен к четвертым сигнальным входам второго и четвертого кумулянтных блоков. Выход третьего инвертора мнимой части соединен с третьим сигнальным входом шестого кумулянтного блока, а выход третьего элемента задержки подключен к четвертым сигнальным входам третьего, пятого и шестого кумулянтных блоков. Тактовые входы первого, второго, третьего, четвертого и пятого кумулянтных блоков соединены с тактовым входом шестого кумулянтного блока, являющегося тактовым входом блока кумулянтной матрицы, их входы "Количество" соединены с одноименным входом шестого кумулянтного блока, являющегося входом "Количество" блока кумулянтной матрицы, а установочные входы соединены с установочным входом шестого кумулянтного блока, являющегося установочным входом блока кумулянтной матрицы, синхронизирующие входы второго, третьего, четвертого, пятого и шестого кумулянтных блоков подключены к синхронизирующему входу первого кумулянтного блока, являющегося синхронизирующим входом блока кумулянтной матрицы. Выход первого кумулянтного блока соединен с входом четвертого элемента задержки, выход второго кумулянтного блока подключен к входам пятого элемента задержки и четвертого инвертора мнимой части, выход третьего кумулянтного блока соединен с входами шестого элемента задержки и пятого инвертора мнимой части, выход четвертого кумулянтного блока подключен к входу седьмого элемента задержки, выход пятого кумулянтного блока соединен с входами восьмого элемента задержки и шестого инвертора мнимой части, а выход шестого кумулянтного блока подключен к входу девятого элемента задержки. Выходы четвертого элемента задержки, пятого элемента задержки, четвертого инвертора мнимой части, шестого элемента задержки, пятого инвертора мнимой части, седьмого и восьмого элементов задержки, шестого инвертора мнимой части и девятого элемента задержки являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами блока кумулянтной матрицы.

Блок фаз предназначен для расчета пространственной разности фаз одного или двух сигналов, имеющих разные азимуты и углы места, принимаемых трехэлементной антенной системой, элементы которой установлены в вершинах прямоугольного и, в общем случае, неравнобедренного треугольника. Он состоит из первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого вычитателей, первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого сумматоров, первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого квадраторов, первого, второго, третьего, четвертого и пятого умножителей на два, первого, второго, третьего и четвертого умножителей, первого и второго инкременторов, первого и второго декременторов, первого, второго, третьего и четвертого делителей и первого, второго, третьего и четвертого вычислителей арктангенса. Входы первых умножителя на два, квадратора и первый вход первого сумматора соединены с первым входом первого вычитателя, являющегося первым входом блока фаз. Первые входы вторых сумматора и вычитателя и вход второго умножителя на два подключены к входу второго квадратора, являющегося вторым входом блока фаз. Вторые входы первых вычитателя и сумматора и вход третьего умножителя на два соединены с входом третьего квадратора, являющегося третьим входом блока фаз. Вторые входы вторых вычитателя и сумматора и четвертого умножителя на два соединены с входом четвертого квадратора, являющегося четвертым входом блока фаз. Выход первого вычитателя подключен к входу пятого квадратора, выход которого соединен с первым входом первого умножителя, выход первого сумматора подключен к входу шестого квадратора, его выход соединен со вторым входом первого умножителя, выход которого подключен к первому входу шестого сумматора. Выход второго вычитателя соединен с входом седьмого квадратора, выход которого подключен к первому входу второго умножителя, выход второго сумматора соединен с входом восьмого квадратора, выход которого подключен ко второму входу второго умножителя, выход которого соединен со вторым входом шестого сумматора, а его выход подключен к первому входу седьмого вычитателя. Выход первого квадратора соединен с первыми входами пятого вычитателя и третьего умножителя, выход второго квадратора подключен к первым входам третьего сумматора и четвертого вычитателя и ко второму входу третьего вычитателя. Выход четвертого квадратора соединен со вторыми входами третьего сумматора и четвертого вычитателя и с первым входом третьего вычитателя. Выход третьего вычитателя подключен к входам первых инкрементора и декрементора, выход четвертого вычитателя соединен с входом второго инкрементора. Выход первого инкрементора подключен ко второму входу третьего умножителя и к первому входу седьмого сумматора, а выход второго инкрементора соединен с первым входом четвертого умножителя, выход третьего квадратора подключен ко вторым входам пятого вычитателя и четвертого умножителя, а выходы третьего и четвертого умножителей соединены соответственно с первым и вторым входами четвертого сумматора. Выход четвертого сумматора подключен ко второму входу пятого сумматора. Выход третьего сумматора соединен с первым входом пятого сумматора, выход которого подключен к входу пятого умножителя на два. Выход пятого умножителя на два через второй декрементор подключен ко второму входу седьмого вычитателя, выход которого соединен с входом вычислителя квадратного корня, а его выход подключен ко вторым входам десятого и одиннадцатого сумматоров и восьмого и девятого вычитателей. Выход второго умножителя на два соединен с первыми входами десятого сумматора и восьмого вычитателя, выход четвертого умножителя на два подключен к первым входам одиннадцатого сумматора и девятого вычитателя, выходы десятого и одиннадцатого сумматоров соединены с первыми входами соответственно первого и третьего делителей, а выходы восьмого и девятого вычитателей подключены к первым входам второго и четвертого делителей. Выход пятого вычитателя соединен со вторым входом седьмого и первым входом восьмого сумматоров, выход седьмого сумматора подключен к первому входу шестого вычитателя, второй вход которого соединен с выходом первого умножителя на два, а выход подключен ко вторым входам первого и второго делителей, второй вход восьмого сумматора соединен с выходом первого декрементора, выход восьмого сумматора подключен к первому входу девятого сумматора, второй вход которого соединен с выходом третьего умножителя на два, а выход девятого сумматора подключен ко вторым входам третьего и четвертого делителей. Выходы первого, второго, третьего и четвертого делителей соединены с входами соответственно первого, второго, третьего и четвертого вычислителей арктангенса, причем выходы первого и второго вычислителей арктангенса являются соответственно первым и вторым выходами "Север-юг" блока фаз, а выходы третьего и четвертого вычислителей арктангенса являются соответственно первым и вторым выходами "Восток-Запад" блока фаз.

Блок дискриминации предназначен для разделения двух сигналов, принимаемых трехэлементной антенной системой, элементы которой установлены в вершинах прямоугольного треугольника, и расчета их азимутов и углов места. Он состоит из первого и второго блоков векторного умножения, компаратора, коммутатора, первых, вторых, третьих и четвертых блоков весовых коэффициентов, делителей и вычитателей и первого и второго блоков углов. Первый фазовый вход первого блока углов и первый вход первого блока весовых коэффициентов, вторые входы второго и третьего блоков весовых коэффициентов, четвертый вход четвертого блока весовых коэффициентов и первый фазовый вход второго блока векторного умножения соединены с первым фазовым входом первого блока векторного умножения, являющегося первым входом "Север-юг" блока дискриминации. Первый информационный вход коммутатора подключен ко второму фазовому входу первого блока векторного умножения, являющегося первым входом "Восток-запад" блока дискриминации, а второй информационный вход коммутатора соединен со вторым фазовым входом второго блока векторного умножения, являющегося вторым входом "Восток-запад" блока дискриминации. Первый фазовый вход второго блока углов, второй вход первого блока весовых коэффициентов, третий вход второго блока весовых коэффициентов и первый вход третьего блока весовых коэффициентов подключены ко второму входу четвертого блока весовых коэффициентов, являющегося вторым входом "Восток-запад" блока дискриминации. Первый и второй входы собственного вектора второго блока векторного умножения соединены с первым и вторым входами собственного вектора первого блока векторного умножения, являющихся соответственно первым и вторым входами собственного вектора блока дискриминации. Выход первого блока векторного умножения соединен с первым входом компаратора, второй вход которого подключен к выходу второго блока векторного умножения, а выход компаратора соединен с управляющим входом коммутатора. Первый выход коммутатора соединен со вторым фазовым входом первого блока углов, третьим входом первого блока весовых коэффициентов, четвертыми входами второго и третьего блоков весовых коэффициентов и первым входом четвертого блока весовых коэффициентов. Второй выход коммутатора соединен со вторым фазовым входом второго блока углов, четвертым входом первого блока весовых коэффициентов, первым входом второго блока весовых коэффициентов, третьими входами третьего и четвертого блоков весовых коэффициентов. Вход "База" первого блока углов соединен с одноименным входом второго блока углов, являющегося входом "База" блока дискриминации. Вход "Частота" первого блока углов соединен с одноименным входом второго блока углов, являющегося входом "Частота" блока дискриминации. Выходы первого, второго, третьего и четвертого блоков весовых коэффициентов подключены ко вторым входам соответственно первого, второго, третьего и четвертого делителей. Первый вход третьего делителя соединен с первым входом первого делителя, являющегося вторым сигнальным входом блока дискриминации. Первый вход второго делителя соединен с первым входом четвертого делителя, являющегося третьим сигнальным входом блока дискриминации. Выходы первого, второго, третьего и четвертого делителей подключены ко вторым входам соответственно первого, второго, третьего и четвертого вычитателей. Первый вход третьего вычитателя соединен с первым входом первого вычитателя, являющегося первым сигнальным входом блока дискриминации. Выход первого вычитателя подключен к первому входу второго вычитателя, выход третьего вычитателя соединен с первым входом четвертого вычитателя. Выходы третьего и четвертого вычитателей являются соответственно первым и вторым сигнальными выходами блока дискриминации, а азимутальные и угломестные выходы первого и второго блоков углов являются соответственно первыми и вторыми азимутальными и угломестными выходами блока дискриминации.

Благодаря указанной совокупности признаков за счет введения новых блоков в первом варианте цифрового радиопеленгатора обеспечивается возможность измерения азимута в условиях интерференции двух сигналов, а при интерференции трех и более сигналов - возможность пеленгования наиболее мощного сигнала, повышается точность оценивания азимута при отклонении параметров шума и антенных элементов от модельных предположений и идентификация получаемых оценок углов прихода и принимаемых сигналов.

Благодаря указанной совокупности признаков за счет введения новых блоков во втором варианте цифрового радиопеленгатора дополнительно обеспечивается возможность пеленгования частично коррелированных радиосигналов и устранения ошибок измерения азимута при приеме пространственных радиоволн за счет измерения угла места.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленных технических решений, отсутствуют, что указывает на их соответствие уровню патентоспособности "новизна". Результаты поиска известных технических решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленных устройств показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленных изобретений на достижение указанного технического результата. Следовательно, заявленные изобретения соответствуют условию патентоспособности "изобретательский уровень".

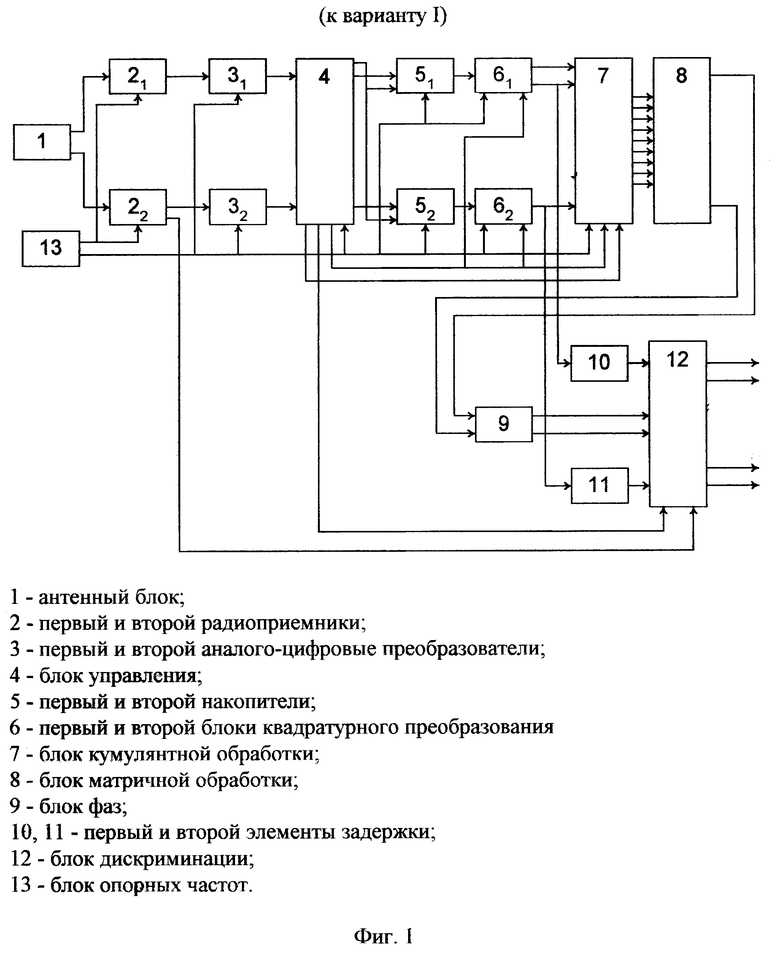

Заявленные устройства поясняются чертежами, на которых показаны:

на фиг. 1 - структурная схема цифрового радиопеленгатора (варианты). Вариант I;

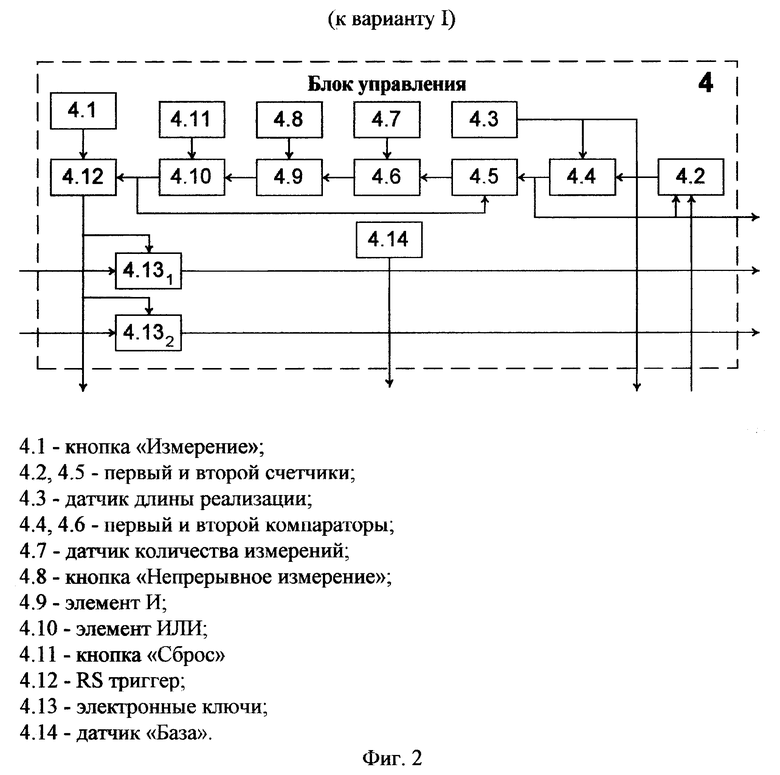

на фиг. 2 - структурная схема блока управления (варианты). Вариант I;

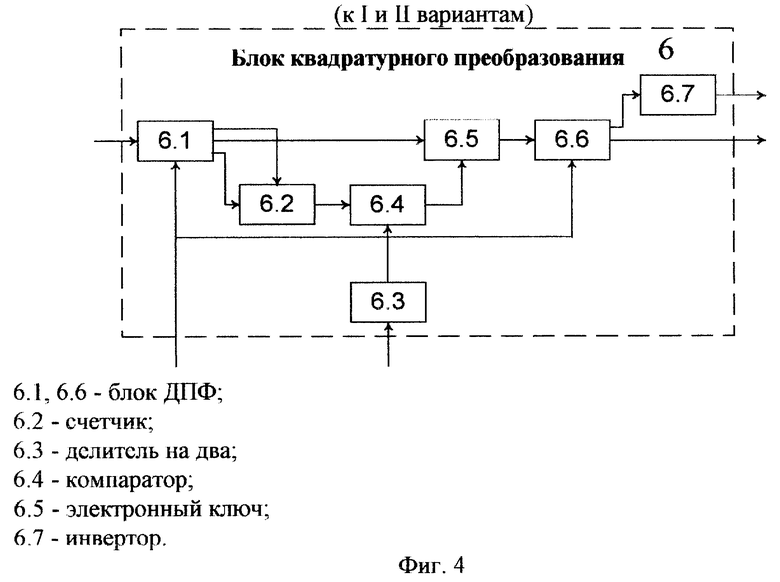

на фиг. 3 - структурная схема блока квадратурного преобразования;

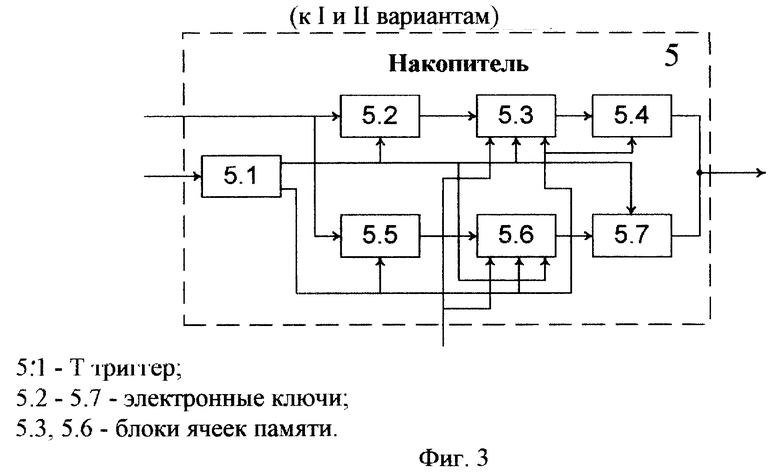

на фиг. 4 - структурная схема накопителя;

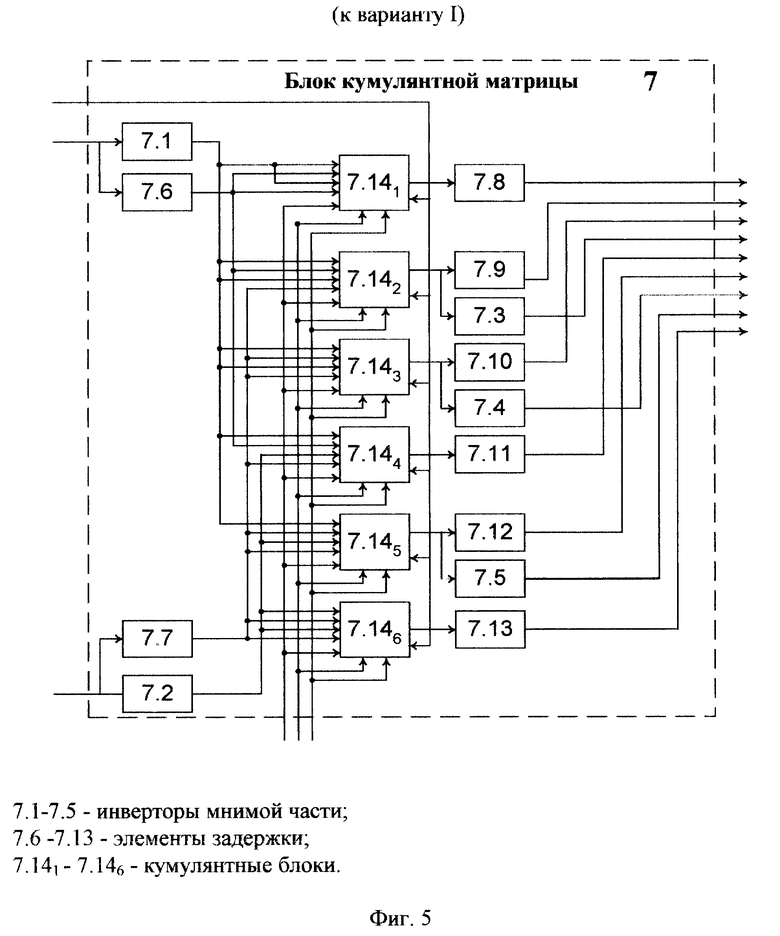

на фиг. 5 - структурная схема блока кумулянтной матрицы (варианты). Вариант I;

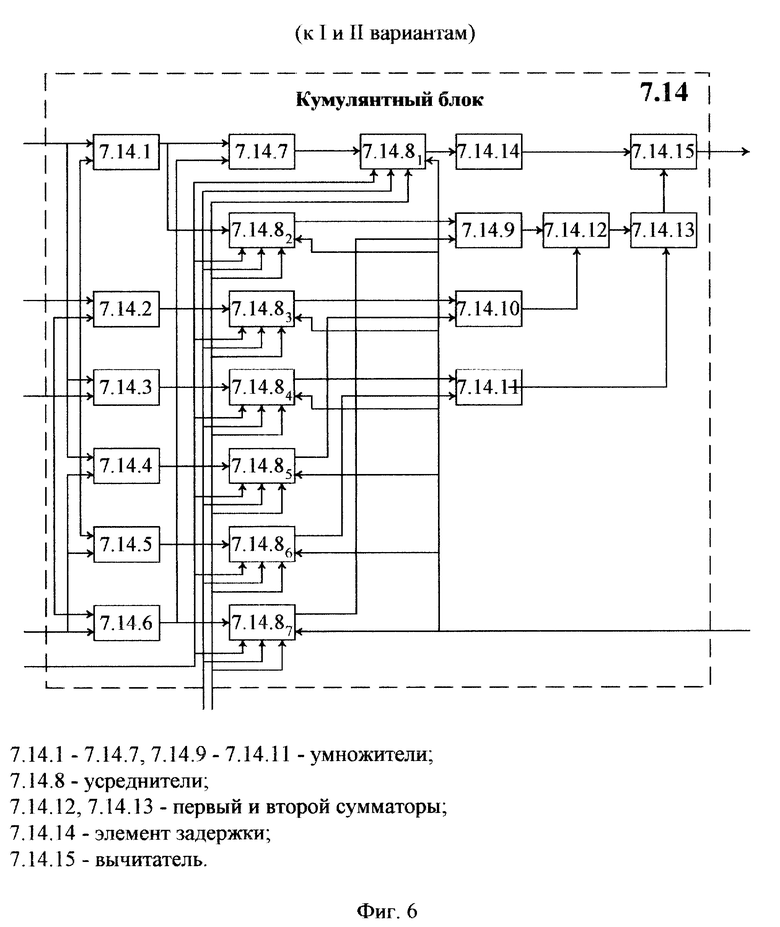

на фиг. 6 - структурная схема кумулянтного блока;

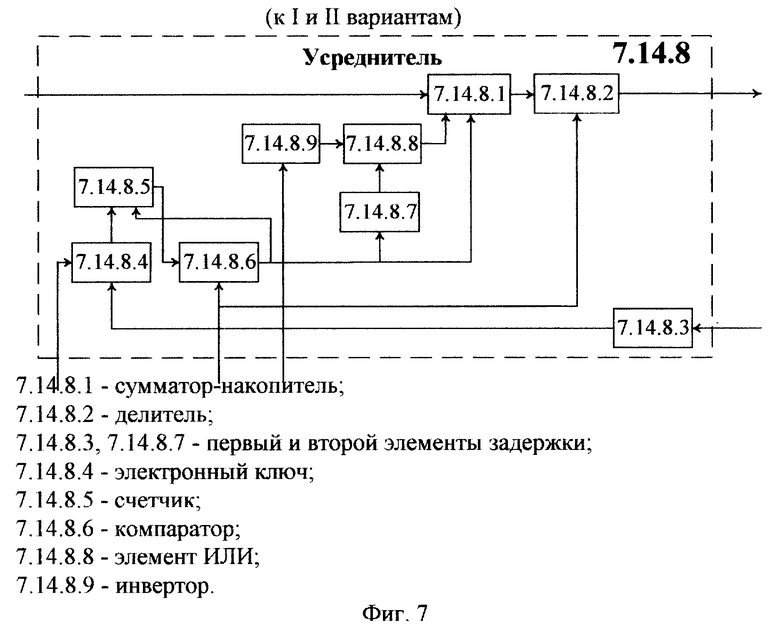

на фиг. 7 - структурная схема усреднителя;

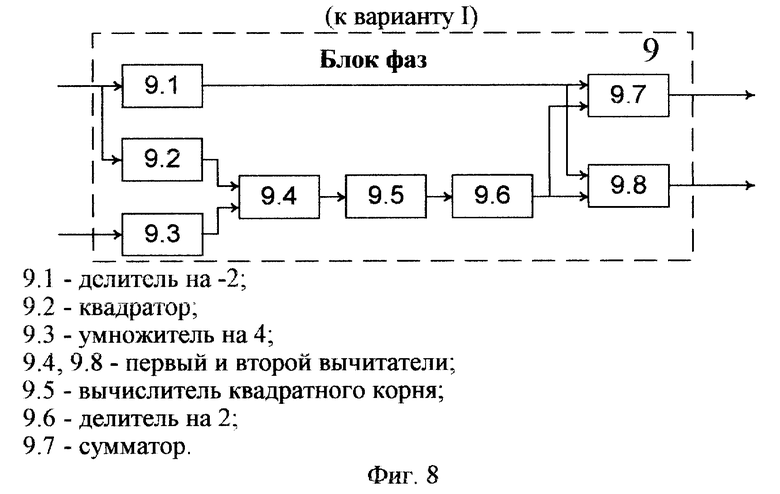

на фиг. 8 - структурная схема блока фаз (варианты). Вариант I;

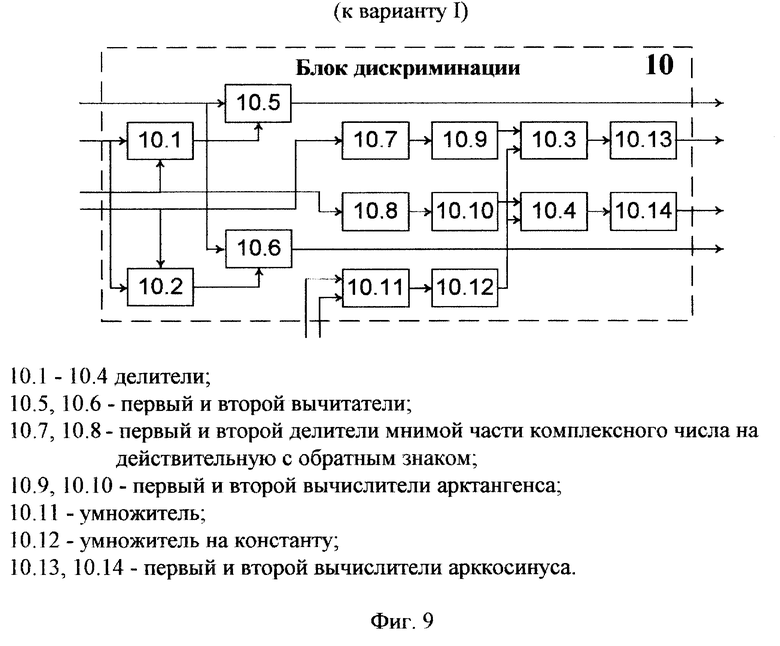

на фиг. 9 - структурная схема блока дискриминации (варианты). Вариант I;

на фиг. 10 - структурная схема цифрового радиопеленгатора (варианты). Вариант II;

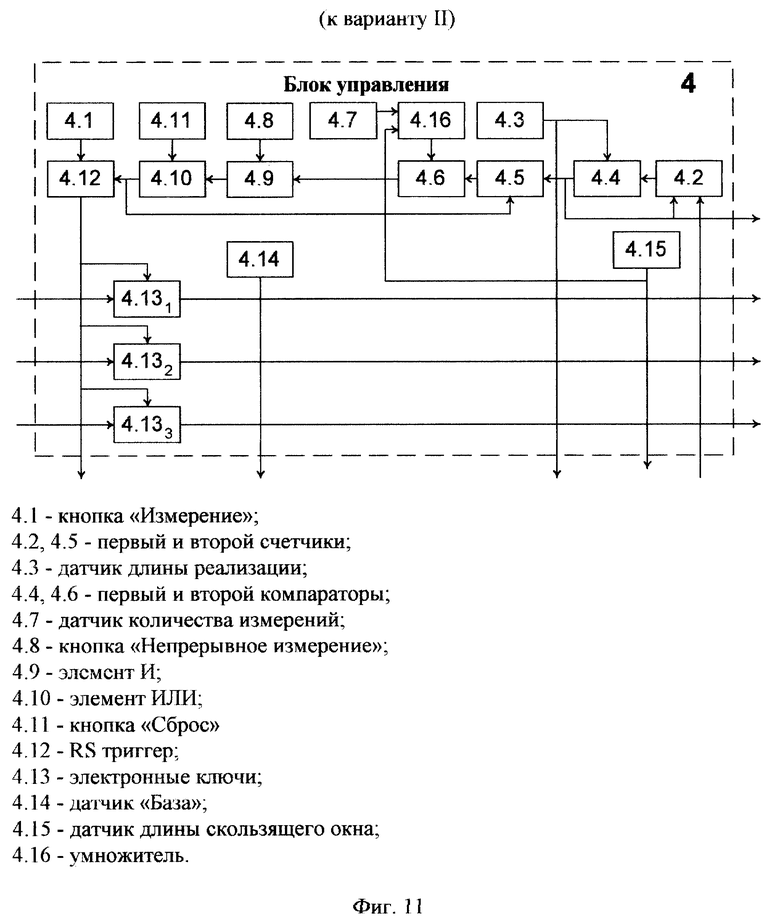

на фиг. 11 - структурная схема блока управления (варианты). Вариант II;

на фиг. 12 - структурная схема блока кумулянтной матрицы (варианты). Вариант II;

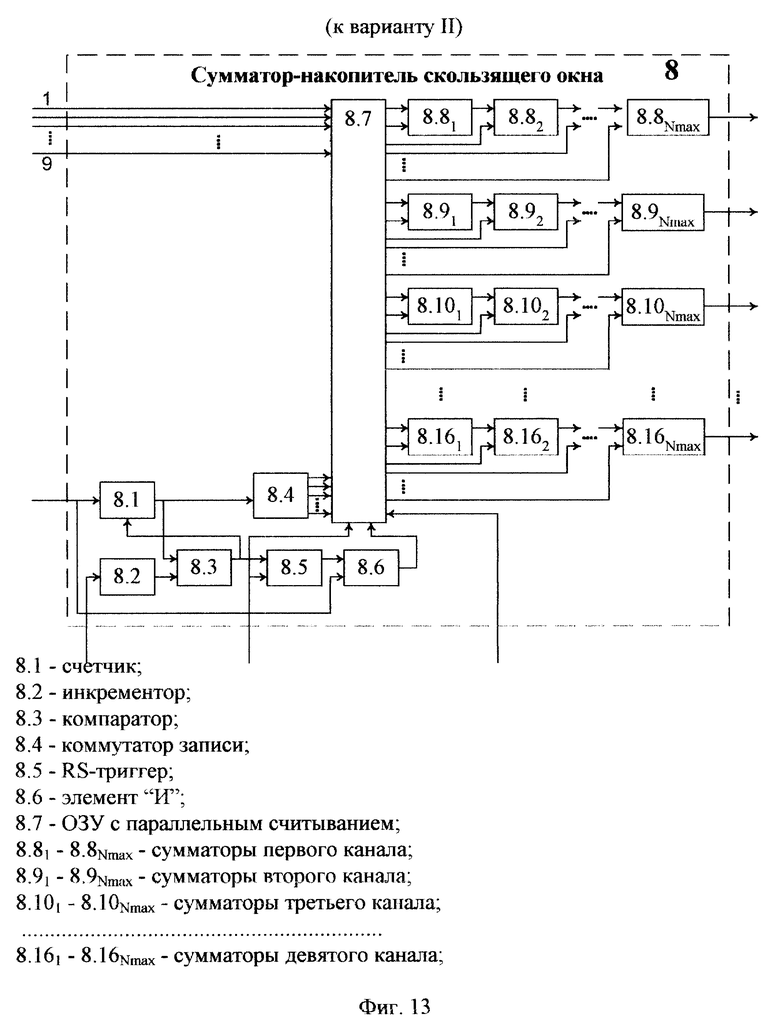

на фиг. 13 - структурная схема сумматора-накопителя скользящего окна;

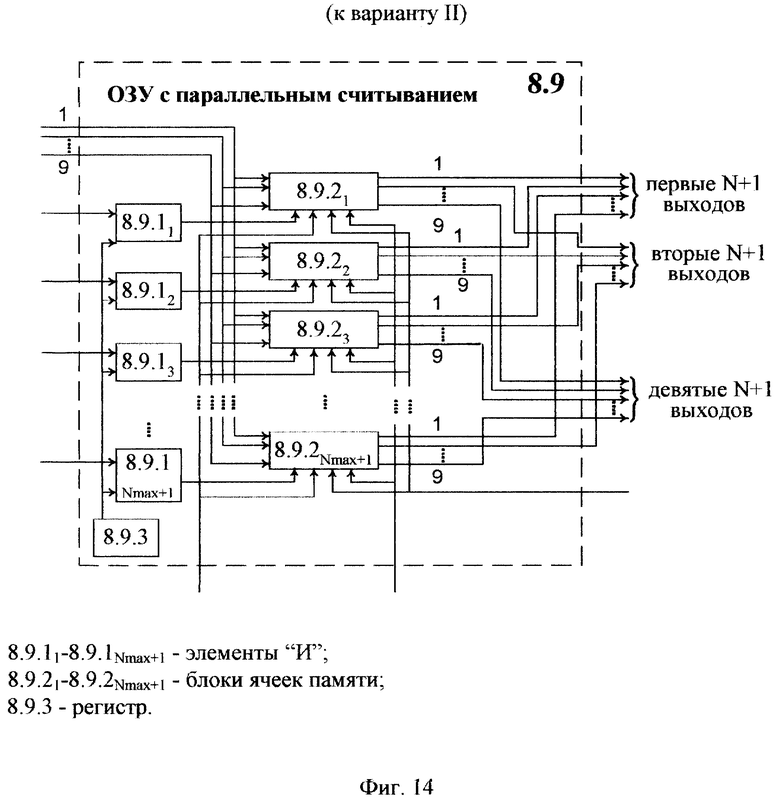

на фиг. 14 - структурная схема ОЗУ с параллельным считыванием;

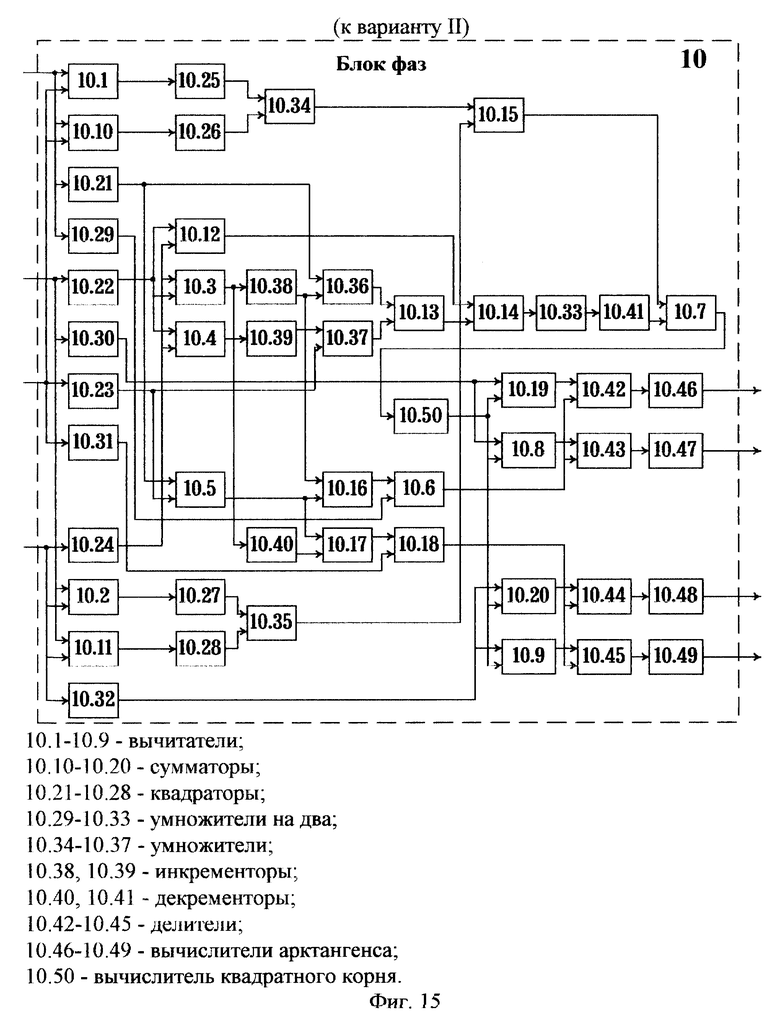

на фиг. 15 - структурная схема блока фаз (варианты). Вариант II;

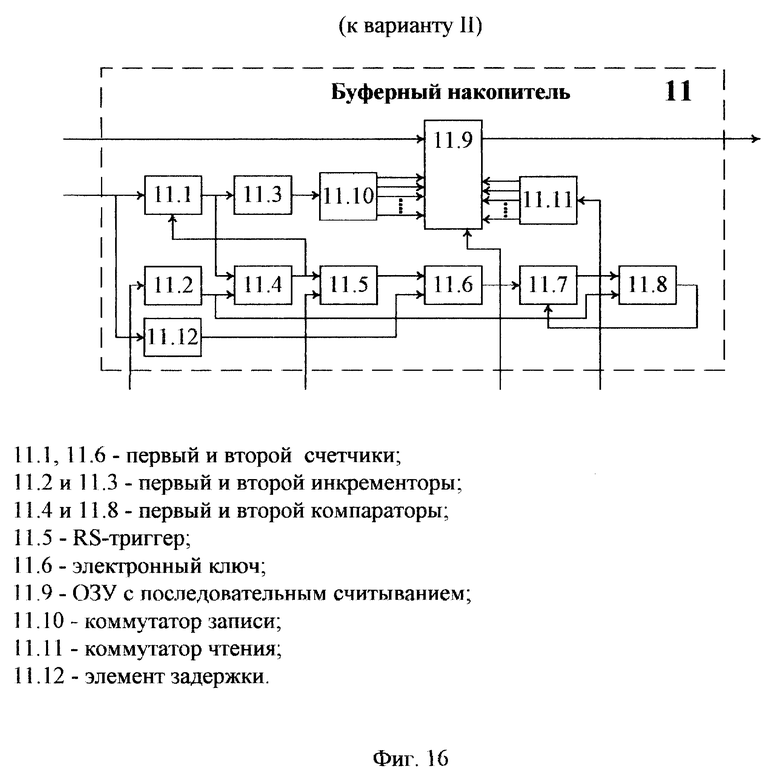

на фиг. 16 - структурная схема буферного накопителя;

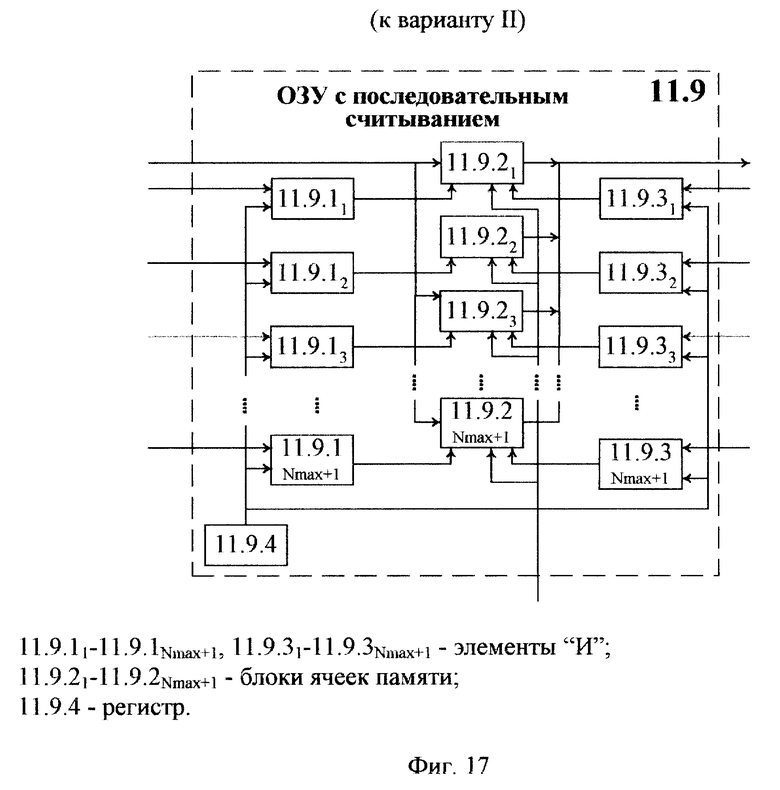

на фиг. 17 - структурная схема ОЗУ с последовательным считыванием;

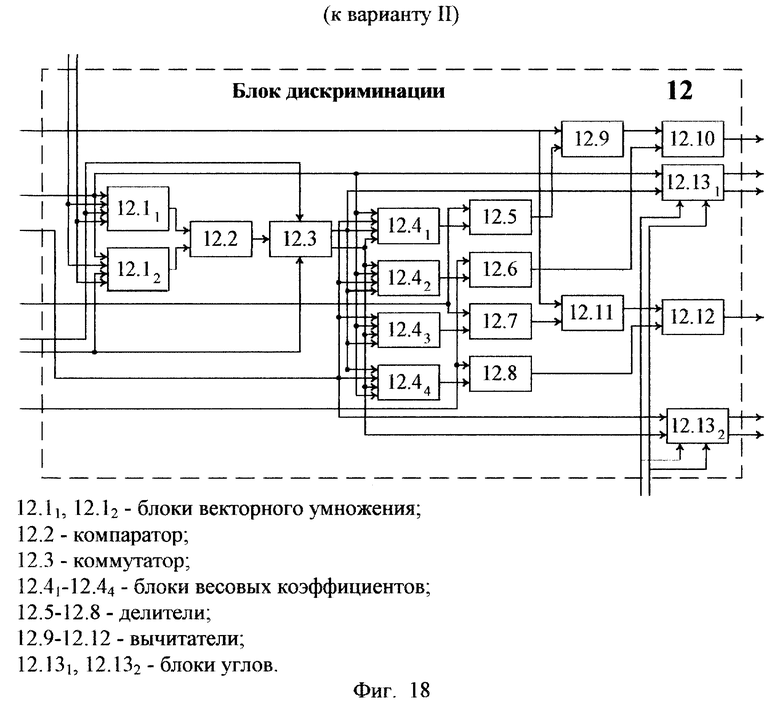

на фиг. 18 - структурная схема блока дискриминации (варианты). Вариант II;

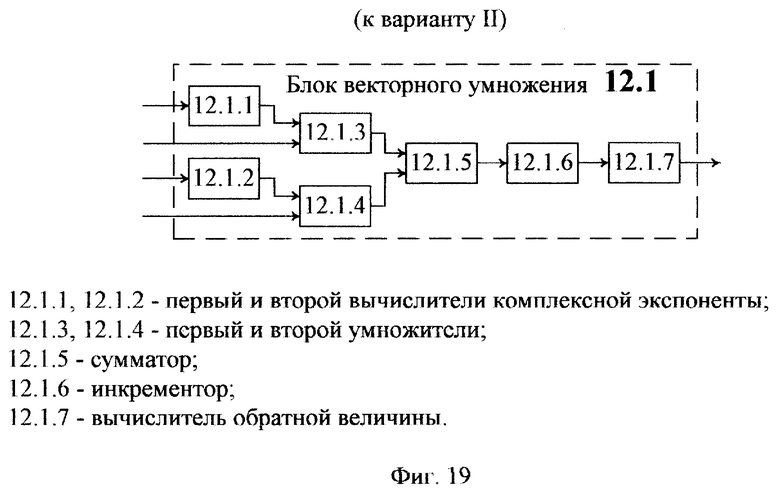

на фиг. 19 - структурная схема блока векторного умножения;

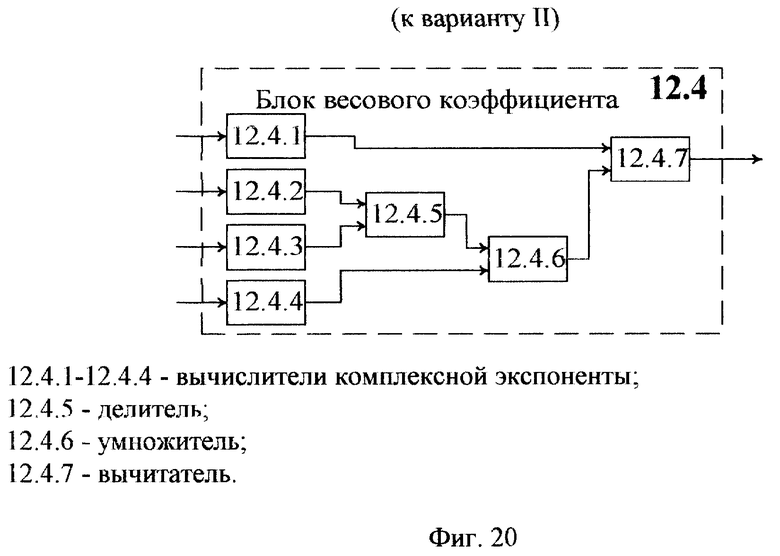

на фиг. 20 - структурная схема блока весового коэффициента;

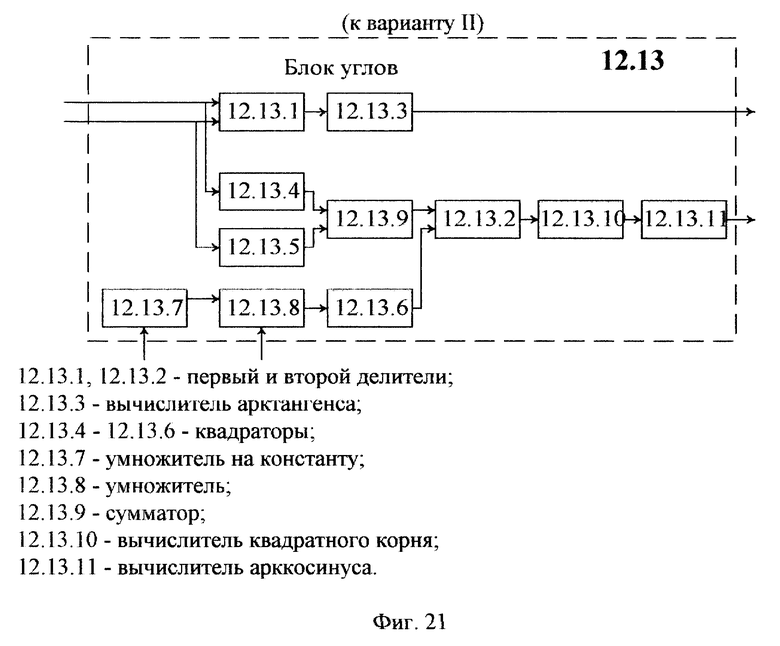

на фиг. 21 - структурная схема блока углов;

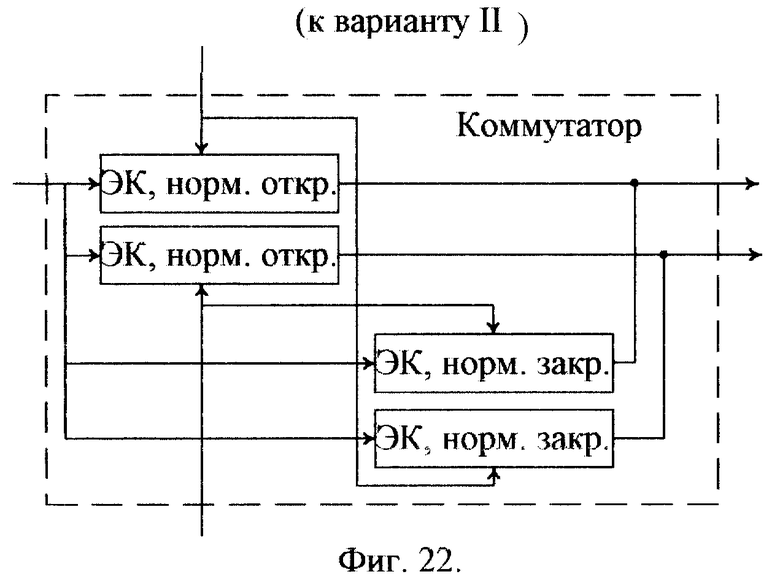

на фиг. 22 - пример реализации коммутатора;

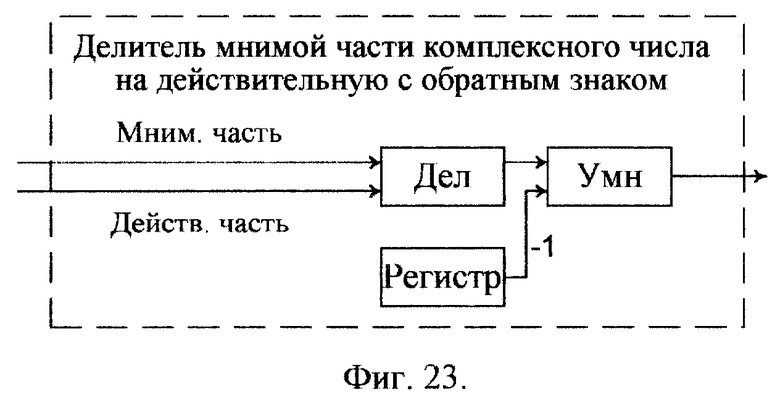

на фиг. 23 - пример реализации делителя мнимой части комплексного числа на его действительную с обратным знаком;

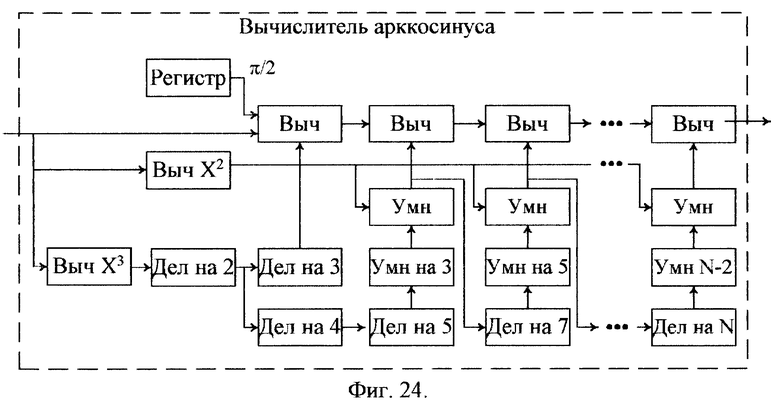

на фиг. 24 - пример вычислителя арккосинуса;

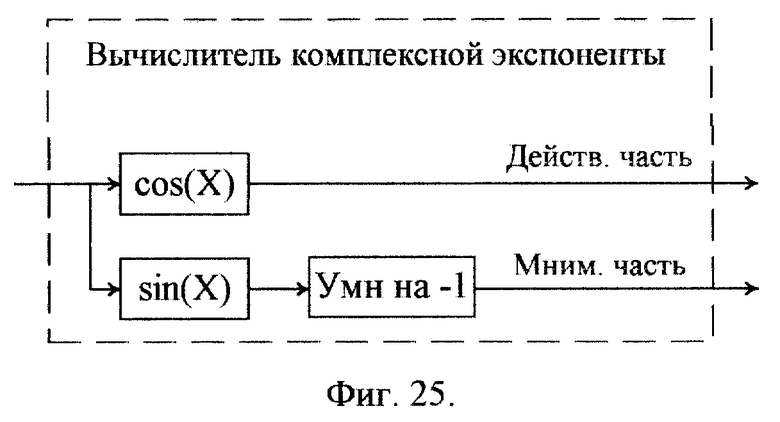

на фиг. 25 - пример реализации вычислителя комплексной экспоненты.

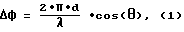

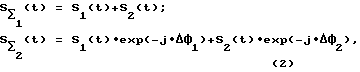

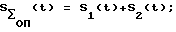

Заявленный цифровой радиопеленгатор (Вариант I), представленный на фиг. 1, состоит из антенного блока 1, включающего две антенны, обладающие в общем случае разными диаграммами направленности, разнесенные на расстояние d[м], определяющее диапазон длин волн пеленгатора, как λ[м]=2d[м], первого и второго радиоприемников 21 и 22, первого и второго аналого-цифровых преобразователей (АЦП) 31 и 32, блока управления (БУ) 4, первого и второго накопителей (Н) 51 и 52, первого и второго блоков квадратурного преобразования (БКП) 61 и 62, блока кумулянтной матрицы (БКМ) 7, блока матричной обработки (БМО) 8, блока фаз (БФ) 9, первого и второго элементов задержки (ЭЗ) 10 и 11, блока дискриминации (БД) 12 и блока опорных частот (БОЧ) 13. Сигнальные входы первого и второго радиоприемников 21 и 22 подключены к соответствующим антеннам антенного блока 1, их гетеродинные входы подключены к гетеродинному выходу БОЧ 11, выход кода частоты второго радиоприемника 22 соединен с одноименным входом БД 10, а сигнальные выходы обоих радиоприемников соединены соответственно с сигнальными входами первого и второго АЦП 31 и 32. Тактовые входы АЦП 31 и 32, Н 51 и 52, БКП 61 и 62, БКМ 7 и счетный вход БУ 4 подключены к выходу тактовой частоты БОЧ 11, а сигнальные выходы АЦП 31 и 32 соединены с соответствующими сигнальными входами БУ 4. Установочный выход БУ 4 соединен с одноименным входом БКМ 7. Выход "Количество" БУ 4 подключен к одноименным входам первого и второго БКП 61 и 62 и БКМ 7, а выход "База" соединен с одноименным входом БД 10. Кадровый выход БУ 4 подключен к кадровым входам первых и вторых Н 51 и 52. Первый и второй сигнальные выходы БУ 4 подключены к входам соответствующих Н 51 и 52. Выходы первого и второго Н 51 и 52 соединены с сигнальными входами первого и второго БКП 61 и 62. Сигнальные выходы первого и второго БКП 61 и 62 подключены к соответствующим входам первого и второго ЭЗ 10 и 11 и БКМ 7, синхронизирующий выход первого БКП 61 соединен с синхронизирующим входом БКМ 7, девять выходов которого подключены к соответствующим входам БМО 8. Первый и второй выходы БМО 8 подключены к соответствующим входам БФ 9, первый и второй выходы которого соединены соответственно с первым и вторым фазовыми входами БД 10. Выходы первого и второго ЭЗ подключены соответственно к первому и второму сигнальным входам БД 10, попарно объединенные первые азимутальный и сигнальный и вторые азимутальный и сигнальный выходы которого являются соответствующими выходами цифрового радиопеленгатора.

Блок управления (Вариант I), показанный на фиг. 2, предназначен для управления работой цифрового радиопеленгатора. БУ 4 включает кнопку "Измерение" 4.1, первый и второй счетчики (Сч) 4.2 и 4.5, датчик длины реализации 4.3, первый и второй компараторы (Комп) 4.4 и 4.6, датчик количества измерений 4.7, кнопку "Непрерывное измерение" 4.8, элемент И 4.9, элемент ИЛИ 4.10, кнопку "Сброс" 4.11, триггер 4.12, первый и второй электронные ключи (ЭК) 4.131 и 4.132 и датчик "База" 4.14. Выход датчика длины реализации 4.3 является выходом "Количество" БУ 4 и соединен с первым входом первого Комп 4.4. Счетный вход первого Сч 4.2 является счетным входом БУ 4, его выход соединен со вторым входом первого Комп 4.4. Выход первого Комп подключен к счетному входу второго Сч 4.5, к установочному входу первого Сч и, кроме того, является кадровым выходом БУ 4. Выход второго Сч 4.5 соединен со вторым входом второго Комп 4.6, первый вход которого соединен с выходом датчика количества измерений 4.7. Выход второго Комп 4.6 подключен ко второму входу элемента И 4.9, первый вход которого соединен с кнопкой "Непрерывное измерение" 4.8, а выход подключен ко второму входу элемента ИЛИ 4.10, первый вход которого соединен с кнопкой "Сброс" 4.11. Выход элемента ИЛИ подключен к установочному входу второго Сч 4.5 и к входу S RS-триггера 4.12, вход R которого подключен к кнопке "Измерение" 4.1. Выход триггера 4.12 соединен с управляющими входами первого и второго ЭК 4.131 и 4.132 и является установочным выходом БУ 4. Сигнальные входы первого и второго ЭК 4.131 и 4.132 являются соответственно первым и вторым сигнальными входами БУ 4, а их сигнальные выходы являются соответствующими сигнальными выходами БУ 4. Датчик "База" 4.14 соединен с одноименным выходом БУ 4.

Накопитель (Н) 5, показанный на фиг. 3, предназначен для накопления заданного в БУ 4 количества отсчетов сигнала и выдачи их для дальнейшей обработки в непрерывном режиме (без потерь). Н 5 включает Т-триггер 5.1, первый, второй, третий и четвертый ЭК 5.2-5.5, нормально закрытые, и первый и второй блоки ячеек памяти 5.6 и 5.7. Вход Т-триггера является кадровым входом Н 5, его первый выход соединен с управляющими входами первого и четвертого ЭК 5.2 и 5.5, входом "Запись" первого блока ячеек памяти 5.6 и входом "Считывание" второго блока памяти 5.7, а второй выход триггера соединен с управляющими входами второго и третьего ЭК 5.3 и 5.4, входом "Запись" второго блока ячеек памяти 5.7 и входом "Считывание" первого блока памяти 5.6. Сигнальный вход третьего ЭК 5.4 соединен с сигнальным входом первого ЭК 5.2, являющегося сигнальным входом Н 5. Выходы первого и третьего ЭК 5.2 и 5.4 соединены с сигнальными входами соответственно первого и второго блоков ячеек памяти 5.6 и 5.7, тактовые входы которых соединены и являются тактовым входом Н 5, а сигнальные выходы подключены к сигнальным входам соответственно второго и четвертого ЭК 5.3 и 5.5. Выходы второго и четвертого ЭК 5.3 и 5.5 соединены между собой и являются сигнальным выходом Н 5.

Блок квадратурного преобразования (БКП) 6, показанный на фиг. 4, предназначен для преобразования действительных значений отсчетов сигнала в комплексную форму. БКП 6 включает первый и второй блоки дискретного преобразования Фурье (ДПФ) 6.1 и 6.6, Сч 6.2, делитель (Дел) на два 6.3, Комп 6.4, ЭК 6.5 и инвертор (Инв) 6.7. Сигнальный вход первого блока ДПФ 6.1 является сигнальным входом БКП 6, его сигнальный выход соединен с сигнальным входом ЭК 6.5, выход которого соединен с сигнальным входом второго блока ДПФ 6.6. Тактовый вход второго блока ДПФ 6.6 подключен к тактовому входу первого блока ДПФ 6.1, являющегося тактовым входом БКП 6. Синхронизирующий выход первого блока ДПФ 6.1 соединен с установочным входом Сч 6.2, тактовый выход первого блока ДПФ 6.1 подключен к счетному входу Сч 6.2, выход которого соединен с первым входом Комп 6.4, второй вход которого соединен с выходом Дел на два 6.3, вход которого является входом "Количество" БКП 6. Выход первого Комп 6.4 подключен к управляющему входу ЭК 6.5. Синхронизирующий выход второго блока ДПФ 6.6 соединен с входом Инв 6.7, выход которого является синхронизирующим выходом БКП 6, а сигнальный выход второго блока ДПФ 6.6 является сигнальным выходом БКП 6.

Блок кумулянтной матрицы (Вариант I) предназначен для расчета по реализациям сигналов, принимаемых двухэлементной антенной таких кумулянтных функций 4-го порядка, значения которых с точностью до постоянного коэффициента совпадают со значениями соответствующих элементов ковариационной матрицы трехэлементной антенной системы. Его блок-схема представлена на фиг. 5. Она включает первый, второй, третий, четвертый и пятый Инв мнимой части соответственно 7.1-7.5, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой ЭЗ соответственно 7.6-7.13 и первый, второй, третий, четвертый, пятый и шестой КБ 7.141-7.146. Входы первого и второго ЭЗ 7.6 и 7.7 соединены с входами соответственно первого и второго Инв мнимой части 7.1 и 7.2, являющихся соответственно первым и вторым сигнальными входами БКМ 7. Выход первого Инв мнимой части 7.1 подключен к первым и третьим сигнальным входам первого, второго и третьего КБ 7.141-7.143 и к первым сигнальным входам четвертого и пятого КБ 7.144 и 7.145. Выход первого ЭЗ 7.6 подключен ко вторым сигнальным входам первого, второго и четвертого КБ 7.141, 7.142 и 7.144 и к четвертому сигнальному входу первого КБ 7.141. Выход второго Инв мнимой части 7.2 соединен с третьими сигнальными входами четвертого, пятого и шестого КБ 7.144-7.146 и с первым сигнальным входом шестого КБ 7.146. Выход второго ЭЗ 7.7 подключен к четвертым сигнальным входам второго, третьего, четвертого, пятого и шестого КБ 7.142-7.146 и ко вторым сигнальным входам третьего, пятого и шестого КБ 7.143, 7.145 и 7.146. Тактовые, установочные и синхронизирующие входы и входы "Количество" первого, второго, третьего, четвертого и пятого КБ 7.161-7.165 соединены с соответствующими входами шестого КБ 7.166, являющимися соответственно тактовым, установочным, синхронизирующим входами и входом "Количество" БКМ 7. Выход первого КБ 7.141 подключен к входу третьего ЭЗ 7.8. Выход второго КБ 7.142 соединен с входами четвертого ЭЗ 7.9 и третьего Инв мнимой части 7.3. Выход третьего КБ 7.143 соединен с входами пятого ЭЗ 7.10 и четвертого Инв мнимой части 7.4. Выход четвертого КБ 7.144 соединен с входом шестого ЭЗ 7.11. Выход пятого КБ 7.145 соединен с входами седьмого ЭЗ 7.12 и пятого Инв мнимой части 7.5. Выход шестого КБ 7.146 соединен с

входом восьмого ЭЗ 7.13. Выходы третьего ЭЗ 7.8, четвертого ЭЗ 7.9, третьего Инв мнимой части 7.3, пятого ЭЗ 7.10, четвертого Инв мнимой части 7.4, шестого и седьмого ЭЗ 7.11 и 7.12, пятого Инв мнимой части 7.5 и восьмого ЭЗ 7.13 являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами блока кумулянтной матрицы.

Кумулянтный блок 7.14 предназначен для расчета значения кумулянтной функции четвертого порядка. Его структурная схема представлена на фиг.6 и состоит из первого, второго, третьего, четвертого, пятого, шестого, седьмого 7.14.1-7.14.7, восьмого, девятого и десятого умножителей (Умн) 7.14.9-7.14.11, первого, второго, третьего, четвертого, пятого, шестого и седьмого усреднителей 7.14.81 - 7.14.87, первого и второго сумматоров (Сум) 7.14.12 и 7.14.13, ЭЗ 7.14.14 и вычитателя (Выч) 7.14.15. Первые входы третьего и четвертого Умн 7.14.3 и 7.14.4 соединены с входом первого Умн 7.14.1. являющегося первым сигнальном входом КБ 7.14. Второй вход первого и первый вход пятого Умн 7.14.1 и 7.14.5 подключены к первому входу второго Умн 7.14.2, являющегося вторым сигнальным входом КБ 7.14. Второй вход второго и первый вход шестого Умн 7.14.2 и 7.14.6 соединены со вторым входом третьего Умн 7.14.3, являющегося третьим сигнальным входом КБ 7.14. Вторые входы четвертого и пятого Умн 7.14.4 и 7.14.5 подключены ко второму входу шестого Умн 7.14.6, являющегося четвертым сигнальным входом КБ. Выход первого Умн 7.14.1 подключен к сигнальному входу второго усреднителя 7.14.82 и к первому входу седьмого Умн 7.14.7, второй вход которого соединен с выходом шестого Умн 7.14.6, причем выход седьмого Умн подключен к сигнальному входу первого усреднителя 7.14.81. Выходы второго, третьего, четвертого, пятого и шестого Умн 7.14.2 - 7.14.6 подключены к сигнальным входам соответственно третьего, четвертого, пятого, шестого и седьмого усреднителей 7.14.83-7.14.87. Тактовые, установочные, синхронизирующие входы и входы "Количество" усреднителей 7.14.81 - 7.14.86 соединены с соответствующими входами усреднителя 7.14.87, являющимися тактовыми, установочными, синхронизирующими входами и входом "Количество" КБ 7.14. Выход первого усреднителя 7.14.81 через ЭЗ 7.14.14 соединен с первым входом Выч 7.14.15. Выход второго усреднителя 7.14.82 подключен к первому входу восьмого Умн 7.14.9, второй вход которого соединен с выходом седьмого усреднителя 7.14.87, причем выход восьмого Умн 7.14.9 подключен к первому входу первого Сум 7.14.12. Выход третьего усреднителя 7.14.83 соединен с первым входом девятого Умн 7.14.10, второй вход которого подключен к выходу пятого усреднителя 7.14.85, причем выход девятого Умн 7.14.10 соединен со вторым входом первого Сум 7.14.12, выход которого подключен к первому входу второго Сум 7.14.13. Выход четвертого усреднителя 7.14.84 соединен с первым входом десятого Умн 7.14.11, второй вход которого подключен к выходу шестого усреднителя 7.14.86, а выход десятого Умн 7.14.11 соединен со вторым входом второго Сум 7.14.13, выход которого подключен ко второму входу Выч 7.14.15. Выход Выч 7.14.15 является выходом КБ 7.14.

Усреднитель 7.14.8 предназначен для расчета среднего арифметического значения (выборочного математического ожидания) входной последовательности отсчетов. Его блок-схема представлена на фиг. 7 и состоит из сумматора-накопителя 7.14.8.1, делителя (Дел) 7.14.8.2, первого и второго ЭЗ 7.14.8.3 и 7.14.8.7, ЭК 7.14.8.4, Сч 7.14.8.5, Комп 7.14.8.6, элемента ИЛИ 7.14.8.8 и Инв 7.14.8.9. Сигнальный вход сумматора-накопителя 7.14.8.1 является сигнальным входом усреднителя 7.14.8. Вход первого ЭЗ является синхронизирующим входом, сигнальный вход ЭК 7.14.8.4 является тактовым входом, а вход Инв 7.14.8.9 является установочным входом усреднителя 7.14.8. Выход Инв 7.14.8.9 подключен ко второму входу элемента ИЛИ 7.14.8.8. Второй вход Дел 7.14.8.2 соединен со вторым входом Комп 7.14.8.6, являющегося входом "Количество" усреднителя 7.14.8. Выход первого ЭЗ 7.14.8.3 соединен с управляющим входом ЭК 7.14.8.4, выход которого подключен к счетному входу Сч 7.14.8.5. Выход Сч 7.14.8.5 соединен с первым входом Комп 7.14.8.6, выход которого подключен к установочному входу Сч 7.14.8.5, входу второго ЭЗ 7.14.8.7 и к разрешающему входу сумматора-накопителя 7.14.8.1. Выход второго ЭЗ 7.14.8.7 соединен с первым входом элемента ИЛИ 7.14.8.8, выход которого подключен к управляющему входу сумматора-накопителя 7.14.8.1, выход которого соединен с первым входом Дел 7.14.8.2. Выход Дел 7.14.8.2 является выходом усреднителя 7.14.8.

Блок фаз 9 (Вариант I) предназначен для расчета значений пространственных разностей фаз двух сигналов на первой и второй антеннах антенного блока 1. Его блок-схема представлена на фиг. 8 и состоит из Дел на минус два 9.1, квадратора (Кв) 9.2, Умн на четыре 9.3, первого и второго Выч 9.4 и 9.8, вычислителя квадратного корня 9.5, Дел на два 9.6 и Сум 9.7. Вход Кв 9.2 соединен с входом Дел на минус два 9.1, являющегося первым входом БФ 9, а вход Умн на четыре 9.3 является вторым входом БФ 9. Выход Дел на минус два 9.1 соединен с первыми входами Сум 9.7 и второго Выч 9.8. Выход Кв 9.2 подключен к первому входу первого Выч 9.4, второй вход которого соединен с выходом Умн на четыре 9.3, причем выход первого Выч 9.4 через вычислитель квадратного корня 9.5 подключен к входу Дел на два 9.6. Выход Дел на два 9.6 соединен со вторыми входами Сум 9.7 и второго Выч 9.8, выходы которых являются соответственно первым и вторым выходами блока фаз 9.

Блок дискриминации 10 (Вариант I) предназначен для разделения сигналов, принимаемых двухэлементной антенной, определения их азимутов и идентификации рассчитанных значений азимутов с принимаемыми сигналами. Его блок-схема представлена на фиг. 9 и включает первый, второй, третий и четвертый Дел 10.1- 10.4, первый и второй Выч 10.5 и 10.6, первый и второй Дел мнимой части комплексного числа на его действительную с обратным знаком 10.7 и 10.8, первый и второй вычислители арктангенса 10.9 и 10.10, Умн 10.11, Умн на константу 10.12, а также первый и второй вычислители арккосинуса 10.13 и 10.14. Первый вход первого Дел 10.1 соединен с первым входом второго Дел 10.2, являющегося вторым сигнальным входом БД 10. Вход второго Дел мнимой части комплексного числа на действительную с обратным знаком 10.8 соединен со вторым входом первого Дел 10.1, являющегося первым фазовым входом БД 10. Вход первого Дел мнимой части комплексного числа на действительную с обратным знаком 10.7 соединен со вторым входом второго Дел 10.2, являющегося вторым фазовым входом БД 10. Первый вход второго Выч 10.6 соединен с первым входом первого Выч 10.5, являющегося первым сигнальным входом БД 10. Выходы первого и второго Дел 10.1 и 10.2 подключены ко вторым входам соответственно первого и второго Выч 10.5 и 10.6. Выходы первого и второго Дел мнимой части комплексного числа на его действительную с обратным знаком 10.7 и 10.8 подключены к входам соответствующих вычислителей арктангенса 10.9 и 10.10, выходы которых соединены с первыми входами соответственно третьего и четвертого Дел 10.3 и 10.4. Первый вход Умн 10.11 является входом "База" БД 10, его второй вход является входом кода частоты БД 10, а выход Умн 10.11 через Умн на константу 10.12 соединен со вторыми входами третьего и четвертого Дел 10.3 и 10.4, выходы которых подключены к входам соответствующих вычислителей арккосинуса 10.13 и 10.14. Выходы первого и второго вычислителей арккосинуса 10.13 и 10.14 являются соответствующими азимутальными выходами БД 10, а выходы первого и второго Выч 10.5 и 10.6 являются соответствующими сигнальными выходами БД 10. Попарно сгруппированные первые и вторые сигнальные и азимутальные выходы БД 10 являются соответствующими выходами цифрового радиопеленгатора.

Ряд блоков цифрового радиопеленгатора по назначению и выполняемым функциям идентичны одноименным блокам прототипа, а именно радиоприемники 21 и 22, АЦП 31 и 32 и БМО. Таким образом, данные блоки могут быть реализованы так же, как и блоки прототипа [5]. Примеры реализации на базе известных логических элементов сумматора, счетчика, компаратора приведены в [6 на стр. 115, 129, 113 соответственно]. Известно, что на основе сумматора, преобразователей основного кода двоичных чисел в обратный и дополнительный коды и регистров [6, стр. 124] в соответствии с известными правилами [6, 7, 10] могут быть синтезированы вычитатель, умножитель, делитель, умножитель на константу, умножитель на мнимую единицу, делитель на константу, квадратор, вычислитель квадратного корня, в том числе и для комплексных чисел, сумматор, умножитель и делитель комплексных чисел. Примеры реализации перечисленных элементов приведены в [5] на фиг. 24-42. По известным правилам [6, 7, 10] на базе известных схем элементов могут быть построены схемы Дел мнимой части комплексного числа на его действительную с обратным знаком и вычислителя арккосинуса. Примеры их реализации приведены на фиг. 22 и 23. Схемы ЭЗ также известны и описаны в [6,10]. В частности, они могут быть реализованы на основе D-триггеров.

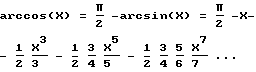

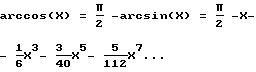

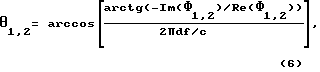

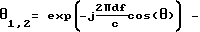

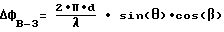

Вычисление арккосинуса производится по формуле разложения в степенной ряд [8, стр. 624]

Заявленный цифровой радиопеленгатор (Вариант II), представленный на фиг. 10, состоит из антенного блока 1, включающего три антенны, в общем случае имеющие разные диаграммы направленности, установленные в вершинах прямоугольного треугольника, ориентированного по сторонам света, причем минимальное расстояние между парой антенн определяет диапазон длин волн пеленгатора как λ[м]≥2dmin[м], первых, вторых и третьих радиоприемников 21-23 и аналого-цифровых преобразователей (АЦП) 31-33, блока управления (БУ) 4, первого, второго и третьего накопителей (Н) 51-53, первого, второго и третьего блоков квадратурного преобразования (БКП) 61-63, блока кумулянтной матрицы (БКМ) 7, сумматора-накопителя скользящего окна 8, блока матричной обработки (БМО) 9, блока фаз (БФ) 10, первого, второго и третьего буферных накопителей (БН) 111-113, блока дискриминации (БД) 12 и блока опорных частот (БОЧ) 13. Сигнальные входы первого, второго и третьего радиоприемников 21-23 подключены к соответствующим антеннам антенного блока 1, причем антенна, установленная в вершине прямого угла (опорная антенна), подключена к сигнальному входу первого радиоприемника 21, антенна, установленная к северу от опорной, подключена к сигнальному входу второго радиоприемника 22, а антенна, установленная к востоку от опорной, подключена к сигнальному входу третьего радиоприемника 23. Гетеродинные входы первого, второго и третьего радиоприемников 21-23 подключены к гетеродинному выходу БОЧ 11, выход кода частоты третьего радиоприемника 23 соединен с одноименным входом БД 10, а сигнальные выходы первого, второго и третьего радиоприемников соединены соответственно с сигнальными входами первого, второго и третьего АЦП 31-33. Тактовые входы АЦП 31-32, Н 51-53, БКП 61-63, БКМ 7, сумматора-накопителя скользящего окна 8, БН 111-113 и счетный вход БУ 4 подключены к выходу тактовой частоты БОЧ 11, а сигнальные выходы АЦП 31-33 соединены с соответствующими сигнальными входами БУ 4. Установочный выход БУ 4 соединен с одноименными входами БКП 61-63 и БКМ 7, сумматора-накопителя скользящего окна 8 и первого, второго и третьего БН 111-113. Выход "Количество" БУ 4 подключен к одноименным входам БКМ 7, выход "Длина окна" подключен к одноименным входам сумматора-накопителя скользящего окна 8 и первого, второго и третьего БН 111-113, а выход "База" соединен с одноименным входом БД 10. Кадровый выход БУ 4 подключен к одноименным входам первого, второго и третьего Н 51-53. Первый, второй и третий сигнальные выходы БУ 4 подключены к сигнальным входам соответствующих Н 53- 53. Выходы первого, второго и третьего Н 51-53 соединены с сигнальными входами первого, второго и третьего БКП 61-63. Сигнальные выходы первого, второго и третьего БКП 61-63 подключены к сигнальным входам соответственно первого, второго и третьего БН 111-113 и соответствующим сигнальным входам БКМ 7, синхронизирующий вход первого БКП 61 соединен с синхронизирующими входами БКМ 7, сумматора-накопителя скользящего окна 8 и БН 111-113. Девять выходов БКМ 7 подключены к соответствующим сигнальным входам сумматора-накопителя скользящего окна 8, девять выходов которого соединены с соответствующими входами БМО 9. Первый и второй выходы БМО 9 подключены шинами комплексных данных к первому и второму входам собственного вектора БД 12 и к входам БФ 10, причем к первому и третьему входам БФ 10 подключены те части шин комплексных данных, по которым передаются действительные части комплексных чисел, а со вторым и четвертым входами БФ 10 соединены те части шин комплексных данных, по которым передаются мнимые части комплексных чисел. Первый и второй выходы "Север-юг" БФ 10 соединены соответственно с первым и вторым входами "Север-юг" БД 12, а первый и второй выходы "Восток-запад" БФ 10 соединены соответственно с первым и вторым входами "Восток-запад" БД 12. Выходы первого, второго и третьего БН 111-113 подключены к соответствующим сигнальным входам БД 12, сгруппированные по три первые и вторые сигнальный, азимутальный и угломестные выходы которого являются соответствующими выходами цифрового радиопеленгатора.

Блок управления (Вариант II), показанный на фиг. 11, предназначен для управления работой цифрового радиопеленгатора. БУ 4 включает кнопку "Измерение" 4.1, первый и второй Сч 4.2 и 4.5, датчик длины реализации 4.3, первый и второй Комп 4.4 и 4.6, датчик количества измерений 4.7, кнопку "Непрерывное измерение" 4.8, элемент И 4.9, элемент ИЛИ 4.10, кнопку "Сброс" 4.11, триггер 4.12, первый, второй и третий электронные ключи (ЭК) 4.131-4.132, датчик "База" 4.14, датчик длины скользящего окна 4.15 и умножитель 4.16. Выход датчика длины реализации 4.3 является выходом "Количество" БУ 4 и соединен с первым входом первого Комп 4.4. Выход датчика длины скользящего окна 4.15 соединен с вторым входом умножителя 4.16 и является выходом "Длина окна" БУ 4. Счетный вход первого Сч 4.2 является счетным входом БУ 4, его выход соединен со вторым входом первого Комп 4.4. Выход первого Комп подключен к счетному входу второго Сч 4.5, к установочному входу первого Сч и, кроме того, является кадровым выходом БУ 4. Выход второго Сч 4.5 соединен со вторым входом второго Комп 4.6. Выход датчика количества измерений 4.7 подключен к первому входу умножителя 4.16, его выход соединен с первым входом второго Комп 4.6, выход которого подключен ко второму входу элемента И 4.9, первый вход которого соединен с кнопкой "Непрерывное измерение" 4.8, а выход подключен ко второму входу второго элемента ИЛИ 4.10, первый вход которого соединен с кнопкой "Сброс" 4.11. Выход второго элемента ИЛИ подключен к установочному входу второго Сч 4.5 и к входу S RS-триггера 4.12, вход R которого подключен к кнопке "Измерение" 4.1. Выход триггера 4.12 соединен с управляющими входами первого и второго ЭК 4.131 и 4.132 и является установочным выходом БУ 4. Сигнальные входы первого и второго ЭК 4.131 и 4.132 являются соответственно первым и вторым сигнальными входами БУ 4, а их выходы являются соответствующими сигнальными выходами БУ 4. Выход датчика "База" 4.14 является выходом "База" БУ 4.

Блок кумулянтной матрицы 7 (Вариант II) предназначен для расчета по реализациям сигналов, принимаемых трехэлементной антенной, таких кумулянтных функций 4-го порядка, значения которых с точностью до постоянного коэффициента совпадают со значениями соответствующих элементов ковариационной матрицы трехэлементной антенной системы. Блок кумулянтной матрицы показан на фиг. 12 и состоит из первого, второго, третьего, четвертого, пятого и шестого Инв мнимой части 7.1-7.6, первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого ЭЗ 7.7- 7.15 и первого, второго, третьего, четвертого, пятого и шестого КБ 7.161-7.166. Входы первого, второго и третьего ЭЗ 7.7-7.9 соединены с входами соответственно первого, второго и третьего Инв мнимой части 7.1-7.3, являющихся соответственно первым, вторым и третьим сигнальными входами БКМ 7. Выход первого Инв мнимой части 7.1 соединен с первыми сигнальными входами первого, второго, третьего, четвертого, пятого и шестого КБ 7.161-7.166 и с третьими сигнальными входами первого, второго и третьего КБ 7.161-7.163. Выход первого ЭЗ 7.7 подключен ко вторым сигнальным входам первого, второго, третьего, четвертого, пятого и шестого КБ 7.161-7.166 и к четвертому сигнальному входу первого КБ 7.161. Выход второго Инв мнимой части 7.2 соединен с третьими сигнальными входами четвертого и пятого КБ 7.164 и 7.165, а выход второго ЭЗ 7.8 подключен к четвертым сигнальным входам второго и четвертого КБ 7.162 и 7.164. Выход третьего Инв мнимой части 7.3 соединен с третьим сигнальным входом шестого КБ 7.166, а выход третьего ЭЗ 7.9 подключен к четвертым сигнальным входам третьего, пятого и шестого КБ 7.163, 7.165 и 7.166. Тактовые, установочные и синхронизирующие входы и входы "Количество" первого, второго, третьего, четвертого и пятого КБ 7.161-7.165 соединены с соответствующими входами шестого КБ 7.166, являющимися соответственно тактовым, установочным и синхронизирующим входами и входом "Количество" БКМ 7. Выход первого КБ 7.161 соединен с входом четвертого ЭЗ 7.10, выход второго КБ 7.162 подключен к входам пятого ЭЗ 7.11 и четвертого Инв мнимой части 7.4, выход третьего КБ 7.163 соединен с входами шестого ЭЗ 7.12 и пятого Инв мнимой части 7.5, выход четвертого КБ 7.164 подключен к входу седьмого ЭЗ 7.13, выход пятого КБ 7.165 соединен с входами восьмого ЭЗ 7.14 и шестого Инв мнимой части 7.6, а выход шестого КБ 7.166 подключен к входу девятого ЭЗ 7.15. Выходы четвертого 7.10, пятого ЭЗ 7.11, четвертого Инв мнимой части 7.4, шестого ЭЗ 7.12, пятого Инв мнимой части 7.5, седьмого и восьмого ЭЗ 7.13 и 7.14, шестого Инв мнимой части 7.6 и девятого ЭЗ 7.15 являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами БКМ 7.

Схемы кумулянтных блоков и усреднителей идентичны рассмотренным в первом варианте. Цифровые схемы Сум, Выч, Умн, Дел, сумматора-накопителя, Комп, Сч и Инв мнимой части комплексного числа известны и описаны, например, в [6]. Схемы ЭЗ также известны и описаны, например, в [6, 10]. В частности, они могут быть реализованы на основе D-триггеров.

Сумматор-накопитель скользящего окна 8 предназначен для усреднения заданного в БУ 4 количества (N) кумулянтных матриц, что обеспечивает возможность разделения частично коррелированных сигналов, причем после накопления N кумулянтных матриц каждая последующая матрица, поступающая на его вход, замещает наиболее старую. Его блок-схема представлена на фиг. 13 и включает Сч 8.1, инкрементор 8.2, Комп 8.3, коммутатор записи 8.4, RS-триггер 8.5, элемент И 8.6, оперативное запоминающее устройство (ОЗУ) с параллельным считыванием 8.7, Nmax Сум первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого каналов 8.81 - 8.8Nmax, 8.91 - 8.9Nmax, 8.101 - 8.10Nmax, 8.111 - 8.11Nmax, 8.121 - 8.12Nmax, 8.131 - 8.13Nmax, 8.141 - 8.14Nmax, 8.151 - 8.15Nmax, 8.161 - 8.16Nmax. Первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый сигнальные входы ОЗУ с параллельным считыванием 8.7 являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым сигнальными входами сумматора-накопителя скользящего окна 8, его тактовый вход является тактовым входом сумматора-накопителя скользящего окна 8. Второй вход элемента И 8.6 соединен со счетным входом Сч 8.1, являющимся синхронизирующим входом сумматора-накопителя скользящего окна 8, вход инкрементора 8.2 является входом "Длина окна" сумматора-накопителя скользящего окна 8. Установочный вход ОЗУ с параллельным считыванием соединен с входом S RS-триггера 8.5, являющегося установочным входом сумматора-накопителя скользящего окна 8. Выход инкрементора 8.2 соединен со вторым входом Комп 8.3, выход Сч 8.1 подключен к первому входу Комп 8.3 и к управляющему входу коммутатора записи 8.4. Первый, второй,..., Nmax, Nmax+1 выходы коммутатора записи 8.4 соединены с первым, вторым,..., Nmax, Nmax+1 входами "Разрешение записи" ОЗУ с параллельным считыванием 8.7. Выход Комп 8.3 соединен с установочным входом Сч 8.1 и входом R RS-триггера 8.5. Выход триггера 8.5 подключен к первому входу элемента И 8.6, выход которого соединен с входом "Разрешение чтения" ОЗУ с параллельным считыванием 8.7. ОЗУ с параллельным считыванием 8.7 имеет 9 групп по Nmax+1 выходов, где Nmax - максимальное количество матриц, используемых для временного сглаживания. Первые выходы ОЗУ с параллельным считыванием 8.7 каждой группы соединены с первыми входами первых Сум соответствующих каналов, вторые, третьи,..., Nmax и Nmax+1 выходы ОЗУ с параллельным считыванием второй, третьей,..., девятой групп подключены ко вторым входам вторых, третьих,..., Nmax-1 и Nmax Сум соответствующих каналов. Выходы первых, вторых, третьих, . .., Nmax-2 и Nmax-1 Сум каналов соединены с первыми входами i-1 и i, i=1...Nmax Сум, причем выходы Nmax Сум первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого каналов являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым выходами сумматора-накопителя скользящего окна 8.

ОЗУ с параллельным считыванием 8.7 предназначено для записи, хранения и выдачи значений элементов до N кумулянтных матриц. Его блок-схема представлена на фиг. 14 и включает Nmax+1 элементов И 8.9.11-8.9.1Nmax+1, Nmax+1 блоков памяти 8.9.21-8.9.2Nmax+1 и регистр 8.9.3. Первые, вторые, третьи, четвертые, пятые, шестые, седьмые, восьмые и девятые сигнальные входы второго, третьего,..., Nmax, Nmax+1 блоков памяти 8.9.22-8.9.2Nmax+1 соединены с первыми, вторыми, третьими, четвертыми, пятыми, шестыми, седьмыми, восьмыми и девятыми входами первого блока памяти 8.9.21, являющимися соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым и девятым сигнальными входами ОЗУ с параллельным считыванием 8.9. Первые входы первого, второго, . . ., Nmax+1 элементов И 8.9.11-8.9.1Nmax+1 являются соответствующими входами "Разрешение записи" ОЗУ с параллельным считыванием, их вторые входы соединены с выходом регистра 8.9.3. Выходы первого, второго,... , Nmax+1 элементов И 8.9.11-8.9.1Nmax+1 подключены к входам "Разрешение записи" соответственно первого, второго,..., Nmax+1 блоков памяти 8.9.21-8.9.2Nmax+1. Тактовые, установочные входы и входы "Разрешение чтения" блоков памяти 8.9.21-8.9.2Nmax+1 соединены с тактовым, установочным входами и входом "Разрешение чтения" блока памяти 8.9.2Nmax, являющимися тактовым, установочным входами и входом "Разрешение чтения" ОЗУ с параллельным считыванием 8.9. Первые, вторые, . . ., девятые выходы первого, второго,..., Nmax+1 блоков памяти 8.9.21-8.9.2Nmax+1 являются соответственно первыми, вторыми,..., девятыми Nmax+1 выходами ОЗУ с параллельным считыванием.

Блок фаз 10 (Вариант II) предназначен для расчета пространственной разности фаз каждого из двух сигналов, имеющих разные азимуты и углы места, принимаемых трехэлементной антенной системой, элементы которой установлены в вершинах прямоугольного треугольника. Его структурная схема показана на фиг. 15 и состоит из первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого Выч 10.1-10.9, первого, второго, третьего, четвертого, пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого Сум 10.10-10.20, первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого Кв 10.22-10.28, первого, второго, третьего, четвертого и пятого Умн на два 10.30-10.33, первого, второго, третьего и четвертого Умн 10.34-10.37, первого и второго инкременторов 10.38 и 10.39, первого и второго декременторов 10.40 и 10.41, первого, второго, третьего и четвертого Дел 10.42-10.45, первого, второго, третьего и четвертого вычислителей арктангенса 10.46-10.49 и вычислителя квадратного корня 10.50. Входы первого Умн на два 10.29, первого Кв 10.21 и первый вход первого Сум 10.10 соединены с первым входом первого Выч 10.1, являющегося первым входом блока фаз 10. Первые входы второго Сум 10.11, второго Выч 10.2 и вход второго Умн на два 10.30 подключены к входу второго Кв 10.22, являющегося вторым входом блока фаз 10. Вторые входы первых Выч 10.1 и Сум 10.10 и вход третьего Умн на два 10.31 соединены с входом третьего Кв 10.23, являющегося третьим входом блока фаз 10. Вторые входы вторых Выч 10.2 и Сум 10.11 и четвертого Умн на два 10.32 соединены с входом четвертого Кв 10.24, являющегося четвертым входом блока фаз 10. Выход первого Выч 10.1 подключен к входу пятого Кв 10.25, его выход соединен с первым входом первого Умн 10.34, выход первого Сум 10.10 подключен к входу шестого Кв 10.26, его выход соединен со вторым входом первого Умн 10.34, выход которого подключен к первому входу шестого Сум 10.15. Выход второго Выч 10.2 соединен с входом седьмого Кв 10.27, его выход подключен к первому входу второго Умн 10.35, выход второго Сум 10.11 соединен с входом восьмого Кв 10.28, выход которого подключен ко второму входу второго Умн 10.35, его выход соединен со вторым входом шестого Сум 10.15, выход которого подключен к первому входу седьмого Выч 10.7. Выход первого Кв 10.21 соединен с первыми входами пятого Выч 10.5 и третьего Умн 10.36, выход второго Кв 10.22 подключен к первым входам третьего Сум 10.12 и четвертого Выч 10.4 и ко второму входу третьего Выч 10.3. Выход четвертого Кв 10.24 соединен со вторыми входами третьего Сум 10.12 и четвертого Выч 10.4 и с первым входом третьего Выч 10.3. Выход третьего Выч 10.3 подключен к входам первых инкрементора 10.38 и декрементора 10.40, выход четвертого Выч 10.4 соединен с входом второго инкрементора 10.39. Выход первого инкрементора 10.38 подключен ко второму входу третьего Умн 10.36 и к первому входу седьмого Сум 10.16, а выход второго инкрементора 10.39 соединен с первым входом четвертого Умн 10.37, выход третьего Кв 10.23 подключен ко вторым входам пятого Выч 10.5 и четвертого Умн 10.37, а выходы третьего и четвертого Умн 10.36 и 10.37 соединены соответственно с первым и вторым входами четвертого Сум 10.13. Выход четвертого Сум 10.13 подключен ко второму входу пятого Сум 10.14, первый вход которого соединен с выходом третьего Сум 10.12, а выход пятого Сум 10.14 подключен к входу пятого Умн на два 10.33. Выход пятого Умн на два 10.33 через второй декрементор 10.41 подключен ко второму входу седьмого Выч 10.7, выход которого соединен с входом вычислителя квадратного корня 10.50, его выход подключен ко вторым входам десятого и одиннадцатого Сум 10.19 и 10.20 и восьмого и девятого Выч 10.8 и 10.9. Выход второго Умн на два 10.30 соединен с первыми входами десятого Сум 10.19 и восьмого Выч 10.8, выход четвертого Умн на два 10.32 подключен к первым входам одиннадцатого Сум 10.20 и девятого Выч 10.9, выходы десятого и одиннадцатого Сум 10.19 и 10.20 соединены с первыми входами соответственно первого и третьего Дел 10.42 и 10.44, а выходы восьмого и девятого Выч 10.8 и 10.9 подключены к первым входам второго и четвертого Дел 10.43 и 10.45. Выход пятого Выч 10.5 соединен со вторым входом седьмого 10.16 и первым входом восьмого Сум 10.17, выход седьмого Сум 10.16 подключен к первому входу шестого Выч 10.6, второй вход которого соединен с выходом первого Умн на два 10.29, а выход подключен ко вторым входам первого и второго Дел 10.42 и 10.43, второй вход восьмого Сум 10.17 соединен с выходом первого декрементора 10.40, выход восьмого Сум 10.17 подключен к первому входу девятого Сум 10.18, его второй вход соединен с выходом третьего Умн на два 10.31, а выход девятого Сум 10.18 подключен ко вторым входам третьего и четвертого Дел 10.44 и 10.45. Выходы первого, второго, третьего и четвертого Дел 10.42-10.45 соединены с входами соответственно первого, второго, третьего и четвертого вычислителей арктангенса 10.46-10.49, причем выходы первого и второго вычислителей арктангенса 10.46 и 10.47 являются соответственно первым и вторым выходами "Север-юг" блока фаз, а выходы третьего и четвертого вычислителей арктангенса 10.49 и 10.49 являются соответственно первым и вторым выходами "Восток-Запад" блока фаз 10.

Буферный накопитель 11 предназначен для записи, хранения заданного количества последовательностей комплексных отсчетов сигналов и последовательной их передачи в БД 12 в порядке поступления одновременно с поступлением на вход БД 12 значений разностей фаз. Его блок-схема представлена на фиг. 16 и включает первый и второй Сч 11.1 и 11.7, первый и второй инкременторы 11.2 и 11.3, первый и второй Комп 11.4 и 11.8, RS-триггер 11.5, ЭК 11.6, ОЗУ с последовательным считыванием 11.9, коммутатор записи 11.10, коммутатор считывания 11.11 и ЭЗ 11.12. Сигнальный вход ОЗУ с последовательным считыванием 11.9 является сигнальным входом БН 11, его тактовый вход является тактовым входом БН 11, вход S RS-триггера 11.4 является установочным входом БН 11, а вход первого инкрементора 11.2 является входом "Длина окна" БН 11. Вход ЭЗ 11.12 соединен со счетным входом первого Сч 11.1, являющегося синхронизирующим входом БН 11. Выход первого Сч 11.1 подключен к входу второго инкрементора 11.3 и к первому входу первого Комп 11.4. Выход второго инкрементора 11.3 соединен с входом коммутатора записи 11.10, N+1 выходов которого соединены с соответствующими N+1 входами "Разрешение записи" ОЗУ с последовательным считыванием 11.9. Выход первого инкрементора 11.2 соединен со вторыми входами первого и второго Комп 11.4 и 11.8. Выход первого Комп 11.4 подключен к установочному входу первого Сч 11.1 и входу R RS-триггера 11.5, выход которого соединен с управляющим входом ЭК 11.6. Выход ЭЗ 11.12 подключен к сигнальному входу ЭК 11.6, выход которого соединен со счетным входом второго Сч 11.7. Выход второго Сч 11.7 соединен с входом коммутатора считывания 11.11 и с первым входом второго Комп 11.8, выход которого соединен с установочным входом второго Сч 11.7. N+1 выходов коммутатора считывания подключены к соответствующим N+1 входам "Разрешение чтения" ОЗУ с последовательным считыванием 11.9. Сигнальный выход ОЗУ с последовательным считыванием 11.9 является сигнальным выходом БН 11.

ОЗУ с последовательным считыванием предназначено для записи, хранения и выдачи заданного количества реализаций сигналов. Его блок-схема представлена на фиг. 17 и включает 2(Nmax+1) элемент И 11.9.11-11.9.1Nmax+1 и 11.9.31-11.9.3Nmax+1, Nmax+1 блок памяти 11.9.21-11.9.2Nmax+1 и регистр 11.9.4. Сигнальные входы второго, третьего, . . . , Nmax+1 блоков памяти 11.9.22-11.9.2Nmax+1 соединены с сигнальным входом первого блока памяти 11.9.21, являющегося сигнальным входом ОЗУ с последовательным считыванием 11.9. Вторые входы 2(Nmax+1) элементов И 11.9.11- 11.9.1Nmax+1 и 11.9.31-11.9.3Nmax+1 подключены к выходу регистра 11.9.4, первые входы Nmax+1 элементов И 11.9.11-11.9.1Nmax+1 являются соответствующими Nmax+1 входами "Разрешение записи", а первые входы Nmax+1 элементов И 11.9.31-11.9.3Nmax+1 являются соответствующими Nmax+1 входами "Разрешение чтения" ОЗУ с последовательным считыванием 11.9. Выходы Nmax+1 элементов И 11.9.11-11.9.1Nmax+1 соединены с входами "Запись" соответствующих Nmax+1 блоков памяти 11.9.21-11.9.2Nmax+1, а выходы Nmax+1 элементов И 11.9.31-11.9.3Nmax+1 соединены с входами "Считывание" соответствующих Nmax+1 блоков памяти 11.9.21-11.9.2Nmax+1. Тактовые входы Nmax блоков памяти 11.9.21-11.9.2Nmax подключены к тактовому входу блока памяти 11.9.2Nmax+1, являющегося тактовым входом ОЗУ с последовательным считыванием 11.9. Выходы Nmax блоков памяти 11.9.22-11.9.2Nmax+1 соединены с выходом первого блока памяти 11.9.21, являющегося сигнальным выходом ОЗУ с последовательным считыванием 11.9.

Блок дискриминации 12 предназначен для разделения сигналов, принимаемых трехэлементной антенной, определения их азимутов и углов места и идентификации рассчитанных значений углов прихода с принимаемыми сигналами. Его блок-схема представлена на фиг. 18 и включает первый и второй блоки векторного умножения (БВУ) 12.11, 12.12, Комп 12.2, коммутатор 12.3, первый, второй, третий и четвертый блоки весовых коэффициентов (БВК) 12.41-12.44, первый, второй, третий и четвертый Дел 12.5-12.8, первый, второй, третий и четвертый Выч 12.9-12.12 и первый и второй блоки углов 12.131, 12.132. Первый фазовый вход первого блока углов 12.131 и первый вход первого БВК 12.41, вторые входы второго и третьего БВК 12.42 и 12.43, четвертый вход четвертого БВК 12.44 и первый фазовый вход второго БВУ 122 соединены с первым фазовым входом первого БВУ 121, являющимся первым входом "Север-юг" БД 12. Первый информационный вход коммутатора 12.3 подключен ко второму фазовому входу первого БВУ 121, являющегося первым входом "Восток-запад" БД 12, а второй информационный вход коммутатора 12.3 соединен со вторым фазовым входом второго БВУ 122, являющегося вторым входом "Восток-запад" БД 12. Первый фазовый вход второго блока углов 12.132, второй вход первого БВК 12.41, третий вход второго БВК 12.42 и первый вход третьего БВК 12.43 подключены ко второму входу четвертого БВК 12.44, являющегося вторым входом "Восток-запад" БД 12. Первый и второй входы собственного вектора второго БВУ 12.12 соединены с первым и вторым входами собственного вектора первого БВУ 12.11, являющихся соответственно первым и вторым входами собственного вектора БД 12. Выход первого БВУ 12.11 соединен с первым входом Комп 12.2, второй вход которого подключен к выходу второго БВУ 12.12, а выход Комп соединен с управляющим входом коммутатора 12.3. Первый выход коммутатора 12.3 соединен со вторым фазовым входом первого блока углов 12.131, третьим входом первого БВК 12.41, четвертыми входами второго и третьего БВК 12.42 и 12.43 и первым входом четвертого БВК 12.44. Второй выход коммутатора 12.3 соединен со вторым фазовым входом второго блока углов 12.132, четвертым входом первого БВК 12.41, первым входом второго БВК 12.42, третьими входами третьего и четвертого БВК 12.43 и 12.44. Входы "База" и "Частота" первого блока углов 12.131 соединены с одноименными входами второго блока углов 12.132, являющихся соответствующими входами блока дискриминации. Выходы первого, второго, третьего и четвертого БВК 12.41 подключены ко вторым входам соответственно первого, второго, третьего и четвертого Дел 12.5-12.8. Первый вход третьего Дел 12.5 соединен с первым входом первого Дел 12.7, являющегося вторым сигнальным входом БД 12. Первый вход второго Дел 12.6 соединен с первым входом четвертого Дел 12.8, являющегося третьим сигнальным входом БД 12. Выход первого Дел 12.5 подключен ко второму входу первого Выч 12.9. выход второго Дел 12.6 соединен со вторым входом второго Выч 12.10, выход третьего Дел 12.7 подключен ко второму входу третьего Выч 12.11, выход четвертого Дел 12.8 соединен со вторым входом четвертого Выч 12.12. Первый вход третьего Выч 12.11 соединен с первым входом первого Выч 12.9, являющегося первым сигнальным входом БД 12. Выход первого Выч 12.9 подключен к первому входу второго Выч 12.10, выход третьего Выч 12.11 соединен с первым входом четвертого Выч 12.12. Выходы третьего и четвертого Выч 12.10 и 12.12 являются соответственно первым и вторым сигнальными выходами БД 12, а азимутальные и угломестные выходы первого и второго блоков углов 12.131 и 12.132 являются соответственно первыми и вторыми азимутальными и угломестными выходами БД 12.

Блок векторного умножения 12.1, показанный на фиг. 19, предназначен для расчета величины произведения вектора разностей фаз на собственный вектор кумулянтной матрицы и состоит из первого и второго вычислителей комплексной экспоненты 12.1.1 и 12.1.2, первого и второго Умн 12.1.3 и 12.1.4, Сум 12.1.5, инкрементора 12.1.6 и вычислителя обратной величины 12.1.7. Первые входы первого и второго вычислителей комплексной экспоненты 12.1.1 и 12.1.2 являются соответственно первым и вторым фазовыми входами БВУ 12.1 и соединены с первыми входами соответственно первого и второго Умн 12.1.3 и 12.1.4, их вторые входы являются соответственно первым и вторым входами собственного вектора БВУ 12.1. Выходы первого и второго Умн 12.1.3 и 12.1.4 соединены соответственно с первым и вторым входами Сум 12.1.5, выход которого подключен к входу инкрементора 12.1.6. Выход инкрементора 12.1.6 соединен с входом вычислителя обратной величины 12.1.7, выход которого является выходом БВУ 12.1.

Блок весового коэффициента 12.4 предназначен для расчета значений весовых коэффициентов, обеспечивающих разделение двух сигналов, принимаемых трехэлементной антенной. Его блок-схема представлена на фиг. 20 и состоит из первого, второго, третьего и четвертого вычислителей комплексной экспоненты 12.4.1-12.4.4, Дел 12.4.5, Умн 12.4.6 и Выч 12.4.7. Входы первого, второго, третьего и четвертого вычислителей комплексной экспоненты являются соответственно первым, вторым, третьим и четвертым входами БВК. Выход первого вычислителя комплексной экспоненты 12.4.1 подключен к первому входу Выч 12.4.7, выход второго вычислителя комплексной экспоненты 12.4.2 соединен с первым входом Дел 12.4.5, а выход третьего вычислителя комплексной экспоненты 12.4.3 подключен к его второму входу, выход четвертого вычислителя комплексной экспоненты 12.4.1 соединен со вторым входом Умн 12.4.6. Выход Дел 12.4.5 соединен с первым входом Умн 12.4.6, его выход подключен ко второму входу Выч 12.4.7. Выход Выч 12.4.7 является выходом БВК 12.4.