Изобретение относится к области вычислительной техники и может быть использовано в качестве устройства для структурно-статистического анализа информационных массивов.

Известно устройство поиска информации, описанное в авторском свидетельстве СССР №1711185, МПК4 G 06 F 15/40, заявленном 05.04.89. В указанном изобретении описано устройство поиска информации, содержащее регистры верхней и нижней границы, сумматор-вычитатель, регистр стратегии поиска, вычитающий и суммирующие счетчики, схемы сравнения, блок памяти, регистр ключа, выходной регистр, группы элементов И и ИЛИ, триггер, распределитель импульсов, вход запуска, входы адресов верхней и нижней границы, вход кода критерия смены стратегии поиска, вход ключа, выход адреса, выход признака отсутствия информации.

Известно также устройство поиска информации, описанное в авторском свидетельстве Российской Федерации №2116670, МПК6 G 06 F 17/30, заявленном 07.04.97. В указанном изобретении описано устройство поиска информации, содержащее распределитель импульсов, первые и вторые формирователи переменной поиска, суммирующие счетчики и блоки памяти, регистр стратегии поиска, формирователь сигналов текущей оценки, дискриминатор зон значений оценки, счетчик временных интервалов, коммутатор, блок деления, классификатор, блок изменения пороговых сигналов, таймер текущих суток, блок индикации и формирователь сигналов сброса, информационный вход, входы "Зона 1" и "Зона 2", входы "Nmax", "Порог" и "Пуск" и выход адреса.

Однако аналоги имеют недостатки, заключающиеся в невысокой скорости поиска комбинаций начала сообщений и в относительно низкой информативности показателей трафика, характеризующих структуру информационных массивов.

Ближайшее устройство поиска информации (прототип) к предлагаемому описано в авторском свидетельстве Российской Федерации №2149446, МПК7 G 06 F 17/30, заявленном 12.05.99. В указанном изобретении описано устройство поиска информации, содержащее формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов сброса, блок индикации, блок изменения пороговых сигналов, таймер текущих суток, блок формирования порога усечения.

Информационные входы формирователя сигналов текущей оценки и дискриминатора зон значений оценки объединены и являются информационным входом устройства. Входы "Изменение состояния обстановки" и "Отсутствие изменения состояния обстановки" блока индикации подключены к одноименным входам формирователя сигнала сброса и выходам классификатора. Входы "Значение верхнего порога классификации" и "Значение нижнего порога классификации" классификатора подключены к одноименным выходам регистра стратегии поиска. Входы "Верхнее значение порога поиска" и "Нижнее значение порога поиска" регистра стратегии поиска подключены к одноименным выходам блока изменения пороговых сигналов и к входам блока формирования порога усечения. Вход "Номер текущего временного интервала" блока формирования порога усечения подключен к одноименным входу регистра стратегии поиска и выходу счетчика временных интервалов. Вход "Сброс" блока формирования порога усечения подключен к одноименным выходу формирователя сигнала сброса, к входам первого и второго блоков памяти и к входу счетчика временных интервалов. Тактовый вход счетчика временных интервалов подключен к входам синхронизации формирователя сигналов текущей оценки и дискриминатора зон значений оценки и первому синхронизирующему выходу распределителя импульсов. Вход "Время" распределителя импульсов подключен к одноименным входам формирователя сигналов текущей оценки, дискриминатора зон значений оценки, блока изменения пороговых сигналов и выходу таймера текущих суток. Выходы "Изменение состояния обстановки" и "Отсутствие изменения состояния обстановки" дискриминатора зон значений оценки подключены к одноименным входам коммутатора. Входы управления и синхронизации коммутатора подключены соответственно к выходу формирователя сигналов текущей оценки и второму выходу распределителя импульсов. Четвертый и третий выходы распределителя импульсов подключены соответственно к входу синхронизации классификатора и к входам синхронизации первого и второго блоков памяти. Выходы "Изменение состояния обстановки" и "Отсутствие изменения состояния обстановки" коммутатора подключены к информационным входам соответственно первого и второго формирователей переменной поиска. Вход "Максимальный номер временного интервала" первого формирователя переменной поиска подключен к одноименным входам второго формирователя переменной поиска, регистра стратегии поиска и выходу блока формирования порога усечения. Входы количества интервалов разбиения значений изменения состояния обстановки "Зона" первого и второго формирователей переменной поиска являются соответственно входами количества интервалов разбиения значений изменения состояния обстановки "Зона 1" и количества интервалов разбиения значений отсутствия изменения состояния обстановки "Зона 2" устройства. Выход первого формирователя переменной поиска подключен к информационному входу первого суммирующего счетчика. Выход первого суммирующего счетчика подключен к второму информационному входу блока деления. Первый информационный вход блока деления подключен к выходу второго суммирующего счетчика и информационному входу второго блока памяти. Выход блока деления подключен к информационному входу классификатора. Выход первого блока памяти подключен к информационному входу первого суммирующего счетчика. Первый и второй информационные входы второго суммирующего счетчика подключены к выходам соответственно второго формирователя переменной поиска и второго блока памяти. Входы «Пуск» и «Порог» блока изменения пороговых сигналов подключены к соответствующим входам блока формирования порога усечения и являются соответственно входами «Пуск» и «Порог» устройства. Входы «Максимальный номер временного интервала», «Числовое значение единицы» и «Объем выборки интервала анализа» блока формирования порога усечения являются одноименными входами устройства.

Описанное устройство обладает более высокой скоростью поиска комбинаций начала сообщений по сравнению с вышеотмеченными, благодаря использованию совокупности новых блоков и корректировке значения максимального номера временного интервала на протяжении всего интервала анализа адекватно входному информационному потоку.

Однако устройство-прототип имеет недостаток, заключающийся в относительно низкой информативности показателей трафика, характеризующих структуру информационного массива, из-за того, что он оценивает только интенсивность входного трафика по комбинациям начала сообщения.

Целью изобретения является создание устройства, обеспечивающего возможность распознавания искомых детерминированных комбинаций, представляющих собой n-разрядные двоичные числа.

Поставленная цель достигается тем, что в известном устройстве поиска информации, включающем формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов сброса, блок индикации, блок изменения пороговых сигналов, таймер текущих суток, блок формирования порога усечения, информационный вход формирователя сигналов текущей оценки подключен к информационному входу дискриминатора зон значений оценки, входы "Изменение состояния обстановки" и "Отсутствие изменения состояния обстановки" блока индикации подключены к одноименным входам формирователя сигнала сброса и выходам классификатора, входы "Значение верхнего порога классификации" и "Значение нижнего порога классификации" которого подключены к одноименным выходам регистра стратегии поиска, входы "Верхнее значение порога поиска" и "Нижнее значение порога поиска" которого подключены к одноименным выходам блока изменения пороговых сигналов и к входам блока формирования порога усечения, вход "Номер текущего временного интервала" которого подключен к одноименным входу регистра стратегии поиска и выходу счетчика временных интервалов, а вход "Сброс" блока формирования порога усечения подключен к одноименным выходу формирователя сигнала сброса, к входам первого и второго блоков памяти и к входу счетчика временных интервалов, тактовый вход которого подключен к входам синхронизации формирователя сигналов текущей оценки и дискриминатора зон значений оценки и первому синхронизирующему выходу распределителя импульсов, вход "Время" которого подключен к одноименным входам формирователя сигналов текущей оценки, дискриминатора зон значений оценки, блока изменения пороговых сигналов и выходу таймера текущих суток, выходы "Изменение состояния обстановки" и "Отсутствие изменения состояния обстановки" дискриминатора зон значений оценки подключены к одноименным входам коммутатора, входы управления и синхронизации которого подключены соответственно к выходу формирователя сигналов текущей оценки и второму выходу распределителя импульсов, четвертый и третий выходы которого подключены соответственно к входу синхронизации классификатора и к входам синхронизации первого и второго блоков памяти, выходы "Изменение состояния обстановки" и "Отсутствие изменения состояния обстановки» коммутатора подключены к информационным входам соответственно первого и второго формирователей переменной поиска, вход «Максимальный номер временного интервала» первого формирователя переменной поиска подключен к одноименным входам второго формирователя переменной поиска, регистра стратегии поиска и выходу блока формирования порога усечения, входы количества интервалов разбиения значений изменения состояния обстановки «Зона» первого и второго формирователей переменной поиска являются соответственно входами количества интервалов разбиения значений изменения состояния обстановки «Зона 1» и количества интервалов разбиения значений отсутствия изменения состояния обстановки «Зона 2» устройства, выход первого формирователя переменной поиска подключен к информационному входу первого суммирующего счетчика, выход которого подключен к второму информационному входу блока деления, первый информационный вход которого подключен к выходу второго суммирующего счетчика и информационному входу второго блока памяти, а выход блока деления подключен к информационному входу классификатора, выход первого блока памяти подключен к информационному входу первого суммирующего счетчика, первый и второй информационные входы второго суммирующего счетчика подключены к выходам соответственно второго формирователя переменной поиска и второго блока памяти, входы «Пуск» и «Порог» блока изменения пороговых сигналов подключены к соответствующим входам блока формирования порога усечения и являются соответственно входами «Пуск» и «Порог» устройства, а входы «Максимальный номер временного интервала», «Числовое значение единицы» и «Объем выборки интервала анализа» блока формирования порога усечения являются одноименными входами устройства, дополнительно введены структурный анализатор, предназначенный для выработки сигнала запуска работы устройства при наличии комбинации начала сообщения во входном информационном потоке и распознавания искомых детерминированных комбинаций, и третий блок памяти.

Информационный выход структурного анализатора подключен к информационному входу формирователя сигналов текущей оценки. Вход «Искомый признак" блока индикации подключен к одноименному выходу структурного анализатора. Выходы "Адрес" и "Тактовые импульсы" структурного анализатора подключены к одноименным входам третьего блока памяти. Выход "Данные" третьего блока памяти подключен к одноименному входу структурного анализатора. Информационный и синхронизирующий вход структурного анализатора являются соответственно информационным и синхронизирующим входами устройства.

Структурный анализатор состоит из входного регистра, дешифратора, первого и второго параллельных регистров, компаратора, вычислителя хеш-функции, RS-триггера, генератора импульсов, ключа. Информационный и синхронизирующий вход входного регистра являются соответственно информационным и синхронизирующим входами структурного анализатора. Выход входного регистра подключен к информационным входам дешифратора, первого параллельного регистра и вычислителя хеш-функции. Выход вычислителя хеш-функции является выходом "Адрес" структурного анализатора. Выход первого параллельного регистра подключен к информационному входу второго параллельного регистра и первому входу компаратора. Выход компаратора подключен к входу "Установка 0" RS-триггера и управляющему входу второго параллельного регистра. Выход второго параллельного регистра является выходом "Искомый признак" структурного анализатора. Выход дешифратора подключен к управляющему входу первого параллельного регистра, запускающему входу вычислителя хеш-функции, к входу "Установка 1" RS-триггера и является информационным выходом структурного анализатора. Второй вход компаратора является входом "Данные" структурного анализатора. Прямой выход RS-триггера подключен к управляющему входу ключа. Информационный вход ключа подключен к генератору импульсов. Выход ключа подключен к управляющему входу компаратора и является выходом "Тактовые импульсы" структурного анализатора.

Благодаря новой совокупности существенных признаков за счет введения структурного анализатора и дополнительного блока памяти, в которых производится хеширование и распознавание искомых детерминированных комбинаций, повышается информативность показателей трафика, характеризующих структуру информационных массивов.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующие совокупность признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности "новизна". Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

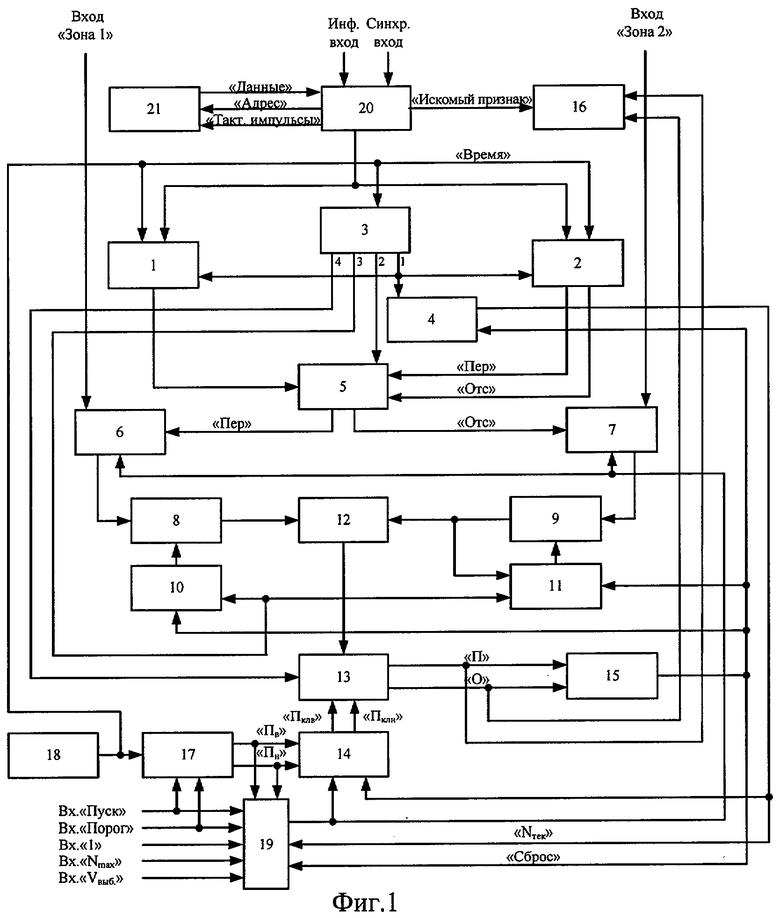

Заявленное устройство поясняется чертежами:

- фиг.1 - общая схема устройства поиска информации;

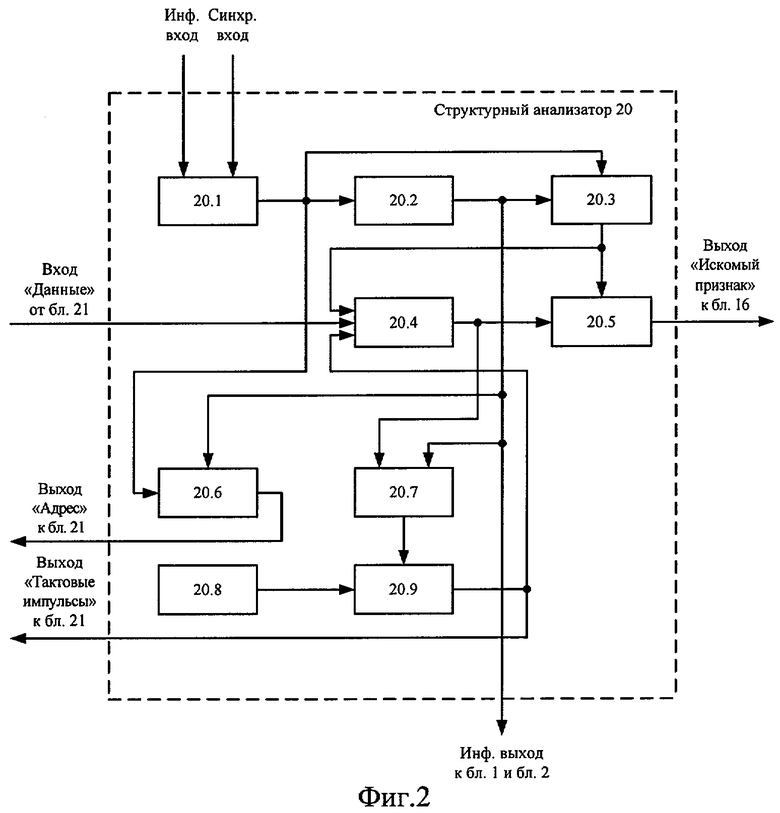

- фиг.2 - структурный анализатор.

Устройство поиска информации, показанное на фиг.1, содержит формирователь сигналов текущей оценки 1, дискриминатор зон значений оценки 2, распределитель импульсов 3, счетчик временных интервалов 4, коммутатор 5, первый 6 и второй 7 формирователи переменной поиска, первый 8 и второй 9 суммирующие счетчики, первый 10 и второй 11 блоки памяти, блок деления 12, классификатор 13, регистр стратегии поиска 14, формирователь сигналов сброса 15, блок индикации 16, блок изменения пороговых сигналов 17, таймер текущих суток 18, блок формирования порога усечения 19, структурный анализатор 20 и третий блок памяти 21.

Информационный вход формирователя сигналов текущей оценки 1 подключен к информационному входу дискриминатора зон значений оценки 2. Входы "Изменение состояния обстановки" - "П" и "Отсутствие изменения состояния обстановки" - "О" блока индикации 16 подключены к одноименным входам формирователя сигнала сброса 15 и выходам классификатора 13. Входы "Значение верхнего порога классификации" - "Пклв" и "Значение нижнего порога классификации" - "Пклн" порогов классификации классификатора 13 подключены к одноименным выходам регистра стратегии поиска 14. Входы "Верхнее значение порога поиска" - "Пв" и "Нижнее значение порога поиска" - "Пн" значений порогов поиска регистра стратегии поиска 14 подключены к одноименным выходам блока изменения пороговых сигналов 17 и к входам блока формирования порога усечения 19. Вход "Номер текущего временного интервала" - "Nтек" блока формирования порога усечения 19 подключен к одноименным входу регистра стратегии поиска 14 и выходу счетчика временных интервалов 4. Вход "Сброс" блока формирования порога усечения 19 подключен к одноименным выходу формирователя сигнала сброса 15, к входам первого 10 и второго 11 блоков памяти и к входу счетчика временных интервалов 4. Тактовый вход счетчика временных интервалов 4 подключен к входам синхронизации формирователя сигналов текущей оценки 1 и дискриминатора зон значений оценки 2 и первому синхронизирующему выходу распределителя импульсов 3. Вход "Время" распределителя импульсов 3 подключен к одноименным входам формирователя сигналов текущей оценки 1, дискриминатора зон значений оценки 2, блока изменения пороговых сигналов 17 и выходу таймера текущих суток 18. Выходы "Изменение состояния обстановки" - "Пер" и "Отсутствие изменения состояния обстановки" - "Отс" дискриминатора зон значений оценки 2 подключены к одноименным входам коммутатора 5. Входы управления и синхронизации коммутатора 5 подключены соответственно к выходу формирователя сигналов текущей оценки 1 и второму выходу распределителя импульсов 3. Четвертый и третий выходы распределителя импульсов 3 подключены соответственно к входу синхронизации классификатора 13 и к входам синхронизации первого 10 и второго 11 блоков памяти. Выходы "Изменение состояния обстановки" - "Пер" и "Отсутствие изменения состояния обстановки" - "Отс" коммутатора 5 подключены к информационным входам соответственно первого 6 и второго 7 формирователей переменной поиска. Вход "Максимальный номер временного интервала" - "Nmax" первого формирователя переменной поиска 6 подключен к одноименным входам второго формирователя переменной поиска 7, регистра стратегии поиска 14 и выходу блока формирования порога усечения 19. Входы количества интервалов разбиения значений изменения состояния обстановки "Зона 1" и количества интервалов разбиения значений отсутствия изменения состояния обстановки "Зона 2" устройства являются входами количества интервалов разбиения значений изменения состояния обстановки "Зона" соответственно первого 6 и второго 7 формирователей переменной поиска. Выход первого формирователя переменной поиска 6 подключен к информационному входу первого суммирующего счетчика 8. Выход первого суммирующего счетчика 8 подключен к второму информационному входу блока деления 12. Первый информационный вход блока деления 12 подключен к выходу второго суммирующего счетчика 9 и информационному входу второго блока памяти 11. Выход блока деления 12 подключен к информационному входу классификатора 13. Выход первого блока памяти 10 подключен к информационному входу первого суммирующего счетчика 8. Первый и второй информационные входы второго суммирующего счетчика 9 подключены к выходам соответственно второго формирователя переменной поиска 7 и второго блока памяти 11. Входы "Пуск" и "Порог" блока изменения пороговых сигналов 17 подключены к соответствующим входам блока формирования порога усечения 19 и являются соответственно входами "Пуск" и "Порог" устройства. Входы "Максимальный номер временного интервала" - "Nmax", "Числовое значение единицы" - "1" и "Объем выборки интервала анализа" - "Vвыб" блока формирования порога усечения 19 являются входами устройства.

Информационный выход структурного анализатора 20 подключен к информационному входу формирователя сигналов текущей оценки 1. Вход "Искомый признак" блока индикации 16 подключен к одноименному выходу структурного анализатора 20. Выходы "Адрес" и "Тактовые импульсы" структурного анализатора 20 подключены к одноименным входам третьего блока памяти 21. Выход "Данные" третьего блока памяти 21 подключен к одноименному входу структурного анализатора 20. Информационный и синхронизирующий вход структурного анализатора 20 являются соответственно информационным и синхронизирующим входами устройства.

Структурный анализатор 20 предназначен для выработки сигнала запуска работы всего устройства, хеширования и распознавания искомых детерминированных комбинаций и может быть реализован различными способами, в частности, как показано на фиг.2. Объектом распознавания являются искомые детерминированные комбинации в информационном массиве. Каждую детерминированную комбинацию, представляющую собой n-разрядное двоичное число, делят на заранее определенное n-разрядное двоичное число с остатком, являющимся значением хеш-функции. По найденному значению хеш-функции, являющемуся адресом, в блоке памяти 21 находят заранее запрограммированные искомые детерминированные комбинации и сравнивают их с поступившей детерминированной комбинацией на наличие совпадения. В случае совпадения одной из хранящихся в блоке памяти 21 детерминированной комбинации с поступившей выдается сигнал "Искомый признак", который представляет собой искомую детерминированную комбинацию, отображаемую в блоке индикации 16.

Структурный анализатор 20 состоит из входного регистра 20.1, дешифратора 20.2, первого 20.3 и второго 20.5 параллельных регистров, компаратора 20.4, вычислителя хеш-функции 20.6, RS-триггера 20.7, генератора импульсов 20.8, ключа 20.9. Информационный и синхронизирующий вход входного регистра 20.1 являются соответственно информационным и синхронизирующим входами структурного анализатора 20. Выход входного регистра 20.1 подключен к информационным входам дешифратора 20.2, первого параллельного регистра 20.3 и вычислителя хеш-функции 20.6. Выход вычислителя хеш-функции 20.6 является выходом "Адрес" структурного анализатора 20. Выход первого параллельного регистра 20.3 подключен к информационному входу второго параллельного регистра 20.5 и первому входу компаратора 20.4. Выход компаратора 20.4 подключен к входу "Установка 0" RS-триггера 20.7 и управляющему входу второго параллельного регистра 20.5. Выход второго параллельного регистра 20.5 является выходом "Искомый признак" структурного анализатора 20. Выход дешифратора 20.2 подключен к управляющему входу первого параллельного регистра 20.3, запускающему входу вычислителя хеш-функции 20.6, к входу "Установка 1" RS-триггера 20.7 и является информационным выходом структурного анализатора 20. Второй вход компаратора 20.4 является входом "Данные" структурного анализатора 20. Прямой выход RS-триггера 20.7 подключен к управляющему входу ключа 20.9. Второй вход ключа 20.9 подключен к генератору импульсов 20.8. Выход ключа 20.9 подключен к управляющему входу компаратора 20.4 и является выходом "Тактовые импульсы" структурного анализатора 20.

Назначение блоков и элементов заявленного устройства следующее. Формирователь сигналов текущей оценки 1 предназначен для выработки по окончании текущего интервала анализа двоичного сигнала, характеризующего состояние обстановки и принимающего значения "П" или "О". Схема формирователя сигналов текущей оценки 1 известна и описана на фиг.2 патента РФ №2116670.

Дискриминатор зон значений оценки 2 предназначен для выработки сигнала о номере зоны того состояния, в котором находится входной информационный поток соответствующей интенсивности. Схема дискриминатора зон значений оценки 2 известна и описана на фиг.3 патента РФ №2116670.

Распределитель импульсов 3 предназначен для синхронизации работы всего устройства посредством формирования четырех импульсных последовательностей, сдвинутых друг относительно друга на некоторую величину Δt. Схема распределителя импульсов 3 известна и описана на фиг.4 патента РФ №2116670.

Счетчик временных интервалов 4 предназначен для подсчета количества наблюдаемых интервалов времени и выдачи комбинации о номере временного интервала "Nтек". Счетчик временных интервалов 4 представляет собой суммирующий счетчик, схема которого известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.120, рис.3.13.

Коммутатор 5 предназначен для коммутации сигнала о номере зоны на вход соответствующего формирователя переменной поиска по сигналу управления, поступающему от формирователя сигналов текущей оценки 1 и принимающему значения "П" и "О". Схема коммутатора 5 известна и описана на фиг.5 патента РФ №2116670.

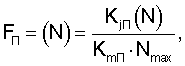

Формирователи переменной поиска 6 и 7 предназначены для построения приращений апостериорных интегральных функций распределения вероятностей нормального FО(N) (формирователь переменной поиска 6) и отклоненного FП(N) (формирователь переменной поиска 7) состояния трафика на N-м интервале наблюдения. Схемы формирователей переменной поиска 6 и 7 идентичны. Схема формирователя переменной поиска 6 известна и описана на фиг.6 патента РФ №2116670.

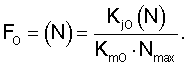

Суммирующие счетчики 8, 9 предназначены для сложения значений приращений FО(N) и FП(N) с соответствующими значениями эмпирической интегральной функции распределения вычисленной за N-1 временной интервал FО(N-1) и FП(N-1). Суммирующие счетчики 8, 9 представляют собой арифметические сумматоры, схемы которых известны и описаны в [Основы импульсной и цифровой техники. Учебное пособие для ВУЗов. - М.: Советское радио, 1975. - 440 с.] на стр.377, рис. 14.17.

Блоки памяти 10, 11 предназначены для хранения приращений FО(N) и FП(N) в течение одного интервала анализа. Блоки памяти 10, 11 представляют собой регистры параллельного действия, схемы которых известны и описаны в [Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973. - 480 с.] на стр.106, рис.1.

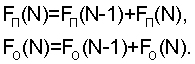

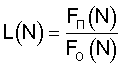

Блок деления 12 предназначен для деления приращения FП(N) на приращение FО(N) и выдачи отношения правдоподобия. Блок деления 12 представляет собой устройство деления двух n-разрядных двоичных чисел без восстановления остатка, схема которого известна и описана в [Бочаров К.П., Немшилов Н.Н., Петров Е.И., Сулин Л.И. Вычислительные комплексы автоматизированных систем управления. - Л.: ВАС, 1984. - 368 с.] на стр.88-90, рис.3.24.

Классификатор 13 предназначен для выработки сигналов "П" или "О" на основе сравнения входной информации с пороговыми значениями. Схема классификатора 13 известна и описана на фиг.7 патента РФ №2116670.

Регистр стратегии поиска 14 предназначен для формирования интервального либо точечного значений порогов классификации в зависимости от того, является ли номер интервала поиска предельным или нет. Схема регистра стратегии поиска 14 известна и описана на фиг.8 патента РФ №2116670.

Формирователь сигнала сброса 15 предназначен для объединения сигналов "П" и "О", их усиления и согласования с последующими блоками. Формирователь сигнала сброса 15 может быть выполнен в виде двухвходовой схемы ИЛИ, которая известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.48-49, рис.2.7.

Блок индикации 16 предназначен для отображения информации о наличии искомых детерминированных комбинаций и изменений интенсивности входного информационного потока. Схема блока индикации 16 известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.194-196, рис.5.20 и 5.21.

Блок изменения пороговых сигналов 17 предназначен для изменения значений пороговых сигналов в зависимости от времени суток. Схема блока изменения пороговых сигналов 17 известна и описана на фиг.9 патента РФ №2116670.

Таймер текущих суток 18 предназначен для установки времени суток всего устройства. Схема таймера текущих суток 18 известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.198-199, рис.5.23.

Блок формирования порога усечения 19 предназначен для корректировки значения максимального номера временного интервала - "Nmax" адекватно входному информационному потоку на протяжение всего интервала анализа. Схема блока 19 известна и описана на фиг.2 патента РФ №2149446.

Структурный анализатор 20 предназначен для выработки сигнала запуска работы всего устройства, хеширования и распознавания искомых детерминированных комбинаций и может быть реализован различными способами, в частности, как показано на фиг.2.

Входной регистр 20.1 предназначен для преобразования поступающей на вход детерминированной комбинации из последовательного кода в параллельный. Схема входного регистра 20.1 известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.182-184.

Дешифратор 20.2 предназначен для выделения комбинации начала сообщения на выходе входного регистра 20.1 и запуска работы всего устройства. Схема дешифратора 20.2 известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.152-153, рис.3.43.

Параллельные регистры 20.3, 20.5 предназначены для хранения детерминированной комбинации в течение одного интервала анализа. Схемы параллельных регистров 20.3, 20.5 известны и описаны в [Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973. - 480 с.] на стр.106, рис.3.1.

Компаратор 20.4 предназначен для сравнения двух n-разрядных чисел и выдачи на выходе (А=В) сигнала "1". Схема компаратора 20.4 известна и описана в [Лебедев О.Н., Сидоров A.M. Импульсные и цифровые устройства. Цифровые узлы и их проектирование на микросхемах. - Л.: ВАС, 1980. - 128 с.] на стр.52-54, рис.2.35, таблица 2.11.

Вычислитель хеш-функции 20.6 предназначен для деления поступающей на вход устройства детерминированной комбинации, представляющей собой n-разрядное двоичное число, на заранее определенное n-разрядное двоичное число с остатком и выдачи адреса детерминированной комбинации в блок памяти 21. Вычислитель хеш-функции 20.6 представляет собой устройство деления двух n-разрядных двоичных чисел методом восстановления остатка, схема которого известна и описана в [Хвощ С.Т., Варлинский Н.Н., Попов Е.А. Микропроцессоры и микроЭВМ в системах автоматического управления. Справочник. - Л.: Машиностроение, 1987. - 640 с.] на стр.573-575, таблица 18.6.

RS-триггер 20.7 предназначен для управления работой ключа 20.9. Схема RS-триггера 20.7 известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.158-159, рис.4.21 (а).

Генератор импульсов 20.8 предназначен для формирования тактовых импульсов. Схема генератора импульсов 20.8 известна и описана в [Батушев В.А., Вениаминов В.Н., Ковалев В.Г. и др. Микросхемы и их применение. - М.: Энергия, 1978. - 248 с.] на стр.193-194, рис.5.19 (г).

Ключ 20.9 предназначен для пропуска тактовых импульсов в третий блок памяти 21 и компаратор 20.4. Схема ключа 20.9 известна и описана в [Шляпоберский В.И. Основы техники передачи дискретных сообщений. - М.: Связь, 1973. - 480 с.] на стр.43-48, рис.2.4.

Третий блок памяти 21 предназначен для хранения заранее запрограммированных искомых детерминированных комбинаций. Третий блок памяти 21 представляет собой электрически программируемое постоянное запоминающее устройство, схема которого известна и описана в [Хвощ С.Т., Варлинский Н.Н., Попов Е.А. Микропроцессоры и микроЭВМ в системах автоматического управления. Справочник. - Л.: Машиностроение, 1987. - 640 с.] на стр.464-474.

Устройство поиска информации работает следующим образом.

Входной информационный поток, синхронизированный с тактовыми импульсами, поступает на информационный вход структурного анализатора 20 (фиг.1).

Структурный анализатор 20 (фиг.2) вырабатывает сигнал запуска работы всего устройства при наличии комбинации начала сообщения во входном информационном потоке, а также осуществляет поиск заранее определенных искомых детерминированных комбинаций и при их наличии выдает сигнал на вход "Искомый признак" блока индикации 16.

Во входном регистре 20.1 детерминированная комбинация под действием синхроимпульсов преобразуется из последовательного кода в параллельный и поступает на информационные входы дешифратора 20.2, первого параллельного регистра 20.3 и вычислителя хеш-функции 20.6.

В дешифраторе 20.2 при появлении комбинации начала сообщения на строго определенных выходных разрядах входного регистра 20.1 вырабатывается сигнал запуска работы всего устройства, который поступает на управляющий вход первого параллельного регистра 20.3, запускающий вход вычислителя хеш-функции 20.6, вход "Установка 1" RS-триггера 20.7 и на информационные входы формирователя сигналов текущей оценки 1 и дискриминатора зон значений оценки 2. По этому сигналу детерминированная комбинация с выхода входного регистра 20.1 записывается в первый параллельный регистр 20.3 и регистры общего назначения вычислителя хеш-функции 20.6, на выходе RS-триггера 20.7 устанавливается уровень логической единицы, а формирователь сигналов текущей оценки 1 и дискриминатор зон значений оценки 2 анализируют интенсивность входного потока.

В первом параллельном регистре 20.3 детерминированная комбинация хранится в течение одного интервала анализа. С выхода первого параллельного регистра 20.3 детерминированная комбинация поступает на информационный вход второго параллельного регистра 20.5 и первый вход компаратора 20.4.

В компараторе 20.4 под действием тактовых импульсов, поступающих на управляющий вход от ключа 20.9, выполняется операция сравнения двух детерминированных комбинаций, представляющих собой два n-разрядных двоичных числа, первое из которых поступает с выхода первого параллельного регистра 20.3 на первый вход, а второе - с выхода "Данные" третьего блока памяти 21 на второй вход, и при наличии совпадения вырабатывается сигнал, который поступает на вход "Установка 0" RS-триггера 20.7 и управляющий вход второго параллельного регистра 20.5. По этому сигналу детерминированная комбинация с выхода первого параллельного регистра 20.3 записывается во второй параллельный регистр 20.5, а на выходе RS-триггера 20.7 устанавливается уровень логического нуля.

С выхода второго параллельного регистра 20.5 детерминированная комбинация по сигналу управления от компаратора 20.4 поступает на вход "Искомый признак" блока индикации 16.

Вычислитель хеш-функции 20.6 производит деление поступившей на информационный вход детерминированной комбинации, представляющей собой n-разрядное двоичное число, на заранее определенное n-разрядное двоичное число методом восстановления остатка, являющегося значением хеш-функции и представляющего собой также n-разрядное двоичное число, которое поступает на вход "Адрес" третьего блока памяти 21.

RS-триггер 20.7 управляет работой ключа 20.9. RS-триггер 20.7 отпирает ключ 20.9 при появлении сигнала на входе "Установка 1" и запирает его при появлении сигнала на входе "Установка 0".

Генератор импульсов 20.8 формирует импульсы, которые поступают на информационный вход ключа 20.9.

С выхода ключа 20.9 при наличии на управляющем входе уровня логической единицы с выхода RS-триггера 20.7 тактовые импульсы поступают на вход "Тактовые импульсы" третьего блока памяти 21 и управляющий вход компаратора 20.4.

С выхода третьего блока памяти 21 заранее запрограммированные искомые детерминированные комбинации, находящиеся по адресу, поступающему с выхода вычислителя хеш-функции 20.6, последовательно считываются под действием тактовых импульсов, поступающих с выхода ключа 20.9, на второй вход компаратора 20.4.

В формирователе сигналов текущей оценки 1 по окончании текущего интервала анализа вырабатывается двоичный сигнал, характеризующий состояние обстановки. При превышении отклонения числа комбинаций начала сообщений от среднего значения в верхнюю или нижнюю сторону больше порогового, на выходе формирователя сигналов текущей оценки 1 формируется сигнал "П", в других случаях вырабатывается сигнал "О". С выхода формирователя сигналов текущей оценки 1 сигнал "П" или "О" поступает затем на управляющий вход коммутатора 5.

В дискриминаторе зон значений оценки 2 вырабатывается сигнал о номере зоны того состояния, в котором находится входной информационный поток соответствующей интенсивности. Этот номер зоны соответствует более точной оценке состояния обстановки по сравнению с оценкой, получаемой в формирователе сигналов текущей оценки 1. С выходов "Изменение состояния обстановки" - "Пер" или "Отсутствие изменения состояния обстановки" - "Отс" дискриминатора зон значений оценки 2 сигнал соответственно "Пер" или "Отс" поступает на одноименный вход коммутатора 5.

Распределитель импульсов 3 осуществляет синхронизацию работы всего устройства посредством формирования четырех импульсных последовательностей, сдвинутых друг относительно друга на некоторую величину Δt.

Счетчик временных интервалов 4 осуществляет подсчет количества наблюдаемых интервалов времени и выдает комбинацию о номере временного интервала на входы "Номер текущего временного интервала" - "Nтек" регистра стратегии поиска 14 и блока формирования порога усечения 19.

Коммутатор 5 в соответствии с поступающим на него сигналом управления от формирователя сигналов текущей оценки 1 обеспечивает подключение сигнала о номере зоны состояния "Пер" или "Отс" соответственно на вход формирователя переменной поиска 6 или 7, где на основе сигнала о номере зоны Km (1<j<m), наибольшего номера зоны Кm и максимального числа наблюдений Nmax производится построение приращений FП(N) и FО(N) эмпирических интегральных функций распределения вероятностей отклоненного и нормального состояния трафика на N-м интервале наблюдения:

В суммирующих счетчиках 8 и 9 производится слежение значений приращений FП(N) и FО(N) с соответствующими значениями эмпирической интегральной функции распределения вычисленной за N-1 временной интервал FП(N-l) и FО(N-1), которые поступают с выходов блоков памяти 10 и 11:

Значения FП(N) и FО(N) поступают на входы блока деления 12 и на запись в первый 10 и второй 11 блоки памяти. Блок деления 12 осуществляет операцию арифметического деления

и выдачу отношения правдоподобия на информационный вход классификатора 13.

Классификатор 13 вырабатывает решение о состоянии обстановки на основе сравнения входной информации с пороговыми значениями и выдает сигнал "П" или "О" на входы блока индикации 16 и формирователя сигналов сброса 15.

Регистр стратегии поиска 14 формирует интервальное либо точечное значения порогов классификации в зависимости от того, является ли номер интервала поиска предельным или нет. Сигнал с одного из выходов "Значение верхнего порога классификации" - "Пклв" или "Значение нижнего порога классификации" - "Пклн" регистра стратегии поиска 14 поступает на соответствующий вход классификатора 13.

Формирователь сигналов сброса 15 вырабатывает сигнал "Сброс" и подает его на входы счетчика 4, первого 10 и второго 11 блоков памяти и блока формировании порога усечения 19 для перевода их в исходное состояние.

Блок индикации 16 отображает информацию о наличии искомых детерминированных комбинаций и изменений интенсивности входного информационного потока при поступлении сигналов соответственно от структурного анализатора 20 и классификатора 13.

Адаптация значений порогов поиска ко времени суток осуществляется в блоке 17, на выходах которого формируются верхнее и нижнее значения порогов, зависящие от времени суток. Код текущего времени поступает на его вход с таймера текущих суток 18, устанавливающего время суток всего устройства.

Блок формирования порога усечения 19 вырабатывает новое значение Nmax по окончании текущего интервала анализа, которое является адекватным характеристикам входного информационного потока, и выдает его на входы "Максимальный номер временного интервала" - "Nmax" регистра стратегии поиска 14 и формирователя переменной поиска 6 или 7.

Все блоки, устройства и элементы, обрабатывающие сигнал, а также линии, их соединяющие, должны иметь разрядность, соответствующую разрядности входных операндов и точности их преобразований.

Оценка повышения информативности показателей трафика в предлагаемом устройстве приведена в Приложении.

Таким образом, полученные результаты позволяют сделать вывод о том, что предлагаемое устройство повышает информативность показателей трафика, характеризующих структуру информационного массива.

ПРИЛОЖЕНИЕ

Оценка повышения информативности показателей трафика устройства поиска информации

Оценка повышения информативности показателей трафика в предлагаемом устройстве поиска информации проведена следующим образом.

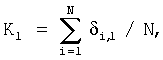

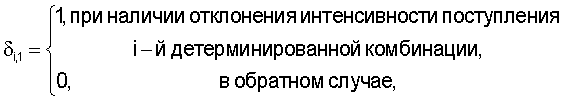

Информативность о наличии изменений интенсивности во входном информационном потоке может быть оценена коэффициентом информативности, равным отношению количества детерминированных комбинаций с отклоненной интенсивностью, к общему количеству поступивших детерминированных комбинаций:

где N - общее количество поступивших детерминированных комбинаций, δi,1 - коэффициент интенсивности i-й детерминированной комбинации, принимающий значение 1, если имеется отклонение интенсивности поступления i-й детерминированной комбинации, и значение 0 в обратном случае.

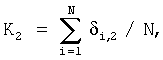

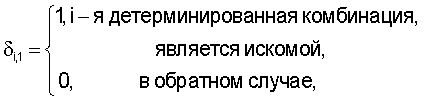

Информативность о наличии искомых детерминированных комбинаций во входном информационном потоке также может быть оценена коэффициентом информативности, равным отношению количества искомых детерминированных комбинаций к общему количеству поступивших детерминированных комбинаций:

где N - общее количество поступивших детерминированных комбинаций, δi,2 - коэффициент сходства i-й детерминированной комбинации, принимающий значение 1, если i-я детерминированная комбинация является искомой, и значение 0 в обратном случае.

Устройство-прототип позволяет находить только первый коэффициент информативности, характеризующий изменения интенсивности входного трафика. При этом количество знаний о входном информационном потоке определяется по формуле:

где х - общее количество показателей трафика.

Предлагаемое устройство позволяет находить два коэффициента информативности. При этом количество знаний о входном информационном потоке определяется по формуле:

где х - общее количество показателей трафика.

Выигрыш предлагаемого устройства по количеству знаний о входном информационном потоке определяется по формуле:

1≤R≤2.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2005 |

|

RU2290691C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2020 |

|

RU2740534C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Статистический анализатор | 1977 |

|

SU693398A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Адаптивный амплитудный анализатор | 1982 |

|

SU1078435A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

Изобретение относится к области вычислительной техники и может быть использовано в качестве устройства для структурно-статистического анализа информационных массивов. Техническим результатом является обеспечение возможности распознавания искомых детерминированных комбинаций, представляющих собой n-разрядные двоичные числа. Указанный результат достигается за счет того, что устройство содержит формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов, таймер текущих суток, блок формирования порога усечения, структурный анализатор и третий блок памяти. 1 з.п. ф-лы, 2 ил.

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1999 |

|

RU2149446C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Устройство для поиска информации | 1989 |

|

SU1711185A1 |

| US 4611298 А, 09.09.1986. | |||

Авторы

Даты

2006-08-10—Публикация

2004-12-28—Подача