Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для структурно-статистического анализа информационных массивов, циркулирующих в сложной, управляемой информационной (информационно-вычислительной или телекоммуникационной) системе в интересах аналитической обработки больших массивов гетерогенных данных об информационном трафике для выявления компьютерных инцидентов в критически важных сетевых инфраструктурах.

Известно устройство (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997), содержащее распределитель импульсов, первые и вторые формирователи переменной поиска, суммирующие счетчики и блоки памяти, регистр стратегии поиска, формирователь сигналов текущей оценки, дискриминатор зон значений оценки, счетчик временных интервалов, коммутатор, блок деления, классификатор, блок изменения пороговых сигналов, таймер текущих суток, блок индикации и формирователь сигналов сброса.

Данное устройство имеет узкую область применения, поскольку с его помощью невозможно производить анализ нескольких параллельных потоков для поиска комбинаций начала сообщений.

Известно устройство (см. патент РФ №2149446 «Устройство поиска информации», МПК G06F 17/30, опубликован 20.05.2000, Бюл. №14), которое содержит формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов сброса, блок изменения пороговых сигналов, таймер текущих суток и блок формирования порога усечения.

Однако данное устройство обеспечивает невысокую скорость поиска комбинаций начала сообщений и относительно низкую информативность показателей трафика, характеризующих структуру информационных массивов.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство мониторинга информационного трафика (см. патент РФ №2290691 «Устройство мониторинга информационного трафика» МПК G06F 17/18, G06F 17/30, опубликован 27.12.2006, Бюл. № 36), содержащее формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов сброса, блок отображения и записи данных, блок изменения пороговых сигналов, таймер текущих суток, блок формирования порога усечения, структурный анализатор, третий, четвертый и пятый блоки памяти, при этом выход формирователя сигналов текущей оценки подключен к управляющему входу коммутатора, выходы «Изменение состояния обстановки – Изм» и «Отсутствие изменения состояния обстановки – Отс» которого подключены к входам первого и второго формирователей переменной поиска, выход второго формирователя переменной поиска подключен к информационному входу второго суммирующего счетчика, выход которого подключен к информационному входу второго блока памяти и второму информационному входу блока деления, выход которого подключен к информационному входу классификатора, выходы «Изменение состояния обстановки – П» и «Отсутствие изменения состояния обстановки – О» которого подключены к одноименным входам и формирователя сигналов сброса и к одноименным входам блока отображения и записи данных, выход «Сброс» формирователя сигналов сброса подключен к входу «Сброс» первого блока памяти, входу «Сброс» второго блока памяти, входу «Сброс» счетчика временных интервалов и входу «Сброс» блока формирования порога усечения, выход «Максимальный номер временного интервала – Nmax» которого подключен к одноименным входам регистра стратегии поиска, первого и второго формирователей переменной поиска, выход первого формирователя переменной поиска подключен к информационному входу первого суммирующего счетчика, выход которого подключен к первому информационному входу блока деления, выходы «Изменение состояния обстановки – Изм» и «Отсутствие изменения состояния обстановки – Отс» дискриминатора зон значений оценки подключены к одноименным входам коммутатора, первый выход распределителя импульсов подключен к входам синхронизации формирователя сигналов текущей оценки и дискриминатора зон значений оценки, а также к тактовому входу счетчика временных интервалов, выход «Номер текущего временного интервала – Nтек» которого подключен к одноименным входам блока формирования порога усечения и регистра стратегии поиска, выходы «Значение верхнего порога классификации – Пклв» и «Значение нижнего порога классификации – Пклн» которого подключены к одноименным входам классификатора, второй выход распределителя импульсов подключен к синхронизирующему входу коммутатора, третий выход распределителя импульсов подключен к входам синхронизации первого и второго блоков памяти, выходы первого и второго блоков памяти подключены к сигнальным входам первого и второго суммирующих счетчиков, четвертый выход распределителя импульсов подключен к синхронизирующему входу классификатора, выход «Время» таймера текущих суток подключен к одноименным входам формирователя сигналов текущей оценки, дискриминатора зон значений оценки, распределителя импульсов, блока отображения и записи данных и блока изменения пороговых сигналов, выходы «Верхнее значение порога поиска – Пв» и «Нижнее значение порога поиска – Пн» которого подключены соответственно к одноименным входам регистра стратегии поиска и к одноименным входам блока формирования порога усечения, входы «Пуск» и «Порог» блока изменения пороговых сигналов подключены к одноименным входам блока формирования порога усечения и являются соответственно входами «Пуск» и «Порог» устройства, вход «Числовое значение единицы – 1», вход «Максимальный номер временного интервала – Nmax», и вход «Объем выборки интервала анализа – Vвыб» блока формирования порога усечения являются одноименными входами устройства, вход «Зона 1» первого формирователя переменной поиска и вход «Зона 2» второго формирователя переменной поиска являются соответственно входами «Зона 1» и «Зона 2» устройства, информационный выход структурного анализатора подключен к информационным входам формирователя сигналов текущей оценки и дискриминатора зон значений оценки, вход «Детерминированная комбинация», вход «Неизвестный признак», вход «Искомый признак» и вход «Адрес неизвестного признака – Адрес НП» блока отображения и записи данных подключены соответственно к одноименным выходам структурного анализатора, выход «Адрес» которого подключен к одноименным входам третьего, четвертого и пятого блоков памяти, выход «Данные 1» третьего блока памяти подключен к одноименным входам блока отображения и записи данных и структурного анализатора, выход «Данные 2» четвертого блока памяти и выход «Данные 3» пятого блока памяти подключены к одноименным входам структурного анализатора, выход «Тактовые импульсы» которого подключен к одноименным входам четвертого и пятого блоков памяти, выход «Данные 1 – запись», выход «Данные 2 – запись» и выход «Данные 3 – запись» блока отображения и записи данных подключены к одноименным входам третьего, четвертого и пятого блоков памяти, выход «Адрес 3 – запись» блока отображения и записи данных подключен к одноименному входу пятого блока памяти, выход «Адрес 1, 2 – запись» блока отображения и записи данных подключен к одноименным входам третьего и четвертого блоков памяти, информационный и синхронизирующий входы структурного анализатора являются соответственно информационным и синхронизирующим входами устройства.

В прототипе реализуется возможность обеспечения более высокой скорости поиска комбинаций начала сообщений благодаря корректировке значения максимального номера временного интервала на протяжении всего времени анализа. Помимо этого, устройство-прототип обеспечивает повышение информативности показателей трафика, характеризующих структуру информационных массивов, за счет структурного анализа детерминированных комбинаций.

Однако прототип имеет недостаток – относительно низкую достоверность анализа информационных массивов в условиях, присущих процессу мониторинга входного информационного потока, циркулирующего в реальной сложной и управляемой информационной (информационно-вычислительной или телекоммуникационной) системе – в условиях неоднозначности (нечеткости) наблюдаемых и анализируемых детерминированных комбинаций, характеризующих известные (искомые) или неизвестные признаки во входном информационном потоке.

Данное устройство позволяет осуществлять мониторинг информационного трафика путем структурно-статистического анализа информационных массивов, для которых характеризующие их детерминированные комбинации заданы (наблюдаются) количественно, идентифицируются четко и однозначно, в то время как детерминированные комбинации, характеризующих искомые или неизвестные признаки для большого количества входных информационных потоков, реально циркулирующих в сложных и разветвленных информационных (информационно-вычислительных или телекоммуникационных) системах, могут носить нечеткий характер, могут быть идентифицированы лишь качественно, т.е., неоднозначно, нечетко, с привлечением лингвистической переменной. Устройство-прототип позволяет оценивать количественные информативные показатели, характеризующие структуру информационных массивов, в то время как при мониторинге потоков данных в реальных системах широкое применение находят модели [1-5], объективно основанные на качественно, нечетко заданных (наблюдаемых) значениях показателей трафика, где наблюдаемые и анализируемые детерминированные комбинации, характеризующие известные (искомые) или неизвестные признаки во входном информационном потоке носят не только количественный – однозначно, четко идентифицируемый, но и нечеткий (идентифицируемый лишь на качественном уровне) характер, традиционно описываемый с привлечением математики нечетких множеств.

Под «детерминированной комбинацией» понимается q-разрядное (q = 1…10) двоичное число, характеризующее структурно-статистические атрибуты (параметры) анализируемого входного информационного массива – комбинация некоторого количества бит, описывающих структуру трафика, очередность и интенсивность поступления данных в рамках информационного потока.

Целью изобретения является разработка устройства, обеспечивающего повышение достоверности мониторинга информационного трафика за счет обеспечения дополнительной возможности структурно-статистического анализа (дополнительной верификации) информационных массивов с учетом наличия не только однозначно определенных, но и нечетко заданных (наблюдаемых, идентифицируемых) детерминированных комбинаций, характеризующих известные (искомые) или неизвестные признаки входных информационных потоков, создание устройства мониторинга информационного трафика, способного с высокой достоверностью оценивать показатели, характерные для реальных информационных массивов – когда детерминированные комбинации, отображающие информацию о наличии известного или неизвестного признака во входном информационном потоке, имеют как количественно, так и качественно, нечетко (с привлечением лингвистической переменной) выраженный физический смысл.

Указанная цель достигается тем, что в известное устройство мониторинга информационного трафика, содержащее формирователь сигналов текущей оценки, дискриминатор зон значений оценки, распределитель импульсов, счетчик временных интервалов, коммутатор, первый и второй формирователи переменной поиска, первый и второй суммирующие счетчики, первый и второй блоки памяти, блок деления, классификатор, регистр стратегии поиска, формирователь сигналов сброса, блок отображения и записи данных, блок изменения пороговых сигналов, таймер текущих суток, блок формирования порога усечения, структурный анализатор, третий, четвертый и пятый блоки памяти, дополнительно включен блок обработки нечетких комбинаций, предназначенный для последовательного сравнения поступающих в двоичном коде детерминированных комбинаций и принятия решения об их математической природе – детерминированная комбинация задана (идентифицирована) параметрически или с использованием функции принадлежности, характерной для нечетких множеств, а также для математически корректного преобразования детерминированных комбинаций заданных (идентифицированных) в нечеткой форме (не параметрически) к виду, пригодному для достоверного (четкого, однозначного) параметрического оценивания структурно-статистических характеристик потока данных в интересах мониторинга информационного трафика. При этом выход формирователя сигналов текущей оценки подключен к управляющему входу коммутатора, выходы «Изменение состояния обстановки – Изм» и «Отсутствие изменения состояния обстановки – Отс» которого подключены к входам соответственно первого и второго формирователей переменной поиска, выход второго формирователя переменной поиска подключен к информационному входу второго суммирующего счетчика, выход которого подключен к информационному входу второго блока памяти и второму информационному входу блока деления, выход которого подключен к информационному входу классификатора, выходы «Изменение состояния обстановки – П» и «Отсутствие изменения состояния обстановки – О» которого подключены соответственно к одноименным входам формирователя сигналов сброса и к одноименным входам блока отображения и записи данных, выход «Сброс» формирователя сигналов сброса подключен к входу «Сброс» первого блока памяти, входу «Сброс» второго блока памяти, входу «Сброс» счетчика временных интервалов и входу «Сброс» блока формирования порога усечения, выход «Максимальный номер временного интервала – Nmax» которого подключен к одноименным входам соответственно регистра стратегии поиска, первого и второго формирователей переменной поиска, выход первого формирователя переменной поиска подключен к информационному входу первого суммирующего счетчика, выход которого подключен к первому информационному входу блока деления, выходы «Изменение состояния обстановки – Изм» и «Отсутствие изменения состояния обстановки – Отс» дискриминатора зон значений оценки подключены соответственно к одноименным входам коммутатора, первый выход распределителя импульсов подключен к входам синхронизации соответственно формирователя сигналов текущей оценки и дискриминатора зон значений оценки, а также к тактовому входу счетчика временных интервалов, выход «Номер текущего временного интервала – Nтек» которого подключен к одноименным входам соответственно блока формирования порога усечения и регистра стратегии поиска, выходы «Значение верхнего порога классификации – Пклв» и «Значение нижнего порога классификации – Пклн» которого подключены к одноименным входам классификатора, второй выход распределителя импульсов подключен к синхронизирующему входу коммутатора, третий выход распределителя импульсов подключен к входам синхронизации первого и второго блоков памяти, выходы первого и второго блоков памяти подключены к сигнальным входам соответственно первого и второго суммирующих счетчиков, четвертый выход распределителя импульсов подключен к синхронизирующему входу классификатора, выходы «Верхнее значение порога поиска – Пв» и «Нижнее значение порога поиска – Пн» блока изменения пороговых сигналов подключены соответственно к одноименным входам регистра стратегии поиска и соответственно к одноименным входам блока формирования порога усечения, входы «Пуск» и «Порог» блока изменения пороговых сигналов подключены к одноименным входам блока формирования порога усечения и являются соответственно входами «Пуск» и «Порог» устройства, вход «Числовое значение единицы – 1», вход «Максимальный номер временного интервала – Nmax», и вход «Объем выборки интервала анализа – Vвыб» блока формирования порога усечения являются одноименными входами устройства, вход «Зона 1» первого формирователя переменной поиска и вход «Зона 2» второго формирователя переменной поиска являются соответственно входами «Зона 1» и «Зона 2» устройства, вход «Неизвестный признак», вход «Искомый признак» и вход «Адрес неизвестного признака – Адрес НП» блока отображения и записи данных подключены соответственно к одноименным выходам структурного анализатора, выход «Адрес» которого подключен к одноименным входам соответственно третьего, четвертого и пятого блоков памяти, выход «Данные 1» третьего блока памяти подключен к одноименным входам соответственно блока отображения и записи данных и структурного анализатора, выход «Данные 2» четвертого блока памяти и выход «Данные 3» пятого блока памяти подключены соответственно к одноименным входам структурного анализатора, выход «Тактовые импульсы» которого подключен к одноименным входам соответственно четвертого и пятого блоков памяти, выход «Данные 1 – запись», выход «Данные 2 – запись» и выход «Данные 3 – запись» блока отображения и записи данных подключены к одноименным входам соответственно третьего, четвертого и пятого блоков памяти, выход «Адрес 3 – запись» блока отображения и записи данных подключен к одноименному входу пятого блока памяти, выход «Адрес 1, 2 – запись» блока отображения и записи данных подключен к одноименным входам соответственно третьего и четвертого блоков памяти, информационный и синхронизирующий входы структурного анализатора являются соответственно информационным и синхронизирующим входами устройства, выход «Время» таймера текущих суток подключен к одноименным входам соответственно формирователя сигналов текущей оценки, дискриминатора зон значений оценки, распределителя импульсов, блока отображения и записи данных и блока изменения пороговых сигналов, информационный выход структурного анализатора подключен к информационным входам формирователя сигналов текущей оценки и дискриминатора зон значений оценки, выход «Детерминированная комбинация» структурного анализатора соединен с проверочным входом блока обработки нечетких комбинаций, верификационный выход которого подключен к входу «Детерминированная комбинация» блока отображения и записи данных.

Блок обработки нечетких комбинаций состоит из счетчика, регистра хранения, регистрирующего счетчика, вычислителя дополнения, основного и вспомогательного запоминающих элементов, основного и вспомогательного вычислителей пересечения, вычислителя объединения и анализатора уровня принадлежности, выход которого объединен с транзитным выходом регистра хранения и является верификационным выходом блока обработки нечетких комбинаций, вход счетчика является проверочным входом блока обработки нечетких комбинаций, выход счетчика соединен с входом регистра хранения, проверочный выход регистра хранения соединен с входом регистрирующего счетчика, первый и второй выходы которого соединены соответственно с входом основного запоминающего элемента и прямым входом вспомогательного запоминающего элемента, а также соответственно с первым и вторым входами вычислителя дополнения, выход основного запоминающего элемента и выход вспомогательного запоминающего элемента подключены соответственно к главному входу основного вычислителя пересечения и к главному входу вспомогательного вычислителя пересечения, к дополнительным входам основного и вспомогательного вычислителей пересечения подключены соответственно первый и второй выходы вычислителя дополнения, выходы основного и вспомогательного вычислителей пересечения подключены соответственно к первому и второму входам вычислителя объединения, выход которого соединен с дополнительным входом вычислителя дополнения, дополнительным входом вспомогательного запоминающего элемента и входом анализатора уровня принадлежности.

Благодаря новой совокупности существенных признаков, за счет введения блока обработки нечетких комбинаций, обеспечивающего последовательное сравнение поступающих в двоичном коде детерминированных комбинаций, принятие решения об их математической природе – детерминированная комбинация задана (идентифицирована) параметрически или с использованием функции принадлежности, характерной для нечетких множеств, а также математически корректное преобразование детерминированных комбинаций заданных (идентифицированных) в нечеткой форме (не параметрически) к виду, пригодному для достоверного (четкого, однозначного) параметрического оценивания структурно-статистических характеристик информационного потока, в заявленном устройстве достигается возможность повышения достоверности мониторинга информационного трафика за счет обеспечения возможности дополнительной верификации детерминированных комбинаций, характеризующих известные (искомые) или неизвестные признаки входных информационных потоков с учетом наличия не только количественных, но и нечетких (с привлечением лингвистической переменной) данных об этих комбинациях.

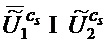

Заявленное устройство поясняется чертежами, на которых представлены:

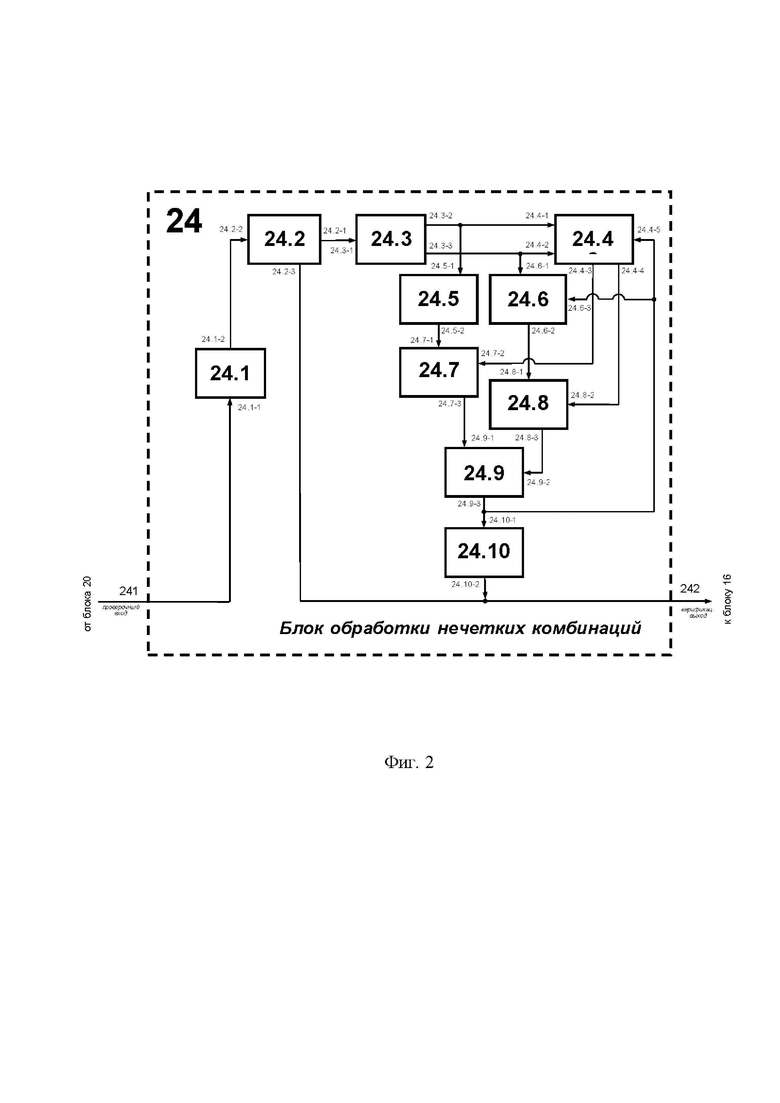

на фиг. 1 – структурная схема устройства мониторинга информационного трафика;

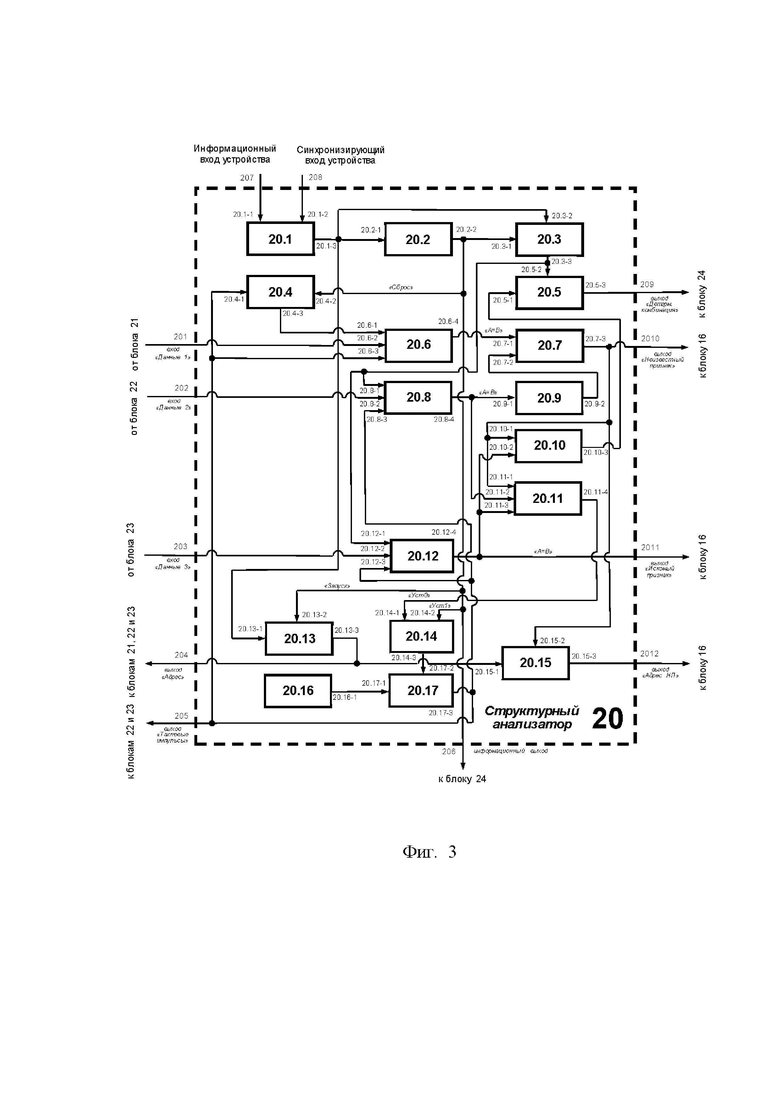

на фиг. 2 – структурная схема блока обработки нечетких комбинаций;

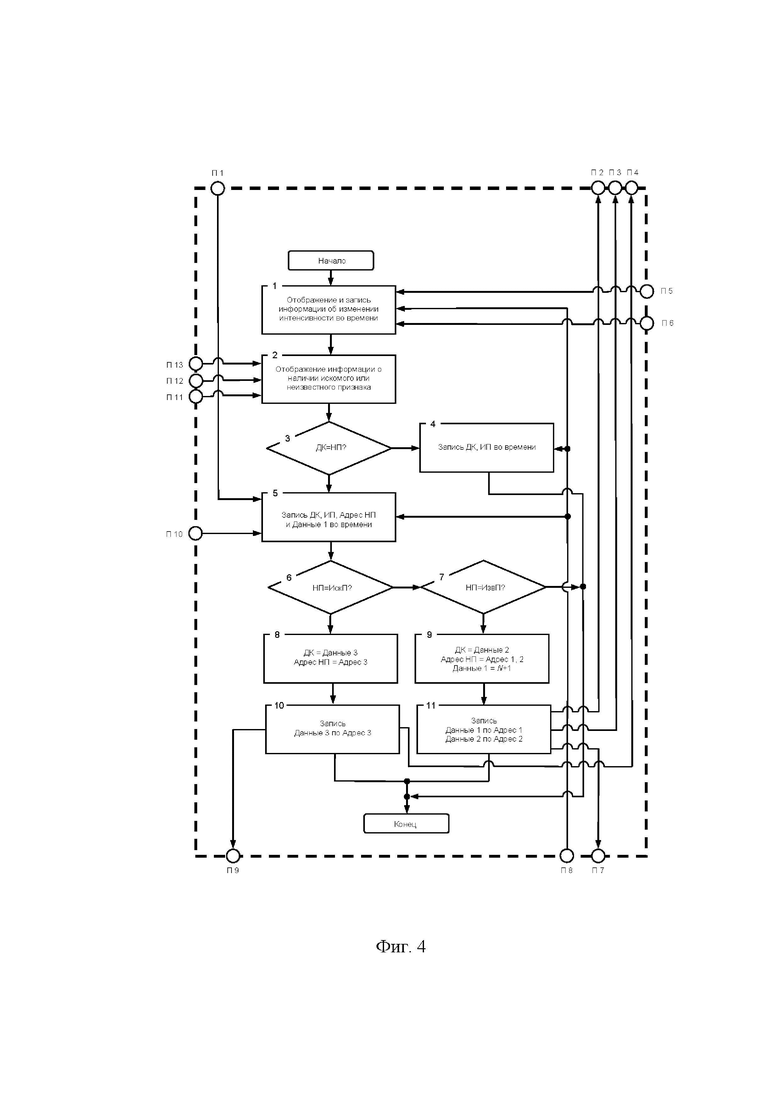

на фиг. 3 – структурная схема структурного анализатора;

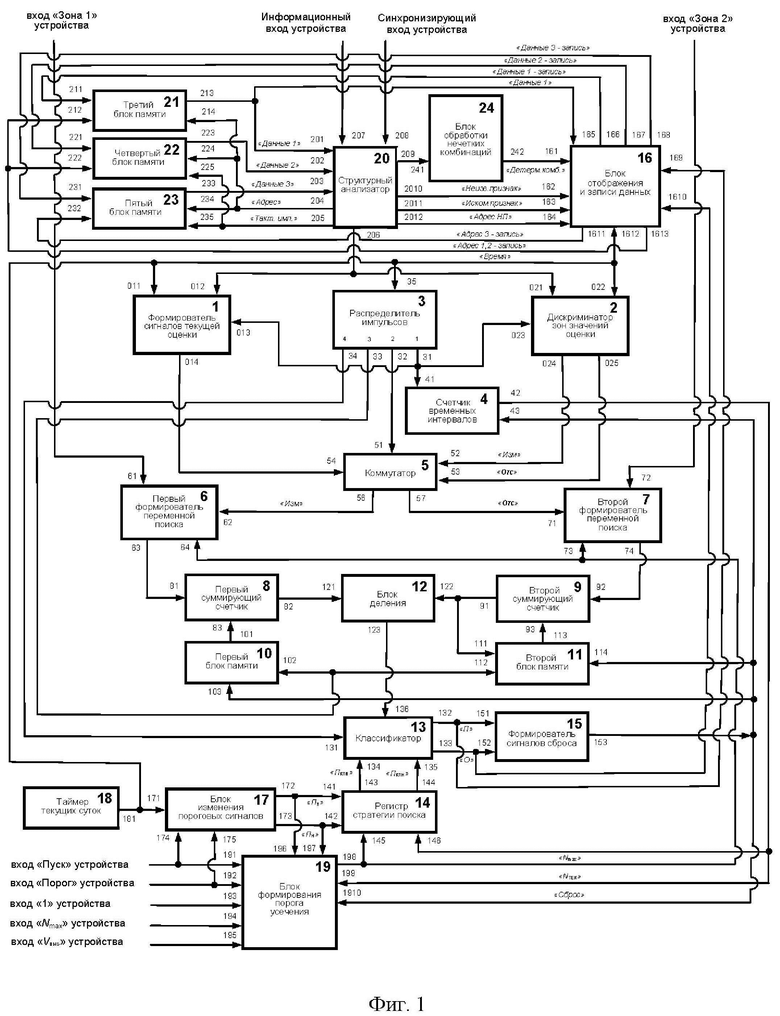

на фиг. 4 – алгоритм работы блока отображения и записи данных.

Устройство мониторинга информационного трафика, изображенное на фиг. 1, содержит формирователь сигналов текущей оценки 1, дискриминатор зон значений оценки 2, распределитель импульсов 3, счетчик временных интервалов 4, коммутатор 5, первый 6 и второй 7 формирователи переменной поиска, первый 8 и второй 9 суммирующие счетчики, первый 10 и второй 11 блоки памяти, блок деления 12, классификатор 13, регистр стратегии поиска 14, формирователь сигналов сброса 15, блок отображения и записи данных 16, блок изменения пороговых сигналов 17, таймер текущих суток 18, блок формирования порога усечения 19, структурный анализатор 20, третий 21, четвертый 22, пятый 23 блоки памяти и блок обработки нечетких комбинаций 24.

Выход 014 формирователя сигналов текущей оценки 1 подключен к управляющему входу 54 коммутатора 5, выходы 56 «Изменение состояния обстановки – Изм» и 57 «Отсутствие изменения состояния обстановки – Отс» которого подключены к входам 62 и 71 соответственно первого 6 и второго 7 формирователей переменной поиска, выход 74 второго формирователя переменной поиска 7 подключен к информационному входу 92 второго суммирующего счетчика 9, выход 91 которого подключен к информационному входу 111 второго блока памяти 11 и второму информационному входу 122 блока деления 12, выход 123 которого подключен к информационному входу 136 классификатора 13, выходы 132 «Изменение состояния обстановки – П» и 133 «Отсутствие изменения состояния обстановки – О» которого подключены соответственно к одноименным входам 151 и 152 формирователя сигналов сброса 15 и к одноименным входам 169 и 1610 блока отображения и записи данных 16, выход 153 «Сброс» формирователя сигналов сброса 15 подключен к входу 103 «Сброс» первого блока памяти 10, входу 114 «Сброс» второго блока памяти 11, входу 43 «Сброс» счетчика временных интервалов 4 и входу 1910 «Сброс» блока формирования порога усечения 19, выход 198 «Максимальный номер временного интервала – Nmax» которого подключен к одноименным входам 145, 64 и 73 соответственно регистра стратегии поиска 14, первого 6 и второго 7 формирователей переменной поиска, выход 63 первого формирователя переменной поиска 6 подключен к информационному входу 81 первого суммирующего счетчика 8, выход 82 которого подключен к первому информационному входу 121 блока деления 12, выходы 024 «Изменение состояния обстановки – Изм» и 025 «Отсутствие изменения состояния обстановки – Отс» дискриминатора зон значений оценки 2 подключены соответственно к одноименным входам 52 и 53 коммутатора 5, первый выход 31 распределителя импульсов 3 подключен к входам синхронизации 013 и 023 соответственно формирователя сигналов текущей оценки 1 и дискриминатора зон значений оценки 2, а также к тактовому входу 41 счетчика временных интервалов 4, выход 42 «Номер текущего временного интервала – Nтек» которого подключен к одноименным входам 199 и 146 соответственно блока формирования порога усечения 19 и регистра стратегии поиска 14, выходы 143 «Значение верхнего порога классификации – Пклв» и 144 «Значение нижнего порога классификации – Пклн» которого подключены к одноименным входам 134 и 135 классификатора 13, второй выход 32 распределителя импульсов 3 подключен к синхронизирующему входу 51 коммутатора 5, третий выход 33 распределителя импульсов 3 подключен к входам синхронизации 102 и 112 первого 10 и второго 12 блоков памяти, выходы 101 и 113 соответственно первого 10 и второго 11 блоков памяти подключены к сигнальным входам 83 и 93 соответственно первого 8 и второго 9 суммирующих счетчиков, четвертый выход 34 распределителя импульсов 3 подключен к синхронизирующему входу 131 классификатора 13, выходы 172 «Верхнее значение порога поиска – Пв» и 173 «Нижнее значение порога поиска – Пн» блока изменения пороговых сигналов 17 подключены соответственно к одноименным входам 141 и 142 регистра стратегии поиска 14 и соответственно к одноименным входам 196 и 197 блока формирования порога усечения 19, входы 174 «Пуск» и 175 «Порог» блока изменения пороговых сигналов 17 подключены к одноименным входам 191 и 192 блока формирования порога усечения 19 и являются соответственно входами «Пуск» и «Порог» устройства, вход 193 «Числовое значение единицы – 1», вход 194 «Максимальный номер временного интервала – Nmax», и вход 195 «Объем выборки интервала анализа – Vвыб» блока формирования порога усечения 19 являются одноименными входами устройства, вход 61 «Зона 1» первого формирователя переменной поиска 6 и вход 72 «Зона 2» второго формирователя переменной поиска 7 являются соответственно входами «Зона 1» и «Зона 2» устройства, вход 162 «Неизвестный признак», вход 163 «Искомый признак» и вход 164 «Адрес неизвестного признака – Адрес НП» блока отображения и записи данных 16 подключены соответственно к одноименным выходам 2010, 2011 и 2012 структурного анализатора 20, выход 204 «Адрес» которого подключен к одноименным входам 214, 224 и 234 соответственно третьего 21, четвертого 22 и пятого 23 блоков памяти, выход 213 «Данные 1» третьего блока памяти 21 подключен к одноименным входам 165 и 201 соответственно блока отображения и записи данных 16 и структурного анализатора 20, выход 223 «Данные 2» четвертого блока памяти 22 и выход 233 «Данные 3» пятого блока памяти 23 подключены соответственно к одноименным входам 202 и 203 структурного анализатора 20, выход 205 «Тактовые импульсы» которого подключен к одноименным входам 225 и 235 соответственно четвертого 22 и пятого 23 блоков памяти, выход 166 «Данные 1 – запись», выход 167 «Данные 2 – запись» и выход 168 «Данные 3 – запись» блока отображения и записи данных 16 подключены к одноименным входам 211, 221 и 231 соответственно третьего 21, четвертого 22 и пятого 23 блоков памяти, выход 1611 «Адрес 3 – запись» блока отображения и записи данных 16 подключен к одноименному входу 232 пятого блока памяти 23, выход 1613 «Адрес 1, 2 – запись» блока отображения и записи данных 16 подключен к одноименным входам 212 и 222 соответственно третьего 21 и четвертого 22 блоков памяти, информационный 207 и синхронизирующий 208 входы структурного анализатора 20 являются соответственно информационным и синхронизирующим входами устройства. Выход 181 «Время» таймера текущих суток 18 подключен к одноименным входам 011, 022, 35, 1612 и 171 соответственно формирователя сигналов текущей оценки 1, дискриминатора зон значений оценки 2, распределителя импульсов 3, блока отображения и записи данных 16 и блока изменения пороговых сигналов 17, информационный выход 206 структурного анализатора 20 подключен к информационным входам 012 и 021 соответственно формирователя сигналов текущей оценки 1 и дискриминатора зон значений оценки 2, выход 209 «Детерминированная комбинация» структурного анализатора 20 соединен с проверочным входом 241 блока обработки нечетких комбинаций 24, верификационный выход 242 которого подключен к входу 161 «Детерминированная комбинация» блока отображения и записи данных 16.

Блок обработки нечетких комбинаций 24 (фиг. 2) предназначен для последовательного сравнения (по количеству двоичных чисел, характеризующих любую детерминированную последовательность) поступающих в двоичном коде детерминированных комбинаций и принятия решения об их математической природе – детерминированная комбинация задана (идентифицирована) параметрически или с использованием функции принадлежности, характерной для нечетких множеств, а также для математически корректного преобразования детерминированных комбинаций заданных (идентифицированных) в нечеткой форме (не параметрически) к виду, пригодному для достоверного (четкого, однозначного) параметрического оценивания структурно-статистических характеристик потока данных в интересах мониторинга информационного трафика.

Блок обработки нечетких комбинаций 24 (фиг. 2) состоит из счетчика 24.1, регистра хранения 24.2, регистрирующего счетчика 24.3, вычислителя дополнения 24.4, основного 24.5 и вспомогательного 24.6 запоминающих элементов, основного 24.7 и вспомогательного 24.8 вычислителей пересечения, вычислителя объединения 24.9 и анализатора уровня принадлежности 24.10, выход которого 24.10-2 объединен с транзитным выходом 24.2-3 регистра хранения 24.2 и является верификационным выходом 242 блока обработки нечетких комбинаций 24. Вход 24.1-1 счетчика 24.1 является проверочным входом 241 блока 24, выход 24.1-2 счетчика 24.1 соединен с входом 24.2-2 регистра хранения 24.2, проверочный выход 24.2-1 регистра хранения 24.2 соединен с входом 24.3-1 регистрирующего счетчика 24.3, первый 24.3-2 и второй 24.3-3 выходы которого соединены соответственно с входом 24.5-1 основного запоминающего элемента 24.5 и прямым входом 24.6-1 вспомогательного запоминающего элемента 24.6, а также соответственно с первым 24.4-1 и вторым 24.4-2 входами вычислителя дополнения 24.4, выход 24.5-2 основного запоминающего элемента 24.5 и выход 24.6-2 вспомогательного запоминающего элемента 24.6 подключены соответственно к главному входу 24.7-1 основного вычислителя пересечения 24.7 и к главному входу 24.8-1 вспомогательного вычислителя пересечения 24.8, к дополнительным входам 24.7-2 и 24.8-2 основного 24.7 и вспомогательного 24.8 вычислителей пересечения подключены соответственно первый 24.4-3 и второй 24.4-4 выходы вычислителя дополнения 24.4, выходы 24.7-3 и 24.8-3 основного 24.7 и вспомогательного 24.8 вычислителей пересечения подключены соответственно к первому 24.9-1 и второму 24.9-2 входам вычислителя объединения 24.9, выход 24.9-3 которого соединен с дополнительным входом 24.4-5 вычислителя дополнения 24.4, дополнительным входом 24.6-3 вспомогательного запоминающего элемента 24.6 и входом 24.10-1 анализатора уровня принадлежности 24.10.

Счетчик 24.1 блока обработки нечетких комбинаций 24 предназначен для регистрации и последовательного сравнения (по количеству двоичных чисел, характеризующих любую детерминированную последовательность) поступающих в двоичном коде детерминированных комбинаций. Техническая реализация счетчика 24.1 возможна на базе серийно выпускаемого синхронного двоичного счетчика, как показано в работе [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 459-460, рис. 13.5].

Регистр хранения 24.2 блока обработки нечетких комбинаций 24 предназначен для хранения данных и принятия решения о математической природе этих данных – двоичного кода, характеризующего поступающую детерминированную комбинацию, эта комбинация наблюдается (задана, идентифицирована) параметрически: количественно, вероятностно или качественно, с использованием функции принадлежности, характерной для нечетких множеств. Регистр хранения 24.2 может быть реализован на базе типового регистра памяти, описанного в литературе [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 443-445, рис. 12.8].

Регистрирующий счетчик 24.3 блока обработки нечетких комбинаций 24 предназначен для регистрации и сортировки в двоичном коде информации на две составляющие – по начальному количеству мнений экспертов (количество экспертов равно двум) о каждом из нечетко наблюдаемых (заданных) значений двоичного кода, характеризующих поступающую детерминированную комбинацию. Регистрирующий счетчик 24.3 может быть технически реализован на базе серийно выпускаемого двоичного синхронного счетчика с последовательным переносом на T-триггерах, как описано в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с., С. 240-242, рис. 4.28].

Вычислитель дополнения 24.4 блока обработки нечетких комбинаций 24 предназначен для осуществления в двоичном коде операции арифметического вычитания из единицы значений функций принадлежности нечетких множеств. Частным случаем технической реализации вычислителя дополнения 24.4 может служить типовое арифметико-логическое устройство (АЛУ), описанное, например, в [Основы электроники: учебник для СПО / О.В. Миловзоров, И.Г. Панков. 5 изд., перераб. и доп. – М.: Издательство Юрайт, 2016. – 407 с. С. 186-189, рис. 3.8.1].

Основной запоминающий элемент 24.5 блока обработки нечетких комбинаций 24 предназначен для хранения нечеткой информации от первого эксперта и передачи в двоичном коде значений функций принадлежности нечетких множеств на главный вход 24.7-1 основного вычислителя пересечения 24.7. Основной запоминающий элемент 24.5 реализуется в виде типового серийно выпускаемого динамического оперативного запоминающего устройства, как показано в литературе [Основы электроники: учебник для СПО / О.В. Миловзоров, И.Г. Панков. – 5-е изд., перераб. и доп. – М.: Издательство Юрайт, 2016. – 407 с. С. 229-231, рис. 4.3.2].

Вспомогательный запоминающий элемент 24.6 блока обработки нечетких комбинаций 24 предназначен для хранения нечеткой информации от второго эксперта и передачи в двоичном коде значений функций принадлежности нечетких множеств на главный вход 24.8-1 вспомогательного вычислителя пересечения 24.8. Вспомогательный запоминающий элемент 24.6 отличается от основного запоминающего элемента 24.5 лишь наличием дополнительного входа, который технически может быть легко объединен с прямым входом, что позволяет осуществить реализацию вспомогательного запоминающего элемента 24.6 аналогично основному запоминающему элементу 24.5, в виде динамического оперативного запоминающего устройства, как описано в [Основы электроники: учебник для СПО / О.В. Миловзоров, И.Г. Панков. – 5-е изд., перераб. и доп. – М.: Издательство Юрайт, 2016. – 407 с. С. 229-231, рис. 4.3.2].

Основной вычислитель пересечения 24.7 блока обработки нечетких комбинаций 24 предназначен для выполнения в двоичном коде математической операции пересечения нечеткого множества, формулируемого первым экспертом с дополнением нечеткого множества, формулируемого вторым экспертом. Основной вычислитель пересечения 24.7 представляет собой цифровой узел сравнения, описанный в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с., С. 102-104, рис. 2.6].

Вспомогательный вычислитель пересечения 24.8 блока обработки нечетких комбинаций 24 предназначен для выполнения в двоичном коде математической операции пересечения нечеткого множества, формулируемого вторым экспертом с дополнением нечеткого множества, формулируемого первым экспертом. Вспомогательный вычислитель пересечения 24.8 идентичен основному вычислителю пересечения 24.7 и также может быть технически реализован на базе цифрового узла сравнения, описанного в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с., С. 102-104, рис. 2.6].

Вычислитель объединения 24.9 блока обработки нечетких комбинаций 24 предназначен для реализации завершающего цикла дизъюнктивного суммирования – определения объединения нечетких множеств. Вычислитель объединения 24.9 представляет собой цифровой узел сравнения и может быть технически реализован в виде серийно выпускаемого быстродействующего цифрового компаратора, как показано в работе [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 428-429, рис. 11.9].

Анализатор уровня принадлежности 24.10 блока обработки нечетких комбинаций 24 предназначен для однозначного выбора (присвоения) количественных значений анализируемых нечетких параметров детерминированной комбинации – для итогового получения четких, однозначных (достоверных) значений параметров детерминированной комбинации, определяющей структурно-статистические характеристики потока данных в интересах мониторинга информационного трафика. Анализатор уровня принадлежности 24.10 представляет собой серийно выпускаемый программируемый ТТЛ-компаратор типа 74LS85, описанный в справочнике [Микросхемы ТТЛ. Том 1.: Пер. с нем. – М.: ДМК Пресс, 2001. – 384 с. (справочник), С. 143-144, рис. б/н].

Формирователь сигналов текущей оценки 1, входящий в общую структурную схему, предназначен для выработки по окончании текущего интервала анализа двоичного сигнала, характеризующего состояние обстановки и принимающего значения «Изм» или «Отс». Структура формирователя сигналов текущей оценки 1, а также алгоритм его работы известны и подробно описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 2).

Дискриминатор зон значений оценки 2, входящий в общую структурную схему, предназначен для выработки сигнала о номере зоны того состояния, в котором находится входной информационный поток соответствующей интенсивности. Структура дискриминатора зон значений оценки 2, а также алгоритм его работы известны и подробно описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 3).

Распределитель импульсов 3, входящий в общую структурную схему, предназначен для синхронизации работы всего устройства посредством формирования четырех импульсных последовательностей, сдвинутых относительно друг друга на некоторую величину Δt. Структура распределителя импульсов 3, а также алгоритм его работы известны и подробно описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 4).

Счетчик временных интервалов 4, входящий в общую структурную схему, предназначен для подсчета количества наблюдаемых интервалов времени и выдачи комбинации о номере временного интервала «Nтек». Счетчик временных интервалов 4 может быть реализован технически на базе серийно выпускаемого суммирующего счетчика с управляемым сбросом, схема которого известна и описана, например, в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с., С. 247-248, рис. 3.47].

Коммутатор 5, входящий в общую структурную схему, предназначен для коммутации сигнала о номере зоны на вход соответствующего формирователя переменной поиска по сигналу управления, поступающему от формирователя сигналов текущей оценки 1 и принимающему значения «Изм» и «Отс». Структура коммутатора 5, алгоритм его работы известны, детально описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 5).

Первый 6 и второй 7 формирователи переменной поиска, входящие в общую структурную схему, предназначены для построения приращений апостериорных интегральных функций распределения вероятностей нормального FО(N) (первый формирователь переменной поиска 6) и отклоненного FП(N) (второй формирователь переменной поиска 7) состояния входного информационного потока на N-м интервале наблюдения. Схемы первого 6 и второго 7 формирователей переменной поиска идентичны, их структура, а также алгоритмы работы известны, описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 6).

Первый 8 и второй 9 суммирующие счетчики, входящие в общую структурную схему, предназначены для сложения значений приращений FО(N) и FП(N) с соответствующими значениями эмпирической интегральной функции распределения вычисленной за N-1 временной интервал FО(N-1) и FП(N-1). Первый 8 и второй 9 суммирующие счетчики представляют собой последовательные многоразрядные арифметические сумматоры, схемы которых известны и описаны, например, в [Миловзоров О.В., Панков И.Г. Основы электроники: учебник для СПО. – 5-е изд., перераб. и доп. – М.: Издательство Юрайт, 2016. – 407 с., С. 182-183, рис.3.38].

Первый 10 и второй 11 блоки памяти, входящие в общую структурную схему, предназначены для хранения приращений FО(N) и FП(N) в течение одного интервала анализа. Первый 10 и второй 11 блоки памяти идентичны и могут быть реализованы технически на базе серийно выпускаемых универсальных регистров параллельного действия, схемы которых известны и описаны, например, в [Миловзоров О.В., Панков И.Г. Основы электроники: учебник для СПО. – 5-е изд., перераб. и доп. – М.: Издательство Юрайт, 2016. – 407 с., С. 206-207, рис.3.52].

Блок деления 12, входящий в общую структурную схему, предназначен для деления приращения FП(N) на приращение FО(N) и выдачи отношения правдоподобия. Блок деления 12 представляет собой устройство деления двух q-разрядных двоичных чисел без восстановления остатка, схема которого известна и описана в [Бочаров К.П., Немшилов Н.Н., Петров Е.И., Сулин Л.И. Вычислительные комплексы автоматизированных систем управления. – Л.: ВАС, 1984. – 368 с., С. 88-90, рис.3.24].

Классификатор 13, входящий в общую структурную схему, предназначен для выработки сигналов «Изм» или «Отс» на основе сравнения входной информации с пороговыми значениями. Структура классификатора 13, а также алгоритм его работы известны и подробно описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 7).

Регистр стратегии поиска 14, входящий в общую структурную схему, предназначен для формирования интервального либо точечного значений порогов классификации в зависимости от того, является ли номер интервала поиска предельным или нет. Структура регистра стратегии поиска 14, а также алгоритм его работы известны и детально описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 8).

Формирователь сигнала сброса 15, входящий в общую структурную схему, предназначен для объединения сигналов «Изм» и «Отс», их усиления и согласования с последующими блоками. Формирователь сигнала сброса 15 может быть реализован технически на базе серийно выпускаемой двухвходовой схемы ИЛИ, структура и алгоритмы работы которой известны и описаны, например, в [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 39-40, рис. 1.22].

Блок отображения и записи данных 16, входящий в общую структурную схему, предназначен для отображения информации о наличии искомых и неизвестных верифицированных (проанализированных и, в случае необходимости – преобразованных в блоке обработки нечетких комбинаций 24) детерминированных комбинаций и изменений интенсивности входного информационного потока, записи не определенных ранее известных верифицированных детерминированных комбинаций в четвертый блок памяти 22 с одновременным изменением в третьем блоке памяти 21 значения о количестве известных верифицированных детерминированных комбинаций, хранящихся в ячейках четвертого блока памяти 22, записи не определенных ранее искомых верифицированных детерминированных комбинаций в пятый блок памяти 23. Запись в третий 21, четвертый 22 и пятый 23 блоки памяти осуществляется по адресу, определенному вычислителем хэш-функции 20.13 структурного анализатора 20. Структура блока отображения и записи данных 16 известна, детально описана в прототипе (см. патент РФ №2290691 «Устройство мониторинга информационного трафика» МПК G06F 17/18, G06F 17/30, опубликован 27.12.2006, Бюл. № 36), этот блок может быть реализован технически на базе микропроцессора, как показано в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с., С. 378-384, рис. 6.21]. Алгоритм работы блока отображения и записи данных 16 известен, подробно описан в прототипе и проиллюстрирован на фиг. 4 данного описания.

Блок изменения пороговых сигналов 17, входящий в общую структурную схему, предназначен для изменения значений пороговых сигналов в зависимости от времени суток. Структура блока изменения пороговых сигналов 17, а также алгоритм его работы известны и подробно описаны в (см. патент РФ №2116670 «Устройство поиска информации», МПК G06F 17/30, опубликован 07.04.1997 г., фиг. 9).

Таймер текущих суток 18, входящий в общую структурную схему, предназначен для установки времени суток всего устройства. Структура таймера текущих суток 18 известна, описана в прототипе (см. патент РФ №2290691 «Устройство мониторинга информационного трафика» МПК G06F 17/18, G06F 17/30, опубликован 27.12.2006, Бюл. № 36), он может быть реализован технически по схеме программируемого интервального таймера, как показано в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. – 3-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2010. – 816 с., С. 486-493, рис. 7.22].

Блок формирования порога усечения 19, входящий в общую структурную схему, предназначен для корректировки значения максимального номера временного интервала «Nmax» адекватно входному информационному потоку на протяжение всего интервала анализа. Структура блока формирования порога усечения 19, а также алгоритм его работы известны и подробно описаны в (см. патент РФ №2149446 «Устройство поиска информации», МПК G06F 17/30, опубликован 20.05.2000, Бюл. №14, фиг. 2).

Структурный анализатор 20, входящий в общую структурную схему, предназначен для выработки сигнала запуска работы всего устройства, хэширования, распознавания искомых и неизвестных детерминированных комбинаций, а также записи этих детерминированных комбинаций на проверочный вход блока обработки нечетких комбинаций 24 для дополнительной верификации (анализа и, в случае необходимости – преобразования). Схема структурного анализатора 20 известна, детально описана в прототипе (см. патент РФ №2290691 «Устройство мониторинга информационного трафика» МПК G06F 17/18, G06F 17/30, опубликован 27.12.2006, Бюл. № 36, фиг. 2) и проиллюстрирована на фиг. 3 данного описания. Структурный анализатор 20 (см. фиг. 3) содержит входной регистр 20.1, дешифратор 20.2, первый 20.3, второй 20.5 и третий 20.15 параллельные регистры, счетчик 20.4, первый 20.6, второй 20.8 и третий 20.12 компараторы, первый 20.7 и второй 20.17 элементы И, элемент НЕ 20.9, первый 20.10 и второй 20.11 элементы ИЛИ, вычислитель хэш-функции 20.13, RS-триггер 20.14 и генератор импульсов 20.16.

Третий блок памяти 21, входящий в общую структурную схему, предназначен для хранения заранее запрограммированных значений о количестве известных верифицированных детерминированных комбинаций, хранящихся в ячейках четвертого блока памяти 22. Техническая реализация третьего блока памяти 21 возможна на базе регистра с функциями постоянного запоминающего устройства, описание работы и схема таких регистров известны и приведены, например, в книге [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 443-445].

Четвертый блок памяти 22, входящий в общую структурную схему, предназначен для хранения заранее запрограммированных известных верифицированных детерминированных комбинаций. Четвертый блок памяти 22 представляет собой регистр с функциями постоянного запоминающего устройства, схема которого известна и описана в [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 443-445].

Пятый блок памяти 23, входящий в общую структурную схему, предназначен для хранения заранее запрограммированных искомых верифицированных детерминированных комбинаций. Техническая реализация пятого блока памяти 23 возможна на базе регистра с функциями постоянного запоминающего устройства, описание работы и схема таких регистров известны и приведены, например, в [Аверченков О.Е. Схемотехника: аппаратура и программы. – М.: ДМК Пресс, 2012. – 588 с., С. 443-445].

Устройство мониторинга информационного трафика работает следующим образом.

Известно [1-5], что с точки зрения верификации наблюдаемых (идентифицируемых) детерминированных комбинаций, характеризующих известные (искомые) или неизвестные признаки входных информационных потоков в рамках мониторинга трафика, существует возможность распознавания (определения) этих комбинаций, наблюдаемых и заданных как количественно, так и качественно, нечетко (с привлечением лингвистической переменной). Эта возможность реализуется с использованием математики нечетких множеств, нечетких вычислительных методов и алгоритмов, позволяющих путем последовательных преобразований, осуществить переход от нечетко распознанных (наблюдаемых, идентифицируемых) детерминированных комбинаций к виду, пригодному для четкого, однозначного принятия достоверного решения о значениях элементов этой комбинации, в рамках конкретного сценария мониторинга информационного трафика. При этом детерминированная комбинация, характеризующая известные или неизвестные признаки входных информационных потоков, может быть верифицирована на основе математических методов принятия решений в слабоформализуемых задачах – нечетких вычислительных методов и алгоритмов, которые достаточно просто могут быть аппаратно реализуемы.

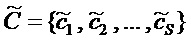

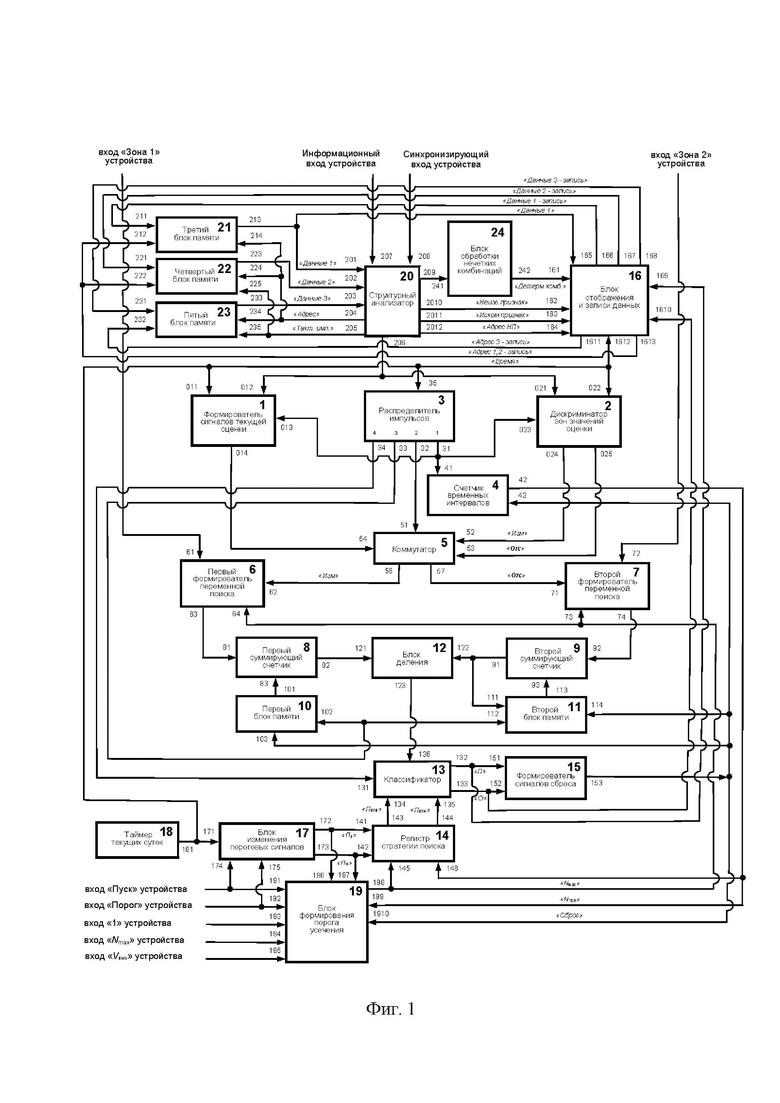

Нечеткие вычислительные методы и алгоритмы работают на основе экспертных оценок, а для решения задачи объединения мнений экспертов, знания которых используются, например, для верификации наблюдаемых (идентифицируемых) детерминированных комбинаций, используется один из типовых вычислительных алгоритмов теории нечетких множеств – алгоритм дизъюнктивного суммирования нечетких множеств. С учетом того, что в прототипе множество значений детерминированных комбинаций (т.е., множество значений q-разрядных двоичных чисел, характеризующих структурно-статистические атрибуты (параметры) анализируемого входного информационного массива – множество значений комбинаций бит, описывающих структуру трафика, очередность и интенсивность поступления данных в рамках информационного потока) может быть представлено в виде

С = {с1, с2, …, сS}, (1)

то с точки зрения рассматриваемого подхода к распознаванию (определению) детерминированных комбинаций, возможно представление значений комбинаций бит не только количественно, численно, но и нечетко, в виде нечеткого множества значений этих q-разрядных двоичных чисел вида:

где

При этом число S соответствует возможному количеству значений комбинаций бит (в рамках детерминированной комбинации) и зависит от количества вариантов сочетаний этих q-разрядных двоичных чисел, достаточных для идентификации детерминированной комбинации и от количества экспертов, задействованных для реализации вычислительного нечеткого алгоритма их верификации. В нашем случае S может принимать значения от 2 (двух) до 20 (двадцати).

Иными словами, анализ результатов работ [1-5] позволяет предусмотреть в устройстве возможность обработки детерминированных комбинаций, описанных (наблюдаемых, идентифицируемых) как количественно, так и нечетко (с привлечением лингвистической переменной).

Формально изменится лишь ключевое выражение (1) на выражение (2), характеризующее, в нашем случае, нечеткие знания операторов, эксплуатирующих устройство, о множестве значений комбинаций бит (в рамках детерминированной комбинации), элементы которого получены с помощью экспертов. Данная трактовка позволяет ввести алгоритм последовательного сведения нечетко идентифицированных детерминированных комбинаций к виду, обуславливающему возможность параметрического оценивания структурно-статистических атрибутов (параметров) анализируемого входного информационного массива в интересах достоверного мониторинга трафика.

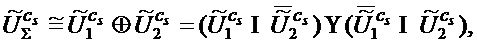

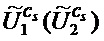

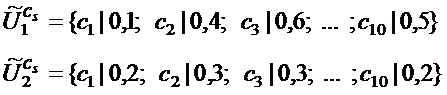

Для решения задачи объединения мнений экспертов об анализируемой детерминированной комбинации (о значениях комбинаций бит информационного потока), используется одна из типовых операций над нечеткими множествами – операция дизъюнктивного суммирования [1-5]. При этом дизъюнктивная сумма, например, двух нечетких множеств (по количеству экспертов), определяется в терминах объединений и пересечений следующим образом:

где

Полученная дизъюнктивная сумма

Для окончательной идентификации (однозначного выбора) количественных значений нечетких параметров детерминированной комбинации, используют функцию [5]:

характеризующую максимальное значение

Таким образом, результаты анализа работ [1-5] и анализа выражений (1)–(4) позволяют сделать вывод о технической возможности реализации однозначной верификации детерминированных комбинаций с количественно и нечетко заданными параметрами. Рассмотренный в [1-4] и детально описанный в [5] вычислительный нечеткий алгоритм (алгоритм дизъюнктивного суммирования нечетких множеств) позволяет математически корректно устранить нечеткость детерминированных комбинаций, характеризующих структурно-статистические атрибуты (параметры) анализируемого входного информационного массива, позволяет однозначно распознать (верифицировать) истинные значения каждой нечетко заданной (идентифицируемой) комбинации бит (q-разрядных двоичных чисел), определяемые конкретным реальным массивом поступающих данных в текущий момент времени, а в конечном итоге, повысить достоверность поиска и определения известных (искомых) или неизвестных признаков входных информационных потоков, и, как следствие, повысить достоверность мониторинга информационного трафика в условиях, присущих реальной динамике процесса информационного обмена в информационных (информационно-вычислительных или телекоммуникационных) системах, сетях передачи данных с коммутацией пакетов, в социальных сетях и в глобальной сети Интернет – в условиях нечеткости данных об истинных значениях параметров трафика.

На вход вычислительного нечеткого алгоритма, реализуемого в блоке обработки нечетких комбинаций 24, поступают данные, характеризующие детерминированные комбинации, распознанные (определенные) в блоке 20 как количественно, так и нечетко. Определяется, какие из детерминированных комбинаций в данный момент времени распознаны количественно, а какие идентифицированы нечетко. В целях верификации детерминированных комбинаций необходимо математически корректно, используя дизъюнктивное суммирование нечетких множеств, преобразовать распознанные нечетко детерминированные комбинации. Этапы функционирования вычислительного нечеткого алгоритма подробно, алгоритмически и аналитически, описаны в [5]. На выходе вычислительного нечеткого алгоритма имеем выходной образ – преобразованные значения комбинации бит (q-разрядных двоичных чисел), которые четко (достоверно) характеризуют интегрированное мнение экспертов о принадлежности этой детерминированной комбинации к пространству достоверных, верифицированных комбинаций, характеризующих структурно-статистические атрибуты (параметры) анализируемого входного информационного потока в интересах мониторинга трафика.

С учетом этого осуществляется мониторинг информационного трафика в заявленном устройстве с дополнительной верификацией (анализом и, в случае необходимости – преобразованием с помощью методов теории нечетких множеств) искомых и неизвестных детерминированных комбинаций.

Входной информационный поток, синхронизированный с тактовыми импульсами, поступает на информационный вход 207 структурного анализатора 20 (фиг. 1).

При этом тактовые импульсы, синхронизирующие входной информационный поток, фиксируют текущее время интервала анализа трафика контролируемой сложной информационной (информационно-вычислительной или телекоммуникационной) системы.

Структурный анализатор 20 (фиг. 3) вырабатывает сигнал запуска работы всего устройства при наличии комбинации начала сообщения во входном информационном потоке, а также осуществляет поиск неизвестных и заранее определенных искомых исходных (не верифицированных) детерминированных комбинаций и, при их наличии, выдает соответственно сигнал на выход 2010 «Неизвестный признак» или выход 2011 «Искомый признак», а также со своего выхода 209 «Детерминированная комбинация» выдает исходную детерминированную комбинацию, характеризующую структурно-статистические атрибуты (параметры) анализируемого входного информационного потока, на проверочный вход 241 блока обработки нечетких комбинаций 24, с верификационного выхода 242 которого уже верифицированная детерминированная комбинация поступает на вход 161 «Детерминированная комбинация» блока отображения и записи данных 16. Таким образом, объектом распознавания в блоке 20 за текущий интервал анализа являются искомые и неизвестные исходные (не верифицированные) детерминированные комбинации во входном информационном потоке.

Каждую исходную (не верифицированную) детерминированную комбинацию, представляющую собой q-разрядное двоичное число, делят на заранее определенное q-разрядное двоичное число с остатком. Остаток является значением хэш-функции. По найденному значению хэш-функции, являющемуся адресом, в четвертом блоке памяти 22 находят заранее запрограммированные известные детерминированные комбинации, сравнивают их с исходной (не верифицированной) поступившей детерминированной комбинацией на наличие совпадения. В случае несовпадения ни одной из хранящихся в четвертом блоке памяти 22 детерминированной комбинации с поступившей выдается сигнал «Неизвестный признак» отображаемый блоком отображения и записи данных 16. Также по найденному значению хэш-функции, являющемуся адресом, в пятом блоке памяти 23 находят заранее запрограммированные искомые детерминированные комбинации и сравнивают их с поступившей исходной (не верифицированной) детерминированной комбинацией на наличие совпадения. В случае совпадения одной из хранящихся в пятом блоке памяти 23 детерминированной комбинации с поступившей выдается сигнал «Искомый признак», отображаемый блоком отображения и записи данных 16.

Во входном регистре 20.1 структурного анализатора 20 (фиг. 3) исходная (не верифицированная) детерминированная комбинация под действием синхроимпульсов преобразуется из последовательного кода в параллельный и поступает на информационный вход 20.2-1 дешифратора 20.2, информационный вход 20.3-2 первого параллельного регистра 20.3 и информационный вход 20.13-1 вычислителя хэш-функции 20.13.

В дешифраторе 20.2 структурного анализатора 20 (см. фиг. 3) при появлении комбинации начала сообщения на строго определенных выходных разрядах и на выходе 20.1-3 входного регистра 20.1, а затем, после дешифровки, на выходе 20.2-2 дешифратора 20.2 вырабатывается сигнал запуска работы всего устройства, который поступает на управляющий вход 20.3-1 первого параллельного регистра 20.3, вход 20.4-2 «Сброс» счетчика 20.4, запускающий вход 20.13-2 вычислителя хэш-функции 20.13, вход 20.14-2 «Установка 1» RS-триггера 20.14 и на информационный выход 206 структурного анализатора 20.

По этому сигналу детерминированная комбинация с выхода 20.1-3 входного регистра 20.1, кроме дешифратора, записывается в первый параллельный регистр 20.3 и в вычислитель хэш-функции 20.13, на выходе RS-триггера 20.14 по сигналу от дешифратора 20.2 устанавливается уровень логической единицы. В первом параллельном регистре 20.3 детерминированная комбинация хранится в течение одного начального (стартового) интервала анализа. С выхода 20.3-3 первого параллельного регистра 20.3 детерминированная комбинация поступает на информационный вход 20.5-2 второго параллельного регистра 20.5 и первые входы 20.8-1 и 20.12-1 соответственно второго 20.8 и третьего 20.12 компараторов.

Счетчик 20.4 структурного анализатора 20 (см. фиг. 3) производит подсчет количества тактовых импульсов, поступающих на его вход 20.4-1 с выхода 20.17-3 второго элемента И 20.17, и выдает комбинацию в первый компаратор 20.6 о количестве поступивших известных детерминированных комбинаций от четвертого блока памяти 22 в структурный анализатор 20 в течение одного интервала анализа.

В первом компараторе 20.6 структурного анализатора 20 (см. фиг. 3) под действием тактовых импульсов, поступающих на его управляющий вход 20.6-3 от второго элемента И 20.17, выполняется операция сравнения двух комбинаций, представляющих собой два m-разрядных двоичных числа, первое из которых поступает с выхода 20.4-3 счетчика 20.4 на первый вход 20.6-1 первого компаратора 20.6, а второе – с выхода 213 «Данные 1» третьего блока памяти 21 на второй вход 20.6-2 первого компаратора 20.6, и при наличии совпадения, на выходе 20.6-4 «Равенство – А=В» вырабатывается сигнал «1», который поступает на первый вход 20.7-1 первого элемента И 20.7.

Во втором компараторе 20.8 структурного анализатора 20 (см. фиг. 3) под действием тактовых импульсов, поступающих на его управляющий вход 20.8-3 от второго элемента И 20.17, выполняется операция сравнения двух детерминированных комбинаций, представляющих собой два q-разрядных двоичных числа, первое из которых поступает с выхода 20.3-3 первого параллельного регистра 20.3 на первый вход 20.8-1 второго компаратора 20.8, а второе – с выхода 223 «Данные 2» четвертого блока памяти 22 на второй вход 20.8-2 второго компаратора 20.8, и при наличии совпадения, на выходе 20.8-4 «Равенство – А=В» второго компаратора 20.8 вырабатывается сигнал «1», который поступает на второй вход 20.11-2 второго элемента ИЛИ 20.11 и на вход 20.9-1 элемента НЕ 20.9.

При отсутствие сигнала «1» (см. фиг. 3) на выходе 20.8-4 «Равенство – А=В» второго компаратора 20.8 на выходе 20.9-2 элемента НЕ 20.9 вырабатывается сигнал «1», поступающий на второй вход 20.7-2 первого элемента И 20.7. При этом при наличии сигнала «1» на первом входе 20.7-1 первого элемента И 20.7, поступающего с выхода 20.6-4 «Равенство – А=В» первого компаратора 20.6, на выходе 20.7-3 первого элемента И 20.7 вырабатывается сигнал «1», поступающий на первые входы 20.10-1 и 20.11-1 соответственно первого 20.10 и второго 20.11 элементов ИЛИ, управляющий вход 20.15-2 третьего параллельного регистра 20.15 и через выход 2010 «Неизвестный признак» структурного анализатора 20 на вход 162 «Неизвестный признак» блока отображения и записи данных 16.

При поступлении сигнала «1» (см. фиг. 3) на любой вход первого элемента ИЛИ 20.10 с выхода 20.7-3 первого элемента И 20.7 или выхода 20.12-4 «Равенство – А=В» третьего компаратора 20.12, на его выходе вырабатывается сигнал «1», поступающий на управляющий вход 20.5-1 второго параллельного регистра 20.5. По этому сигналу детерминированная комбинация записывается во второй параллельный регистр 20.5 и поступает через выход 209 «Детерминированная комбинация» структурного анализатора 20 на проверочный вход 241 блока обработки нечетких комбинаций 24.

Блок обработки нечетких комбинаций 24 может быть реализован в соответствии со схемой, предложенной на фиг. 2. Исходная (до верификации) детерминированная комбинация, характеризующая структурно-статистические атрибуты (параметры) анализируемого входного информационного потока, с выхода 209 «Детерминированная комбинация» структурного анализатора 20 через проверочный вход 241 блока обработки нечетких комбинаций 24 поступает на вход 24.1-1 счетчика 24.1, который рассчитан на регистрацию в каждой ячейке (разряде) одного двоичного числа (бита) поступающей информации.

Последовательное сравнение (по количеству двоичных чисел, характеризующих любую детерминированную последовательность) поступающих в двоичном коде детерминированных комбинаций и принятия решения об их математической природе – детерминированная комбинация задана (идентифицирована) параметрически или с использованием функции принадлежности, характерной для нечетких множеств, осуществляется в счетчике 24.1 и регистре хранения 24.2 блока обработки нечетких комбинаций 24 следующим образом.

Если количество двоичных чисел, характеризующих любой q-ый разряд поступающей s-ой (s=

Иными словами, изначально качественная и количественная информация, поступающая с выхода 209 «Детерминированная комбинация» структурного анализатора 20, может различаться по количеству двоичных чисел, характеризующих любой из разрядов поступающей s-ой (s=

С учетом этого факта построены счетчик 24.1 и регистр хранения 24.2 (см. фиг. 2). Оба этих элемента блока обработки нечетких комбинаций 24 рассчитаны на регистрацию, анализ и хранение одного двоичного числа, характеризующего любой из разрядов поступающей детерминированной комбинации.

Если количество двоичных чисел превышает единицу, значит, с точки зрения нечеткой математики – эта детерминированная комбинация поступает в нечеткой форме. В этом случае и регистр хранения счетчик 24.1 и регистр хранения 24.2 блока обработки нечетких комбинаций 24 выполняют функции транзитного узла, причем, с проверочного выхода 24.2-1 регистра хранения 24.2 эта информация в двоичном коде сразу поступает на вход 24.3-1 регистрирующего счетчика 24.3.

Если на вход 24.1-1 счетчика 24.1 блока обработки нечетких комбинаций 24 поступает в двоичном коде одно двоичное число, характеризующее любой из разрядов поступающей s-ой детерминированной комбинации, значит эта детерминированная комбинация поступает (идентифицирована) в четкой форме, имеет количественный смысл, при этом счетчик 24.1 регистрирует эту комбинацию и со своего выхода 24.1-2 направляет ее на вход 24.2-2 регистра хранения 24.2, который через свой транзитный выход 24.2-3 направляет эту информацию (заданную в четкой форме детерминированную комбинацию – количественно заданные, не требующие дополнительной верификации данные, характеризующие структурно-статистические атрибуты (параметры) анализируемого входного информационного потока) через верификационный выход 242 блока обработки нечетких комбинаций 24 на вход 161 «Детерминированная комбинация» блока отображения и записи данных 16.

Информация, требующая дополнительной верификации (наблюдаемая и заданная в нечеткой форме детерминированная комбинация – нечетко идентифицированные данные, характеризующие структурно-статистические атрибуты (параметры) анализируемого входного информационного потока), в двоичном коде с проверочного выхода 24.2-1 регистра хранения 24.2 поступает на вход 24.3-1 регистрирующего счетчика 24.3 блока обработки нечетких комбинаций 24 (фиг. 2). Преобразование (трансформирование) детерминированных комбинаций, заданных в нечеткой форме к виду, пригодному для получения четких, однозначных (достоверных) данных, характеризующих структурно-статистические атрибуты (параметры) анализируемого входного информационного потока, происходит следующим образом. В целом, сущность дальнейшего преобразования (трансформирования) нечетко заданных детерминированных комбинаций в блоке обработки нечетких комбинаций 24, с точки зрения математики, заключается в корректном вычислении интегрированного мнения экспертов (выражение (3)) и принятии решения о максимальном значении функции принадлежности (степень уверенности) этого интегрированного мнения (выражение (4)), определяющем однозначный выбор количественного значения нечеткого параметра – количественного значения двоичного числа, характеризующего любой из разрядов поступающей s-ой детерминированной комбинации.

Нечеткая детерминированная комбинация (нечетко идентифицированные (наблюдаемые, заданные) значения двоичного числа, описывающего любой из разрядов этой комбинации, характеризующей структурно-статистические атрибуты (параметры) анализируемого входного информационного потока), поступает на вход 24.3-1 регистрирующего счетчика 24.3 блока обработки нечетких комбинаций 24 (фиг. 2). Регистрирующий счетчик 24.3 регистрирует и сортирует информацию на две составляющие, в соответствии с количеством мнений экспертов (количеством экспертов) о степени принадлежности конкретной s-ой детерминированной комбинации (

то

где

Анализатор уровня принадлежности 24.10 блока обработки нечетких комбинаций 24 осуществляет получение однозначного итогового результата о степени принадлежности конкретной s-ой детерминированной комбинации к пространству истинных (однозначно, четко определенных) детерминированных комбинаций, опираясь на выражение (4). Являясь, по сути, программируемой схемой сравнения (программируемым ТТЛ-компаратором типа 74LS85), в которой в двоичном коде сравниваются получаемые из вычислителя объединения 24.9 значения функции принадлежности конкретной s-ой нечетко заданной (наблюдаемой) детерминированной комбинации, анализатор уровня принадлежности 24.10, на основе определения максимума функции принадлежности, однозначно, четко и окончательно присваивает (верифицирует) численное значение этой комбинации бит (q-разрядных двоичных чисел), характеризующих структурно-статистические атрибуты (параметры) анализируемого входного информационного потока.

Передача информации на дополнительный вход 24.4-5 вычислителя дополнения 24.4 и на дополнительный вход 24.6-3 вспомогательного запоминающего элемента 24.6 предназначена для случая, когда количество экспертов больше двух. В этом случае определяется дополнение полученного с выхода 24.9-3 вычислителя объединения 24.9 нечеткого множества в вычислителе дополнения 24.4 и полученные с выхода 24.9-3 вычислителя объединения 24.9 значения перезаписываются во вспомогательный запоминающий элемент 24.6, играя роль информации от первого эксперта. Информация от нового (например, третьего) эксперта записывается через регистрирующий счетчик 24.3 в основной запоминающий элемент 24.5 и цикл вычислений повторяется снова.

Таким образом, осуществляется однозначная верификация количественных значений комбинации бит (q-разрядных двоичных чисел), характеризующих структурно-статистические атрибуты (параметры) анализируемого входного информационного потока в соответствии с выражением (4) – анализатор уровня принадлежности 24.10 выдает на своем выходе 24.10-2 в двоичном коде верифицированное, количественное значение конкретной s-ой (s=

Иными словами, происходит преобразование определенных (распознанных) нечетко детерминированных комбинаций, характеризующих входной информационный поток, к виду, пригодному для достоверного (четкого, однозначного) параметрического оценивания структурно-статистических характеристик потока данных в интересах мониторинга информационного трафика.

В результате, на выходе анализатора уровня принадлежности 24.10 и на верификационном выходе 242 блока обработки нечетких комбинаций 24 (см. фиг. 2) получаем информацию, характеризующую (на основе анализа полученного в рамках математики нечетких множеств интегрированного мнения экспертов) истинный вид детерминированной комбинации, преобразованной (верифицированной) в интересах повышения достоверности мониторинга.

Анализатор уровня принадлежности 24.10 записывает, хранит и выдает со своего выхода 24.10-2 через верификационный выход 242 блока обработки нечетких комбинаций 24 на вход 161 «Детерминированная комбинация» блока отображения и записи данных 16 (см. фиг. 1) двоичный код, содержащий верифицированные результаты анализа и обработки детерминированной комбинации – код, четко и однозначно определяющий структурно-статистические атрибуты (параметры) анализируемого входного потока данных в интересах достоверного мониторинга информационного трафика.

Дальнейшие процедуры мониторинга информационного трафика в заявленном устройстве реализуются в соответствии с последовательностью, подробно описанной в прототипе (см. патент РФ №2290691 «Устройство мониторинга информационного трафика» МПК G06F 17/18, G06F 17/30, опубликован 27.12.2006, Бюл. № 36), но с учетом полученных в блоке обработки нечетких комбинаций 24 результатов дополнительной верификации искомых и неизвестных детерминированных комбинаций, следующим образом.

При поступлении сигнала «1» (см. фиг. 3) на любой из трех входов второго элемента ИЛИ 20.11 с выхода 20.7-3 первого элемента И 20.7, выходов 20.8-4 и 20.12-4 «Равенство – А=В» соответственно второго 20.8 или третьего 20.12 компараторов, на его выходе вырабатывается сигнал «1», поступающий на вход 20.14-1 «Установка 0» RS-триггера 20.14. По этому сигналу RS-триггер 20.14 прекращает формировать сигнал «1» на вход 20.17-2 второго элемента И 20.17, при этом с выхода 20.17-3 второго элемента И 20.17 прекращают поступать тактовые импульсы, работа структурного анализатора 20 на данном интервале анализа заканчивается.

В третьем компараторе 20.12 (см. фиг. 3) под действием тактовых импульсов, поступающих на управляющий вход 20.12-3 от второго элемента И 20.17, выполняется операция сравнения двух верифицированных детерминированных комбинаций, представляющих собой два q-разрядных двоичных числа, первое из которых поступает с выхода 20.3-3 первого параллельного регистра 20.3 на первый вход 20.12-1 третьего компаратора 20.12, а второе число – с выхода 233 «Данные 3» пятого блока памяти 23 (см. фиг. 1) на второй вход 20.12-3 третьего компаратора 20.12, и, при наличии совпадения, на выходе 20.12-4 «Равенство – А=В» третьего компаратора 20.12 вырабатывается сигнал «1», который поступает на второй вход 20.10-2 первого элемента ИЛИ 20.10, третий вход 20.11-3 второго элемента ИЛИ 20.11 и через выход 2011 «Искомый признак» структурного анализатора 20 на вход 163 «Искомый признак» блока отображения и записи данных 16.

Вычислитель хэш-функции 20.13 структурного анализатора 20 (см. фиг. 3) производит деление поступившей на его информационный вход 20.13-1 исходной (не верифицированной) детерминированной комбинации, представляющей собой q-разрядное двоичное число, на заранее определенное q-разрядное двоичное число методом восстановления остатка, являющегося значением хэш-функции и представляющего собой также q-разрядное двоичное число, которое поступает на информационный вход 20.15-1 третьего параллельного регистра 20.15 и через выход 204 «Адрес» структурного анализатора 20 (см. фиг. 1) на входы 214, 224 и 234 «Адрес» соответственно третьего 21, четвертого 22 и пятого 23 блоков памяти.

RS-триггер 20.14 структурного анализатора 20 (см. фиг. 3) управляет работой второго элемента И 20.17, выполняющего функцию ключа. RS-триггер 20.14 отпирает ключ (второй элемент И 20.17) при появлении сигнала «1» на входе 20.14-2 «Установка 1» и запирает его при появлении сигнала «1» на входе 20.14-1 «Установка 0».

При поступлении сигнала «1» (см. фиг. 3) на управляющий вход 20.15-1 третьего параллельного регистра 20.15 адрес, сформированный вычислителем хэш-функции 20.13, записывается в третий параллельный регистр 20.15 и с его выхода 20.15-3 через выход 2012 «Адрес НП» структурного анализатора 20 поступает на вход 164 «Адрес НП» (см. фиг. 1) блока отображения и записи данных 16.

Генератор импульсов 20.16 структурного анализатора 20 (см. фиг. 3) формирует импульсы, которые поступают на второй вход 20.17-1 второго элемента И 20.17. С выхода 20.17-3 второго элемента И 20.17 при наличии на первом входе сигнала «1» с выхода 20.14-3 RS-триггера 20.14 тактовые импульсы поступают на информационный вход 20.4-1 счетчика 20.4, на управляющие входы 20.6-3, 20.8-3 и 20.12-3 соответственно первого 20.6, второго 20.8 и третьего 20.12 компараторов, а также на входы 225 и 235 «Тактовые импульсы» (см. фиг. 1) соответственно четвертого 22 и пятого 23 блоков памяти устройства.

С выхода 213 третьего блока памяти 21 структурного анализатора 20 (см. фиг. 3) заранее запрограммированные значения о количестве известных верифицированных детерминированных комбинаций, находящихся в ячейках четвертого блока памяти 22 по адресу, поступающему с выхода 20.13-3 вычислителя хэш-функции 20.13, считываются на второй вход 20.6-2 первого компаратора 20.6. С выхода 223 четвертого блока памяти 22 заранее запрограммированные известные верифицированные детерминированные комбинации, находящиеся по адресу, поступающему с 20.13-3 выхода вычислителя хэш-функции 20.13, последовательно считываются под действием тактовых импульсов, поступающих с выхода 20.17-3 второго элемента И 20.17, на второй вход 20.8-2 второго компаратора 20.8. С выхода 233 пятого блока памяти 23 заранее запрограммированные искомые детерминированные комбинации, находящиеся по адресу, поступающему с выхода 20.13-3 вычислителя хэш-функции 20.13, последовательно считываются под действием тактовых импульсов, поступающих с выхода 20.17-3 второго элемента И 20.17, на второй вход 20.12-2 третьего компаратора 20.12. При этом множества известных и искомых верифицированных детерминированных комбинаций, хранящихся соответственно в четвертом 22 и пятом 23 блоках памяти, одинаковых детерминированных комбинаций не имеют.

Сигнал запуска работы всего устройства с выхода 20.2-2 дешифратора 20.2, поступающий, кроме прочего, на информационный выход 206 структурного анализатора 20 (фиг. 3), вырабатывается для текущего времени интервала анализа трафика контролируемой сложной информационной (информационно-вычислительной или телекоммуникационной) системы.

Таким образом, с информационного выхода 206 структурного анализатора 20 на информационный вход 012 формирователя сигналов текущей оценки 1 и на информационный вход 021 дискриминатора зон значений оценки 2 (см. фиг. 1) поступают логические значения кода, задающего значения времени интервала анализа. Это, по сути, сигнал запуска работы всего устройства анализа трафика контролируемой сложной информационной (информационно-вычислительной или телекоммуникационной) системы.

Формирователь сигналов текущей оценки 1 и дискриминатор зон значений оценки 2 анализируют интенсивность входного потока на интервала анализа. В формирователе сигналов текущей оценки 1 (см. фиг. 1) по окончании времени интервала анализа, вырабатывается двоичный сигнал, характеризующий состояние обстановки. При превышении отклонения числа комбинаций начала сообщений от среднего значения в верхнюю или нижнюю сторону больше порогового, на выходе 014 формирователя сигналов текущей оценки 1 формируется сигнал «Изм», в других случаях вырабатывается сигнал «Отс». С выхода 014 формирователя сигналов текущей оценки 1 сигнал «Изм» или «Отс» поступает на управляющий вход 54 коммутатора 5. В дискриминаторе зон значений оценки 2 вырабатывается сигнал о номере зоны того состояния, в котором находится входной информационный поток соответствующей интенсивности на интервале анализа. Этот номер зоны соответствует более точной оценке состояния обстановки по сравнению с оценкой, получаемой в формирователе сигналов текущей оценки 1. С выходов 024 «Изм» или 025 «Отс» дискриминатора зон значений оценки 2 сигнал соответственно «Изм» или «Отс» поступает на одноименные входы 52 «Изм» или 53 «Отс» коммутатора 5. При этом распределитель импульсов 3 осуществляет синхронизацию работы всего устройства посредством формирования четырех импульсных последовательностей, сдвинутых относительно друг друга на некоторую величину Δt, а счетчик временных интервалов 4 осуществляет подсчет количества наблюдаемых интервалов времени и выдает со своего выхода 42 комбинацию о номере временного интервала на вход 146 «Nтек» регистра стратегии поиска 14 и на вход 199 «Nтек» блока формирования порога усечения 19.