Изобретение относится к устройствам передачи информационного сигнала и может найти применение в системах управления, контроля, измерения, вычислительных и других устройствах различных отраслей техники.

Известна линия задержки, описанная, например, в [1], содержащая несколько последовательно включенных схем НЕ. К недостаткам такого устройства следует отнести невозможность увеличения или повторения времени задержки выходного сигнала без прерывания задержки при повторном входном кратковременном сигнале.

Известно также устройство описанное, например, в [2], содержащее двоичный счетчик импульсов и дешифратор с множеством выходов.

К недостаткам такого устройства также следует отнести невозможность увеличения или повторения времени задержки выходного сигнала без применения задержки при кратковременном повторном входном сигнале.

Поставленная цель достигается тем, что в устройство дополнительно установлены однотактный D-триггер, управляющий внутренним генератором импульсов, а также две схемы ИЛИ и схема ИЛИ-НЕ для управления триггером и, кроме этого, схема И и многоцелевой элемент цифровых структур (МЭЦС) для осуществления повторного отсчета времени.

В качестве прототипа принять устройство, описанное [2].

Целью настоящего изобретения является расширение функциональных возможностей устройства, а именно возможность увеличения или повторения времени задержки выходного сигнала без прерывания задержки при повторном кратковременном входном сигнале.

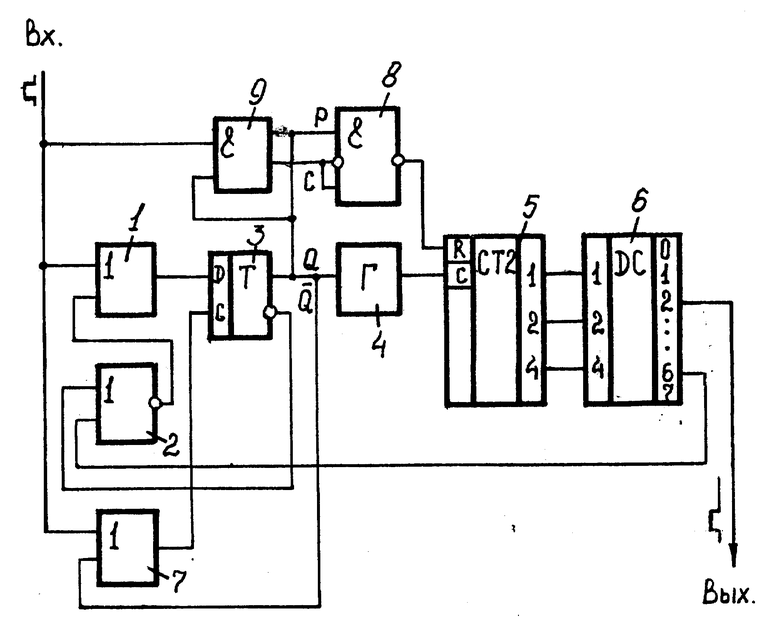

Сущность изобретения поясняется чертежом, где приведена схема устройства.

Устройство (фиг. 1) содержит двухвходовую схему ИЛИ 1, соединенную одним входом с входом Вх устройства, двухвходовую схему ИЛИ-НЕ 2. соединенную своим выходом с вторым входом двухвходовой схемы ИЛИ 1, выход которой соединен с входом D-однотактного D-триггера 3, выход Q которого соединен с генератором импульсов Г 4, выход которого в свою очередь соединен с входом С двоичного счетчика СТ2 5. Двоичные выходы счетчика СТ2 5 соединены с аналогичными двоичными входами дешифратора DC 6. Выход Q триггера 3 соединен также с одним входом двухвходовой схемы ИЛИ 7, к второму входу которой подсоединен вход Вх устройства, а ее выход соединен с входом С триггера 3. Один из входов двухвходовой схемы ИЛИ-НЕ 2 соединен с последним используемым выходом дешифратора DC 6, а второй - с выходом  триггера 3. (МЭЦС) 8 [3] соединен своим выходом с входом R двоичного счетчика СТ2 5, а его синхровход C - с выходом двухвходовой схемы И 9, причем разрешающий вход P МЭЦС соединен с выходом Q триггера 3. Выход Вых устройства соединен с одним из используемых выходов дешифратора DC 6. Число импульсов, подсчитываемых счетчиком до используемого выхода дешифратора, и частота генератора определяют время задержки выходного сигнала при первом управляющем сигнале, поданном на вход устройства. Повторный управляющий сигнал повторяет отсчет импульсов без прерывания времени задержки, осуществляя его продление или повторение.

триггера 3. (МЭЦС) 8 [3] соединен своим выходом с входом R двоичного счетчика СТ2 5, а его синхровход C - с выходом двухвходовой схемы И 9, причем разрешающий вход P МЭЦС соединен с выходом Q триггера 3. Выход Вых устройства соединен с одним из используемых выходов дешифратора DC 6. Число импульсов, подсчитываемых счетчиком до используемого выхода дешифратора, и частота генератора определяют время задержки выходного сигнала при первом управляющем сигнале, поданном на вход устройства. Повторный управляющий сигнал повторяет отсчет импульсов без прерывания времени задержки, осуществляя его продление или повторение.

Использование МЭЦС для увеличения или повторения времени задержки выходного сигнала без его прерывания при повторном входном сигнале в источниках не обнаружено.

Устройство работает следующим образом.

В исходном состоянии триггер 3 находится в состоянии Q = 0;  = 1 (выключен), а запись в двоичном счетчике СТ2 5 стерта (счетчик обнулен). При поступлении на вход Вх устройства передаваемого с задержкой на выход сигнала он передается через схему ИЛИ 1 на вход D триггера Т 3, а через схему ИЛИ 7 - на его вход С и на один из входов схемы И 9 (ключ). Триггер Т 3 переключается в состояние Q = 1;

= 1 (выключен), а запись в двоичном счетчике СТ2 5 стерта (счетчик обнулен). При поступлении на вход Вх устройства передаваемого с задержкой на выход сигнала он передается через схему ИЛИ 1 на вход D триггера Т 3, а через схему ИЛИ 7 - на его вход С и на один из входов схемы И 9 (ключ). Триггер Т 3 переключается в состояние Q = 1;  = 0, включая в работу генератор Г 4. Одновременно с этим сигнал подается на разрешающий вход P МЭЦС и второй вход схемы И 9 и на синхровход С МЭЦС. МЭЦС формирует кратковременный нулевой сигнал, передает его на вход R счетчика СТ2 5, подтверждая его обнуление и переводит выходной сигнал в форму потенциальной логической единицы, позволяющей работать счетчику СТ2 5. Прямоугольные импульсы генератора Г 4 поступают на счетный вход С счетчика СТ2 5, подсчитывающего и преобразующего их десятичное число в двоичный код, который передается на дешифратор DС 6. Одновременно сигнал с выхода Q триггера Т 3 поступает также на один их входов схемы ИЛИ 7, на второй вход которой подается сигнал с входа Вх устройства. Сигнал с выхода схемы ИЛИ 7 подается на вход С триггера Т 3. Нулевой сигнал

= 0, включая в работу генератор Г 4. Одновременно с этим сигнал подается на разрешающий вход P МЭЦС и второй вход схемы И 9 и на синхровход С МЭЦС. МЭЦС формирует кратковременный нулевой сигнал, передает его на вход R счетчика СТ2 5, подтверждая его обнуление и переводит выходной сигнал в форму потенциальной логической единицы, позволяющей работать счетчику СТ2 5. Прямоугольные импульсы генератора Г 4 поступают на счетный вход С счетчика СТ2 5, подсчитывающего и преобразующего их десятичное число в двоичный код, который передается на дешифратор DС 6. Одновременно сигнал с выхода Q триггера Т 3 поступает также на один их входов схемы ИЛИ 7, на второй вход которой подается сигнал с входа Вх устройства. Сигнал с выхода схемы ИЛИ 7 подается на вход С триггера Т 3. Нулевой сигнал  = 0 триггера Т 3 поступает на один из входов схемы ИЛИ-НЕ 2, на втором входе которой также существует нулевой сигнал, снимаемый с последнего используемого выхода дешифратора DC 6. С выхода схемы ИЛИ-НЕ 2 единичный сигнал через схему ИЛИ 1 поступает на вход D триггера Т 3, удерживая его во включенном состоянии. После этого момента задерживаемый сигнал с входа устройства может быть снят. При подсчете первого заданного числа импульсов сигнал с другого соответствующего выхода дешифратора DC 6, например 2, передается на выход Вых устройства, осуществляя задержку передачи импульсного сигнала на выходную линию, соответствующую времени подсчета двух импульсов генератора. Если до этого момента на вход Вх устройства поступит следующий кратковременный сигнал, он через схему И 9 (ключ) поступает на синхровход С МЭЦС 8, который вновь формирует кратковременный нулевой выходной сигнал, подаваемый на вход R счетчика CT2 5. Счетчик обнуляется и подсчет импульсов повторяется от нуля, так как триггер Т 3 не изменял своего состояния и генератор импульсов продолжал работу.

= 0 триггера Т 3 поступает на один из входов схемы ИЛИ-НЕ 2, на втором входе которой также существует нулевой сигнал, снимаемый с последнего используемого выхода дешифратора DC 6. С выхода схемы ИЛИ-НЕ 2 единичный сигнал через схему ИЛИ 1 поступает на вход D триггера Т 3, удерживая его во включенном состоянии. После этого момента задерживаемый сигнал с входа устройства может быть снят. При подсчете первого заданного числа импульсов сигнал с другого соответствующего выхода дешифратора DC 6, например 2, передается на выход Вых устройства, осуществляя задержку передачи импульсного сигнала на выходную линию, соответствующую времени подсчета двух импульсов генератора. Если до этого момента на вход Вх устройства поступит следующий кратковременный сигнал, он через схему И 9 (ключ) поступает на синхровход С МЭЦС 8, который вновь формирует кратковременный нулевой выходной сигнал, подаваемый на вход R счетчика CT2 5. Счетчик обнуляется и подсчет импульсов повторяется от нуля, так как триггер Т 3 не изменял своего состояния и генератор импульсов продолжал работу.

При подсчете второго заданного числа импульсов сигнал с соответствующего следующего выхода дешифратора DC 6, например 6, поступает на один из входов схемы ИЛИ-НЕ 2, а с ее выхода в нулевой форме на один из входов схемы ИЛИ 1 (входной сигнал к этому времени снят) и на вход D триггера Т 3. Триггер выключается, включая генератор Г 4. Устройство прекращает работу. Длительность выходного сигнала определяется длительностью импульса генератора или временем подсчета числа импульсов между первым и последним сигналами, снятыми с дешифратора, для чего эти выходы должны быть объединены схемой ИЛИ. Время задержки выходного сигнала определяется частотой генератора и числом подсчитанных (в сумме) импульсов. Число разрядов двоичного счетчика и дешифратора принимается в зависимости от максимального времени задержки и длительности выходного сигнала.

Литература:

1. Гольденберг Л.М. Импульсные устройства. М. Радио и связь, 1981, стр. 134, рис. 5.19а.

2. Бирюкова С. А. Цифровые устройства на интегральных микросхемах. М., Радио и связь, 1987, стр. 73, рис. 103.

3. Харазов К. П. и др. Основы проектирования логических устройств, М.: МАИ, 1979, с. 52-54.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

| ТАЙМЕР | 1996 |

|

RU2100901C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2103813C1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| СЕЛЕКТОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ | 1997 |

|

RU2118044C1 |

| ФОРМИРОВАТЕЛЬ ГРУППЫ ИМПУЛЬСОВ | 1996 |

|

RU2103807C1 |

| ТАЙМЕР | 1996 |

|

RU2103808C1 |

| ЛИНИЯ ЗАДЕРЖКИ СИГНАЛА | 1998 |

|

RU2130231C1 |

| D-К-ТРИГГЕР | 1997 |

|

RU2147787C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1997 |

|

RU2147788C1 |

Линия задержки относится к вычислительной технике и может найти применение в системах управления, контроля и измерения. Техническим результатом является расширение функциональных возможностей за счет увеличения или повторения времени задержки входного сигнала. Линия задержки содержит D-триггер, генератора импульсов, счетчик, дешифратор, многоцелевой элемент цифровых структур и схемы ИЛИ, ИЛИ-НЕ и И. 1 ил.

Линия задержки, содержащая вход и выход, а также двоичный счетчик импульсов и дешифратор, отличающаяся тем, что дополнительно в линии задержки установлены однотактный D-триггер, генератор прямоугольных импульсов, многоцелевой элемент цифровых структур, две двухвходовых схемы ИЛИ и двухвходовая схема ИЛИ - НЕ, причем к входу D-триггера подсоединен выход одной двухвходовой схемы ИЛИ, один из входов которой соединен с входом линии задержки, а другой - с выходом двухвходовой схемы ИЛИ - НЕ, к одному из входов которой подсоединен последний выход дешифратора, а к другому - выход  D-триггера, выход Q которого соединен с входом генератора, соединенного своим выходом с входом C двоичного счетчика импульсов, выходы которого поразрядно соединены с соответствующими входами дешифратора, другой выход которого соединен с выходом линии задержки, причем вторая двухвходовая схема ИЛИ одним входом соединена с входом линии задержки, а другим - с Q выходом D-триггера, вход C которого соединен с выходом второй двухвходовой схемы ИЛИ, при этом вход устройства соединен также с одним из входов двухвходовой схемы И, выход которой соединен с синхровходом C многоцелевого элемента цифровых стуктур, разрешающий P вход которого соединен с выходом Q D-триггера, а выход - с входом R двоичного счетчика импульсов, причем второй вход двухвходовой схемы И соединен с выходом Q D-триггера.

D-триггера, выход Q которого соединен с входом генератора, соединенного своим выходом с входом C двоичного счетчика импульсов, выходы которого поразрядно соединены с соответствующими входами дешифратора, другой выход которого соединен с выходом линии задержки, причем вторая двухвходовая схема ИЛИ одним входом соединена с входом линии задержки, а другим - с Q выходом D-триггера, вход C которого соединен с выходом второй двухвходовой схемы ИЛИ, при этом вход устройства соединен также с одним из входов двухвходовой схемы И, выход которой соединен с синхровходом C многоцелевого элемента цифровых стуктур, разрешающий P вход которого соединен с выходом Q D-триггера, а выход - с входом R двоичного счетчика импульсов, причем второй вход двухвходовой схемы И соединен с выходом Q D-триггера.

| Бирюков С.А | |||

| Цифровые устройства на интегральных микросхемах | |||

| - М.: Радио и связь, 1987, с.73 | |||

| Гольденберг Л.М | |||

| Импульсные устройства | |||

| - М.: Радио и связь, 1981, С.134, рис.5.19а | |||

| Харазов К.И | |||

| и др | |||

| Основы проектирования логических устройств | |||

| - М.: МАИ, 1979, с.52 - 54. |

Авторы

Даты

1998-08-10—Публикация

1996-12-26—Подача