Изобретение относится к устройствам отсчета времени и может найти применение в системах управления, контроля, измерения, в вычислительных устройствах, устройствах связи различных отраслей техники,

Известен таймер, описанный, например, в [1], содержащий двоичный счетчик импульсов и дешифратор с множеством выходов, К недостаткам такого устройства следует отнести необходимость дополнительной установки внешнего генератора импульсов и ключа, позволяющего управлять работой устройства при импульсном управляющем сигнале.

Известно также устройство, описанное, например, в [2], содержащее D - триггер, инверсный выход которого соединен с выходной шиной, и четное число элементов НЕ, а также дополнительный D - триггер и элемент И с шиной управления режимом работы. К недостаткам такого устройства следует отнести необходимость дополнительной установки внешнего ключа, позволяющего управлять работой устройства при импульсном управляющем сигнале.

В качестве прототипа принято устройство, описанное в [2].

Целью предлагаемого изобретения является расширение функциональных возможностей, а именно возможность формирования сигнала заданной длительности при импульсном управляющем входном сигнале.

Постоянная цель достигается еме, что в устройство дополнительно введены двухтактный D - триггер, линия задержки на двух схемах НЕ, а также схемы И, ИЛИ и НЕ для управления триггером.

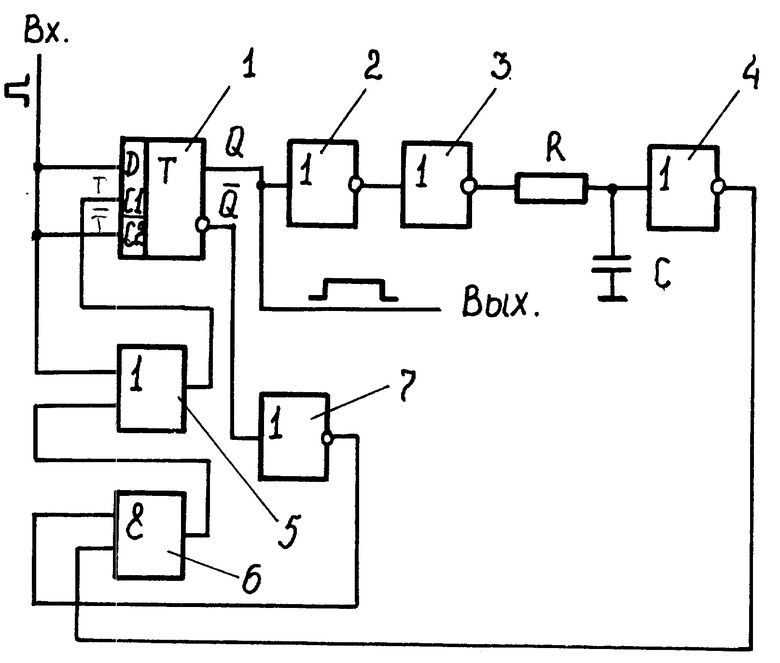

Сущность изобретения поясняется чертежом, где приведена схема таймера.

Устройство содержит вход Вх, двухтактный триггер 1, подсоединенный к выходу Вых устройства и линии задержки на двух элементах НЕ 2, 3 и RC - цепочку, а также выходной элемент НЕ 4. Кроме этого, устройство содержит схему управления триггером, состоящую из двухвходового элемента ИЛИ 5, двухвходового элемента И 6 и элемента НЕ 7.

Вход Вх устройства соединен со входами D и C2 двухтактного D - триггера 1, прямой выход которого соединен с выходом Вых устройства и входом первого элемента НЕ 2, выход которого в свою очередь соединен со входом второго элемента НЕ 3. К выходу элемента НЕ 3 подсоединен резистор R, подсоединенный к входу третьего элемента НЕ 4 и конденсатору C. Два первых элемента НЕ, резистор R и конденсатор C, подключенный второй стороной к минусу источника питания (массе), образуют линию задержки устройства. Вход Вх устройства соединен также с одним из входов элемента ИЛИ 5, ко второму входу которого подключен выход элемента И 6. Один из входов схемы И 6 соединен с выходом элемента не 4, а второй - с выходом элемента НЕ 7, вход которого соединен с прямым выходом триггера 1. Выход элемента ИЛИ 5 соединен со входом C1 триггера 1. Емкость конденсатора C и сопротивление резистора R выбираются из условия обеспечения заданной выдержки времени. Резистор R может быть переменным для настройки выдержки времени.

Использование двухтактного D - триггера и схемы управления им, реализованной на элементах НЕ, И и ИЛИ, в источниках не обнаружено.

Устройство работает следующим образом.

В исходном состоянии триггер находится в нулевом состоянии прямого и единичном инверсного выходов (выключен), а конденсатор C разряжен. На выходе Вых устройства сигнал отсутствует. При поступлении кратковременного управляющего сигнала на вход Вх устройства, он передается на входы D и C2 двухтактного D - триггера 1 и один из входов элементов ИЛИ 5, с выхода которого сигнал передается на вход C1 триггера, переключая его в единичное состояние прямого и нулевого инверсного выходов (включая). Ввиду того, что конденсатор C разряжен, на выходе элемента НЕ 4 существует сигнал логической единицы, поступающий на один из входов элемента И 6. При появлении нулевого сигнала на инверсном выходе триггера и инвертирования его элементом НЕ 7 на втором входе элемента И 6 и ее выхода также появляется сигнал логической единицы. Элемент ИЛИ 5 передает единичный сигнал на вход C1 триггера, удерживая его во включенном состоянии, после чего управляющий сигнал может быть снят. На выходе Вых устройства появляется выходной сигнал. Оновременно сигнал через элементы НЕ 2 и НЕ 3 поступает на RC-цепочку, Конденсатор C заряжается до уровня минимальной логической единицы, вызывая переключение элемента НЕ 4. Ее выходной нулевой логический сигнал передается на элемент И 6, с выхода которого он передается на элемент ИЛИ 5 и на вход C1 триггера 1. Независимо от состояния входа Вх устройства, триггер 1 переключается в нулевое состояние прямого и единичного инверсного выходов (выключается) и сигнал на выходе Вых устройства исчезает.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНИЯ ЗАДЕРЖКИ | 1997 |

|

RU2147788C1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| КОНТРОЛЬНО-РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1999 |

|

RU2156042C1 |

| ЛИНИЯ ЗАДЕРЖКИ СИГНАЛА | 1998 |

|

RU2130231C1 |

| ПЕРЕКЛЮЧАТЕЛЬ УПРАВЛЯЮЩИХ КАНАЛОВ | 1997 |

|

RU2103814C1 |

| ПЕРЕКЛЮЧАТЕЛЬ ДВУХТАКТНЫЙ | 1997 |

|

RU2118043C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2103813C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2117387C1 |

| ТАЙМЕР | 1996 |

|

RU2100901C1 |

Изобретение относится к устройствам отсчета времени и может найти применение в системах управления, контроля, измерения, в вычислительных устройств, устройствах связи различных отраслей техники. Таймер содержит двухтактный D - триггер, управляемый посредством схем И, ИЛИ, НЕ, а также линию задержки на схемах НЕ и RC- цепочке. Устройство позволяет выдерживать выходной сигнал заданной длительности при поступлении импульсного входного сигнала. 1 ил.

Таймер, содержащий D-триггер, D-вход которого соединен с входом устройства, четыре элемента НЕ, элемент И, первый вход которого соединен с выходом первого элемента НЕ, отличающийся тем, что в него введены RC-цепочка, элемент ИЛИ, выход которого соединен с C1- входом D-триггера, выполненного двухтактным, С2-вход которого соединен с входом устройства и с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента И, второй вход которого соединен с выходом второго элемента НЕ, вход которого соединен с инверсным выходом D-триггера, прямой выход которого является выходом устройства и через третий элемент НЕ соединен с входом четвертого элемента НЕ, выход которого через RC-цепочку соединен с входом первого элемента НЕ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бирюков С.А | |||

| Цифровые устройства на интегральных микросхемах | |||

| М.: Радио и связь, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| SU, авторское свидетельство, 1718368, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1998-01-27—Публикация

1996-11-27—Подача