Изобретение относится к устройствам отсчета времени и может найти применение в системах управления, контроля, измерения, вычислительных устройствах, устройствах связи и других устройствах различных отраслей техники.

Известен таймер, описанный, например в [1] содержащий компаратор напряжения, ключ, конденсатор и делитель напряжения. К недостаткам такого устройства следует отнести невозможность передачи сигнала с различной его длительностью на несколько выходных цепей.

Известен также таймер, описанный, например, в [2] содержащий счетчик импульсов и дешифратор с множеством выходов. К недостаткам такого устройства следует отнести необходимость во внешнем генераторе импульсов и ключе, позволяющем реализовывать работу при импульсном управляющем сигнале и невозможность передачи сигнала с различной его длительностью на несколько выходных цепей.

В качестве прототипа принято устройство, описанное в [2]

Целью настоящего изобретения является расширение функциональных возможностей устройства, а именно возможности формирования нескольких сигналов различной длительности с передачей их на несколько выходов при одном импульсном управляющем входном сигнале.

Цель достигается тем, что в устройство введены однотактный D-триггер, линия задержки на генераторе прямоугольных импульсов, двоичном счетчике импульсов и дешифраторе, схема управления триггером, содержащая две схемы ИЛИ и схему ИЛИ-НЕ, а также по меньшей мере два одинаковых выходных устройства (ячейки), каждая из которых содержит однотактный D-триггер, схему ИЛИ и схему ИЛИ-НЕ.

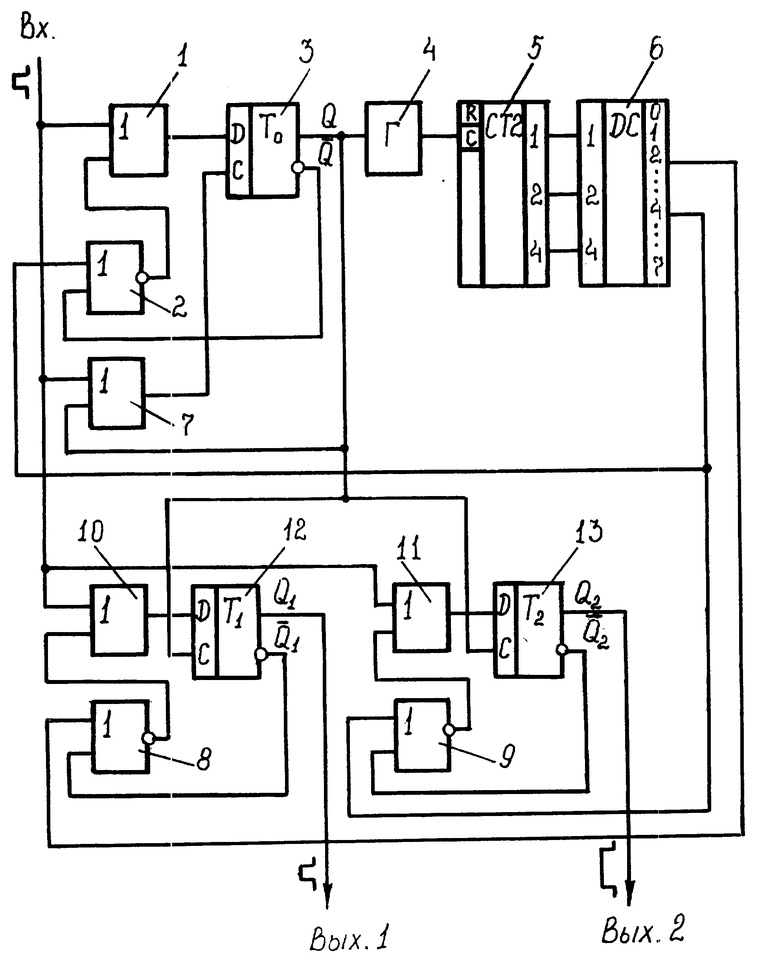

На чертеже приведена схема таймера, например, на два выхода.

Устройство содержит схему ИЛИ 1, и схему ИЛИ-НЕ 2, предназначенные для включения и выключения однотактного D-триггера 3, управляющего генератором прямоугольных импульсов Г 4; двоичного счетчика импульсов СТ2 5 и дешифратора ДС 6. Для управления выходными линиями схема содержит также по меньшей мере два одинаковых выходных устройства (ячейках), каждое из которых содержит однотактный D-триггер Т1 и Т2 12 и 13 и схему управления им, состоящую из схемы ИЛИ 10 и 11 и схемы ИЛИ-НЕ 8 и 9. Вход Вх устройства соединен с одним из входов двухвходовой схемы ИЛИ 1, второй вход которой соединен с выходом схемы ИЛИ-НЕ 2. Выход схемы ИЛИ 1 соединен с входом D-триггера Т0 3, выход Q которого соединен с генератором Г 4. Выход генератора Г 4 соединен с входом С счетчика импульсов 5, двоичные выходы которого соответственно соединены с двоичными входами дешифратора ДС 6. Выход  триггера Т0 3 устройства соединен с одним из входов двухвходовой схемы ИЛИ-НЕ 2, второй вход которой соединен с последним используемым выходом, например 4, дешифратора ДС 6. Вход Вх устройства соединен также с одним из входов двухвходовой схемы ИЛИ 7, со вторым входом которой соединен выход Q триггера Т0 3. Выход схемы ИЛИ 7 соединен с входом С триггера Т0 3. Вход устройства соединен также с одним из входов двухвходовых схем ИЛИ 10 и 11 выходных устройств ко второму входу которых подсоединены выходы двухвходовых схем ИЛИ-НЕ 8 и 9, один из входов которых соединен с выходом

триггера Т0 3 устройства соединен с одним из входов двухвходовой схемы ИЛИ-НЕ 2, второй вход которой соединен с последним используемым выходом, например 4, дешифратора ДС 6. Вход Вх устройства соединен также с одним из входов двухвходовой схемы ИЛИ 7, со вторым входом которой соединен выход Q триггера Т0 3. Выход схемы ИЛИ 7 соединен с входом С триггера Т0 3. Вход устройства соединен также с одним из входов двухвходовых схем ИЛИ 10 и 11 выходных устройств ко второму входу которых подсоединены выходы двухвходовых схем ИЛИ-НЕ 8 и 9, один из входов которых соединен с выходом  триггера Т1 и Т2 12 и 13, а второй вход с используемыми выходами, например 2 и 4 дешифратора ДС 6. Выходы дешифратора ДС 6 выбираются из условий обеспечения заданных выдержек времени.

триггера Т1 и Т2 12 и 13, а второй вход с используемыми выходами, например 2 и 4 дешифратора ДС 6. Выходы дешифратора ДС 6 выбираются из условий обеспечения заданных выдержек времени.

Использование схемы управления D-триггером на схемах ИЛИ и ИЛИ-НЕ для последовательного его включения и выключения, а также выходных схем (ячеек) для реализации нескольких выходных линий, содержащих однотактный D-триггер и аналогичные схемы управления им в источниках не обнаружено.

Устройство работает следующим образом. В исходном состоянии все триггеры находятся в состоянии Q= 0;  1 (выключения), а запись в двоичном счетчике стерта (счетчик "обнулен"). При поступлении импульсного управляющего сигнала на вход Вх устройства, он передается через схему ИЛИ 1 на вход D и через схему ИЛИ 7 на вход триггера Т0 3, переключая его в состояние Q=1;

1 (выключения), а запись в двоичном счетчике стерта (счетчик "обнулен"). При поступлении импульсного управляющего сигнала на вход Вх устройства, он передается через схему ИЛИ 1 на вход D и через схему ИЛИ 7 на вход триггера Т0 3, переключая его в состояние Q=1;  0. Триггер Т0 3 включает в работу генератор Г 4. Прямоугольные импульсы, генерируемые им, подаются на вход С двоичного счетчика СТ2 5. Его выходной двоичный код передается на дешифратор ДС 6. Одновременно с выхода Q триггера Т0 3 сигнал поступает через схему ИЛИ 7 на вход С триггера Т0 3, удерживая его в сработанном состоянии после окончания импульсного управляющего сигнала. Одновременно со входа Вх устройства через схемы ИЛИ 10 и 11 сигнал подается на входы D триггеров Т1 и Т2 12 и 13 выходных схем, а с выхода Q триггера Т0 3 на их входы С, переключая их в состояние Qi=1

0. Триггер Т0 3 включает в работу генератор Г 4. Прямоугольные импульсы, генерируемые им, подаются на вход С двоичного счетчика СТ2 5. Его выходной двоичный код передается на дешифратор ДС 6. Одновременно с выхода Q триггера Т0 3 сигнал поступает через схему ИЛИ 7 на вход С триггера Т0 3, удерживая его в сработанном состоянии после окончания импульсного управляющего сигнала. Одновременно со входа Вх устройства через схемы ИЛИ 10 и 11 сигнал подается на входы D триггеров Т1 и Т2 12 и 13 выходных схем, а с выхода Q триггера Т0 3 на их входы С, переключая их в состояние Qi=1  =0 (включая). На выходах Выхi выходных схем появляются выходные сигналы. При подсчете первого заданного числа импульсов сигнал с соответствующего выхода дешифратора ДС 6, например 2, передается через схемы ИЛИ-НЕ в нулевой форме на вход схемы ИЛИ 10. Ввиду того, что импульсный управляющий сигнал со входа Вх устройства снят, на входе D-триггера Т1 12 появляется нулевой сигнал, выключающий его. На выходе Вых1 выходной сигнал заканчивается. Длительность сигнала на выходе Вых1 определяется временем подсчета в данном примере двух импульсов генератора. При подсчете следующего заданного числа импульсов с соответствующего выхода дешифратора ДС 6, например 4, снимается сигнал, выключающий аналогичным способом выходной сигнал с выхода Вых2. Сигнал с выхода 4 дешифратора ДС 6 может быть передан через схему ИЛИ-НЕ 2 в нулевой форме на схему ИЛИ 1. Ввиду того, что импульсный управляющий сигнал с входа Вх устройства снят, на входе D-триггера Т0 3 появляется нулевой сигнал, выключающий его. Для этих же целей может быть использован и другой последующий выход дешифратора ДС 6 или сигнал от другого элемента системы управления.

=0 (включая). На выходах Выхi выходных схем появляются выходные сигналы. При подсчете первого заданного числа импульсов сигнал с соответствующего выхода дешифратора ДС 6, например 2, передается через схемы ИЛИ-НЕ в нулевой форме на вход схемы ИЛИ 10. Ввиду того, что импульсный управляющий сигнал со входа Вх устройства снят, на входе D-триггера Т1 12 появляется нулевой сигнал, выключающий его. На выходе Вых1 выходной сигнал заканчивается. Длительность сигнала на выходе Вых1 определяется временем подсчета в данном примере двух импульсов генератора. При подсчете следующего заданного числа импульсов с соответствующего выхода дешифратора ДС 6, например 4, снимается сигнал, выключающий аналогичным способом выходной сигнал с выхода Вых2. Сигнал с выхода 4 дешифратора ДС 6 может быть передан через схему ИЛИ-НЕ 2 в нулевой форме на схему ИЛИ 1. Ввиду того, что импульсный управляющий сигнал с входа Вх устройства снят, на входе D-триггера Т0 3 появляется нулевой сигнал, выключающий его. Для этих же целей может быть использован и другой последующий выход дешифратора ДС 6 или сигнал от другого элемента системы управления.

Выдержка времени выходных сигналов определяется частотой генератора и номером выхода дешифратора. Число разрядов двоичного счетчика и дешифратора принимается в зависимости от максимальной выдержки времени выходных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2100900C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2103813C1 |

| ЛИНИЯ ЗАДЕРЖКИ | 1996 |

|

RU2117387C1 |

| ТАЙМЕР | 1997 |

|

RU2130692C1 |

| ТАЙМЕР | 1996 |

|

RU2103808C1 |

| СЕЛЕКТОРНЫЙ ПЕРЕКЛЮЧАТЕЛЬ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ | 1997 |

|

RU2118044C1 |

| ЛИНИЯ ЗАДЕРЖКИ СИГНАЛА | 1998 |

|

RU2130231C1 |

| ФОРМИРОВАТЕЛЬ ГРУППЫ ИМПУЛЬСОВ | 1996 |

|

RU2103807C1 |

| КОНТРОЛЬНО-РАСПРЕДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1999 |

|

RU2156042C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ РЕВЕРСИВНЫЙ ДВОИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 1997 |

|

RU2115227C1 |

Таймер относится к устройствам отсчета времени действия управляющих сигналов и может найти применение в системах управления, контроля, измерения, вычислительных устройствах, устройствах связи и других устройствах различных отраслей техники. Таймер содержит однотактный D-триггер, управляемый посредством двух схем ИЛИ и схемы ИЛИ-НЕ, а также по меньшей мере двух одинаковых выходных ячеек, каждая из которых содержит однотактный D-триггер, управляемый схемами ИЛИ и ИЛИ-НЕ. Управление выходными ячейками осуществляется от дешифратора, двоичного счетчика и генератора импульсов. Таймер позволяет выдерживать заданную различную длительность по меньшей мере двух выходных сигналов. 1 ил.

Таймер, содержащий вход и по меньшей мере два выхода, двоичный счетчик импульсов, выходы которого поразрядно соединены с входами дешифратора, отличающийся тем, что в устройство дополнительно установлены генератор импульсов, однотактный D-триггер, две двухвходовые схемы ИЛИ, двухвходовая схема ИЛИ-НЕ, а также по меньшей мере две одинаковые выходные ячейки, состоящие из однотактного D-триггера, двухвходовой схемы ИЛИ и двухвходовой схемы ИЛИ-НЕ, при этом D вход однотактного D-триггера соединен с выходом двухвходовой схемы ИЛИ, один из входов которой соединен с входом устройства, а другой с выходом двухвходовой схемы ИЛИ-НЕ, один из входов которой соединен с соответствующим выходом дешифратора, а другой с выходом  однотактного D-триггера, выход которого соединен с входом генератора импульсов, соединенного с входом С двоичного счетчика импульсов, причем вход устройства также соединен с одним из входов двухвходовой схемы ИЛИ, второй вход которой соединен с выходом Q однотактного D-триггера, а ее выход соединен с входом С того же однотактного D-триггера, выходы дешифратора соединены с одним из входов двухвходовой схемы ИЛИ-НЕ выходных ячеек, с вторым входом которых соединены выходы

однотактного D-триггера, выход которого соединен с входом генератора импульсов, соединенного с входом С двоичного счетчика импульсов, причем вход устройства также соединен с одним из входов двухвходовой схемы ИЛИ, второй вход которой соединен с выходом Q однотактного D-триггера, а ее выход соединен с входом С того же однотактного D-триггера, выходы дешифратора соединены с одним из входов двухвходовой схемы ИЛИ-НЕ выходных ячеек, с вторым входом которых соединены выходы  однотактных D-триггеров соответствующих выходных ячеек, причем выходы двухвходовых схем ИЛИ-НЕ выходных ячеек соединены с одним из входов двухвходовой схемы ИЛИ соответствующих выходных ячеек, второй вход которых соединен с входом устройства, а их выход соединен с входом D однотактного D-триггера соответствующей выходной ячейки, при этом выход Q однотактного D-триггера соединен также с входами С однотактных D-триггеров выходных ячеек, выходы Q которых соединены с соответствующими выходами устройства.

однотактных D-триггеров соответствующих выходных ячеек, причем выходы двухвходовых схем ИЛИ-НЕ выходных ячеек соединены с одним из входов двухвходовой схемы ИЛИ соответствующих выходных ячеек, второй вход которых соединен с входом устройства, а их выход соединен с входом D однотактного D-триггера соответствующей выходной ячейки, при этом выход Q однотактного D-триггера соединен также с входами С однотактных D-триггеров выходных ячеек, выходы Q которых соединены с соответствующими выходами устройства.

| Гольденберг Л.М Импульсные устройства | |||

| - М.: Радио и связь, 1981, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Бирюков С.А | |||

| Цифровые устройства на интегральных микросхемах | |||

| -М.: Радио и связь, 1987, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

Авторы

Даты

1997-12-27—Публикация

1996-12-10—Подача