Изобретение относится к спутниковым радионавигационным системам и может быть использовано для определения местоположения и параметров вектора скорости подвижных объектов (наземных: сухопутных, морских, воздушных, низкоорбитальных космических) (И.Н. Мищенко, А.И.Волынкин, П.С.Волосов и др. Глобальная навигационная система NAVSTAR. -Зарубежная радиоэлектроника, 1980, N 8, с. 52-83).

Каждый подвижный объект системы может в любом месте определить или уточнить в любой момент времени параметры своего движения (три координаты местоположения и три составляющих вектора скорости). В аппаратуре пользователя должны быть представлены радионавигационные сигналы от Nc ≥4 радиовидимых навигационных космических аппаратов. Эти сигналы используются для определения трех разностей дальностей и трех разностей радиальных скоростей объекта относительно спутников. С помощью этих сигналов пользователю также передается (со скоростью 50 бит в секунду) информация о параметрах орбит спутников и другие данные, необходимые для определения его местоположения с высокой точностью. В таких системах имеет место пассивная автономная навигация.

Известно устройство (патент США N 5459473), реализующее приемник, в котором преобразование входного сигнала в сигнал более низкой частоты является комплексным. Затем сигнал подвергается жесткому ограничению и дальнейшая обработка производится в частотной области.

Недостатками такого приемника являются высокие требования к мощности центрального процессора из-за высокой частоты дискретизации, большое время поиска сигнала по задержке, а также постоянное функционирование блока, реализующего быстрое преобразование Фурье (БПФ). Эти обстоятельства приводят к сложности реализации (большому числу эквивалентных вентилей), а также к большому энергопотреблению.

Наиболее близким, по структуре схемы приемника является приемник глобальной системы позиционирования (патент США N 4578678), содержащий N ≥4 каналов обработки сигналов от Nc спутников. Входные сигналы после усиления и преобразования частот, аналогово-цифрового преобразования поступают в квадратурном виде на объединенные входы N каналов преобразования сигналов и генераторов дальномерных псевдослучайных последовательностей (ПС), причем на второй вход квадратурного преобразования частоты поступает колебание от стабильного опорного генератора, и блоки формирования частоты гетеродина, а на вторые входы блоков ПС поступают колебания от стабильного генератора через блок временной синхронизации. Выходы каждого из N каналов подключены ко входам блока управления. От ПС передаются оценки задержек и частот, а по обратному каналу от блока управления поступают предсказанные задержки и частоты, а также осуществляется управления блоком ПС. Блок управления также обеспечивает поступление информации к пользователю и получение команд от него. По прямым каналам пользователь получает информацию о координатах подвижных объектов и о параметрах вектора скорости, а по обратным каналам пользователь может передавать ожидаемые априорно известные значения частот и задержек, а также может передать сигналы управления.

Однако это устройство, выбранное в качестве прототипа, также не обеспечивает снижения массогабаритов приемника, его стоимости и энергопотребления. Это объясняется расщеплением сигнала во входном блоке квадратурного смесителя, а также применения АЦП, что требует большой памяти блока БПФ.

Целью предлагаемого изобретения является снижение объема аппаратуры приемника, его стоимости и энергопотребления, при сохранении его функциональных и рабочих характеристик по сравнению с устройством-прототипом.

Указанная цель достигается тем, что по сравнению с известным устройством, содержащим N корреляционных каналов обработки, в которых осуществляется генерирование дальномерных псевдослучайных последовательностей и преобразование сигналов, производится получение оценок частот и задержек, а также вычисляются корреляционные интегралы квадратурных составляющих I и Q; реализуется аппаратный режим поиска и слежения, осуществляется расщепление сигнала на квадратурные составляющие на выходе канала, что позволяет за счет снижения числа эквивалентных вентилей выполнить схему приемника на единственной микросхеме по технологии программируемых логических матриц.

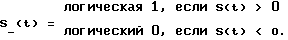

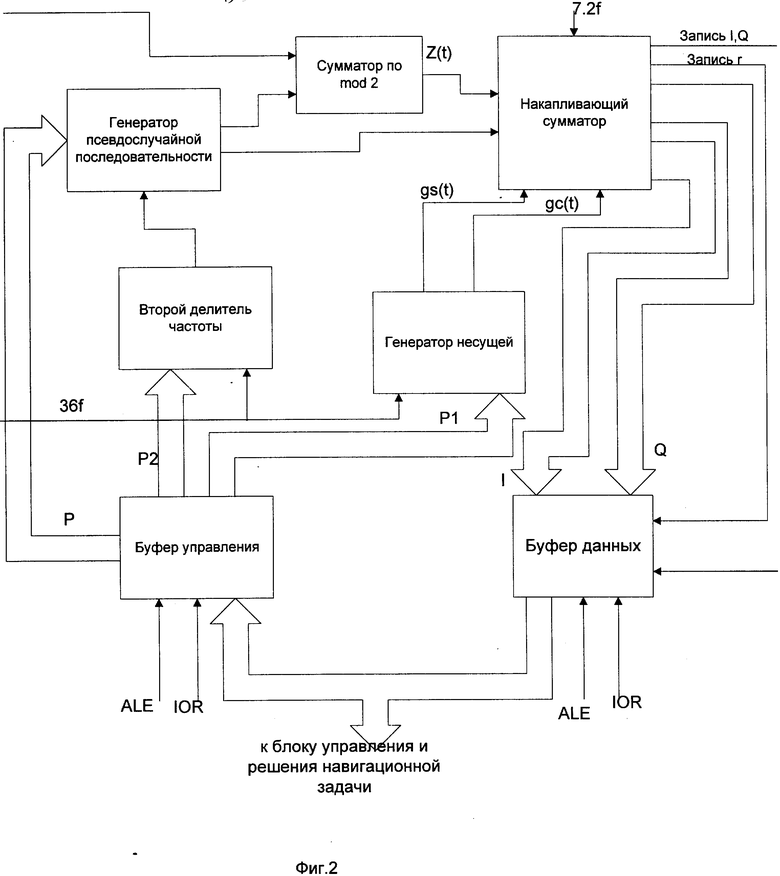

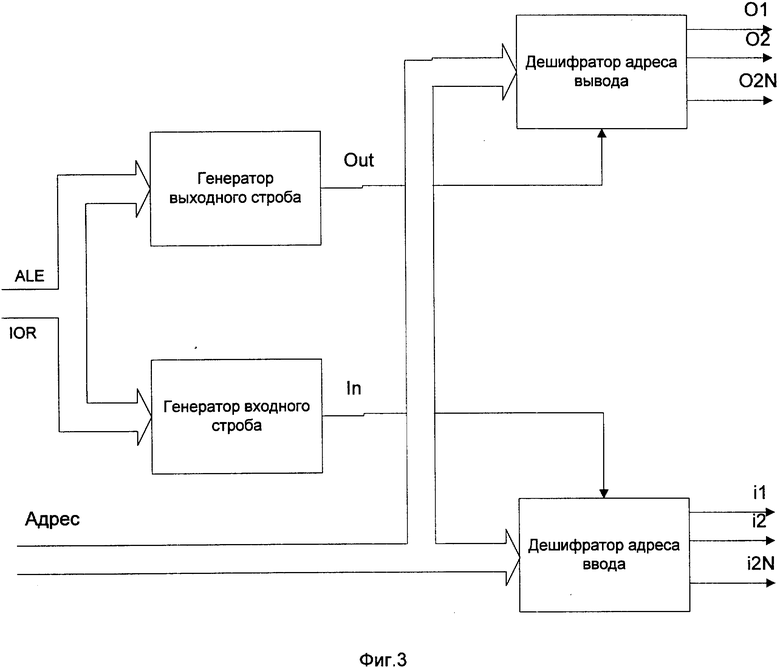

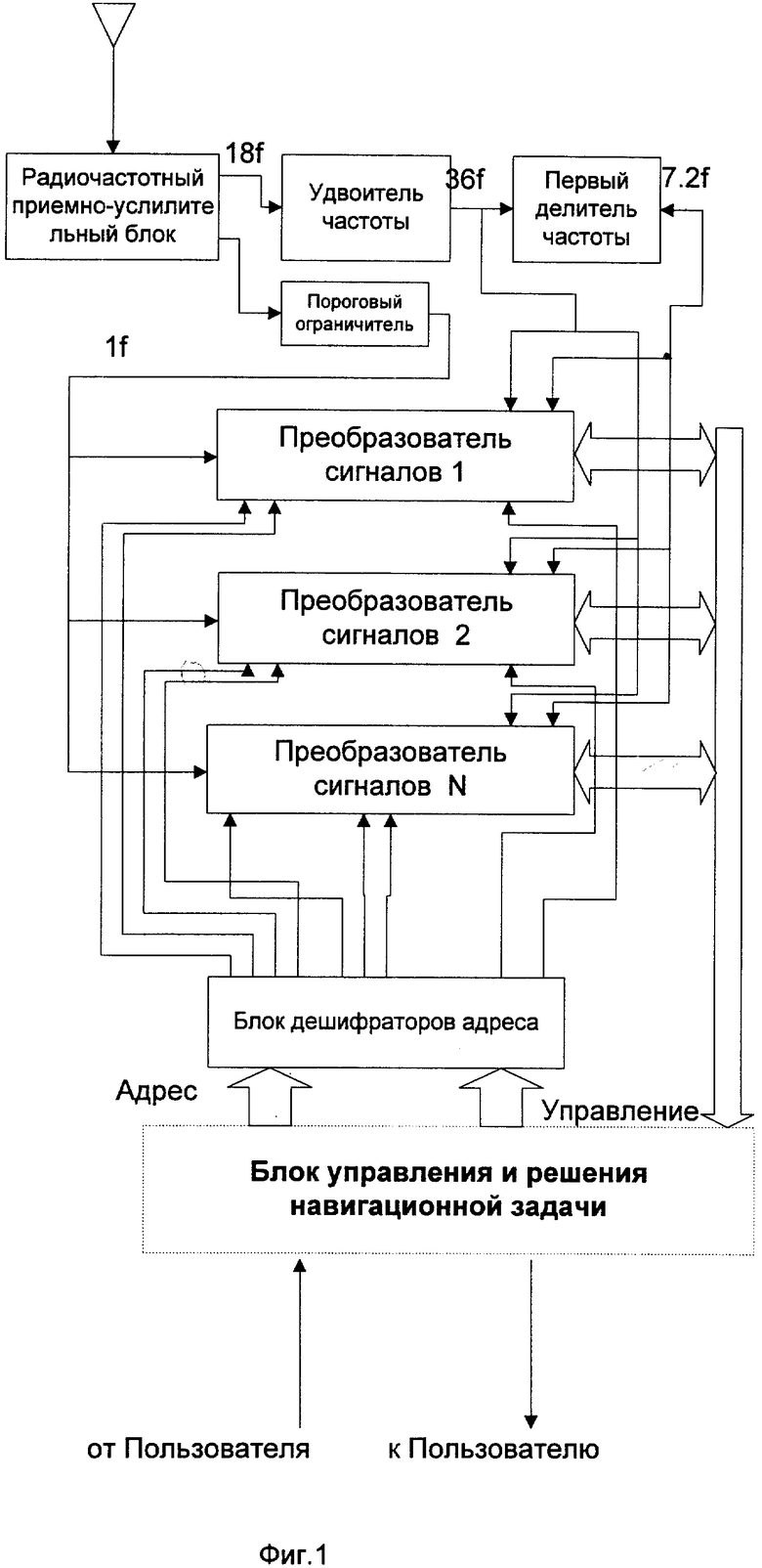

На фиг. 1 приведена укрупненная структурная схема предлагаемого приемника; на фиг. 2 - структурная схема одного корреляционного канала обработки устройства; на фиг. 3 - структурная схема сегмента интерфейса; на фиг. 4 - схема генератора псевдослучайной последовательности (ПСП); на фиг. 5 - схема генератора несущей; на фиг. 6 - функциональная схема аккумулятора (накапливающего сумматора - HC); на фиг. 7 - функциональная схема буфера управления.

Обычным приемникам следящего типа свойственны недостатки, связанные со срывами слежения при движении объекта с большими перегрузками, а также при наличии переотраженных сигналов. Проблемы слежения за высокодинамическими объектами и последствия скачков фазы принимаемого сигнала, присущие приемникам следящего типа, преодолеваются за счет применения устройство прямого оценивания (без обратной связи) параметров сигналов. Однако для реализации подобных устройств требуется гораздо больший объем аппаратуры, либо очень высокое быстродействие при программной реализации на микропроцессорах. В предлагаемом приемнике применен подход, при котором основная нагрузка падает на аппаратно-реализованные устройства оценивания следящего типа, а устройства прямого оценивания реализуются программно и включаются только в редких случаях для формирования начальных значений (целеуказаний) в следящие измерители и для восстановления слежения при его срывах. Благодаря этому подходу предлагаемый приемник сочетает преимущества обоих типов измерителей, избегая вместе с тем дополнительных затрат аппаратуры и чрезмерных нагрузок на вычислитель.

Преимуществом настоящего изобретения является то, что преобразование на частоту 1,023 МГц, пороговое ограничение, демодуляция и дискретизация по времени являются действительными, а не комплексными, и поэтому эти операции требуют вдвое меньшего объема аппаратуры.

Еще одним преимуществом настоящего изобретения является отсутствие фильтра спектральных наложений, благодаря чему снижается объем аппаратуры цифровой обработки сигналов.

Еще одним преимуществом настоящего изобретения является то, что быстрое преобразование Фурье (БПФ) выполняется только тогда, когда это необходимо для инициализации фазовой автоподстройки частоты (ФАПЧ), обнаружения границы бита данных и восстановления слежения ФАПЧ при срыве. Основную часть времени модуль БПФ не включен, благодаря чему уменьшается нагрузка на блок управления.

Приемник работает следующим образом. Сигнал с несущей частотой 1575,42 МГц, принятый антенной, в радиочастотном приемно-усилительном блоке (РПУБ) переносится на более низкую частоту 1,023 МГц. Этот сигнал пропускается через пороговый ограничитель и подается на вход N корреляционных каналов обработки по цепи, обозначенной 1f. РПУБ содержит задающий генератор с частотой 18f, и его сигнал также подается на N корреляционных каналов обработки через удвоитель частоты по цепи, обозначенной 36f.

Сигнал на входе 1fN корреляционных каналов обработки представляет собой аддитивную смесь спутниковых сигналов и шума. Выделение спутниковых сигналов из шума производится в N корреляционных каналах обработки и блоке управления, основными функциями которых являются:

поиск сигналов отдельных спутников в частотно-временной области;

вынесение решений об обнаружении этих сигналов;

слежение за сигналами спутников в частотной и временной областях;

оценка псевдодальностей и псевдо-доплеровских частот;

решение навигационной задачи, т.е. вычисление координат и вектора скорости приемника.

Принятый сигнал S(t) преобразуется в логические уровни:

Логический сигнал S-(t) умножается (суммируется по модулю 2) на код ПСП G(t-τ) , и полученный в результате сигнал Z(t) умножается (суммируется по модулю 2) на синфазную и квадратурную компоненты несущего колебания, которые формируются генератором несущей частоты. "Произведения" z(t) ⊕ gs(t) и z(t) ⊕ gc(t) интегрируются в HC на временном интервале 1 мс, и полученные в результате корреляционные интегралы I и Q обрабатываются в режиме поиска и в режиме слежения различным образом.

В режиме поиска значения корреляционных интегралов накапливаются в памяти центрального процессора, и когда будут получены 20 пар (I,Q), выполняется быстрое преобразование Фурье (БПФ). Частотно-временная ячейка (f,τ) , в которой сигнал превышает порог, фиксируется пороговым детекторов. Порядок осмотра ячеек задается модулем частотно-временного сканирования.

В режиме слежения значения корреляционных интегралов I, Q передаются в реализуемые в блоке управления модуль ФАПЧ и модуль слежения за задержкой. Модуль ФАПЧ состоит из фазового дискриминатора, фильтра интегратора и управляемого генератора. Управляемый генератор формирует сигнал несущей с частотой f и фазой ϕ0. . Петля слежения за задержкой реализуется с помощью модуля сканирования по задержке, управляющего генератором ПСП, и модуля оценки задержки. При формировании сигнала управления задержкой генерируемой ПСП P□ используются значения полной фазы ϕ0 из петли слежения за несущей (ФАПЧ).

Выходом системы обработки сигнала являются измерения псевдодальностей τ и псевдодоплеровской частоты f, а также последовательность битов навигационного сообщения D(t).

Распределение функций между аппаратурой цифровой обработки сигналов и блока управления таково: в аппаратуре реализуется генератор ПСП, генератор несущей, сумматоры по модулю 2 и НС. Совокупность таких аппаратных блоков образует один корреляционный канал обработки. Одна микросхема программируемой логической матрицы (FPGA) типа Xilinx 4013 может содержать до 8 таких N корреляционных каналов обработки.

Все остальные блоки обработки реализуются программно в блоке управления: память на 20 выборок по каждому каналу, БПФ, частотно-временной сканер, пороговый детектор, фазовый дискриминатор, фильтр, интегратор, генератор ФАПЧ, сканер по задержке и модуль оценивания задержки.

Функциональная схема устройства, пригодного для реализации как на FPGA, так и в заказной интегральной схеме, представлена на фиг. 1. Устройство содержит N независимых каналов для поиска и слежения за N сигналами спутников одновременно.

Двоично-квантованный сигнал 1f с выхода порогового ограничителя и преобразования в логические уровни подается на входы всех каналов. Логическая 1 на входах каналов соответствует положительному значению аналогового сигнала на выходе РПУБ, а логический 0 - отрицательному значению.

Каждый корреляционный канал обработки синхронизируется двумя синхросигналами 36f и 7,2f. Первый из них получается из сигнала 18f с помощью удвоителя частоты, а второй - формируется из сигнала 36f путем деления частоты на 5.

Делитель 5:1 предназначен для генерирования последовательности 7,2f, используемой в HC N корреляционных каналов обработки. Он реализован по схеме счетчика Джонсона.

Основной функцией корреляционного канала обработки, является вычисление так называемых "корреляционных интегралов" I и Q, соответствующих корреляции входного сигнала с двумя копиями сигнала спутника, сдвинутыми по фазе на 90o на (f) 1,023 МГц. Цикл накопления в YC равен одному периоду ПСП, так что накопленные значения корреляционных интегралов I (синфазный канал) и Q (квадратурный канал) записываются в буфер данных в момент, когда сдвиговый регистр генератора ПСП переходит в состояние "все единицы". Кроме того, сразу же после защелкивания выходных данных в буфере данных в слове I устанавливается в 1 специальный разряд Г, служащий индикатором того, что данные I, Q готовы для передачи в блок управления.

Формирование копии сигнала в каждом канале управляется данными, поступающими от блока управления.

P - 10-разрядный код, определяющий кодовую последовательность, соответствующую данному спутнику в системе;

P2 -6-разрядный код, определяющий число тактов основной частоты синхронизации 36f, на которое сдвигается следующий период ПСП по отношению к предыдущему периоду;

P1 = 12-разрядный код частоты генератора несущей.

Управляющие данные поступают в буфер управления от блока управления с упреждением по времени, и выдаются из буфера управления в генератор копии сигнала по тому же сигналу Готово, который устанавливает в 1 разряд Г в буфере данных.

Обмен данными с центральным процессором осуществляется по системной шине через сегмент интерфейса под управлением блока управления.

Функциональная схема корреляционного канала обработки представлена на фиг. 2. Входной бинарно-квантованный сигнал "умножается" на ПСП, формируемую генератором ПСП. Перемножение бинарно-квантованных сигналов эквивалентно суммированию по модулю 2 (обозначенное ⊕ ) соответствующих логических последовательностей. Настройка на индивидуальный код ПСП спутника осуществляется посредством управляющего P-кода. P-код представляет собой 10-разрядное слово, содержащее 1 в двух разрядах соответственно выбору фазы кода для данного спутника, и 0 в остальных разрядах. Например, для спутника N 1 выбор фазы кода соответствует 2 и 6, и P- код равен 0100010000.

Генератор ПСП синхронизируется частотой 1,023 МГц, которая формируется из основной частоты синхронизации 36f путем ее деления на 36. Делитель 36:1 представляет собой двоичный счетчик, считающий до 36. Он состоит из 6 разрядов (каскадов). Если в начале текущего цикла в него записывается некоторое число P2(P2<36), то в этом цикле счетчик считает до P2, а не до 36. Аналогично, если 36 < P2 < 64 в каком-то цикле, то счетчик в этом цикле считает до 64-P2. Таким образом, вся ПСП сдвигается по оси времени на P2 или (64-P2) периодов основной частоты синхронизации за счет удлинения или укорочения длительности первого разряда следующего периода ПСП.

Сигнал Z(t) является результатом перемножения входного сигнала 1f и сгенерированной ПСП. Когда сгенерированная ПСП оказывается выравненной по задержке с входным сигналом, Z(t) представляет собой меандр с частотой 1f +FD (FD - доплеровская частота). Фаза сигнала Z(t) сдвинута на неизвестное значение. Шумы и помехи искажают форму сигнала Z(t), и для устранения этих искажений синфазная и квадратурная составляющая с выхода сумматора по модулю 2 накапливаются в НС.

Для этой цели в генераторе несущей частоты используется основная частота синхронизации 36f, из которой формируются два сигнала gs(t) и gc(t) в форме меандров, сдвинутых по фазе на 90o. Частота сигналов gs(t) и gc(t) управляется кодами P1, поступающими от блока управления, и она может быть установлена в интервале от 1f - 5 кГц до 1f + 5 кГц, где 1f = 1,023 МГц.

В соответствующих НС сигнал Z(t) перемножается (суммируется по модулю 2) с сигналами gs(t) и sc(t). Затем в НС производится подсчет числа импульсов последовательности 7,2f, которые соответствуют нулевым значениям произведений z(t) ⊕ gs(t) и z(t) ⊕ gc(t). Другими словами, в i- аккумуляторе подсчитывается число импульсов 7,2f, когда z(t) ⊕ gs(t) равно логической 1, и то же делается в Q-аккумуляторе, когда z(t) ⊕ gc(t) равно логической 1.

В конце каждой эпохи, т.е. когда текущий период ПСП заканчивается, накопленные значения I и Q передаются в выходной буфер канала, или буфер данных. После этого HC сбрасывается в 0, и накопление возобновляется, но с новыми значениями P2, P1 и P. Сигнал конца эпохи, или сигнал Готово, вырабатывается генератором ПСП (так называемый сигнал состояния "все единицы").

Блок-схема сегмента интерфейса представлена на фиг.3. Сегмент интерфейса предназначен для формирования сигналов (01...02N) для подключения выходных буферов данных к системной шине (данные) БУРНЗ, и для формирования сигналов (i1...i2N) для записи управляющих данных (P, P1, P2) из системной шины центрального процессора (данные) в буферы управления. При появлении сигналов разрешения чтения адреса ALE и разрешения чтения данных IOR генератор строба вывода формирует сигнал Out, который стробирует выход декодера адреса вывода. При появлении сигналов разрешения чтения адреса ALE и разрешения записи данных IOW генератор строба вывода формирует сигнал In, который стробирует выход декодера адреса ввода.

Дешифратор адреса вывода и дешифратор адреса ввода реализованы одинаковым способом. Они представляют собой двухступенчатые декодеры. Первая ступень декодирует два старших разряда из 9 адресных разрядов, а вторая ступень - остальные 7 разрядов. Первая ступень стробируется сигналом Out или In. Схемы генераторов строба ввода и строба вывода одинаковы. Они представляют собой схему выбора первого сигнала, появляющегося на линии IOR или IOW после перехода сигнала ALE в состояние разрешения чтения адреса.

Генератор ПСП (фиг. 4) состоит из генератора G1, генератора G2, 10-входового вентиля "И" (группа элементов "И") и сумматора по модулю 2. Генератор G1 представляет собой 10-каскадный регистр сдвига с обратной связью, соответствующей сумме по модулю 2 выходов 3-го и 10-го каскадов. Начальное состояние соответствует единицам во всех каскадах (шестнадцатеричное 3FF). Период генерируемого кода равен 1023 циклам частоты синхронизации f0, которая поступает от делителя 36:1. В последнем цикле эпохи, когда состояние генератора G1 равно 1FF ( шестнадцатеричное), вырабатывается сигнал Готово. Схема генератора G2 аналогична G1, но обратная связь соответствует сумме по модулю 2 выходов 2-го, 3-го, 6-го, 8-го и 10-го каскадов. ПСП представляет собой сумму по модулю 2 выхода генератора G1 и выходов некоторых двух каскадов генератора кода G2. Выбор каскадов, суммируемых по модулю 2, выполняется совокупностью из 10 вентилей "И", которые управляются P- кодом, поступающим от блока управления.

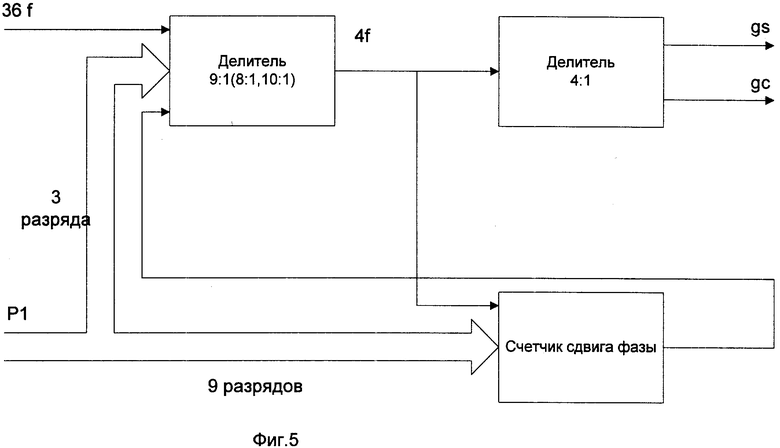

Функциональная схема генератора несущей частоты представлена на фиг. 5. Генерация сигналов выполняется с помощью двух последовательно соединенных делителей: делитель 9:1 (8:1, 10: 1) и делитель 4:1. Первый делитель делит частоту последовательности 36f на 9, если сигнал управления фазой отсутствует. Получающаяся последовательность частоты 4f подается на вход делителя 4: 1, который генерирует сигналы gs и gc, сдвинутые по фазе на 90o. Последовательность 4f подается также на вход счетчика сдвига фазы, который считает до значения, определяемого 9-ю младшими разрядами 12-разрядного кода P1. По достижении заданного значения счетчик сдвига фазы вырабатывает сигнал сдвига фазы, поступающий на управляющий вход делителя 9:1 (8:1, 10:1). Таким образом, каждый раз, когда появляется сигнал сдвига фазы, этот делитель устанавливается в режим деления 8:1 или 10:1 в зависимости от содержимого 3-х старших разрядов кода P1. Поэтому фаза сигналов периодически увеличивается (или уменьшается) с периодом, определяемым 9-ю младшими разрядами кода P1.

Делитель 9:1 (8:1, 10:1) выполнен в виде 5-каскадного счетчика Джонсона с коммутатором в цепи обратной связи. Коммутатор управляется тремя старшими разрядами кода P1. Когда содержимое старших разрядов кода P1 равно 001, обратная связь осуществляется с 4-го каскада, и коэффициент деления равен 8. Когда содержимое старших разрядов кода P1 равно 010, обратная связь осуществляется с 5-го каскада, и коэффициент деления равен 10. Когда содержимое старших разрядов кода P1 равно 100, обратная связь осуществляется с 4-го и 5-го каскадов, и коэффициент деления равен 9.

Делитель 4:1 реализуется в виде 2-каскадного счетчика Джонсона. Выходной сигнал gs снимается с первого каскада счетчика, а выходной сигнал gc снимается со второго каскада.

Счетчик сдвига фазы представляет собой 9-каскадный двоичный счетчик с последовательным переносом и параллельной загрузкой начального значения. По достижении конечного значения генерируется сигнал сдвига фазы, и загружается новое начальное значение, задаваемое 9-ю младшими разрядами кода P1.

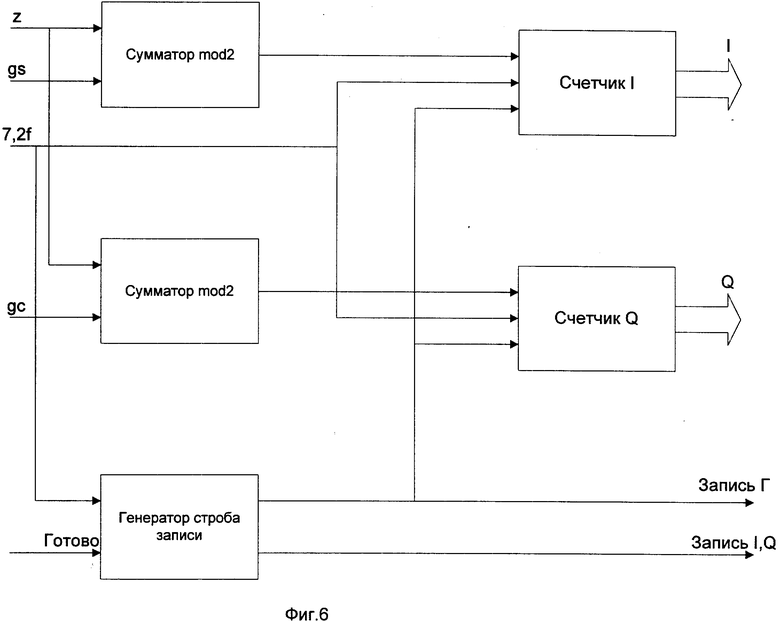

Функциональная схема НС представлена на фиг. 6. Он предназначен для накопления корреляционных интегралов I и Q для синфазной (gs) и квадратурной (gc) компонент на временном интервале, равном одному периоду ПСП (1 мс). Выходные коды I и Q передаются в выходной буфер данных канала.

Чтобы получить значение корреляционного интеграла I, сигналы Z и g перемножаются и полученное произведение Z ⊕ gs подается на вход 3-входового вентиля "И". На второй вход этого вентиля подается последовательность 7,2f. Число "импульсов" 7,2f, прошедших через вентиль за время одного периода ПСП, примерно пропорционально корреляционному интегралу I. 13-разрядный счетчик I подсчитывает эти импульсы. Аналогично работает счетчик Q, но с входным сигналом Z ⊕ gc.

Во время последнего разряда ПСП 3-входной вентиль "И" бланкируется сигналом Готово, вырабатываемым генератором ПСП, накопление заканчивается (т.е. счетчик I останавливается), генератор строба записи вырабатывает сигнал Запись I, Q и выход счетчика I выдается в буфер данных. Те же действия выполняются для корреляционного интеграла Q. После переписи выходных данных счетчиков I и Q в буфер данных генератор строба записи вырабатывает сигнал Запись Г, который записывает флаг Г в буфер данных и сбрасывает в 0 счетчики I и Q.

Счетчики I и Q устроены одинаковым образом. Они представляют собой двоичные счетчики с последовательным переносом. Каждый каскад реализован в виде D- триггера с обратной связью (схема Джонсона).

Генератор строба записи содержит двухкаскадный регистр сдвига для задержки сигнала Готово и два 3-входовых вентиля "НЕ-И" для выбора первого и второго импульса 7,2f в стробе сигнала Готово. Первый импульс выдается в качестве сигнала Запись I, Q, а второй - в качестве сигнала Запись Г.

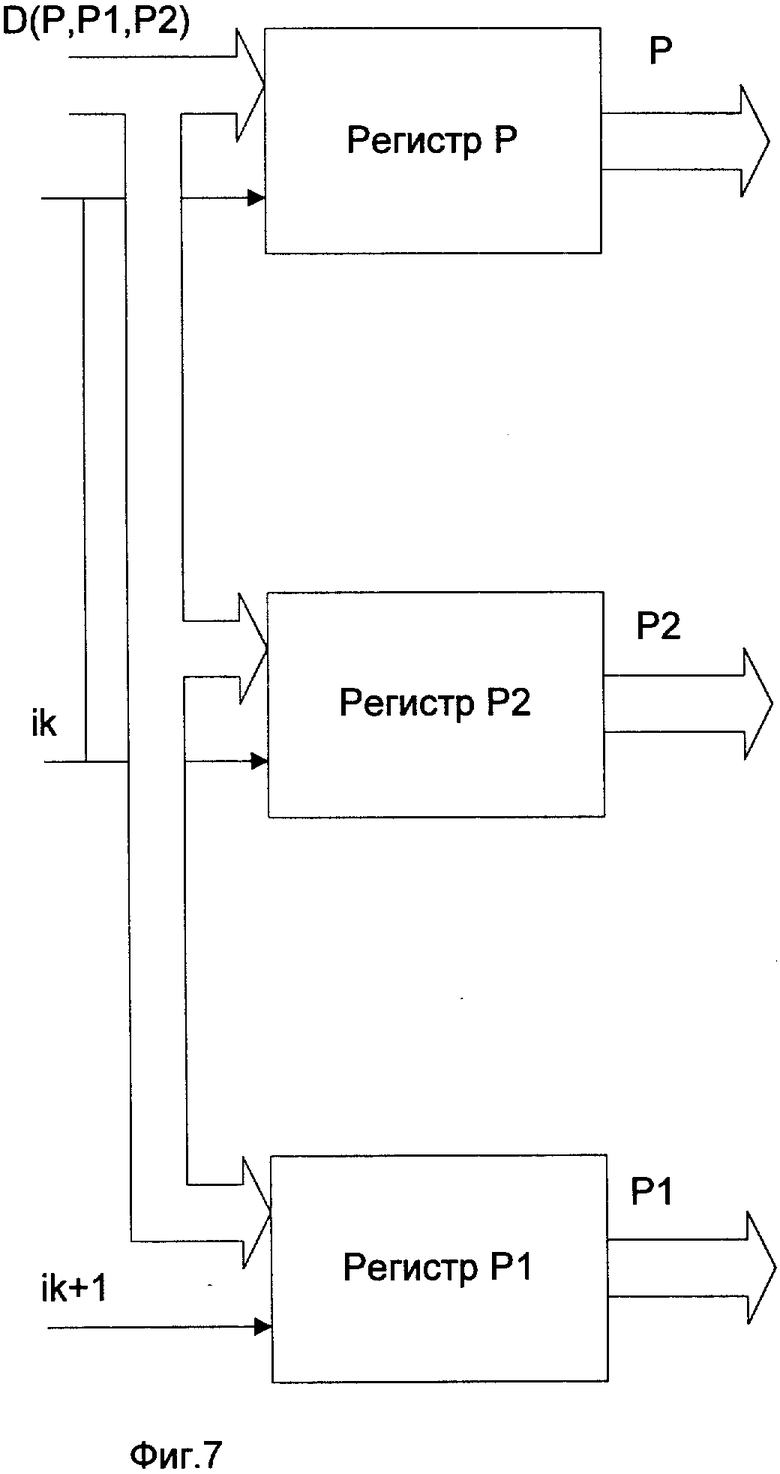

Один канал буфера управления, схема которого приведена на фиг. 7 предназначен для приема управляющих данных D(P,P1,P2) от БУРНЗ и хранения этих данных в течение необходимого времени. Он состоит из 10-разрядного регистра P, 6-разрядного регистра P2 и 12-разрядного регистра P1.

Сигнал i1 (i3, i5,...i2N-1) поступает от сегмента интерфейса, по этому сигналу записываются данные в регистр P и регистр P2. Сигнал о2 (о4, о6... о2N) сбрасывает регистр P2 в ноль в момент, когда выход регистра Q выдается в системную шину.

Сигнал i2(i4,i6,...i2B) также поступает из сегмента интерфейса. По этому сигналу производится запись данных в регистр P1.

Буфер данных каждого канала предназначен для временного хранения накопленных значений I и Q и флага готовности данных Г. Буфер данных состоит из 13-разрядного регистра I, одноразрядного регистра Г и 13-разрядного регистра Q.

Данные в регистры I и Q поступают от аккумулятора. Сигнал Запись I, Q также поступает от HC. Сигнал Готово, поступающий от генератора ПСП, записывается в регистр Г с помощью сигнала Запись Г, поступающего от HC с задержкой относительно сигнала Запись I, Q. Сигнал о1 (о3, о5,...о2N-1),, поступающий от сегмента интерфейса, подключает регистры I и Г к системной шине. Если сигнал о1(о3, о5, ...о2N-1) неактивен, то регистры I и Г находятся в третьем состоянии, т.е. отключены от системной шины. После выдачи выходных данных регистров I и Г в системную шину сигал о2 (о4, о6 ...о2N) сбрасывает регистр Г в ноль.

Сигнал о2(о4,о6 ...о2N), поступающий от сегмента интерфейса, подключает регистр Q к системной шине. Если сигнал о2 (о4, о6,...о2N) неактивен, то регистр Q находится в третьем состоянии, т.е. отключен от системной шины.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2001 |

|

RU2205417C2 |

| Единый генератор псевдослучайных последовательностей (ПСП) приемника сигналов Глобальных Навигационных Спутниковых Систем (ГНСС) | 2022 |

|

RU2789320C1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1999 |

|

RU2140090C1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ УЗКОПОЛОСНЫХ ПОМЕХ В СПУТНИКОВОМ НАВИГАЦИОННОМ ПРИЕМНИКЕ | 2012 |

|

RU2513028C2 |

| МНОГОКАНАЛЬНЫЙ ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1994 |

|

RU2079148C1 |

| ПРИЕМНИК СПУТНИКОВЫХ НАВИГАЦИОННЫХ СИГНАЛОВ С БЛОКОМ БЫСТРОГО И ВЫСОКОЧУВСТВИТЕЛЬНОГО ПОИСКА | 2010 |

|

RU2444027C2 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ НАВИГАЦИИ | 1995 |

|

RU2090902C1 |

| ИНТЕГРИРОВАННЫЙ ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2146378C1 |

Изобретение относится к технике радионавигационных систем и может быть использовано для приема сигналов в системах глобальной спутниковой навигации. В приемнике осуществляется жесткое ограничение сигнала на промежуточной частоте 1,023 МГц с дальнейшим преобразованием его в логические уровни. Полученный логический сигнал суммируется по модулю с дальномерной псевдослучайной последовательностью спутника, сигнал которого должен быть обнаружен или должен сопровождаться, после чего осуществляется суммирование по модулю два полученного сигнала с синфазной и квадратурной компонентами генератора несущей, которые представлены в виде бинарных составляющих с доплеровской частотой и фазой, соответствующими спутнику, сигналы которого подлежат обнаружению или слежению. В накопителях I и Q осуществляется интегрирование полученных сигналов за время одного периода псевдослучайной последовательности. На базе быстрого преобразования Фурье выносятся решения об обнаружении сигнала и инициализации фазовой автоподстройки частоты. Псевдодальности и псевдодоплеровские частоты оцениваются с помощью петли слежения за задержкой и петли слежения за несущей соответственно. С помощью полученных оценок вычисляются искомые координаты и векторы скорости. Технический результат, достигаемый при реализации данного изобретения, состоит в снижении объема аппаратуры приемника и энергопотребления. 7 ил.

Приемник спутниковой радионавигационной системы, содержащий антенну, подключенную к входу радиочастотного приемно-усилительного блока, а также N корреляционных каналов обработки, сигнальные входы которых соединены между собой, причем в состав каждого из N корреляционных каналов обработки входят генератор псевдослучайной последовательности (ПСП) и генератор несущей частоты, а выходы N корреляционных каналов обработки соединены с соответствующими входами блока управления, отличающийся тем, что в него введены пороговый ограничитель, удвоитель частоты, делитель частоты и блок дешифраторов адреса, причем в состав каждого из корреляционных каналов обработки введены сумматор по модулю два, накапливающий сумматор, делитель частоты, буфер управления и буфер данных, причем выход генератора ПСП через сумматор по модулю два подключен к первому входу накапливающего сумматора, к другому входу которого подключен выход сигнала "Готов" генератора ПСП, к управляющему входу которого подключен выход "Код спутника" буфера управления, выход "Код тактовой частоты" подключен к управляющему входу второго делителя частоты, выход которого подключен к входу синхронизации генератора ПСП, а выход "Код несущей частоты" буфера управления подключен к управляющему входу генератора несущей частоты, выходы квадратурных составляющих которого соединены с соответствующими входами накапливающего сумматора, выходы которого соединены с соответствующими входами буфера данных, причем выход которого является выходом корреляционного канала обработки, который соединен общей шиной с входом буфера управления и с блоком управления, сигнальным входом корреляционного канала обработки которого является другой вход сумматора по модулю два, соединенные между собой управляющие входы второго делителя частоты и генератора несущей частоты, а также управляющий вход накапливающего сумматора являются соответственно первым и вторым входами сигналов синхронизации корреляционного канала обработки, управляющие входы записи и считывания буфера управления и выходного буфера данных являются соответствующими входами корреляционного канала обработки, при этом первый выход радиочастотного приемно-усилительного блока соединен с сигнальными входами N корреляционных каналов обработки, а второй выход подключен к входу удвоителя частоты, выход которого подключен к первому входу синхронизации N корреляционных каналов обработки непосредственно, а к второму входу синхронизации N корреляционных каналов обработки через первый делитель частоты, а выходы сигналов адреса и сигналов управления через блок дешифраторов адреса соединены с соответствующими управляющими входами записи и считывания каждого из N корреляционных каналов обработки.

| US, патент, 4578678 A, G 01 S 5/02, 1985 | |||

| SU, авторское свидетельство, 1821922 A1, H 04 B 7/02 | |||

| FR, патент, 2673781 A1, H 04 B 7/02, 19923 |

Авторы

Даты

1998-08-20—Публикация

1997-08-14—Подача