Изобретение относится к управляющей выбором изображения схеме для видеофонической системы, которая по задействованию переключателя делает изображение видеофонической системы подвижным или неподвижны.

В известной видеофонической системе видеосигналы, поступающие на ее вход, отображаются на экране такими, как они есть, и не предусмотрено устройство, позволяющее делать выбор между представлением этих видеосигналов в виде неподвижного или подвижного изображения. Поэтому пользователи, желающие видеть на экране неподвижное изображение, испытывают неудовлетворение.

Краткое описание изобретения

Поэтому целью настоящего изобретения является создание управляющей выбором между подвижностью и неподвижностью изображения видеофонической системы, которая способна представлять вводимые видеосигналы в виде неподвижного изображения или подвижного изображения.

Другой целью настоящего изобретения является создание управляющей выбором между подвижностью и неподвижностью изображения видеофонической системы очень простой конструкции, которая способна делать выбор между видеосигналами, вводимыми в качестве неподвижного изображения или подвижного изображения, после задействования переключателя.

Цели настоящего изобретения осуществлены созданием схемы, содержащей аналого-цифровой преобразователь для преобразования входных видеосигналов в цифровые сигналы путем синхронизации с сигналом поднесущей частоты, цифроаналоговый преобразователь для преобразования выходных сигналов аналого-цифрового преобразователя в аналоговые сигналы путем синхронизации с сигналом поднесущей частоты, блок выбора неподвижности для вывода импульсных сигналов, путем замыкания переключателя "неподвижность", генерирующий однокадровый сигнал для генерирования однокадровых сигналов путем синхронизации с сигналом кадровой синхронизации после выхода импульсных сигналов из блока выбора неподвижности, генерирующий сигнал подвижности блок для создания непрерывного выходного сигнала, задающего подвижность, путем замыкания переключателя "подвижность" для прекращения выдачи управляющих подвижностью сигналов по однокадровому сигналу от генерирующего однокадровый сигнал блока, управляющий неподвижностью/подвижностью блок для подачи сигнала поднесущей частоты на аналого-цифровой преобразователь только тогда, когда появляется однокадровый сигнал на выходе генерирующего однокадровый сигнал блока или управляющий подвижностью сигнал на выходе генерирующего сигнал подвижности блока, и запоминающую секцию для занесения выходных сигналов аналого-цифрового преобразователя в память произвольного доступа (RAM), когда появляется однокадровый сигнал на выходе генерирующего однокадровый сигнал блока, и для подачи сигналов, хранящихся в RAM, на цифро-аналоговый преобразователь, когда однокадровый сигнал не поступает от генерирующего, однокадровый сигнал блока и управляющий подвижностью сигнал не появляется на выходе генерирующего сигнал подвижности блока.

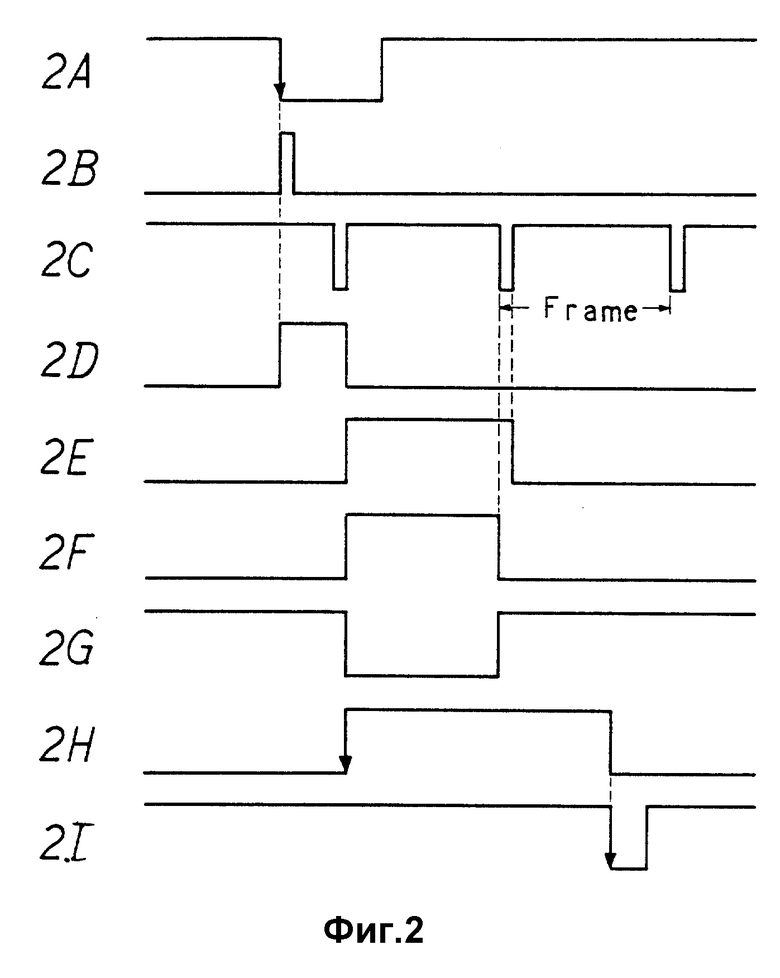

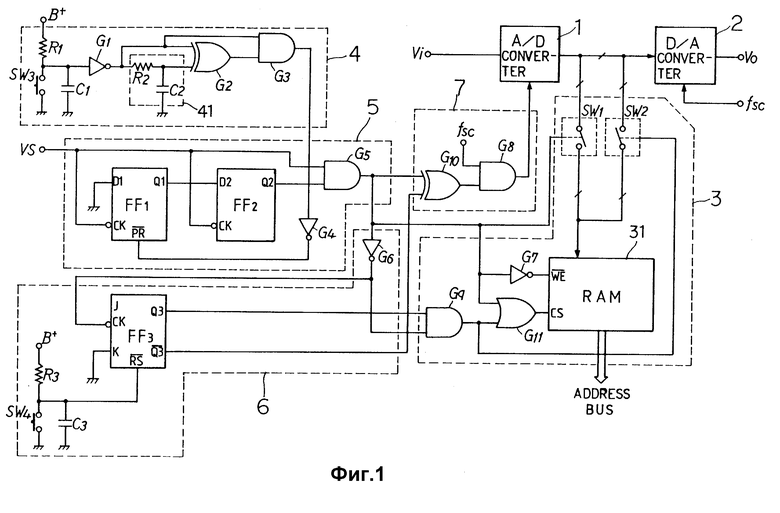

На фиг. 1 приведена принципиальная схема управляющей выбором неподвижного-подвижного изображения схемы видеофонической системы, соответствующей настоящему изобретению; на фиг. 2А - I - формы сигналов каждой из частей, изображенных на фиг. 1.

Подробное описание изобретения

Ниже подробно описан предпочтительный вариант осуществления настоящего изобретения со ссылками на фиг. 1 и 2.

Как показано на фиг. 1, управляющая выбором неподвижного-подвижного изображения схема для видеофонной системы, соответствующая настоящему изобретению, содержит блок выбора неподвижности 4 для подачи импульсных сигналов путем замыкания выключателя "неподвижность" SW3, генерирующий однокадровый сигнал блок 5 для создания однокадровых сигналов, синхронизируемых с сигналом кадровой синхронизации, когда импульсные сигналы появляются на выходе выбирающего неподвижность блока 4, генерирующий сигнал подвижности блок 6 для создания непрерывной последовательности управляющих непрерывностью сигналов путем замыкания выключателя. SW4 и для прекращения выдачи управляющих подвижностью сигналов по однокадровым сигналам от генерирующего однокадровый сигнал блока 5; управляющий неподвижностью-подвижностью блок 7 для подачи сигнала поднесущей частоты на аналого-цифровой преобразователь 1 только тогда, когда однокадровые сигналы появляются на генерирующем однокадровый сигнал блоке 5 или управляющие подвижностью сигналы появляются на выходе генерирующего сигнал подвижности блока 6; и запоминающую секцию 3 для записи выходных сигналов аналого-цифрового преобразователя 1 в память произвольного доступа (РАМ) 31, когда однокадровые сигналы появляются на выходе генерирующего однокадровый сигнал блока 5, и для подачи сигналов, хранящихся в РАМ 31, на цифроаналоговый преобразователь 2, когда однокадровые сигналы не появляются на выходе генерирующего однокадровый сигнал блока 5 и управляющие подвижностью сигналы не появляются на выходе генерирующего сигнал подвижности блока 6.

Выбирающий неподвижность блок 4 построен таким образом, что общая точка резистора R1, выключателя "неподвижность" SW3 и конденсатора C1 соединена с выводом вентиля "Исключающее ИЛИ" G2 и выводом вентиля "И" C3 через инвертор G1, их общая точка соединена с другим выводом вентиля "Исключающее ИЛИ" G2 через интегратор 41, состоящий из резистора R2 и конденсатора C2, и выход вентиля "Исключающее ИЛИ" G2 соединен с другим выводом вентиля "И" G3, в результате чего на выходе вентиля "И" G3 появляется сигнал высокого потенциала при замыкании включателя "неподвижность" SW3.

Генерирующий однокадровый сигнал блок 5 построен так, что выходной вывод вентиля "И" G3, который является выходом выбирающего неподвижность блока 4, соединен с единичным входом (PR) триггера FFI через инвертор G4, вход сигнала кадровой синхронизации (VS) соединен со счетными входами триггеров FF1 и FF2 и одним из входом вентиля "И" G5, выход Q1 триггера FF1 соединен с входом Q2 триггера FF2 и выход Q2 триггера FF2 соединен с другим входом вентиля "И" G5, в результате чего выходной сигнал высокого потенциала синхронизируется сигналом кадровой синхронизации после того, как сигнал высокого потенциала появляется на выбирающем неподвижность блоке 4.

Генерирующий сигнал подвижности блок 6 построен таким образом, что выход вентиля "И" G5, который является выходом генерирующего однокадровый сигнал блока 5, соединен со счетным входом (СК) триггера FF3 через инвертор G6 и общая точка резистора R3, выключателя "подвижность" SW4 и конденсатора C3 соединена с нулевым входом  триггера F3, в результате чего создается на выходе управляющий "подвижностью" сигнал, когда замкнут выключатель "подвижность" SW4, и накладывается запрет на подачу на выход управляющего "подвижностью" сигнала, когда высокого потенциала сигнал одного кадра появляется на выходе генерирующего однокадровый сигнал блока 5.

триггера F3, в результате чего создается на выходе управляющий "подвижностью" сигнал, когда замкнут выключатель "подвижность" SW4, и накладывается запрет на подачу на выход управляющего "подвижностью" сигнала, когда высокого потенциала сигнал одного кадра появляется на выходе генерирующего однокадровый сигнал блока 5.

Управляющий подвижностью-неподвижностью блок 7 построен таким образом, что выход вентиля "И" G5, который является выходом генерирующего однокадровый сигнал блока 5, и выход  триггера FF3 соединены с одним из входов вентиля "И" G8 через вентиль "ИЛИ" G10, а на другой вход вентиля "И" G8 поступает сигнал поднесущей частоты (fSC), и выход вентиля "И" G8 соединен с аналого-цифровым преобразователем 1, на который поступают видеосигналы, в результате чего сигнал поднесущей частоты (fSC) проходит на аналого-цифровой преобразователь 1 только тогда, когда высокого потенциала сигнал одного кадра появляется на выходе генерирующего однокадровый сигнал блока 6 или когда управляющий подвижностью сигнал появляется на выходе генерирующего сигнал подвижности блока 6.

триггера FF3 соединены с одним из входов вентиля "И" G8 через вентиль "ИЛИ" G10, а на другой вход вентиля "И" G8 поступает сигнал поднесущей частоты (fSC), и выход вентиля "И" G8 соединен с аналого-цифровым преобразователем 1, на который поступают видеосигналы, в результате чего сигнал поднесущей частоты (fSC) проходит на аналого-цифровой преобразователь 1 только тогда, когда высокого потенциала сигнал одного кадра появляется на выходе генерирующего однокадровый сигнал блока 6 или когда управляющий подвижностью сигнал появляется на выходе генерирующего сигнал подвижности блока 6.

Запоминающая секция 3 построена таким образом, что выход генерирующего однокадровый сигнал блока 5 соединен с управляющим выводом выключателя SW1 и одним из входов вентиля "ИЛИ" G11 и соединен с входом "разрешение записывания"  памяти произвольного доступа RAM 31 через инвертор G7, выход инвертора G6, который соединен с выходом генерирующего однокадровый сигнал блока 5, и выход Q3 триггера FF3 генерирующего сигнал подвижности блока 6 соединены с другим входом вентиля "ИЛИ" G11 и управляющим выводом выключателя SW2 через вентиль "И" G9, выход вентиля "ИЛИ" G11 соединен с коммутирующим чип входом (CS) памяти RAM 31 и выключатели SW1 и SW2 соединены параллельно между общей точкой аналого-цифрового преобразователя 1 и цифроаналогового преобразователя 2 и памятью RAM 31, в результате чего память RAM 31 переходит в режим записывания и записывает сигналы, появляющиеся на выходе аналого-цифрового преобразователя 1, когда высокого потенциала сигнал одного кадра появляется на выходе генерирующего однокадровый сигнал блока 5, и память RAM 31 переходит в режим считывания и считывает записанные в ней сигналы, передавая их на цифроаналоговый преобразователь 2, когда отсутствует высокого потенциала сигнал одного кадра на выходе генерирующего однокадровый сигнал блока 5 и отсутствует управляющий подвижностью сигнал на выходе генерирующего сигнал водвижности блока 6.

памяти произвольного доступа RAM 31 через инвертор G7, выход инвертора G6, который соединен с выходом генерирующего однокадровый сигнал блока 5, и выход Q3 триггера FF3 генерирующего сигнал подвижности блока 6 соединены с другим входом вентиля "ИЛИ" G11 и управляющим выводом выключателя SW2 через вентиль "И" G9, выход вентиля "ИЛИ" G11 соединен с коммутирующим чип входом (CS) памяти RAM 31 и выключатели SW1 и SW2 соединены параллельно между общей точкой аналого-цифрового преобразователя 1 и цифроаналогового преобразователя 2 и памятью RAM 31, в результате чего память RAM 31 переходит в режим записывания и записывает сигналы, появляющиеся на выходе аналого-цифрового преобразователя 1, когда высокого потенциала сигнал одного кадра появляется на выходе генерирующего однокадровый сигнал блока 5, и память RAM 31 переходит в режим считывания и считывает записанные в ней сигналы, передавая их на цифроаналоговый преобразователь 2, когда отсутствует высокого потенциала сигнал одного кадра на выходе генерирующего однокадровый сигнал блока 5 и отсутствует управляющий подвижностью сигнал на выходе генерирующего сигнал водвижности блока 6.

Ниже описана работа устройства, соответствующего настоящему изобретению.

Когда питание подано на силовой вывод B+ и нажат выключатель SW3, низкого потенциала сигнал, проиллюстрированный на фиг. 2А, поступает на вход инвертора G1 и высокого потенциала сигнал появляется на выходе инвертора G1, высокого потенциала сигнал поступает на один из входов вентиля "Исключающее "ИЛИ" G2 и один из входов вентиля "И" G3, а затем после задержки на предопределенное время в интеграторе 41, которое зависит от резистора P2 и конденсатора C2, он (т. е. высокого потенциала сигнал) поступает на другой вход вентиля "Исключающее ИЛИ" C2. Поэтому высокого потенциала сигнал появляется на выходе вентиля "Исключающее ИЛИ" G2 после определенной задержки поступает на другой вход вентиля "И" G8 таким образом, что вентиль "И" G3 создает на своем выходе высокого потенциала импульсные сигналы, показанные на фиг. 2B. Высокого потенциала импульсные сигналы преобразуются в низкого потенциала импульсные сигналы инвертором G4 и поступают на единичный вход  триггера FF1, в результате чего триггер FF1 устанавливается в единичное состояние и высокого потенциала сигнал, показанный на фиг. 2, D, появляется на выходе Q1 и поступает на вход D2 триггера FF2. В то же самое время сигналы кадровой синхронизации (VS), показанные на фиг. 2C, поступают на вход сигналов кадровой синхронизации (VS), низкого потенциала сигнал, показанный на фиг. 2, появляется на выходе Q1 триггера FF1 в тот момент, когда в первый раз вводится сигнал кадровой синхронизации, и в то же самое время высокого потенциала сигнал, показанный на фиг. 2E, появляется на выходе Q2 триггера FF2 и поступает на другой вход вентиля "И" C5, после чего низкого потенциала сигнал появляется на выходе Q2 триггера FF2, когда вновь вводится сигнал кадровой синхронизации.

триггера FF1, в результате чего триггер FF1 устанавливается в единичное состояние и высокого потенциала сигнал, показанный на фиг. 2, D, появляется на выходе Q1 и поступает на вход D2 триггера FF2. В то же самое время сигналы кадровой синхронизации (VS), показанные на фиг. 2C, поступают на вход сигналов кадровой синхронизации (VS), низкого потенциала сигнал, показанный на фиг. 2, появляется на выходе Q1 триггера FF1 в тот момент, когда в первый раз вводится сигнал кадровой синхронизации, и в то же самое время высокого потенциала сигнал, показанный на фиг. 2E, появляется на выходе Q2 триггера FF2 и поступает на другой вход вентиля "И" C5, после чего низкого потенциала сигнал появляется на выходе Q2 триггера FF2, когда вновь вводится сигнал кадровой синхронизации.

В результате этого вентиль "И" G5 исполняет операцию "И" над сигналами, показанными на фиг. 2C и 2E, и выдает высокого потенциала сигналы для однокадрового периода. Высокого потенциала сигнал с выхода вентиля "И" G5 поступает на один из входов вентиля "И" G8 через вентиль "ИЛИ" G10, и поэтому сигнал поднесущей частоты (fSC) поступает на аналого-цифровой преобразователь 1 через вентиль "И" G8. Соответственно, видеосигналы, поступающие на вход видеосигналов (V1) синхронизируются сигналом поднесущей частоты (fSC) на аналого-цифровом преобразователе 1 и превращаются в цифровые сигналы, а затем вновь синхронизируются с сигналом поднесущей частоты (fSC) на цифро-аналоговом преобразователе 2 и преобразуются в аналоговые сигналы и появляются на выходе для видеосигналов (V0). В это же время высокого потенциала сигнал, который идет с выхода вентиля "И" G5 генерирующего однокадровый сигнал блока 5, поступает на управляющий вход выключателя (SW1) и замыкает его и также поступает на коммутирующий тип вход (cS) памяти RAM 31, коммутируя ее через вентиль "ИЛИ" G11. Высокого потенциала сигнал преобразуется в низкого потенциала сигнал на преобразователе G7 и поступает на вход "разрешение записывания"  памяти РАМ 31, в результате чего память переходит в режим записывания. Соответственно, сигналы, которые выдает аналого-цифровой преобразователь 1, запоминаются в памяти РАМ 31, проходя через выключатель SW1.

памяти РАМ 31, в результате чего память переходит в режим записывания. Соответственно, сигналы, которые выдает аналого-цифровой преобразователь 1, запоминаются в памяти РАМ 31, проходя через выключатель SW1.

Далее, высокого потенциала сигнал, идущий с выхода вентиля "И" G5, преобразуется в низкого потенциала сигнал, показанный на фиг. 2G, на инверторе G6 и поступает на счетный вход (СК) триггера FF3, в результате чего высокого уровня сигнал, показанный на фиг. 2H, появляется на выходе Q3 триггера FF3 и низкого потенциала сигнал появляется на выходе Q3 триггера FF3. После этого, когда низкого потенциала сигнал, показанный на фиг. 2F, появляется на выходе вентиля "И" G5 генерирующего однокадровый сигнал блока 5, низкого потенциала сигнал появляется на выходе вентиля "ИЛИ" G10, в результате чего сигнал поднесущей частоты (fSC) не проходит через вентиль "И" G8 и аналого-цифровой преобразователь 1 не осуществляет аналого-цифровое преобразование.

В то же самое время, поскольку низкого потенциала сигнал с выхода вентиля "И" G5 поступает на управляющий вход выключателя SW1, этот выключатель SW1 размыкается, и низкого потенциала сигнал преобразуется в высокого потенциала сигнал на инверторе G7 и поступает на вход "разрешение записывания" памяти RAM 31. Далее, низкого потенциала сигнал с выхода вентиля "И" C5 преобразуется в высокого потенциала сигнал, показанный на фиг. 2G, на инверторе G6 и поступает на один из входов вентиля "И" G9 и поскольку высокого потенциала сигнал с выхода Q3 триггера FF3 поступает на другой вход вентиля "И" G9, на выходе вентиля "И" G9 появляется высокого потенциала сигнал, который поступает на управляющий вход выключателя SW2 и замыкает его. Высокого потенциала сигнал с выхода вентиля G9 поступает на коммутирующий чип вход (cS) памяти RAM 31 через вентиль "ИЛИ" G11, в результате чего память RAM 31 переходит в режим считывания.

Соответственно, цифровые сигналы, хранящиеся в памяти RAM 31, считываются, проходят через выключатель SW2 и преобразуются в аналоговые сигналы на цифро-аналоговом преобразователе 2 путем синхронизации с сигналом поднесущей частоты (fSC) и затем подаются на выход (V0) для видеосигналов.

В результате этого, сигналы, хранящиеся в памяти РАМ 31 непрерывно выводятся на однокадровом периоде, создавая неподвижные изображение на экране.

В то же время, когда выключатель "подвижность" SW4 замкнут, низкого потенциала сигнал, показанный на фиг. 2I, поступает на нулевой вход  триггера FF3, поэтому триггер FF3 переходит в нулевое состояние и на его выходе появляются сигналы, задающие подвижность. Поэтому, поскольку низкого потенциала сигнал, показанный на фиг. H, появляется на выходе Q3 триггера FF3, низкого потенциала сигнал появляется на выходе вентиля "И" G9, память RAM 31 не коммутируется и выключатель SW2 разомкнут.

триггера FF3, поэтому триггер FF3 переходит в нулевое состояние и на его выходе появляются сигналы, задающие подвижность. Поэтому, поскольку низкого потенциала сигнал, показанный на фиг. H, появляется на выходе Q3 триггера FF3, низкого потенциала сигнал появляется на выходе вентиля "И" G9, память RAM 31 не коммутируется и выключатель SW2 разомкнут.

Более того, в это же время высокого потенциала сигнал, который является управляющим подвижностью сигналом, появляется на выходе  триггера FF3 и, поскольку высокого потенциала сигнал поступает на вентиль "И" G8 через вентиль "ИЛИ" C10, сигнал поднесущей частоты (fSC) непрерывно поступает на аналого-цифровой преобразователь 1 через вентиль "И" G8. Соответственно, видеосигналы, поступающие на вход (V1) для видеосигналов, преобразуются в цифровые сигналы на аналого-цифровом преобразователе 1 путем синхронизации с сигналом поднесущей частоты (fSC) и непрерывно выводятся на выход (V0) для видеосигналов, в результате чего на экране создается подвижное изображение.

триггера FF3 и, поскольку высокого потенциала сигнал поступает на вентиль "И" G8 через вентиль "ИЛИ" C10, сигнал поднесущей частоты (fSC) непрерывно поступает на аналого-цифровой преобразователь 1 через вентиль "И" G8. Соответственно, видеосигналы, поступающие на вход (V1) для видеосигналов, преобразуются в цифровые сигналы на аналого-цифровом преобразователе 1 путем синхронизации с сигналом поднесущей частоты (fSC) и непрерывно выводятся на выход (V0) для видеосигналов, в результате чего на экране создается подвижное изображение.

Изобретение относится к управляющим схемам выбора неподвижного-подвижного изображения. Техническим результатом изобретения является создание управляющей схемы в видеофонической системе, которая представляет вводимые видеосигналы в виде неподвижного или подвижного изображения. Схема управления выбором содержит аналого-цифровой преобразователь, цифроаналоговый преобразователь, блок генерирования сигнала управления заставкой при замыкании ключа заставки, блок генерирования однокадрового сигнала, реагирующий на сигнал управления заставкой, блок генерирования сигнала перемещения для генерирования сигнала управления перемещения, блок управления заставкой-перемещением, переключатель, подключенный к входу цифроаналогового преобразователя для ввода запомненного цифрового сигнала, причем цифровые сигналы синхронизированы сигналом поднесущей частоты. 6 з.п.ф-лы, 2 ил.

| US 4506387 A, 10.11.5/78, 1985 | |||

| Устройство для записи и воспроизведения телевизионного сигнала цветного изображения | 1974 |

|

SU1466667A3 |

Авторы

Даты

1998-10-27—Публикация

1990-07-31—Подача