Изобретение относится к обрабатывающему изображения устройству и внешнему запоминающему устройству, используемому в нем. Более конкретно настоящее изобретение относится к обрабатывающему изображения устройству, предназначенному для использования в качестве телевизионного игрового устройства и способному отображать цветное изображение на экране дисплея в соответствии с цветовыми данными на каждую точку.

Один из примеров обрабатывающего изображения устройства такого типа описан в выложенном японском патенте (Kakai Sho) 59-118184 от 7 июля 1984 (соответствующем патенту США N 4824106, выданном 25 апреля 1989 г.). Это известное обрабатывающее изображения устройство отображает цветное изображение путем комбинирования подвижного изображения (объектов) и фонового изображения (неподвижных изображений) на экране растрового сканирующего монитора. Соответственно присвоены приоритеты подвижному изображению и неподвижному изображению, и только обладающее большим приоритетом подвижное изображение или неподвижное изображение отображается в области, в которой подвижное изображение и неподвижное изображения перекрываются. В этом случае, поскольку подвижное изображение или неподвижное изображение более низкого приоритета не отображается, невозможно отобразить состояние, где два изображения частично совпадают, или изображение прозрачного предмета, подобного стеклу.

Известного технического уровня обрабатывающее изображения устройство способно отображать подвижное изображение и фоновое изображение, которые частично совпадают, путем отображения подвижного изображения в каждом втором кадре растрового сканирующего монитора. Однако даже при таком способе отображения нельзя отображать прозрачный объект.

Прозрачный объект можно отобразить, если обрабатывающее изображения устройство оснащено памятью для хранения модифицированных цветовых данных, представляющих наложенное изображение подвижной картины и неподвижной картины независимо от исходных цветовых данных. Компьютерная графическая технология позволяет использовать способ, при котором наперед запоминаются дополнительные цветовые данные, поскольку нет ограничений на емкость памяти. Однако телевизионное игровое устройство должно быть недорогим, а поэтому его запоминающая способность оказывается ограниченной. Поэтому невозможно приложить компьютерную графическую технологию к телевизионному игровому устройству.

Исходя из сказанного, главной целью настоящего изобретения является создание обрабатывающего изображения устройства, способного отобразить структуры из множества изображений.

Следующей целью настоящего изобретения является создание обрабатывающего изображения устройства, способного отображать прозрачный объект.

Кратко говоря, настоящее изобретение предполагает создание обрабатывающего изображения устройства, способного отображать цветное изображение на дисплее в соответствии с цветовыми данными по каждой точке, которое содержит первое генерирующее изобразительные данные устройство для генерирования первых цветовых данных первого изображения, второе генерирующее изобразительные данные устройство для генерирования вторых цветовых данных второго изображения для каждой его точки, арифметическое устройство для выполнения предопределенной арифметической операции путем использования первых цветовых данных и вторых цветовых данных, и генерирующее видеосигналы устройство для преобразования выходных данных арифметического устройства в видеосигнал для посылки на тот же самый дисплей.

Первые цветовые данные и вторые цветовые данные, созданные соответственно первым генерирующим изобразительные данные устройством и вторым генерирующим изобразительные данные устройством, поступают на арифметическое устройство и затем арифметическое устройство вычисляет, например, среднее значение первых цветовых данных и вторых цветовых данных для создания цветовых данных, представляющих наложенную структуру первого и второго изображений. Генерирующее видеосигнал устройство принимает цветовые данные, генерирует RGB (красный-зеленый-синий) сигналы или полный видеосигнал на основе цветовых данных и затем передает RGB сигналы или полный видеосигнал на дисплей, подобный растровому сканирующему монитору. В результате этого первое и второе изображения отображаются составным цветом на экране растрового сканирующего монитора.

В соответствии с настоящим изобретением есть возможность отобразить на дисплее наложенную структуру некоторого множества изображений с простой структурой. Таким образом, обрабатывающее изображения устройство способно отображать прозрачный объект, подобный изделию из стекла. В соответствии с настоящим изобретением обрабатывающее изображения устройство способно отобразить прозрачный объект без необходимости увеличения емкости памяти, поскольку любые цветовые данные, представляющие некоторое наложенное изображение, нет необходимости предварительно заносить в память. Поэтому обрабатывающее изображения устройство, соответствующее настоящему изобретению, в частности, пригодно к использованию в качестве телевизионного игрового устройства.

В одном из вариантов осуществления внешнее запоминающее устройство, используемое внутри обрабатывающего изображения устройства, включает в себя запоминающее символьные данные устройство для хранения символьных данных символов подвижных изображений и символов неподвижных изображений и запоминающее программы цветовой арифметики устройство для хранения программы цветовой арифметики, по которой выполняются цветовые арифметические операции. Первое генерирующее цветовые данные устройство и второе генерирующее цветовые данные устройство генерируют соответственно первые цветовые данные первого изображения и вторые цветовые данные второго изображения на базе символьных данных, считываемых из внешнего запоминающего устройства. Арифметическое устройство выполняет арифметическую операцию, определенную арифметической программой, считанной из внешнего запоминающего устройства, над первыми цветовыми данными и вторыми цветовыми данными.

Дополнительно арифметическое устройство включает в себя некоторое множество арифметических функций, а цветовая арифметическая программа включает в себя данные, специфицирующие одну из этого множества арифметических функций. Поэтому арифметическое устройство исполняет ту арифметическую операцию, которая соответствует арифметической функции, специфицированной специфицирующими арифметическую функцию данными.

Дополнительно цветовая арифметическая программа включает в себя программу области данных для генерирования данных, специфицирующих область на экране названного дисплея, и арифметическое устройство для выполнения арифметической операции в области, специфицированной названными областями данных.

Далее цветовая арифметическая программа включает в себя программу монохроматичных цветовых данных для генерирования монохроматичных цветовых данных, которая специфицирует цвет всего экрана дисплея в качестве некоторого монохроматичного цвета, и арифметическое устройство выполняет арифметическую операцию, используя по крайней мере что-либо одно из первых цветовых данных или вторых цветовых данных и монохроматичные цветовое данные, созданные на основе монохроматичных цветовых данных.

Эти и другие цели, признаки, аспекты и преимущества настоящего изобретения станут более очевидны после ознакомления с нижеследующим подробным описанием вариантов осуществления настоящего изобретения, которое ведется со ссылками на приложенные фигуры.

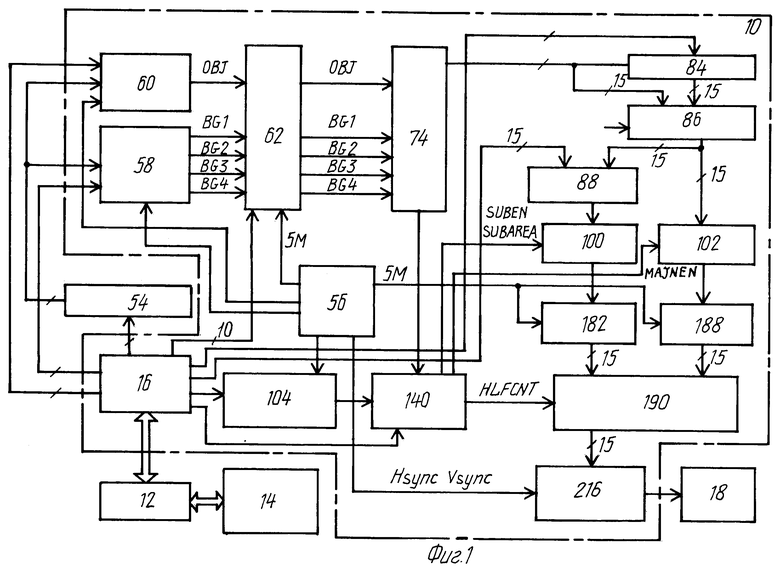

Фиг. 1 является блок-схемой, иллюстрирующей один из вариантов осуществления настоящего изобретения.

Фиг. 2 является иллюстрацией программных данных, которые подлежат предварительному запоминанию программным запоминающим устройством, входящим в состав варианта осуществления, которые представлены фиг. 1.

Фиг. 3 иллюстрирует возможность образования цветового окна в варианте осуществления, представленном фиг. 1.

Фиг. 4 является блок-схемой, иллюстрирующей интерфейс центрального процессорного устройства, входящий в состав варианта осуществления, представленного фиг. 1.

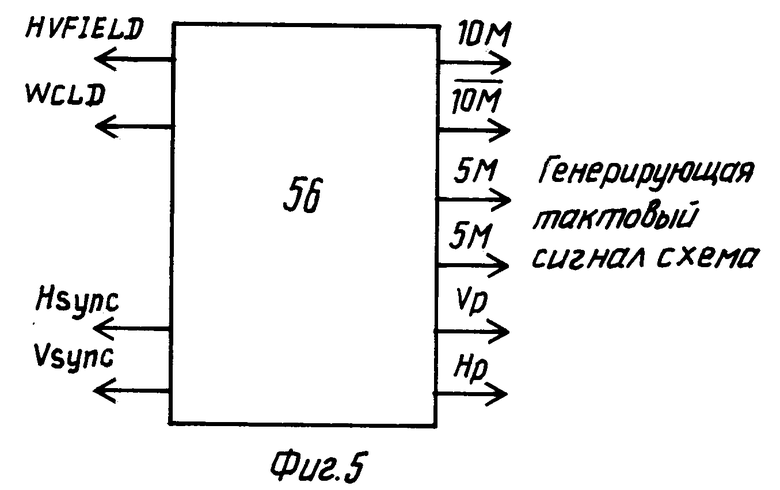

Фиг. 5 иллюстрирует генерирующую тактовые сигналы схему, входящую в состав варианта, представленного фиг. 1.

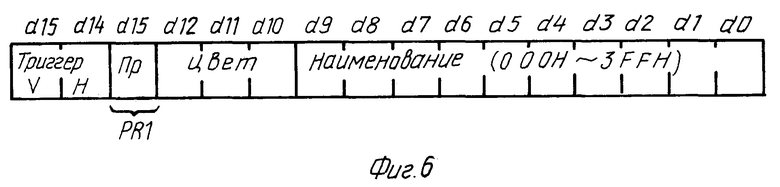

Фиг. 6 иллюстрирует пример кодовых данных неподвижного изображения, соответствующий варианту осуществления, представленного фиг. 1.

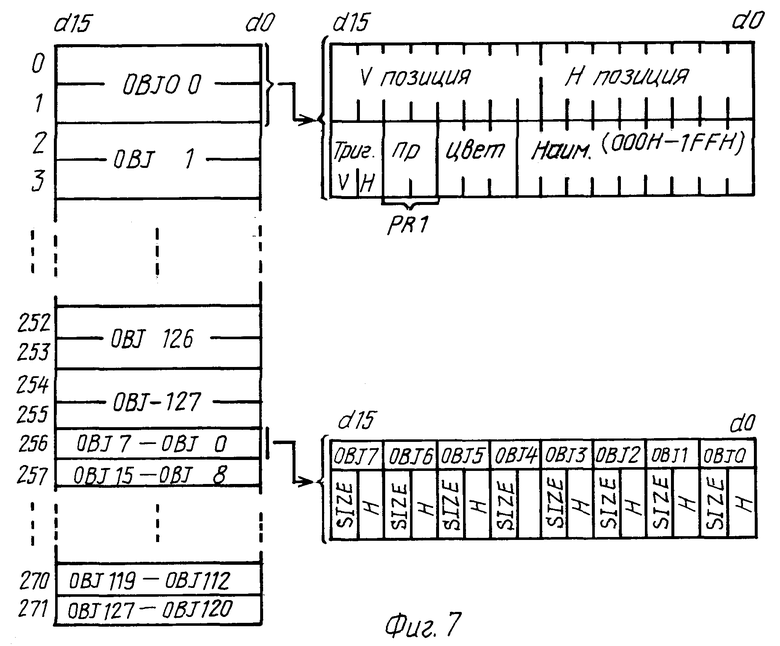

Фиг. 7 иллюстрирует пример данных подвижного изображения, соответствующий варианту осуществления, представленному фиг. 1.

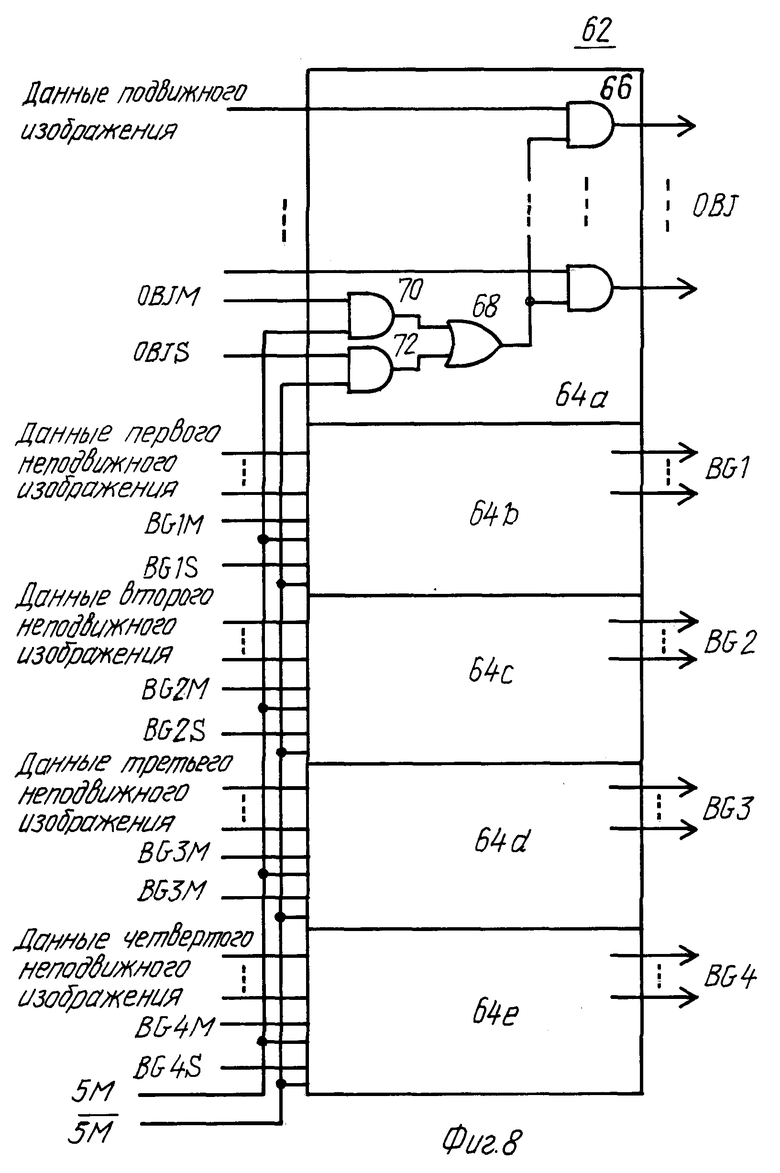

Фиг. 8 представляет блок-схему выбирающей основные/вспомогательные данные схемы, используемой в варианте осуществления, представленном фиг. 1.

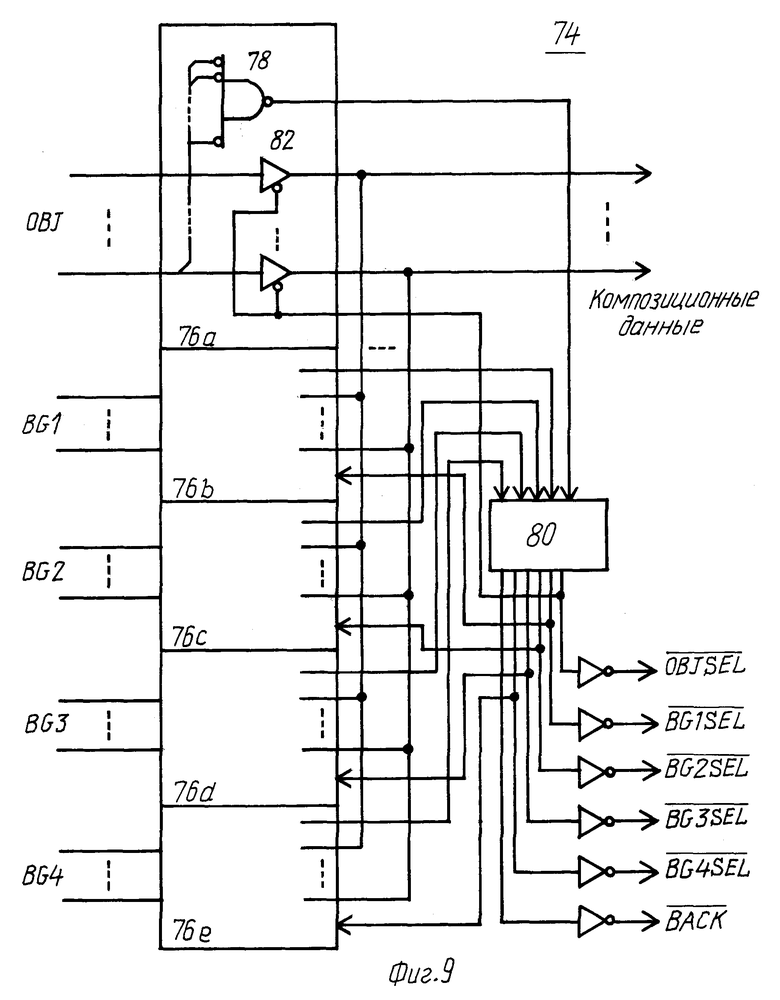

Фиг. 9 является блок-схемой приоритетной схемы варианта, представленного фиг. 1.

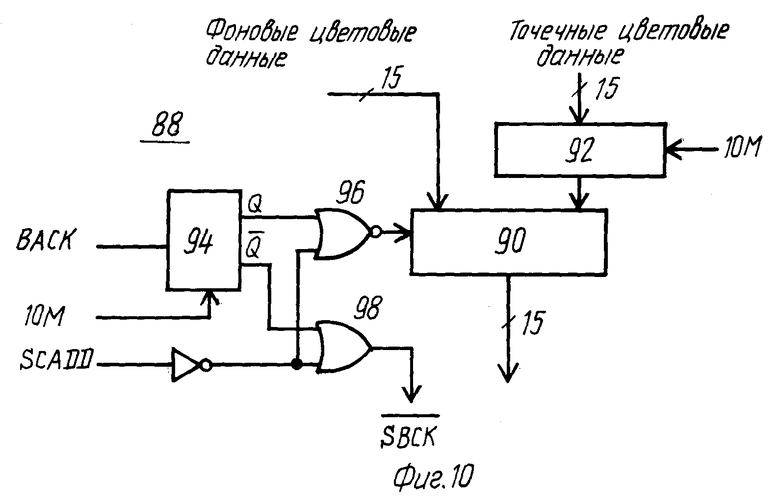

Фиг. 10 является блок-схемой прибавляющей монохроматический цвет схемы варианта, представленного фиг. 1.

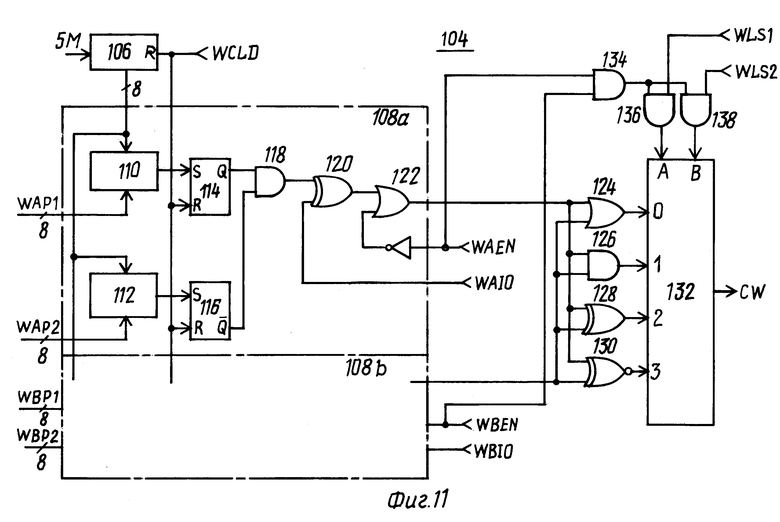

Фиг. 11 является блок-схемой генерирующей сигнал интервала изображения варианта осуществления, представленного фиг. 1.

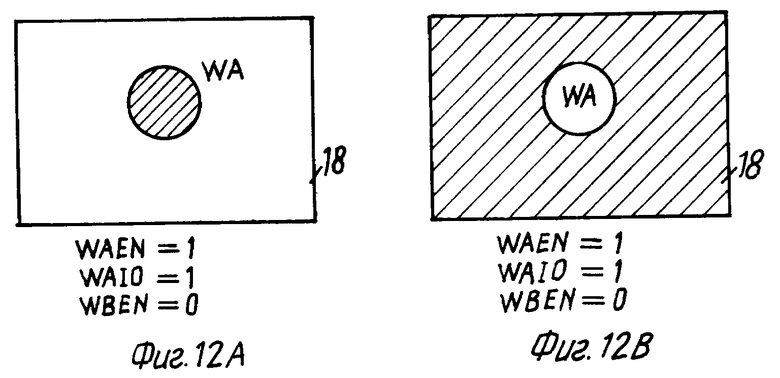

Фиг. 12A и фиг. 12B являются иллюстрациями состояний экрана растрового развертывающего монитора, когда разрешена внутренность первого окна и когда разрешена наружность первого окна соответственно.

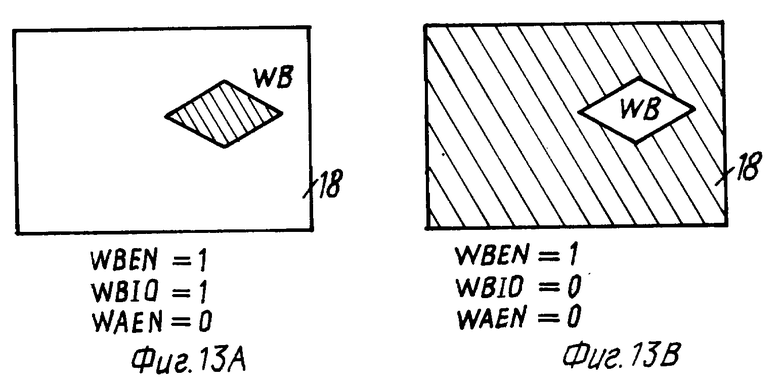

Фиг. 13A и фиг. 13B являются иллюстрациями состояний экрана растрового развертывающего монитора, когда разрешена внутренность второго окна и когда разрешена наружность второго окна соответственно.

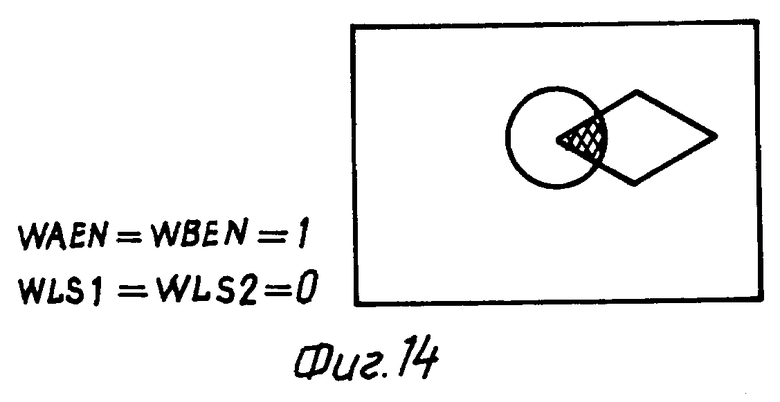

Фиг. 14 является иллюстрацией состояния экрана растрового развертывающего монитора, когда одновременно разрешены первое и второе окна, как при И операции.

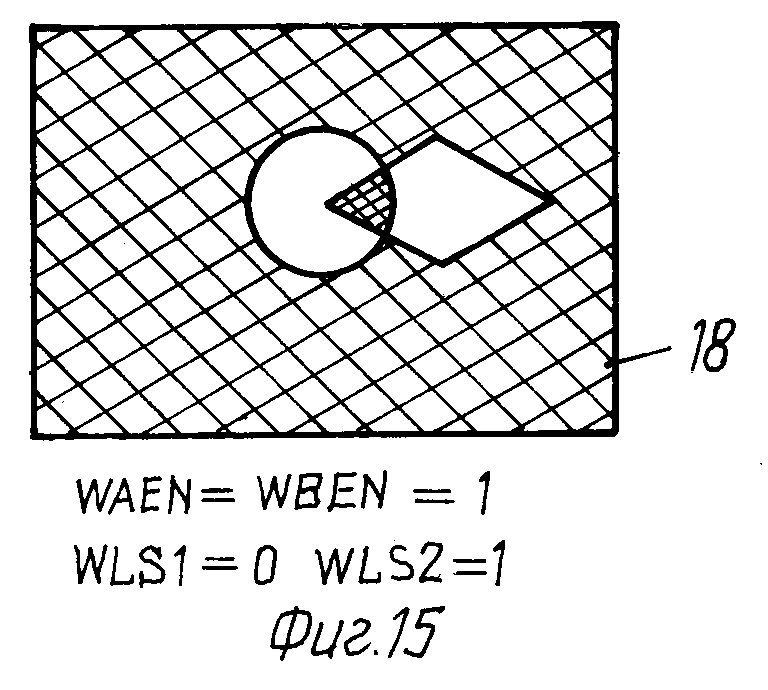

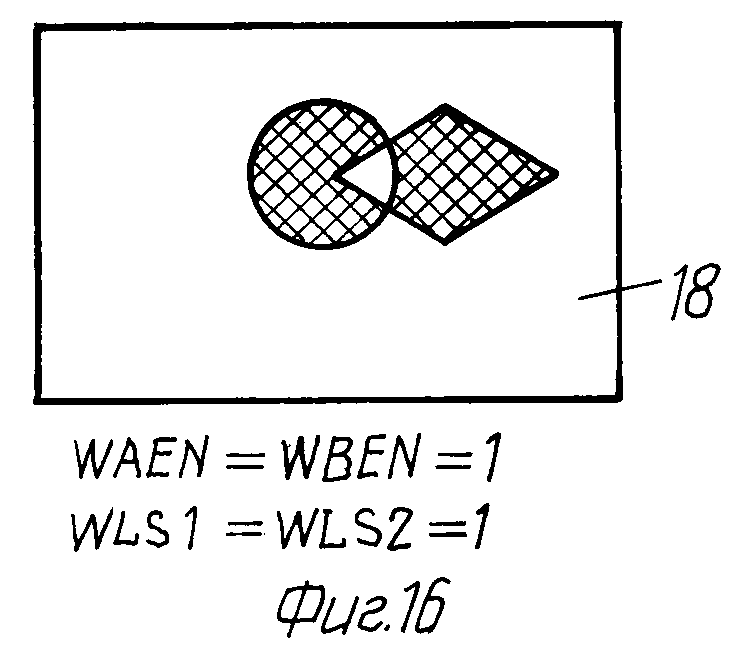

Фиг. 15, 16 являются иллюстрацией состояния экрана растрового развертывающего монитора, когда разрешены первое и второе окна, как при Исключающее ИЛИ и Исключающее НЕ-ИЛИ операции соответственно.

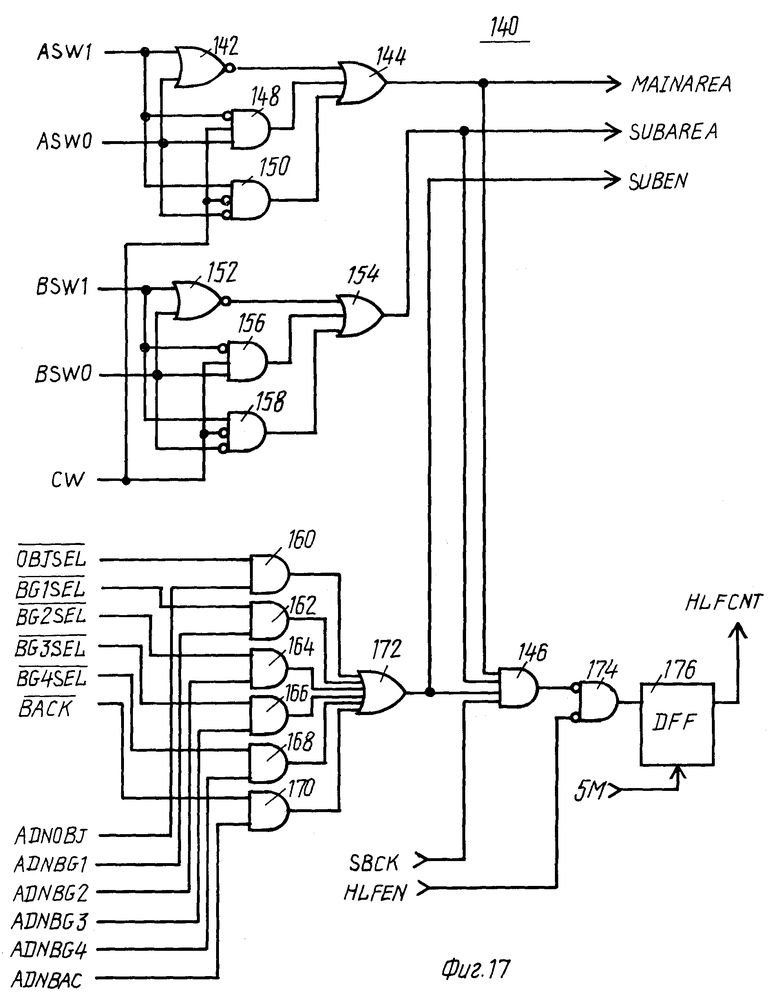

Фиг. 17 является блок-схемой, иллюстрирующей управляющую работой схему варианта осуществления, представленного фиг. 1.

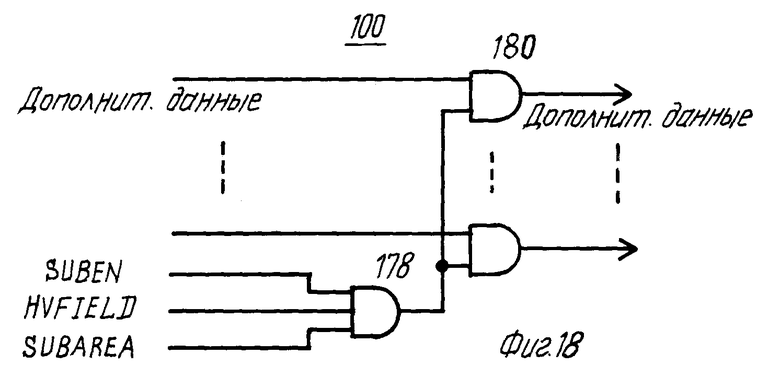

Фиг. 18 является блок-схемой, иллюстрирующей управляющую дополнительными данными схему варианта осуществления, представленного фиг. 1.

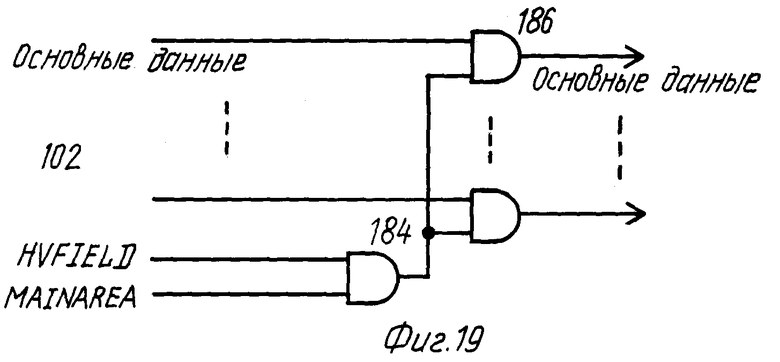

Фиг. 19 является блок-схемой, иллюстрирующей управляющую основными данными схему варианта, представленного фиг. 1.

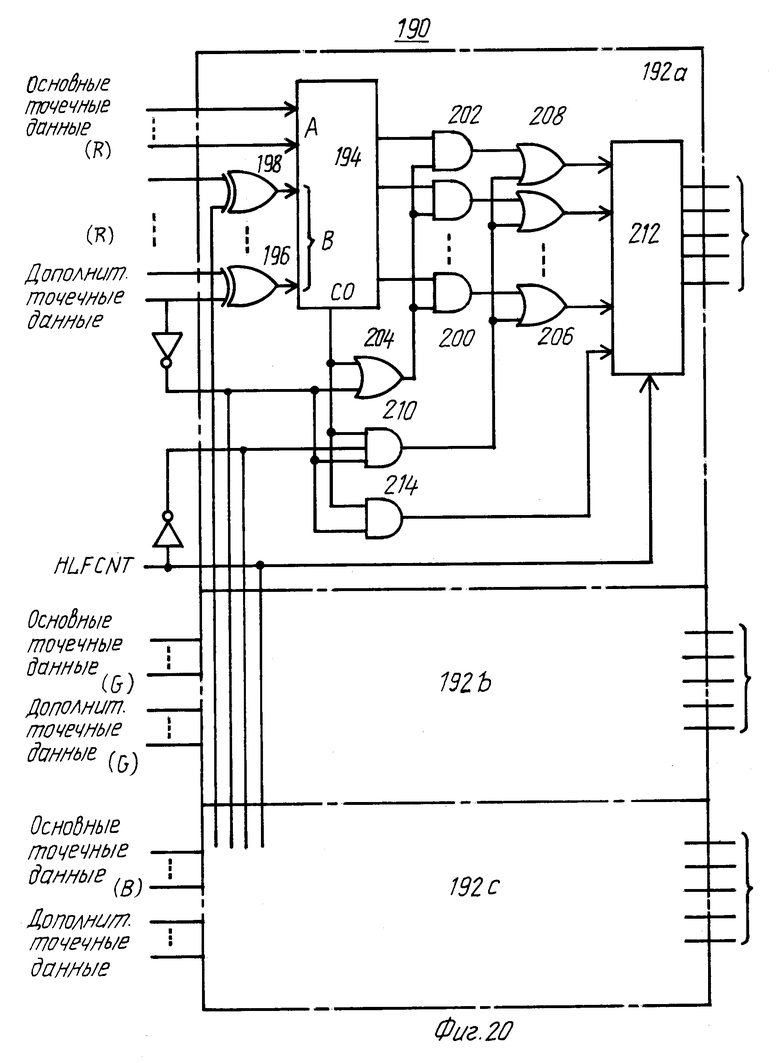

Фиг. 20 является блок-схемой, иллюстрирующей арифметическую схему варианта осуществления, представленного фиг. 1.

Подробное описание предпочтительных вариантов осуществления

Как видно на фиг. 1, видеопроцессор 10 в иллюстрируемом варианте осуществления соединен с центральным процессорным устройством 12. Центральное процессорное устройство 12 работает в соответствии с программными данными, хранящимися в запоминающем устройстве 14, подобном съемной запоминающей кассете, для подачи необходимых сигналов в данных через интерфейс центрального процессорного устройства 16, который входит в состав видеопроцессора 10, на компоненты (описания которых даны ниже) видеопроцессора 10, чтобы в соответствии с программой на экране растрового сканирующего монитора 18 отображалось изображение. Центральное процессорное устройство 12 может представлять собой, например, 16-битовый микропроцессор.

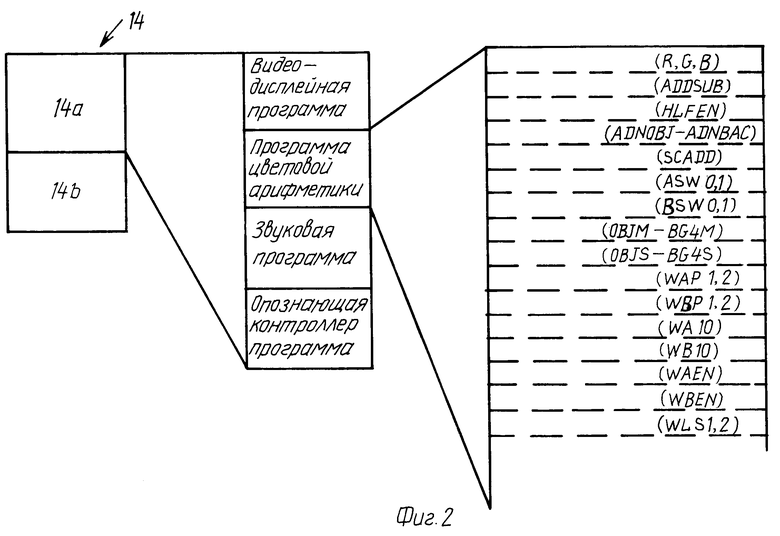

Запоминающее программы устройство 14, которым может быть съемная запоминающая кассета, как сказано выше, включает в себя память, которая хранит программные данные, необходимые для введения игры, и символьные данные символов подвижных изображений и символы неподвижных изображений для игры. Как видно на фиг. 2, программные данные хранятся в программной памяти 14a, которую типично создают в виде ROM (только считываемая память), и символьные данные хранятся в символьной памяти 14b, которую типично создают в виде памяти произвольного доступа RAM. В программной памяти 14a, помимо программы, необходимой для ведения игры, хранится цветовая арифметическая программа. Цветовая арифметическая программа включает в себя монохроматичные цветовые данные R (красный), G (зеленый) и B (синий), специфицирующие арифметику данные ADDSUB, специфицирующие средние значения данные HLFEN, специфицирующие операционное изображение данные ADNOBJ - ADNBAC, разрешающий прибавление монохроматического цвета сигнал SCADD, устанавливающие основное изображение данные ASW0 и ASW1, устанавливающие дополнительное изображение данные BSW0 и BSW1, специфицирующие основное изображение данные OBJM - BG4M, специфицирующие вспомогательные изображения данные OBJS - BG4S, устанавливающие первое окно данные WAP1 и WAP2, специфицирующие внутренность/наружность данные WAIO, специфицирующие внутренность/наружность второго окна данные WBIO, разрешающий первое окно сигнал WAEN, разрешающий второе окно сигнал WBEN, связные данные WLS1 и WLS2 и т.д.

Монохроматичные цветовые данные R, G или B представляют собой 5 битов, указывающих градацию цвета при окрашивании фона в красный, синий или зеленый цвет, когда ничто из подвижных изображений OBJ и с первого по четвертое неподвижных изображений BG1 - BG4 не отображается. Специфицирующие арифметическую операцию данные ADDSUB состоят из одного бита, специфицирующего сложение или вычитание для арифметического устройства, которое будет описано ниже. Специфицирующие среднее значение данные HLFEN состоят из одного бита, указывающего арифметическому устройству на необходимость или ненадобность вычисления среднего значения. Специфицирующие операционное изображение данные ADNOBJ - ADNBAC представляют увеличиваемые данные, к которым прибавляются дополнительные изобразительные данные, включающие в себя специфицирующие данные ADNOBJ, ADNBG1, ADNBG2, ADNBG3, ADNBG4 и ADNBAC, по одному биту. Специфицирующие операционное изображение данные ADNBAC указывают цвет фона. Разрешающий прибавление монохроматичного цвета сигнал SCADD состоит из одного бита, специфицирующего необходимость добавления названного выше фонового цвета. Каждое из устанавливающих основное изображение данных ASW0 и ASW1 состоит из одного бита, подаваемого на управляющую основными данными схему (описанную ниже). Каждое из устанавливающих дополнительные изображения данных BSW0 и BSW1 состоит из одного бита, подаваемого на управляющую данными схему (описанную ниже). Специфицирующие основное изображение данные OBJM - BG4M представляют собой данные, которые указывают, какое изображение назначается главным, (и) которые включают в себя специфицирующие данные OBJM, BG1M, BG2M, BG3M и BG4M, каждое из которых состоит из одного бита. Специфицирующие дополнительные изображения данные OBJS - BG4S представляют собой данные, которые указывают, какое изображение назначено дополнительным, (и) которые включают в себя специфицирующие данные OBJS, BG1S, BG2S, BG3S и BG4S, каждое из которых состоит из одного бита.

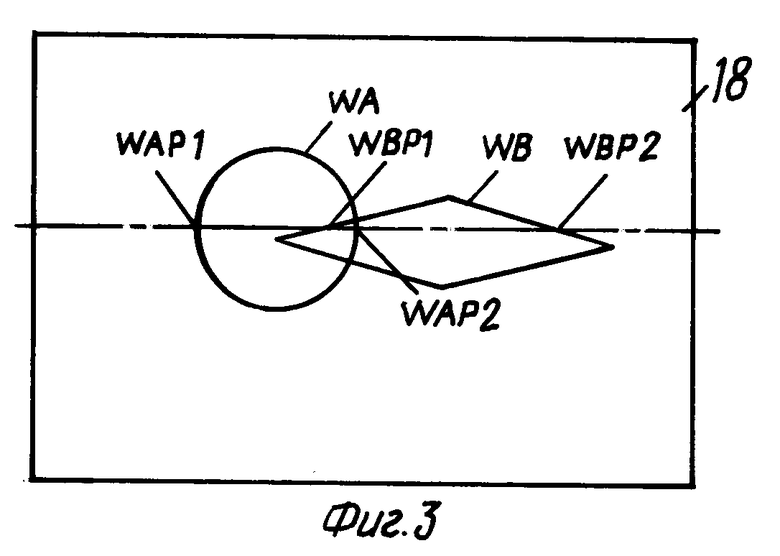

Представленный вариант осуществления способен установить два окна WA и WB на растровом сканирующем мониторе 18, соединенном с видеопроцессором 10, как показано на фиг. 3, и выполнять цветовую арифметическую операцию для внутренности или наружности окна WA и/или окна WB. Устанавливающие первое окно данные WAP1 и WAP2 задаются для каждой строки, причем эти данные соответственно указывают левую крайнюю позицию и правую крайнюю позицию первого окна WA. Устанавливающие второе окно данные WBP1 и WBP2 соответственно указывают левую крайнюю позицию и правую крайнюю позицию второго окна WB. Каждое из специфицирующих наружность/внутренность первого окна данных WAPIO и специфицирующих внутренность/наружность второго окна данных WBPIO представляет собой один бит, специфицирующий внутренность или наружность первого окна WA и второго окна WB соответственно. Однобитовый разрешающий установку первого окна сигнал WAEN устанавливается (в единицу) для разрешения первого окна WA, и однобитовый разрешающий второе окно сигнал WBEN устанавливается (в единицу) для разрешения второго окна WB. Связные данные WLS1 и WLS2 используются в качестве связных сигналов для коммутирования мультиплексора 123 (смотрите фиг. 11), который описан ниже.

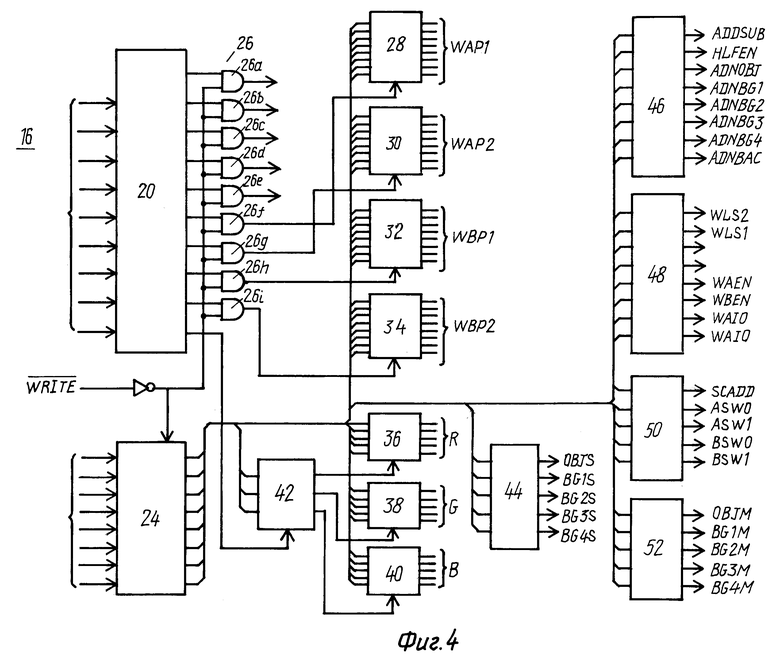

Центральное процессорное устройство 12 считывает программные данные из программного запоминающего устройства 14 и выводит их через интерфейс центрального процессорного устройства 16. Интерфейс центрального процессорного устройства 16 включает в себя адресный декодер 20, который принимает адресные данные по адресной шине центрального процессорного устройства 12, и затвор данных 24, который принимает данные по шине данных центрального процессорного устройства 12. Адресный декодер 22 декодирует адреса, принятые от центрального процессорного устройства 12, и создает открывающие затворы сигналы для открытия соответствующих затворов, изображенных на фиг. 1. Каждый из открывающих затворы сигналов поступает на один вход каждого И вентиля 26a-26i, которые образуют вентильную схему 26, и сигнал "записать" (WRITE), созданный центральным процессорным устройством 12, инвертируется и поступает на другой вход каждого из И вентилей 26a-26i. Инвертированный сигнал "записать" (WRITE) также поступает на затвор данных 24 в качестве сигнала "запереть".

Когда центральное процессорное устройство 12 подает определяющие левую крайнюю позицию первого окна данные WAP1 на шину данных, адрес, специфицирующий затвор данных 28, выдается на адресную шину, и поэтому адресный декодер 20 подает "1" на И вентиль 26f вентильной схемы 26. Поэтому определяющие левую крайнюю позицию первого окна данные WAP1, запертые затвором данных 24, отпираются затвором данных 28. Аналогично, определяющие правую крайнюю позицию первого окна данные WAP2, левую крайнюю позицию второго окна данные WBP1 и крайнюю правую позицию второго окна данные WBP2 запираются затворами данных 30, 32 и 34 в ответ на сигналы, подаваемые И вентилями 26g, 26h и 26i соответственно.

Монохроматические цветовые данные R, G и B, создаваемые центральным процессорным устройством 12, запираются запорами данных 36, 38 и 40 соответственно. Поскольку монохроматические цветовые данные R, G и B являются 5-битовыми наборами и затвор данных 24 является 8-битовым, старшие три бита данных, создаваемых центральным процессорным устройством 12, обозначают один из затворов данных 36, 38 и 40. В то же самое время декодер 42 декодирует старшие три бита и создает сигнал, разрешающий открыться одному из трех затворов данных 36, 38 и 40, поскольку адресный декодер 20 создает сигнал, специфицирующий декодер 42. Однако, если те же самые данные надлежит записать в затвор данных 36, 38 и 40, декодер 42 создает сигнал, отпирающий все затворы данных 36, 38 и 40, чтобы затворы данных 36, 38 и 40 запирали одинаковые градационные данные.

Затворы данных 44, 46, 48, 50 и 52 запирают данные или сигналы, как это разъяснено ниже со ссылками на фиг. 4, считанные из запоминающего программные данные устройства 14 центральным процессорным устройством 12, поэтому опущено дублирующее описание.

Например, запоминающее видеоданные устройство 54, построенное на 64К байтовой SRAM (статической произвольного доступа памяти), включает в себя экранную произвольного доступа память RAM и символьную произвольного доступа память RAM. Центральное процессорное устройство 12 пересылает графические данные (точечные данные), хранящиеся в символьной памяти 14b запоминающего программы устройства 14, через интерфейс центрального процессорного устройства 16 на символьную память RAM.

Видеопроцессор 10 снабжен генерирующей тактовые сигналы схемой 56. Генерирующая тактовые сигналы схема 56 создает тактовые сигналы путем обработки основного синхронизирующего сигнала, имеющего частоту, например, 21,47727 МГц, посредством, например, декодера и логической схемы и подает синхронизирующие сигналы на компоненты видеопроцессора 10. Если основной тактовый сигнал разделить по частоте на два, то будет получен синхронизирующий сигнал /10M (здесь "/" означает инверсию). Синхронизирующий сигнал /10M далее делится по частоте на 2, чтобы получить синхронизирующий сигнал /5M. Синхронизирующий сигнал /5M соответствует дисплейному интервалу в одну точку (т.е. одному пикселу) на экране растрового сканирующего монитора 18. Соответственно V-позиционные данные Vp, указывающие позицию относительно вертикального направления на экране растрового сканирующего монитора 18, и H-позиционные данные Hp, указывающие позицию относительно горизонтального направления на экране растрового сканирующего монитора 18, можно получить путем подсчета синхронизирующего сигнала /5M. Далее генерирующая тактовые сигналы схема 56 создает синхронизирующие сигналы Vsync и Hsync, необходимые для растрового сканирующего монитора 18, на базе V-позиционных данных Vp и H-позиционных данных Hp, и подает их на генерирующую видеосигналы схему (которая описана ниже). Генерирующая тактовые сигналы схема 56 создает сигнал HVFIELD, который остается "1" во время операции сканирования (дисплейный период) растрового сканирующего монитора 18, и тактовый сигнал WCLD, который устанавливается в "1" в начале каждой горизонтальной развертки. Сигнал HVFIELD подается на управляющую основными данными схему и управляющую дополнительными данными схему (которые описаны ниже), и сигнал WCLD поступает на генерирующую сигнал интервала схему (которая описана ниже).

Генерирующая данные неподвижного изображения схема 58 считывает шаблонные данные (символьный код) неподвижного изображения (фонового изображения) из программной памяти 14a запоминающего программы устройства 14, соответствующие данной ему программе через интерфейс центрального процессорного устройства 16 центральным процессорным устройством 12, считывает графические данные неподвижного изображения символа из запоминающего видеоданные устройства 54 с учетом шаблонных данных и затем выдает данные неподвижного изображения BG1, BG2, BG3 и BG4. Таким образом шаблонные данные неподвижного изображения, изображенные на фиг. 6, запоминаются в области запоминания шаблонных данных неподвижного изображения запоминающего видеоданные устройства 54 для каждого символа. Символьные данные неподвижного изображения, представляющие собой символ, представляют собой 10-битовые именные данные (символьный код), 3-битовые аттрибутивные данные, однобитовые приоритетные данные и двухбитовые переключательные данные. Генерирующая данные неподвижного изображения схема 58 вычисляет адресное значение области хранения символьного шаблона неподвижного изображения в запоминающем изобразительные данные устройстве 54, соответствующие каждой строчной позиции на экране растрового сканирующего монитора 18 на базе H-позиционных данных Hp и V-позиционных данных Vp, представляемых генерирующей тактовые сигналы схемой 56. Затем графические данные (точечные данные), образующие символ, специфицированный именными данными, хранящимися в ячейке, указанной адресным значением, в запоминающем видеоданные устройстве 54, выдаются. Если необходимо отобразить некоторое множество клеток неподвижного изображения, операция считывания для считывания именных данных и приоритетных данных воспроизводится, благодаря чему считываются точечные данные, соответствующие каждой клетке неподвижного изображения вместе с приоритетными данными. Поскольку видеопроцессор 10 в этом варианте осуществления способен одновременно предоставлять четыре клетки неподвижного изображения, генерирующая данные неподвижного изображения схема 58 выдает данные неподвижных изображений с первых по четвертые BG1, BG2, BG3 и BG4.

Генерирующая данные подвижного изображения схема 60 включает в себя объектную аттрибутивную память OAM, которая не изображена. Объектная аттрибутивная память способна запоминать объектные данные (аттрибутивные данные), 128 таких данных общим числом. Как видно на фиг. 7, каждый набор объектных данных состоит из 34 битов, из которых: 9 битов специфицирующих объект именных данных (именные данные), 8 битов V-позиционных данных, 9 битов H-позиционных данных, 3 бита цветовых данных, 2 бита приоритетных данных, 2 бита переключательных данных и один бит выбирающих размер данных. Область символьных данных в запоминающем видеоданные устройстве 54 адресуются по именным данным и позиционным данным, входящим в объектные данные, считываемые из объектной аттрибутивной памяти OAM, и V-позиционным данным, предоставляемым генерирующей тактовые сигналы схемой 56. Запоминающее видеоданные устройство 54 предоставляет графические данные (точечные данные) и приоритетные данные символы. Таким образом, генерирующая символьные данные подвижного изображения схема 60 выдает символьные данные подвижного изображения OBJ.

Тактирующий сигнал /5M, выдаваемый генерирующей тактовые сигналы схемой 56, поступает на выбирающую основные/дополнительные данные схему 62 вместе с описанными выше символами данными подвижного изображения OBJ и символьными данными неподвижного изображения BG1-BG4. Центральное процессорное устройство 12 передает специфицирующие основное изображение данные OBJS-BG4S через интерфейс центрального процессорного устройства 16 на выбирающую основные/дополнительные данные схему 62. Выбирающая основные/дополнительные данные схема 62 определяет на основе специфицирующих основное изображение данных и специфицирующих дополнительные изображения данных, какое изображение и определяемых символами данными подвижного изображения OBJ в символами данными неподвижных изображений BG1-BG4 будет основным изображением и какое будет дополнительным изображением, и выдает основные данные и дополнительные данные поочередно в синхронизме с тактирующим сигналом 5M в режиме разделения времени.

В частности, выбирающая основные/дополнительные данные схема 62 включает в себя выбирающие вентильные схемы 64a по 64e, как иллюстрирует фиг. 8. На фиг. 8 подробно изображена лишь выбирающая вентильная схема 64a. Выбирающие вентильные схемы 64a-64e идентичны, поэтому ниже будет описана только выбирающая вентильная схема 64a, описания остальных выбирающих вентильных схем опущены.

Выбирающая вентильная схема 64a включает в себя И вентили 66, И вентиль 70, И вентиль 72 и ИЛИ вентиль 68. Каждый бит данных подвижного изображения OBJ, созданный генерирующей данные подвижного изображения схемой 60, подается на вход каждого из И вентилей 66 и выходной сигнал ИЛИ вентиля 68 подается на другой вход каждого из И вентилей 66. Выходные сигналы И вентилей 70 и 72 подаются соответственно на два входа ИЛИ вентиля 68. Специфицирующие основное изображение данные OBJM поступают через интерфейс центрального процессорного устройства 16 на один вход И вентиля 70, и тактовый сигнал 5M, генерируемый генерирующей тактовые сигналы схемой 56, поступает на другой вход И вентиля 70. Специфицирующие дополнительное изображение данные OBJS поступают через интерфейс 16 на один вход И вентиля 72, и тактовый сигнал /5M, генерируемый генерирующей тактовый сигнал схемой 56, поступает на другой вход И вентиля 72.

Поэтому, если подвижное изображение выбрано в качестве основного изображения, специфицирующие основное изображение данные OCJM устанавливаются в "1" и специфицирующие дополнительное изображение данные OBJS устанавливаются в "0", Поэтому И вентили обеспечивают данные подвижного изображения OBJ синхронно с тактовым сигналом 5M. Если подвижное изображение выбрано в качестве дополнительного изображения, то специфицирующие дополнительное изображение данные OBJS устанавливаются в "1". Поэтому И вентили 66 подают данные подвижного изображения OBJ синхронно с тактовым сигналом /5M.

Аналогично, если первое неподвижное изображение, второе неподвижное изображение, третье неподвижное изображение или четвертое неподвижное изображение выбрано в качестве основного изображения, то специфицирующие основное изображение данные BG1M, BG2M, BG3M или BG4M устанавливаются в "1". Следовательно, выбирающая вентильная схема 64b, 64c, 64d или 64e подает данные неподвижного изображения BG1, BG2, BG3 или BG4 синхронно с тактовым сигналом 5M. Если первое неподвижное изображение, второе неподвижное изображение, третье неподвижное изображение или четвертое неподвижное изображение выбрано в качестве дополнительного изображения, специфицирующие дополнительное изображение данные BG1S, BG2S, BG3S или BG4S устанавливаются в "1" и, следовательно, выбирающая вентильная схема 64b, 64c, 64d или 64e подает данные неподвижного изображения BG1, BG2, BG3 или BG4 синхронно с тактовым сигналом /5M.

Таким образом, выбирающая основные/дополнительные данные схема 62 выдает данные основного изображения и данные дополнительного изображения, когда тактирующий сигнал 5M установлен в "1" и когда тактирующий сигнал /5M установлен в "1" соответственно.

Выбирающая основные/дополнительные данные схема 62 передает данные основного изображения и данные дополнительного изображения на приоритетную схему 74.

Дополнительно данные, передаваемые на приоритетную схему 74 выбирающей основные/дополнительные данные схемой 62, включает в себя графические данные (точечные данные) и приоритетные данные. В некоторых случаях такие данные включают в себя цветовые коды (фиг. 6 и 7) и палитровые данные вместо графических данных.

Приоритетная схема 74 выдает символьные данные подвижного изображения или символьные данные неподвижного изображения в зависимости от того, каким из них приписан более высокий приоритет, когда подвижное изображение и неподвижное изображение перекрывают друг друга и сконструированы так, как иллюстрирует фиг. 9. Приоритетная схема 74 содержит опознающие прозрачность схемы 76a, 76b, 76c, 76d и 76e, которые в указанном порядке соответствуют символьным данным подвижного изображения OBJ и символьным данным неподвижных изображений BG1, BG2, BG3 и BG4. На фиг. 9 подробно изображена лишь опознающая прозрачность схема 76a. Поскольку опознающие прозрачность схемы 76a по 76e идентичны, то описана лишь опознающая прозрачность схема 76a, а описания других опознающих прозрачность схем опущены.

Опознающая прозрачность схема 76a содержит ИЛИ вентиль 78 и трехуровневые вентили 82. Каждый бит символьных данных подвижного изображения OBJ подается на каждый вход ИЛИ вентиля 78. ИЛИ вентиль 78 подает выходной сигнал на приоритетную схему 80 в качестве сигнала опознавания прозрачности. Каждый из трехуровневых вентилей 82 принимает каждый бит символьных данных подвижного изображения OBJ. Когда символ подвижного изображения прозрачен, все биты символьных данных подвижного изображения OBJ равны "0". В таком случае приоритетная схема 80 присваивает приоритеты только символьным данным, которые устанавливают выходы ИЛИ вентилей опознающих прозрачность вентилей 76a по 76e в "1". Трехуровневые вентили 82 разрешают приоритетной схеме 74 создавать одиночные композиционные видеоданные символьных данных подвижного изображения OBJ и символьных данных неподвижных изображений BG1, BG2, BG3 и BG4, которые поступают индивидуально на приоритетную схему 74. Более конкретно приоритетная схема 80 опознает данные, обладающие наивысшим приоритетом среди данных, которые выходными сигналами опознающих прозрачность схем 76a-76e устанавливаются в "1", и устанавливают идентифицирующий композиционные видеоданные сигнал в "0", чтобы вывести данные, обладающие наивысшим приоритетом. Например, если символьные данные подвижного изображения OBJ обладают наивысшим приоритетом и выходной сигнал ИЛИ вентиля 78 опознающей прозрачность схемы 80 подает идентифицирующий композиционные видеоданные сигнал /OBJSEL в виде "0" и другие идентифицирующие композиционные видеоданные сигналы /BG1SEL, /BG2SEL, /BG3SEL, BG4SEL и /BAC в виде "1". Следовательно, трехуровневые вентили 82 опознающей прозрачность схемы 76a открыты и приоритетная схема 74 выдает только символьные данные подвижного изображения OBJ.

Идентифицирующий композиционные видеоданные сигнал /BACK указывает, что ни символьные данные подвижного изображения OBJ, ни символьные данные неподвижных изображений BG1 по BG4 не выдаются. В таком случае на экране наблюдается фоновый цвет.

Как сказано выше, эти данные выводятся в качестве основных данных и дополнительных данных из выбирающей основные/дополнительные данные схемы 62 в режиме разделения времени, и таким образом приоритетная схема 74 определяет соответствующие приоритеты основных данных и дополнительных данных.

Если композиционные данные, созданные приоритетной схемой 74, включают в себя цветовые коды и палитровые данные вместо графических данных, такие данные подаются на цветовую произвольного доступа память RAM 84.

Цветовая произвольного доступа память 84 принимает 8-битовые выбирающие палитру данные через интерфейс центрального процессорного устройства 16 от центрального процессорного устройства 12 и преобразует цветовые коды и палитровые данные, предоставленные приоритетной схемой 74, в 15-битовые цветовые данные (градационные данные), состоящие из трех наборов 5-битовых цветовых данных для трех цветов. Цветовые данные представляют градации, задаваемые пятью битами для каждого цвета: красного, зеленого и синего. Таким образом, цветовые данные представляют собой набор данных из 15 битов.

Если данные, предоставленные выбирающей основные/дополнительные данные схемой 62, другими словами, композиционные данные, предоставленные приоритетной схемой 74, являются графическими данными, композиционные данные непосредственно передаются на селектор данных 86. Центральное процессорное устройство 12 подает режимный сигнал "1", означающий непосредственный режим, или режимный сигнал "0", означающий косвенный режим, на селектор данных 86. Селектор данных 86 выбирает цветовые данные из тех, которые хранятся в цветовой произвольного доступа памяти 84, если режимный сигнал равен "0", или выбирает 15-битовые цветовые данные, предоставляемые приоритетной схемой 74, если режимный сигнал равен "1".

Дополнительно основные данные и дополнительные данные выдаются на соответствующий тракт и дополнительные данные поступают на прибавляющую монохроматический цвет схему 88.

Прибавляющая монохроматический цвет схема 88 принимает также фоновые цветовые данные, предоставляемые затворами данных 36, 38 и 40 интерфейса центрального процессорного устройства 16 (фиг. 4) и складывает фоновые цветовые данные в качестве цветовых данных с порциями, лишенными дополнительных данных, или полностью заменяет дополнительные данные на фоновые цветовые данные.

Обратимся к фиг. 10, иллюстрирующему прибавляющую монохроматический цвет схему 88. 5-битовые фоновые цветовые данные соответственно для красного, зеленого и синего, передаются через интерфейс центрального процессорного устройства 16 на селектор данных 90, и 5-битовые цветовые данные соответственно для красного, зеленого и синего подаются через затворную схему 92 на селектор данных 90 селектором данных 86 (фиг. 1). Затворная схема 92 содержит D-триггеры и запирает цветовые данные, подаваемые селектором данных 86, в ответ на тактовый сигнал /10M. Идентифицирующий композиционные видеоданные сигнал /BACK от приоритетной схемы 74 и тактовый сигнал /10M подаются на D-триггер 94. D-триггер 94 служит для регулирования времени. D-триггер 94 запирает идентифицирующий композиционные видеоданные сигнал /BACK, подаваемый приоритетной схемой 74, в ответ на тактовый сигнал /10M. Сигнал с выхода Q D-триггера 94 поступает через НЕ-ИЛИ вентиль 96 на вход "выбрать сигнал" селектора данных 90, и выходной сигнал /Q D-триггера поступает на один вход ИЛИ вентиля 98. Сигнал SCADD, подаваемый через интерфейс центрального процессорного устройства 16 центральным процессорным устройством 12, инвертируется инвертором и затем поступает на другой вход ИЛИ вентиля 98. Если сигнал SCADD равен "0", выходной сигнал НЕ-ИЛИ вентиля 96 равен "0", и поэтому селектор данных 90 выбирает фоновые цветовые данные. Если сигнал SCADD равен "1", сигнал на выходе НЕ-ИЛИ вентиля 96 зависит от значения сигнала /BACK. Как сказано выше, сигнал /BACK указывает, что нет изобразительных данных, и он подается в качестве дополнительных данных в подходящее время на НЕ-ИЛИ вентиль 96 D-триггером 94. Соответственно селектор данных 90 выбирает фоновые цветовые данные, если дополнительные данные не содержат каких-либо изобразительных данных, и он же выбирает цветовые данные, если дополнительные данные содержат какие-либо изобразительные данные.

Таким образом, прибавляющая монохроматический цвет схема 88 выдает фоновые цветовые данные в качестве дополнительных данных, если нет изобразительных данных. В таком случае ИЛИ вентиль 98 подает сигнал SBCK, указывающий, что фоновые цветовые данные выбраны в качестве дополнительных данных.

Дополнительные данные, поставляемые прибавляющей монохроматический цвет схемой 88, подаются на управляющую дополнительными данными схему 100, и основные данные, подаваемые селектором данных 86, передаются на управляющую основными данными схему 102.

Генерирующая сигнал дисплейного интервала схема 104 описана ниже. Генерирующая сигнал дисплейного интервала схема 104 создает сигнал интервала цветового окна CW, специфицирующий интервал цветового окна на экране растрового развертывающего монитора 18. Как показано в деталях на фиг. 11, генерирующая сигнал дисплейного интервала схема 104 содержит счетчик 106. Тактовый сигнал 5M, генерируемый генерирующей тактовый сигнал схемой 56, подается на тактовый (счетный) вход счетчика 106. Показание счетчика 106 обновляется для каждой точки на экране растрового развертывающего монитора 18. Тактовый сигнал WCLD, генерируемый генерирующей тактовый сигнал схемой 56, поступает на вход "сброс" счетчика 106. Соответственно показание счетчика 106 увеличивается (на единицу) тактовым сигналом 5M в начале каждой горизонтальной развертки.

Выходной сигнал счетчика 106 поступает на первую оконную схему 108a и вторую оконную схему 108b. На фиг. 11 подробно показана лишь первая оконная схема 108a. Поскольку первая оконная схема 108a и вторая оконная схема 108b идентичны по конструкции, ниже будет описана лишь первая оконная схема 108a.

Первая оконная схема 108a имеет две опознающих совпадения схемы 110 и 112. Выходной сигнал счетчика 106 поступает на один вход каждой из опознающих совпадение схем 110 и 112. Левой крайней позиции первого окна данные WAP1, подаваемые затвором данных 28 интерфейса центрального процессорного устройства 16, поступают на другой вход опознающей совпадения схемы 110, и правой крайней позиции первого окна данные WAP2, подаваемые затвором данных 30 интерфейса центрального процессорного устройства 16, поступают на другой вход опознающей совпадения схемы 112. Опознающая совпадения схема 110 сравнивает левой крайней позиции данные WAP1 и показание счетчика 106 и дает сигнал "установить" на RS-триггер 114 при их совпадении. Аналогично опознающая совпадения схема 112 сравнивает показание счетчика 106 и правой крайней позиции данные WAP2 и затем дает сигнал "установить" на RS-триггер 116 при их совпадении. Поскольку RS-триггер 114 и RS-триггер 116, как и счетчик 106 обнуляются сигналом WCLD, на выходах Q RS-триггера 114 и RS-триггера 116 устанавливаются "1", когда на них поступает сигнал "установить". Однако, поскольку RS-триггер 116 подает сигнал /Q, на выходе RS-триггера 116 устанавливается "0", когда на него поступает сигнал "установить".

Выходной сигнал Q RS-триггера 114 и инвертированный сигнал Q RS-триггера 116 поступают на входы И вентиля 118. Поэтому И вентиль 118 имеет на выходе "1" на временном интервале между моментом, соответствующим левой крайней позиции первого окна, и моментом, соответствующим правой крайней позиции, при каждой горизонтальной развертке. Выходной сигнал И вентиля 118 поступает на один вход Исключающее ИЛИ вентиля 120, и специфицирующий внутренность/наружность первого окна сигнал WAIO, приходящий через интерфейс центрального процессорного устройства 16, подается на другой вход Исключающее ИЛИ вентиля 120. Исключающее ИЛИ вентиль 120 инвертирует выходной сигнал И вентиля 118, когда сигнал WAIO равен "1", и подает его на один вход ИЛИ вентиля 122. Разрешающий первое окно сигнал WAEN, приходящий через интерфейс центрального процессорного устройства 16, инвертируется инвертором и подается на другой вход ИЛИ вентиля 122. ИЛИ вентиль 122 выдает "1" на временном интервале, когда на выходе И вентиля 118 имеется "1", в то время как сигнал WAEN равен "1".

Аналогично ИЛИ вентиль второй оконной схемы 108b создает выходной сигнал ИЛИ вентиля. ИЛИ-вентильные выходные сигналы первой оконной схемы 108a и второй оконной схемы 108b поступают на ИЛИ вентиль 124, И вентиль 126, Исключающее ИЛИ вентиль 128 и Исключающее НЕ-ИЛИ вентиль 130 в качестве двух входных сигналов соответственно. Выходные сигналы вентилей 124-130 подаются на мультиплексор 132.

Сигналы WAEN и WBEN, приходящие через интерфейс центрального процессорного устройства 16, поступают на входы И вентиля 134, и выходной сигнал И вентиля 134 поступает на один вход каждого из И вентилей 136 и 138. Управляющий сигнал WLS1, поступающий через интерфейс центрального процессорного устройства 16, подается на другой вход И вентиля 136, и управляющий сигнал WLS2 подается на другой вход И вентиля 138. Выходные сигналы И вентилей 136 и 138 подаются в качестве сигналов "выбрать" A и B соответственно на мультиплексор 132.

Мультиплексор 132 выбирает один из четырех входных сигналов, поданных вентилями 124-130, в соответствии с сигналами "выбрать" A и B и выдает выбранный сигнал в качестве сигнала оконного интервала CW.

Когда используется лишь первое или второе окно, сигнал WAEN или WBEN, поступающий через интерфейс центрального процессорного устройства 16, устанавливается в "1". В этом случае на выходе И вентиля 134 устанавливается "0". Следовательно, выходные сигналы И вентилей 136 и 138 устанавливается в "0", и поэтому мультиплексор 132 выбирает выходной сигнал ИЛИ вентиля 124 в качестве сигнала цветного оконного интервала CW. При разрешении только первого окна WA сигнал интервала цветового окна CW устанавливается в "1" для заштрихованной площади на фиг. 12A, когда первый специфицирующий внутренность/наружность сигнал WAIO установлен в "1", или заштрихованной площади на фиг. 12B установлен в "1", когда специфицирующий внутренность/наружность первого окна сигнал WAIO установлен в "0". При разрешении только второго окна WB сигнал интервала цветового окна CW устанавливается в "1" для заштрихованной площади на фиг. 13A, когда второй специфицирующий внутренность/наружность сигнал WBIO равен "1", или сигнал интервала цветового окна CW устанавливается в "1" для заштрихованной площади на фиг. 13B, когда второй специфицирующий внутренность/наружность сигнал WBIO равен "0".

Если сигналы WAEN и WBEN одновременно установлены в "1", то мультиплексор 132 выбирает сигнал с выхода И вентиля 126, выхода Исключающее ИЛИ вентиля 128 или выхода Исключающее НЕ-ИЛИ вентиля 130 в качестве сигнала интервала цветового окна CW в соответствии с управляющими сигналами WLS1 и WLS2. В этом случае оба специфицирующих внутренность/наружность сигнала WAIO и WBIO устанавливаются в "1". Если оба управляющих сигнала WLS1 и WLS2 установлены в "0", то мультиплексор 132 выбирает сигнал с выхода И вентиля 126. В этом случае сигнал интервала цветового окна CW для заштрихованной площади на фиг. 14 устанавливается в "1". Если управляющий сигнал WLS1 устанавливается в "0" и управляющий сигнал WLS2 установлен в "1", то мультиплексор 132 выбирает выходной сигнал Исключающее ИЛИ вентиля 128. В этом случае сигнал интервала цветового окна CW устанавливается в "1" для заштрихованной площади на фиг. 15. Если оба управляющих сигнала WLS1 и WLS2 установлены в "1", то мультиплексор 132 выбирает выходной сигнал Исключающее НЕ-ИЛИ вентиля 130. В этом случае сигнал интервала цветового окна CW устанавливается в "1" для заштрихованной площади на фиг. 16.

Предварительно надо отметить, что арифметическая схема, которая будет описана ниже, выполняет предопределенную арифметическую операцию в соответствии с командами, подаваемыми операционным управлением, только в течение периода времени, когда сигнал интервала цветового окна CW равен "1".

На фиг. 17 изображена управляющая операциями схема 140. Центральное процессорное устройство 12 считывает данные ASW1 и ASW0, BSW1 и BSW0 из запоминающего программы устройства 14 и посылает их наружу через интерфейс центрального процессорного устройства 16. Данные или сигналы ASW0, 1 и BSW0, 1 являются сигналами, определяющими, как сигнал интервала цветового окна CW, подаваемый генерирующей дисплейного интервала сигнал схемой 104, должен быть использован при исполнении арифметической операции арифметическим устройством 190. Если оба сигнала ASW0 и ASW1 установлены в "0", то НЕ-ИЛИ вентиль 142 подает выходной сигнал "1" на ИЛИ вентиль 144. Соответственно сигнал MAINAREA становится "1" и подается на описанную выше управляющую основными данными схему 102 и на один вход И вентиля 146.

Если оба сигнала ASW0 и ASW1 установлены в "1", то на выходе НЕ-ИЛИ вентиля 142 устанавливается "0". Поскольку сигнал ASW0 поступает после инвертирования на И вентиль 148, выходной сигнал И вентиля 148 становится "0". Поскольку сигнал ASW1 поступает после инвертирования на И вентиль 150, то выходным сигналом И вентиля 150 также становится "0", и поэтому выходной сигнал ИЛИ вентиля 144 становится "0". Выход ИЛИ вентиля 144 становится независимым от сигнала интервала цветного изображения CW.

Если сигнал ASW0 равен "0" и сигнал ASW1 равен "0", то на выходе НЕ-ИЛИ вентиля 142 будет "0" и на выходе И вентиля 150 будет "0". Затем И вентиль 148 выдает сигнал интервала цветного изображения CW в том виде, в каком он есть. Сигнал интервала цветового изображения CW проходит через ИЛИ вентиль 144 и далее используется как сигнал MAINAREA (основная область).

Если сигнал ASW0 равен "0" и сигнал ASW1 равен "1", то или вентиль 144 подает инвертированный сигнал интервала цветного изображения CW, проходящий через И вентиль 150.

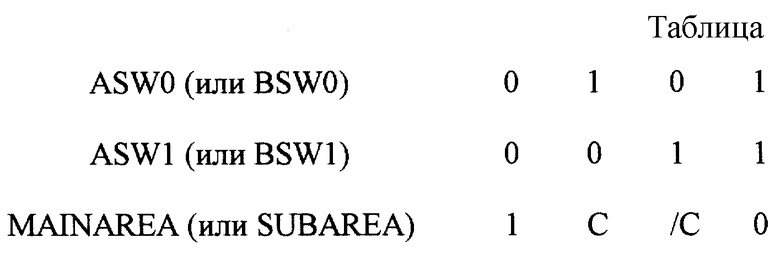

Вентили 152-158 работают аналогично вентилю 142-150 применительно к сигналам BSW0 и BSW1. Поэтому соответствующие состояния сигналов MAINAREA и SUBAREA, подаваемых ИЛИ вентилями 144 и 154, можно представить в таблице.

Управляющая операциями схема 140 имеет шесть И вентилей 160, 162, 164, 166, 168 и 170. Сигнал /OBJSEL, подаваемый приоритетной схемой 74, и данные ADNOBJ, подаваемые через интерфейс центрального процессорного устройства 16, поступают на два входа И вентиля 160. Аналогично сигнал /BG1SEL и данные ADNBG1 поступают на два входа И вентиля 162. Сигнал /BG2SEL и данные ADNBG2 поступают на два входа И вентиля 164. Сигнал /BG3SEL и данные ADNBG3 поступают на И вентиль 166. Сигнал /BG4SEL и данные ADNBG4 поступают на И вентиль 168. Сигнал /BACK и данные ADNBACK поступают на И вентиль 170. Соответственно каждый из вентилей 160-170 подает сигнал команды сложения, когда оба сигнала, поступившие на его входы, равны "1". Сигналы команды сложения, подаваемые И вентилями 160-170, передаются через ИЛИ вентиль 172 на управляющую дополнительными данными схему 100 и на вход И вентиля 146.

Также поступает на вход И вентиля 146 сигнал /SBCK, подаваемый прибавляющей монохроматический цвет схемой 88. Выходной сигнал И вентиля 146 и данные HLFEN, подаваемые через интерфейс центрального процессорного устройства 16, поступают на входы И вентиля 174. Затем И вентиль 174 подает сигнал "1" только в том случае, когда сигнал команды сложения подан и оба сигнала MAINAREA и SUBAREA равны "1". Выходной сигнал И вентиля 174 подается на D-триггер 176. Тактирующий сигнал /5M, создаваемый генерирующей тактовый сигнал схемой 56, поступает на счетный вход D-триггера 176. Выходной сигнал HLFCNT D-триггера 176 поступает на арифметическое устройство (которое описано ниже).

Как видно на фиг. 18, описанная выше управляющая дополнительными данными схема 100 имеет 8-входовой И вентиль. Сигналы SUBEN, HVFIELD и SUBAREA поступают на входы И вентиля 178. Сигналы SUBEN и SUBAREA создаются описанной выше управляющей операционной схемой 140. Сигнал HVFIELD создается генерирующей тактовый сигнал схемой 56 и остается равным "1" на временном интервале, когда растровый развертывающий монитор 18 выполняет дисплейную операцию. Выходной сигнал И вентиля 178 поступает на один вход прибавляющей монохроматический цвет схемой 88, подается на другой вход каждого из И вентилей 180. Цветовые данные от прибавляющей монохроматический цвет схемы 88 передаются регистру дополнительных данных 182 (фиг. 1) только в том случае, если все сигналы SUBEN, SUBAREA и HVFIELD равны "1".

При обработке предопределенных видеоданных основных данных в сочетании с дополнительными данными, например, когда символьные данные подвижного изображения OBJ и символьные данные неподвижных изображений BG1 указаны в качестве основных данных и только символьные данные неподвижного изображения BG1 надлежит обрабатывать в комбинации с дополнительными данными, сигнал SUBEN устанавливается в "1", если основными данными являются символьные данные неподвижного изображения BG1, и дополнительные данные поступают на регистр дополнительных данных 182.

В случае, когда основные данные и дополнительные данные обрабатываются лишь в некоторой конкретной площади экрана растрового развертывающего монитора 18 заданной предшествующей оконной маскирующей функцией, сигнал SUBAREA равен "1" только для этой конкретной площади.

Управляющая основными данными схема, изображенная на фиг. 19, имеет 2-входовой И вентиль 184. Описанные выше сигналы HVFIELD и MAINAREA поступают на входы И вентиля 184. Сигнал MAINAREA равен "1" для конкретной площади экрана растрового развертывающего монитора 18, и сигнал HVFIELD равен "1" все время, пока растровый развертывающий монитор 18 находится в дисплейном режиме. Выходной сигнал И вентиля 184 поступает на один вход каждого из И вентилей 186, и каждый бит основных данных поступает на другой вход каждого из И вентилей 186. Основные данные поступают на регистр основных данных 188 (фиг. 1) только для конкретной площади на экране растрового развертывающего монитора 18 все время, пока растровый развертывающий монитор 18 находится в дисплейном режиме.

Как видно на фиг. 20, арифметическое устройство 190 включает в себя R арифметическую схему 192a, G арифметическую схему 192b и B арифметическую схему 192c, предназначенные соответственно красному, зеленому и синему цветам. На фиг. 20 подробно изображена лишь R арифметическая схема 192a. Поскольку арифметические схемы 192a, 192b и 192c идентичны по конструкции, то ниже дано описание только R арифметической схемы 192a, а описания остальных схем опущены.

R арифметическая схема 192a имеет сумматор 194. Сумматор 194 имеет вход A, который принимает 5-битовые градационные данные для красного цвета, поступающие от регистра основных данных 188, и вход B, который принимает выходной сигнал дополнительной схемы 196. Дополнительная схема 196 принимает дополнительные данные для красного цвета от регистра дополнительных данных 182. Дополнительная схема 196

включает в себя пять Исключающее ИЛИ вентилей 198, соответствующих пятибитовым дополнительным данным. Каждый бит дополнительных данных поступает на один вход каждого из Исключающее ИЛИ вентилей 198, и данные ADDSUB, поступающие через интерфейс центрального процессорного устройства 16, подаются на другой вход каждого их Исключающее ИЛИ вентилей 198. Дополнительная схема 196 дает данные, поступающие от дополнительного регистра 182, сумматору 194 в том виде, как они есть, если данные ADDSUB равны "0", и подает "дополнение до двух" на сумматор 194, если данные ADDSUB равны "1". Соответственно сумматор 194 суммирует основные данные и дополнительные данные, если данные ADDSUB равны "0", и вычитает дополнительные данные из основных данных, если данные ADDSUB равны "1".

Выходной сигнал сумматора 194 подается на вентильную схему 200, которая включает в себя пять И вентилей 202, соответствующих битам пяти битов выхода сумматора 194. Каждый бит выходного сигнала сумматора 194 поступает на один вход каждого из И вентилей 202, и выходной сигнал ИЛИ вентиля 204 поступает на другой вход каждого из И вентилей 202. Данные ADDSUB поступают через инвертор на один вход ИЛИ вентиля 204, и сигнал переноса CO, подаваемый сумматором 194, поступает на другой вход ИЛИ вентиля 204. Соответственно выходы всех И вентилей 202 являются "0", если данные ADDSUB являются "0", а именно, когда результат вычитания в сумматоре оказывается отрицательным.

Выходной сигнал вентильной схемы 200 поступает на другую вентильную схему 206, которая включает в себя пять ИЛИ вентилей 208 и И вентиль 210. Каждый бит выходного сигнала вентильной схемы 200 поступает на один вход каждого из ИЛИ вентилей 208, и выходной сигнал И вентиля 210 поступает на другой вход каждого из ИЛИ вентилей 208. И вентиль 210 принимает сигнал переноса CO, подаваемый сумматором 194, данные ADDSUB через инвертор и сигнал HLFCNT, подаваемый управляющей операциями схемой 140 через инвертор. Соответственно вентильная схема устанавливает все биты в "1" в согласии с выходным сигналом И вентиля 210, когда в результате сложения появляется признак переполнения сумматора 194.

Выходной сигнал вентильной схемы 206 поступает на однобитовую сдвиговую схему 212. Однобитовая сдвиговая схема 212 сдвигает данные, принимаемые от вентильной схемы 206, на один бит в ответ на выходной сигнал И вентиля 214, когда управляющая операциями схема 140 подает сигнал HLFCNT. И вентиль 214 принимает сигнал переноса CO от сумматора 194 и данные ADDSUB через инвертор. И вентиль 214 подает сигнал "1", когда сумматор 194 переполняется. Соответственно однобитовая сдвиговая схема 212 прибавляет "1", поступающую от И вентиля 214, к старшему биту для создания максимального значения Rmax при вычислении среднего значения в соответствии с выходным сигналом HLFCNT управляющей операциями схемы 140, поскольку максимальное значение Rmax нельзя получить, если сдвинуть данные на один бит для вычисления среднего значения, когда сумматор 194 переполнен.

Таким образом однобитовая сдвигающая схема 212 подает пять старших битов для вычисления среднего значения и подает пять младших битов в других случаях.

Выходной сигнал однобитовой сдвиговой схемы 212 поступает на создающую видеосигнал схему 216. Создающая видеосигнал схема 216 принимает синхронизирующие сигналы Hsync и Vsync от генерирующей тактовые сигналы схемы 56. Создающая видеосигнал схема 216 преобразует градационные данные о красном, зеленом и синем цветах, поступающие от арифметической схемы 190, в полный телевизионный видеосигнал, включающий в себя RGB (красный-зеленый-синий) сигнал и синхронизирующий сигнал известным способом, и передает его растровому развертывающему монитору 18.

Дополнительно запоминающая кассета, содержащая полупроводниковую память, используется как внешнее запоминающее устройство в описанных выше вариантах осуществления; однако возможно в настоящем изобретении использовать внешнее запоминающее устройство, подобное CD-ROM. В случае использования запоминающей кассеты программные данные, включающие в себя символьные данные символов подвижного изображения и символы неподвижных изображений, и названные выше цветовые арифметические программные данные хранятся в полупроводниковой памяти, и центральное процессорное устройство 12 генерирует управляющие данные для символов подвижного изображения и символов неподвижного (фонового) изображения на основе программных данных, считываемых из полупроводниковой памяти, и выдает их на компоненты видеопроцессора 10.

Альтернативно в случае использования CD-ROM (постоянной памяти) описанные выше программные данные и цветовые арифметические программные данные оптически записываются в виде цифровых данных в постоянную память CD-ROM (не показана). Дополнительно оптический считыватель для оптического считывания записанных на CD-ROM данных соединен с подходящим разъемом, подобным удлиняющему разъему. Даже если CD-ROM используется в качестве внешнего запоминающего устройства, все равно используется запоминающая кассета. В этом случае запоминающая кассета оснащается ROM постоянной памятью (не изображена), которая хранит запускающую программу для управления работой оптического считывателя, буферную память произвольного доступа RAM (не изображена) и т. д. Далее перед началом дисплейной операции центральное процессорное устройство посылает управляющие данные на оптический считыватель на основе программы пуска ROM постоянной памяти, чтобы заставить оптический считыватель считывать записанные на CD-ROM памяти данные. Часть символьных данных, считываемых с CD-ROM памяти, передается на символьную память произвольного доступа, встроенную в запоминающую кассету. Центральное процессорное устройство 12 управляет компонентами видеопроцессора 10 на основе программных данных, хранящихся в буферной памяти произвольного доступа RAM. Это означает, что после того, как данные, считанные из CD-ROM (постоянной памяти) оптическим считывателем, пересланы на соответствующие запоминающие устройства, центральное процессорное устройство 12 и видеопроцессор 10 выполняют дисплейную операцию путем доступа соответствующих запоминающих устройств, как это делается в описанных выше вариантах осуществления.

Хотя настоящее изобретение подробно описано и проиллюстрировано, должно быть ясно, что это сделано лишь в иллюстративных целях и не должно восприниматься как ограничение, поскольку существо и объем настоящего изобретения определяются приложенной формулой.

Изобретение относится к обработке изображений. Его использование в телевизионном игровом устройстве позволяет достичь технический результат в виде недорогого устройства, позволяющего отображать структуры из множества изображений, в том числе прозрачных объектов. Обрабатывающее изображение устройство содержит средство генерирования данных изображения для неподвижного изображения, средство генерирования данных изображения для изображения, отличного от неподвижного изображения, и средство генерирования видеосигнала. Технический результат достигается благодаря введению средства генерирования данных предела для генерации данных положения правого края окна и данных положения левого края окна, средства изменения данных положения, выполненного с возможностью изменять окно на экране в произвольную форму, средства выполнения арифметической операции, средства определения функции арифметической операции, причем средство генерирования видеосигнала выполнено с возможностью преобразования в видеосигнал цветовых данных из средства выполнения арифметической операции. 2 с. и 7 з.п.ф-лы, 20 ил., 1 табл.

| US 4824106 A, 25.04.1989 | |||

| Устройство для отображения графической информации на экране телевизионного индикатора | 1988 |

|

SU1575231A1 |

| US 4317114 A, 23.02.1982 | |||

| ОКНО С РАМОЙ ИЗ ШТАМПОВАННЫХ ПРОФИЛЬНЫХ ЭЛЕМЕНТОВ | 1994 |

|

RU2100556C1 |

| УСТРОЙСТВО для РАСЧИСТКИ ВЫРУБОК | 0 |

|

SU268070A1 |

| УСТРОЙСТВО для ИЗГОТОВЛЕНИЯ СТЕРЖНЕЙ НАКОНЕЧНИКОВ ФИЛЬТРОВ ДЛЯ СИГАРЕТ | 0 |

|

SU277657A1 |

Авторы

Даты

2001-02-27—Публикация

1991-11-15—Подача