Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для решения задач при формировании архитектуры информационно-вычислительных и управляющих сетей.

Известно устройство для "Сопряжения процессоров и однородной вычислительной системе" (а. с. N 1273940, 1986 г. Бюл. N 44), позволяющее сформировать гибкую систему вычислительной сети.

Известно также "Коммутационное устройство" (а.с. N 1246109, 1986 г. Бюл. N 27), позволяющее создать коммутационную сеть процессорных элементов.

В качестве прототипа выбрано "Устройство коммутации процессоров" (а.с. N 1300488, 1987 г. Бюл. N 12), которое позволяет формировать архитектуру сетей. Из одного локального вычислительного кольца в другое, за счет возможности объединения этих колец в одно. С помощью данного устройства последовательно объединяются два смежных локальных кольца в одно. По объединенному сформированному основному кольцу передают адресату информационное сообщение.

Поставлена задача о расширении функциональных возможностей коммутационной сети, упрощении аппаратной поддержку, а также увеличении скорости передачи информации из одного локального вычислительного кольца в другое.

Изобретение позволит повысить скорость перестраиваемой коммутационной среды. Предлагаемое устройство позволит значительно снизить аппаратные средства, что ведет к упрощению комбинационной схемы устройства.

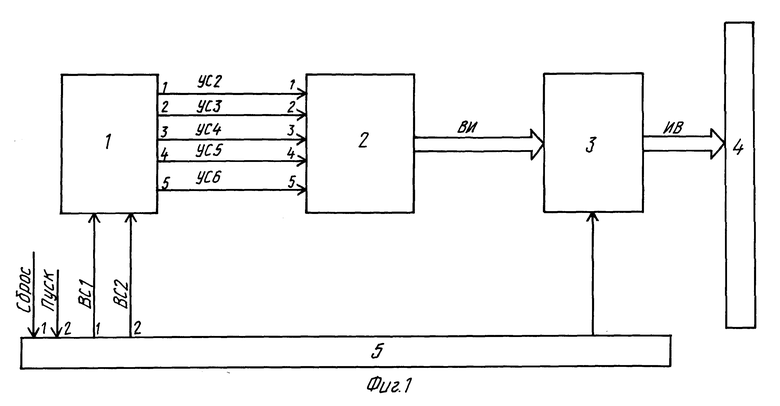

Решение задачи осуществляется тем, что в устройство, содержащее дешифратор, коммутатор, дополнительно введены блок процессоров и системы ключей, блок ключей, блок выходного канала и блок управления, причем первый и второй управляющие выходы блока управления соединены соответственно с первым и вторым управляющими входами блока дешифратора, первый по пятый управляющие входы которого соединены соответственно с первым по пятый управляющими входами блока процессоров и системы ключей, информационный выход которого соединен с информационным входом блока системы ключей, управляющий вход которого соединен с третьим управляющим выходом блока управления, информационный выход блока системы ключей соединен с информационным входом блока выходного канала. Первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами устройства.

В предлагаемом устройстве роль коммутаторов играют электронные ключи.

Если на вход такого ключа подан логический нуль, т.е. запирающий сигнал, то при этом происходит прерывание информации от источника (процессора) к приемнику (процессора, на вход которого поступает информация с выхода источника). Тем самым можно организовать гибкую систему коммутации. Если на вход ключа подана логическая единица, т.е. отпирающий сигнал, то при этом происходит соединение источника с приемником (входная информация с одного процессора поступает в этом случае на вход другого процессора - приемника). Так, с помощью подачи отпирающих и запирающих сигналов на вход ключей происходит организация коммутационной сети.

Блок ДШ дешифратор служит для определения формата работы коммутирующей системы всего устройства. В этом блоке формируются управляющие сигналы, которые определяют работу всей системы.

Блок ПСК процессоров и системы ключей служит для проведения процесса вычислений, а также для формирования формата работы коммутирующей системы устройства.

Блок СК системы ключей служит для коммутации выходной информации блока процессоров и системы ключей с выходным каналом устройства.

Блок ВК - входной канал устройства.

Отличительной особенностью многопроцессорных систем с программируемой архитектурой является простота программирования и распараллеливания задач. Однотипность МП, однородность распределенной памяти и коммутационной структуры, являющихся основой многопроцессорных систем с программируемой архитектурой, требует небольшого числа типов БИС, необходимых для синтеза. В результате достигаются высокая технологичность, надежность и ремонтноспособность подобных систем, а также возможность их неограниченного наращивания.

Это делает многопроцессорные системы с программируемой архитектурой параллельными в системах управления сложными объектами, при решении сложных задач, требующих параллельной переработки колоссальных потоков информации, при работе сложных задач [1].

Многопроцессорные системы, ориентированные на достижение сверхбольших скоростей работы, содержат десятки или сотни сравнительно простых (элементарных) процессоров с упрощенными блоками управления. Отказ от универсальности применения таких ВС и специализация их на определенном, достаточно широком круге задач, допускающих эффективное распараллеливание вычислений, позволяют строить их с регулярной структурой связей между процессорами [2].

На фиг. 1 изображена структурная схема коммутирующей системы;

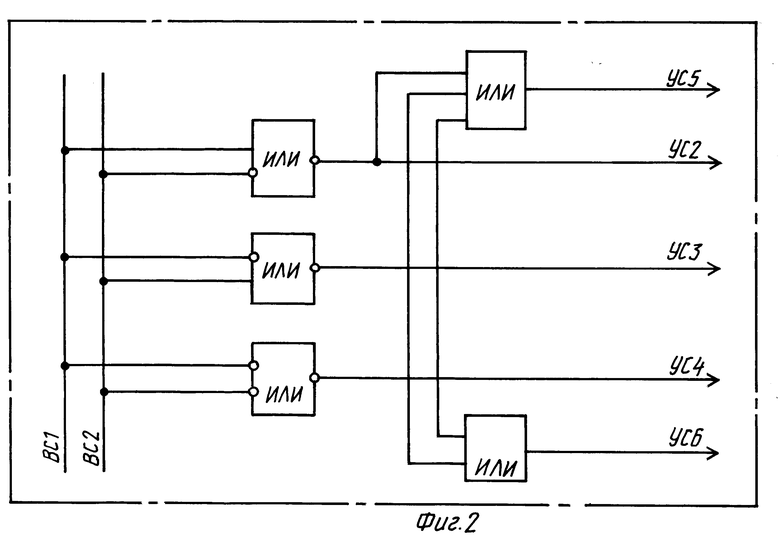

На фиг. 2 представлен вариант технической реализации блока дешифратора;

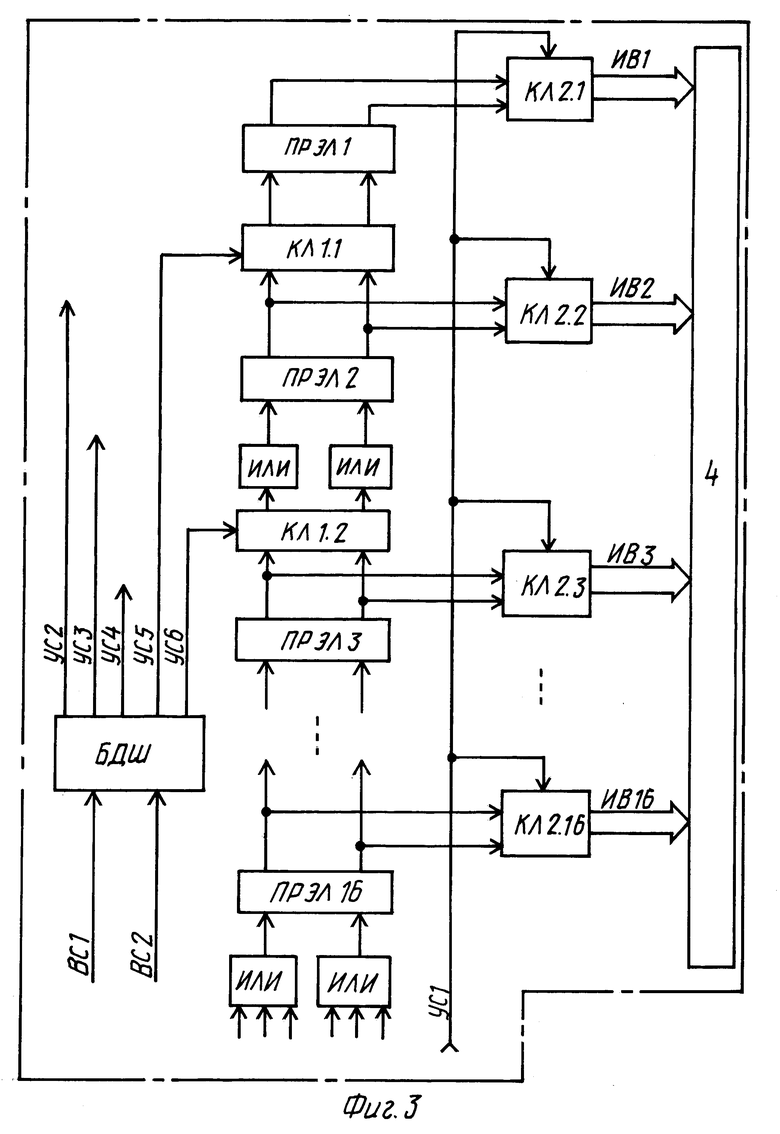

на фиг. 3 представлен вариант технической реализации коммутирующей системы, работающей в независимом режиме 1.

на фиг. 4 представлен вариант технической реализации коммутирующей системы, работающей в режиме 2, при котором организуются группы процессорных элементов, соединенных по 2. В режиме все процессорные элементы (всего 16) разбиваются на 8 групп. В каждой группе по 2 процессорных элемента. Группы работают независимо друг от друга. По сигналу из блока дешифратора вся выходная информация каждой группы через блок систему ключей поступает в выходной канал устройства).

На фиг. 5 представлен вариант технической реализации коммутирующей системы, работающей в режиме 3, при котором организуются группы процессорных элементов, соединенных по 4 процессорных элемента в каждой;

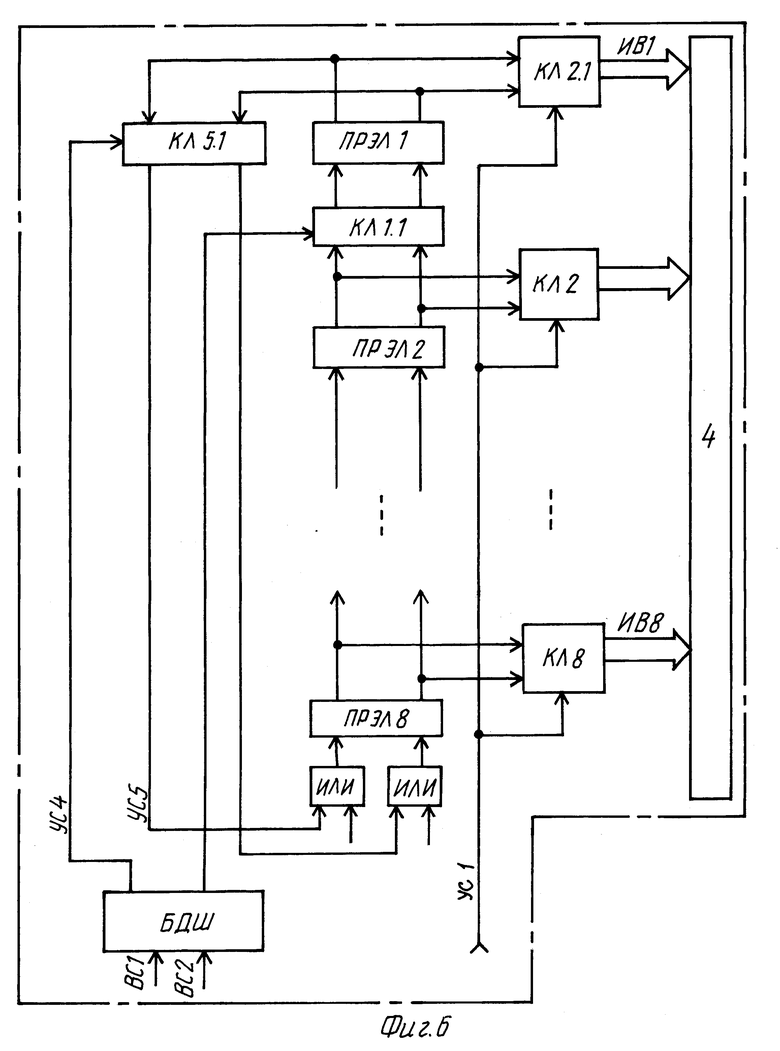

на фиг. 6 представлен вариант технической реализации коммутирующей системы, работающей в режиме 4, при котором организуются группы процессорных элементов, соединенных по 8 процессорных элемента в каждой;

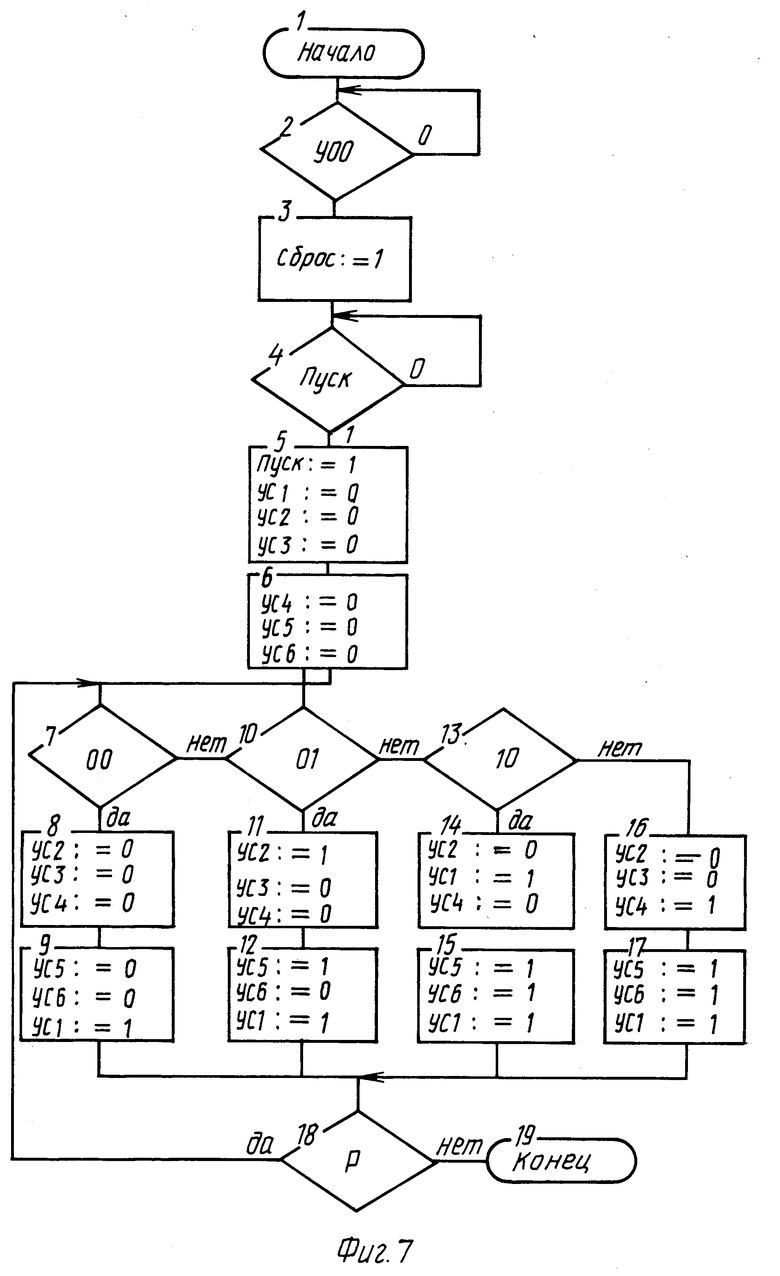

на фиг. 7 - содержательная ГСА работы устройства;

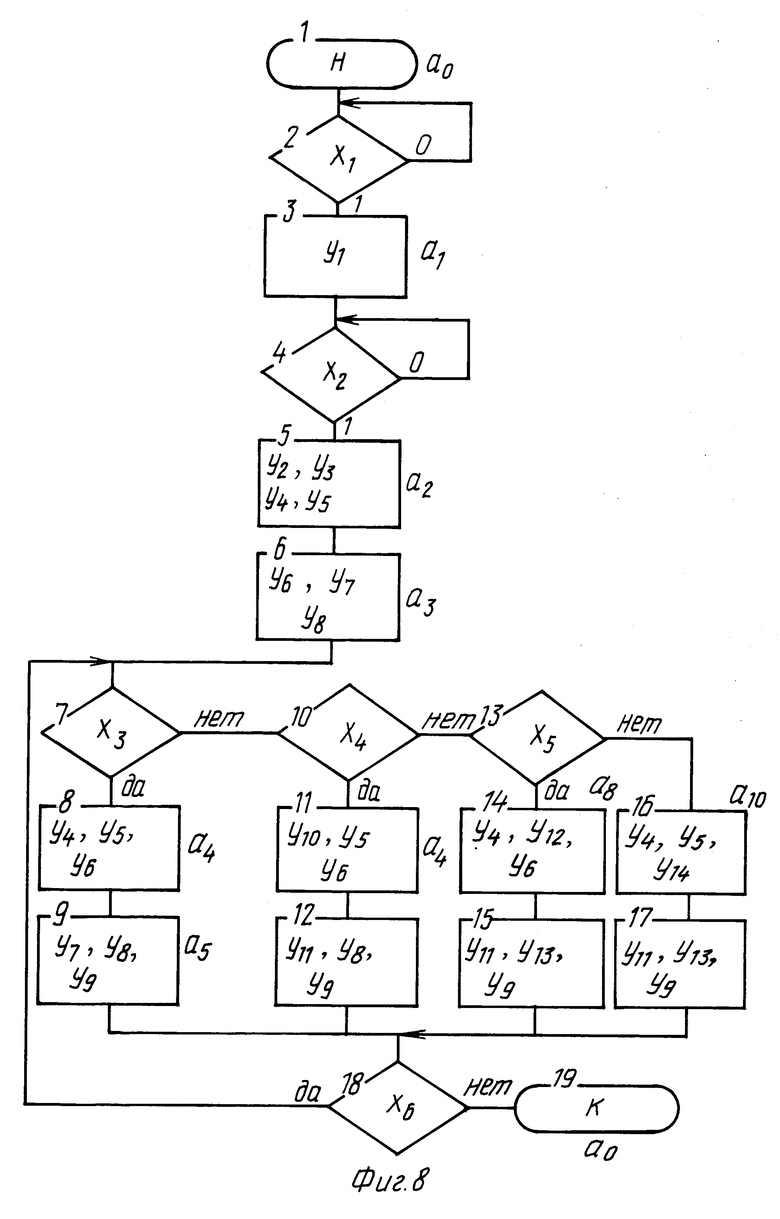

на фиг. 8 - размеченная ГСА работы устройства.

Система коммутации процессорных элементов (фиг. 1) содержит блок 1 дешифратор, блок 2 процессоров и системы ключей, блок 3 систему ключей, блок 4, выходной канал устройства, блок 5 управления.

С появлением микропроцессоров (МП) проблема многопроцессорных вычислительных систем приобрела большую актуальность и выдвинулась на первый план.

Казалось, что создание МП позволит легко решить проблему синтеза многопроцессорных систем и обеспечит реализацию параллельных методов переработки информации. Однако многочисленные попытки синтезировать многопроцессорные структуры из разработанных и выпускаемых в настоящее время промышленностью МП натолкнулись на серьезные трудности.

Современные МП являются медленно действующими. Обмен информации между МП в многопроцессорной системе оказывается затруднительным, а работа МП является недостаточно согласованной, так как в них используется машинный язык низкого уровня.

В результате многочисленных исследований были разработаны широко ныне известные многопроцессорные системы, в том числе магистральные, конвейерные, векторные, кольцевые, матричные, звездные, иерархические, ассоциативные, рекурсивные, модульные с перестраиваемой структурой.

К недостаткам многопроцессорных систем относятся жесткость, неизменность каналов связей, трудности распределения частей задач между параллельно работающими МП, трудности обмена информацией между МП, между МП и памятью, сложность и неэффективность внутренних систем коммутации, наличие узких каналов в системах обмена информацией.

Большое внимание уделяется проблемам коммутации, вопросам управления МП, памятью и внутрисистемными каналами связи, разработка простых, надежных и эффективных коммутационных структур. С целью устранения этих недостатков разработаны многопроцессорные вычислительные системы с гибкой программируемой архитектурой, в которых каналы связи между МП образуются путем их программирования в специальной коммутационной структуре.

Важнейшей составной частью многопроцессорной системы с программируемой архитектурой является универсальная коммутационная структура. Универсальные коммутационные структуры состоят из однотипных, соединенных друг с другом регулярным образом, автоматических коммутационных ячеек, которые характеризуются коллективным поведением. Такие коммутационные структуры позволяют образовывать любые многочисленные каналы связи между МП в многопроцессорных вычислительных системах. Настройка указанных каналов связи осуществляется путем программирования коммутационной структуры, в результате чего электронные каналы связи образуются автоматически. Каналы связи могут перестраиваться в процессе работы многопроцессорной системы с программируемой архитектурой [1].

Одним из способов построения многопроцессорных вычислительных систем универсального назначения является использование быстродействующего коммутатора межмодульных связей.

Коммутатор, приобретающий в таких системах характер центрального устройства, обеспечивает возможность установления связи любого процессора с любым модулем и любым модулем управления вводом-выводом, а также любого модуля управления вводом-выводом с любым модулем памяти.

Коммутатор образует межмодульные связи путем установления межсоединений в соответствующих точках пересечения прямоугольной сетки шин. Соединения между модулями сохраняются на все время передачи данных. При наличии коммутатора существенно уменьшается число конфликтов в системе, так как сам коммутатор не порождает конфликтов [2].

Для описания алгоритма работы блока 4 управления используются следующие идентификаторы.

1. ПУСК - команда запуска устройства.

2. СБРОС - команда сброса работы устройства.

3. ВС1 - входной сигнал 1, код этого сигнала формирует работу коммутирующей системы.

4. ВС2 - входной сигнал 2, код этого сигнала формирует работу коммутирующей системы.

5. УС1 - управляющий сигнал 1, который управляет работой блока 3 системы ключей.

6. УС2 - управляющий сигнал 2, поступающий на управляющие входы ключей блока процессоров и системы ключей.

7. УС3 - управляющий сигнал 3, поступающий на управляющие входы ключей блока процессоров и системы ключей.

8. УС4 - управляющий сигнал 4, поступающий на управляющие входы ключей блока процессоров и системы ключей.

9. УС5 - управляющий сигнал 5, поступающий на управляющие входы ключей блока процессоров и системы ключей.

10. УС6 - управляющий сигнал 6, поступающий на управляющие входы ключей блока процессоров и системы ключей.

11. ВИ - выходная информация блока 2 процессоров и системы ключей.

12. ИВ - выходная информация блока 3 системы ключей.

13. Уоо - установка исходных состояний функциональных блоков. Блок ДШ дешифратор состоит из элементов ИЛИ-НЕ, НЕ, ИЛИ. Синтез блока заключается в следующем: x1 и x2- входные переменные; УС2, УС3 и УС4 -выходные (см. таблицу).

Все функции реализованы в базисе ИЛИ- НЕ.

Помимо перечисленных функций используются функции УС5 и УС6; УС5 = УС2 V УС3 V УС4; функция УС6 = УС3 V УС4.

Сигнал УС1 поступает на управляющие входы ключей: Кл 2.1 - Кл 2.16 блока СК системы ключей.

Сигнал УС2 поступает на управляющие входы ключей Кл 3.1 - Кл 3.8 блока ПСК процессоров и системы ключей.

Сигнал УС3 поступает на управляющие входы ключей: Кл 4.1 - Кл 4.4 блока ПСК процессоров и системы ключей.

Сигнал УС4 поступает на управляющие входы ключей: Кл 1.4, Кл 1.11, Кл 5.1, Кл 5.2 блока ПСК процессоров и системы ключей.

Сигнал УС5 поступает на управляющие входы ключей: Кл 1.1 и Кл 1.3, Кл 1.5, Кл 1.7, Кл 1.8, Кл 1.10, Кл 1.12, Кл 1.14 блока ПСК процессоров и системы ключей.

Сигнал УС6 поступает на управляющие входы ключей: Кл 1.2, Кл 1.6, Кл 1.9, Кл 1.13 блока ПСК процессоров и системы ключей.

Блок ПСК процессоров и системы ключей состоит из 16 процессорных элементов, ключей Кл 1.1 - Кл 1.1.4, схем ИЛИ 1.1 - 1.8, Кл 3.1 - Кл 3.8, Кл 4.1 - 4.4, Кл 5.1, Кл 5.2. Схематическое решение этого блока заключается в следующем.

Выходная информация ПРЭ 1 поступает на информационные входы ключей Кл 1.1, Кл 4.1, Кл 5.1, а также на вход Кл 2.1 ключей блока СК системы ключей.

Выходная информация ПРЭ 2 поступает на вход Кл 1.1, выход Кл 1.1 является входом ПРЭ 1. Выходная информация Кл 3.1 поступает на первые вход схемы ИЛИ 1.1. Выход ПРЭ 1 также поступает на вход ключей Кл 2.2 СК блока системы ключей.

Выходная информация ПРЭ 3 поступает на вход Кл 1.2, выход которого является вторым входом схемы ИЛИ 1.1, а также поступает на вход Кл 3.2 и на вход Кл 1.3 блока СК системы ключей. Выходная информация ПРЭ 4 поступает на вход ключа Кл 1.3, выход которого поступает на вход ПРЭ 3, а также на вход Кл 2.4 блока СК системы ключей. Выходная информация ПРЭ 5 поступает на информационный вход ключа Кл 1.4, выход которого является первым входом в схему ИЛИ 1.2, на второй и третий входы схемы ИЛИ 1.2 поступает соответственно выходная информация ключей: Кл 3.2 и Кл 4.1. Также выход ПРЭ 5 поступает на информационные входы ключей: Кл 3.3 и Кл 1.5 блока СК системы ключей.

Выходная информация ПРЭ 6 поступает на информационный вход Кл 1.5, выход которого поступает на вход ПРЭ 5, также выход ПРЭ 6 соединен с информационным входом Кл 1.6 блока СК системы ключей.

Выходная информация ПРЭ 7 поступает на информационный вход Кл 1.6, выход которго соединен со вторым входом схемы ИЛИ 1.3, выход которой соединен со входом ПРЭ 6. На второй вход схемы ИЛИ 1.3 поступает выходная информация Кл 3.3, также выход ПРЭ 7 соединен с входом Кл 2.7 блока СК системы ключей и с информационным входом Кл 3.4, выход которого соединен с первым входом схемы ИЛИ 1.4, на второй вход схемы ИЛИ 1.4 поступает выход с ключа Кл 4.2, на третий вход этой схемы поступает выход с ключа Кл 5.1.

Выход схемы ИЛИ 1.4 поступает на вход ПРЭ 8, выход ПРЭ 8, выход которого поступает на информационный вход Кл 1.7, а также на вход Кл 2.8 блока СК системы ключей.

Выходная информация ПРЭ 9 поступает на информационные входы ключей: Кл 3.5, Кл 5.2, а также на вход ключа Кл 2.9 блока СК системы ключей.

Выходная информация ПРЭ 10 поступает на информационный вход Кл 1.8, выход которого является входом ПРЭ 9, также выход ПРЭ 10 соединен с входом ключа Кл 1.10 блока СК системы ключей.

Выходная информация ПРЭ 11 поступает на информационные входы ключей: Кл 2.12 блока СК системы ключей и на Кл 1.10, выход которого является входом ПРЭ 11.

Выходная информация ПРЭ 12 поступает на информационные воды ключей: Кл 2.12 блока СК системы ключей и на Кл 1.10, выход которого является входом ПРЭ 11.

Выходная информация ПРЭ 13 поступает на информационые входы ключей: Кл 3.7, Кл 4.4, Кл 2.13 блока системы ключей, а также на Кл 1.11, выход которого является первым входом схемы ИЛИ 1.6. На второй и третий входы этой схемы ИЛИ 1.6 поступают выходы ключей: Кл 3.6 и Кл 4.3 соответственно. Выход схемы ИЛИ 1.6 соединен с входом ПРЭ 12.

Выходная информация ПРЭ 14 поступает на информационные входы ключей: Кл 2.14 блока СК системы ключей, а также Кл 1.12, выход которого является входом ПРЭ 13.

Выходная информация ПРЭ 15 поступает на информационные входы ключей: Кл 3.8, Кл 2.15 блока СК системы ключей, а также Кл 1.13, выход которого является первым входом схемы ИЛИ 1.7. На второй вход этой схемы ИЛИ 1.7 поступает выход ключа Кл 3.7, выход схемы ИЛИ 1.7 является входом ПРЭ 14.

Выходная информация ПРЭ 16 поступает на информационные входы ключей: Кл 2.16, блока СК системы ключей, а также Кл 1.14, выход которого является входом ПРЭ 15.

Выходная информация ключей: Кл 3.8, Кл 4.4, Кл 5.2 поступает на первый, второй и третий входы схемы ИЛИ 1.8 соответственно, выход которой является входом ПРЭ 16.

Работа устройства системы коммутации процессорных элементов заключается в следующем.

Внешние управляющие сигналы "Пуск" и "Сброс" поступают в блок БУ управления. Из блока БУ управления в блок ДШ дешифратора поступают сигналы ВС1 и ВС2. Эти сигналы являются управляющими сигналами блока ДШ дешифратора. Двоичный код сигналов ВС1 и ВС2 формирует режим работы системы коммутации процессорных элементов. Существуют четыре двоичных набора двух сигналов. Первый код - ОО. По приходу в блок ДШ дешифратора двоичного кода ОО из блока БУ управления система коммутации работает в первом - "независимом" режиме. Этот режим характерен независимой работой процессорных элементов. Все процессорные элементы при этом работают независимо друг от друга. Этот режим организуется следующим образом.

На управляющие выходы ключей: Кл 1.1 - Кл 1.14, Кл 3.1 - Кл 3.8, Кл 4.1 - Кл 4.4, Кл 5.1, Кл 5.2 системы поданы из блока ДШ дешифратора запирающие потенциалы, при этом блокируется связь между процессорными элементами, тем самым обеспечивается "независимый" режим работы системы коммутации. На управляющие входы системы ключей Кл 2.1 - Кл 2.16 блока СК подан отпирающий потенциал из блока управления. При этом вся выходная информация каждого процессорного элемента системы коммутации через открытые ключи блока СК поступает на блок выходного канала устройства.

Двоичный код из блока ДШ дешифратора 01 определяет второй режим работы системы коммутации - "режим по два". При этом режиме образуются группы процессорных элементов по два процессорных элемента в каждой группе. Образуются восемь групп.

В состав первой группы входят: ПРЭ 1 и ПРЭ 2 (процессорные элементы), а также ключи: Кл 1.1, схема ИЛИ 1.1, Кл 3.1. На управляющие входы этих ключей подан отпирающий потенциал.

Вторая группа состоит из ПРЭ 3 и ПРЭ 4, а также ключей: Кл 1.3, схемы ИЛИ 1.2, Кл 3.2. На управляющий вход ключа Кл 1.2 подан запирающий потенциал, тем самым нет связи между первой и второй группой.

Третья группа состоит из ПРЭ 5 и ПРЭ 6, а также ключей Кл 1.5, схемы ИЛИ 1.3, Кл 3.3. На управляющие входы этих ключей подан отпирающий потенциал. На управляющий вход ключа Кл 1.4 подан запирающий потенциал, тем самым нет связи между второй и третьей группой.

Четвертая группа состоит из ПРЭ 7 и ПРЭ 8, а также ключей Кл 1.7, схемы ИЛИ 1.4, Кл 3.4. На управляющие входы этих ключей подан отпирающий потенциал. На управляющий вход ключа Кл 1.6 подан запирающий потенциал, тем самым нет связи между третьей и четвертой группой.

Пятая группа состоит из ПРЭ 9 и ПРЭ 10, а также ключей Кл 1.8, схемы ИЛИ 1.5, Кл 3.5. На управляющие входы этих ключей подан отпирающий потенциал. Связи между четвертой и пятой группой нет по схеме.

Шестая группа состоит из ПРЭ 11 и ПРЭ 12, а также ключей Кл 1.10, схемы ИЛИ 1.6, Кл 3.6. На управляющие входы этих ключей подан отпирающий потенциал. На управляющий вход ключа Кл 1.9 подан запирающий потенциал, тем самым нет связи между пятой и шестой группой.

Седьмая группа состоит из ПРЭ 13 и ПРЭ 14, а также ключей Кл 1.12, схемы ИЛИ 1.7, Кл 3.7. На управляющие входы этих ключей подан отпирающий потенциал.

На управляющий вход ключа Кл 1.11 подан запирающий потенциал, тем самым нет связи между шестой и седьмой группой.

Восьмая группа состоит из ПРЭ 15 и ПРЭ 16, а также ключей Кл 1.14, схемы ИЛИ 1.8, Кл 3.8. На управляющие входы этих ключей подан отпирающий потенциал. На управляющий вход ключа Кл 1.13 подан запирающий потенциал, тем самым нет связи между седьмой и восьмой группой.

На управляющие входы ключей Кл 4.1 - Кл 4.4, а также Кл 5.1 и Кл 5.2 подан соответственно запирающий потенциал. На управляющие входы блока СК системы ключей Кл 2.1 - Кл 2.16 из блока управления подан отпирающий потенциал, при этом вся выходная информация групп блока ПСК процессоров и системы ключей через "открытые" ключи поступает на блок выходного канала устройства.

Двоичный код из блока ДШ дешифратора 10 определяет третий режим работы системы коммутации - "режим по четыре". При этом режиме образуются группы процессорных элементов по четыре процессорных элемента в каждой группе. Образуются четыре группы.

В состав первой группы входят ПРЭ 1, ПРЭ 2, ПРЭ 7 и ПРЭ 8, а также ключи: Кл 1.5, схема ИЛИ 1.3, Кл 1.6, Кл 1.7, схема ИЛИ 1.4, Кл 4.2. На управляющие входы этих ключей подан отпирающий потенциал. На управляющие входы ключей Кл 3.3 и Кл 3.4 подан соответственно запирающий потенциал, тем самым нет связи между первой и второй группой этого режима.

В состав третьей группы входят ПРЭ 9, ПРЭ 10, ПРЭ 11 и ПРЭ 12, а также ключи: Кл 1.8, схема ИЛИ 1.5, Кл 1.9, Кл 1.10, схема ИЛИ 1.6, Кл 4.3. На управляющие входы этих ключей подан отпирающий потенциал. На управляющие входы этих ключей ключей Кл 3.5, Кл 3.6 подан запирающий потенциал. На управляющий вход ключа Кл 1.11 подан соответственно запирающий потенциал, тем самым нет связи между третьей и четвертой группой этого режима.

Четвертая группа - ПРЭ 13, ПРЭ 14, ПРЭ 15 и ПРЭ 16, а также ключи: Кл 1.12, схема ИЛИ 1.7, Кл 1.13, Кл 1.14, схема ИЛИ 1.8. Кл 4.4. На управляющие входы ключей Кл 1.12, Кл 1.13, Кл 1.14, Кл 4.4, поданы отпирающие потенциалы. На управляющие входы ключей Кл 3.7 и Кл 3.8 поданы запирающие потенциалы.

В этом режиме на управляющие входы ключей Кл 5.1, Кл 5.2 поданы запирающие потенциалы. В каждой группе процессорные элементы работают в совокупности. Выходная информация из блока 2 процессоров и системы ключей через систему ключей блока 3 по приходу сигнала "УС1:=1" соединяется с выходным каналом.

Четвертый режим - "режим по восемь". При этом режиме образуются две группы по восемь процессорных элементов в каждой.

Первая группа - ПРЭ 1, ПРЭ 2, ПРЭ 3, ПРЭ 4, ПРЭ 5, ПРЭ 6, ПРЭ 7, ПРЭ 8, а также ключи Кл 1.1, схема ИЛИ 1.3, Кл 1.2, Кл 1.3, схема ИЛИ 1.2, Кл 1.4, Кл 1.5, схема ИЛИ 1.3, Кл 3.1, Кл 1.6, Кл 1.7, схема ИЛИ 1.4, Кл 5.1. На управляющие входы этих ключей Кл 3.1, Кл 3.2, Кл 3.3, Кл 3.4, Кл 4.1, Кл 4.2 поданы запирающие потенциалы, тем самым организована первая группа элементов четвертого режима.

Вторая группа - ПРЭ 9, ПРЭ 10, ПРЭ 11, ПРЭ 12, ПРЭ 13, ПРЭ 15, ПРЭ 16, а также ключи КЛ 1.8, схема ИЛИ 1.5, Кл 1.9, Кл 1.14, схема ИЛИ 1.6, Кл 1.11, Кл 1.12, схема ИЛИ 1.7, Кл 1.13, Кл 1.14, схема ИЛИ 1.8, Кл 5.2. На управляющие входы этих ключей поданы отпирающие потенциалы. На управляющие входы ключей Кл 3.5, Кл 3.6, Кл 3.7, Кл 3.8, Кл 4.3, Кл 4.4 поданы запирающие потенциалы, тем самым организована вторая группа элементов четвертого режима.

В каждой группе процессорные элементы работают в совокупности. Выходная информация из блока 2 процессорных элементов и системы ключей через систему ключей блока 3 по приходу из блока управления управляемого сигнала "УС1:=1" соединяется с блоком выходного канала (ВК).

Работа алгоритма управления устройства.

Содержательная ГСА управления приведена на фиг. 7 и отражает работу блока управления 5 (фиг. 1).

По сигналам "Уоо" и "ПУСК" (блоки 2, 4 - граф-схемы алгоритма) происходит установка в нуль всех процессорных элементов устройства по командам "СБРОС:=1", "ПУСК:=1" соответственно (блоки 3 и 5).

Также в блоке 5 алгоритма по команде "УС1:=0" происходит подача из блока БУ управления запирающего потенциала на управляющие входы ключей блока БСК системы ключей.

По команде "УС2:=0" (блока 5 алгоритма) происходит подача из блока БДШ дешифратора запирающего потенциала на управляющие входы ключей: Кл 4.1 - Кл 4.4 блока БПСК процессоров и системы ключей.

По команде "УС3:=0" (блока 5 алгоритма) происходит подача из блока БДШ дешифратора запирающего потенциала на управляющие входы ключей: Кл 1.4. Кл 1.11, Кл 5.1, Кл 5.2 блока БПСК процессоров и системы ключей.

В блоке 6 алгоритма по команде "УС4:=0" происходит подача из блока БДШ дешифратора запирающего потенциала на управляющие входы ключей: Кл 1.4, Кл 1.11, Кл 5.1, Кл 5.2 блока БПСК процессоров и системы ключей.

По команде "УС5:=0" (блока 6 алгоритма) происходит подача из блока БДШ дешифратора запирающего потенциала на управляющие входы ключей: Кл 1.1, Кл 1.3, Кл 1.5, Кл 1.7, Кл 1.8, Кл 1.10, Кл 1.12, Кл 1.14 блока БПСК процессоров и системы ключей.

По команде "УС6:=0" (блока 6 алгоритма) происходит подача из блока БДШ дешифратора запирающего потенциала на управляющие входы ключей: Кл 1.2, Кл 1.6, Кл 1.9, Кл 1.13 блока БПСК процессоров из системы ключей.

В блоке 7 алгоритма по команде происходит проверка признака работы устройства в "независимом режиме", который характеризуется кодом 00 ("ВС1=0" и "ВС2=0"), при этом осуществляет переход на блок 10 алгоритмов.

В блоке 8 и 9 происходит подача запирающих и отпирающих потенциалов из блоков БДШ дешифратора из блока БУ управления, которые определяют работу устройства в независимом режиме.

В блоке 8 алгоритма по командам "УС2:=0", "УС3:=0", "УС4:=0" происходит подача из блока БДШ дешифратора запирающих потенциалов на управляющие входы соответствующих ключей.

В блоке 9 алгоритма по командам "УС5:=0" и "УС6:=0" происходит подача из блока БДШ дешифратора запирающих потенциалов на управляющие входы соответствующих ключей блока БПСК процессоров и системы ключей.

По команде "УС1:=1" происходит подача из блок БУ управления запирающих потенциалов на управляющие входы ключей Кл 2.1 - Кл 2.16 блока БПСК процессоров и системы ключей. При этом осуществится переход на блок 18 алгоритма (фиг. 7).

В блоке 10 алгоритма происходит проверка признака работы устройства в "режиме по два", который характеризуется кодом 01 (ВС1=0" и "ВС2=1"), при этом осуществляется переход на блок 13 алгоритма.

В блоке 11 алгоритма по командам "УС2:=1", "УС3:=0", "УС4:=0" происходит подача из блока БДШ дешифратора запирающих потенциалов на управляющие входы соответствующих ключей блока БПСК процессоров и системы ключей.

В блоке 12 алгоритма по командам "УС5:=1", "УС6:=0", "УС1:=1" происходит подача из блока БДШ дешифратора и соответственно отпирающего и запирающего потенциалов на соответствующие ключи блока БПСК процессоров и системы ключей, а также подача из блока БУ управления отпирающего потенциала на соответствующие ключи блока БСК системы ключей. При этом осуществляется переход на блок 18 алгоритма (фиг. 7).

В блоке 13 алгоритма происходит проверка признака работы устройства в "режиме по четыре", который характеризуется кодом 10 ("ВС1=1" и "ВС2=0"). При этом осуществляется переход на блок 16 алгоритма (фиг. 7).

В блоке 14 алгоритма по командам "УС2:=0", "УС3:=1", "УС4:=0" происходит подача из блока БДШ дешифратора соответственно запирающего, отпирающего и запирающего потенциалов на управляющие входы соответствующих ключей блока БПСК процессоров и системы ключей (фиг. 7).

В блоке 15 алгоритма по командам "УС5:=1", "УС6:=1" происходит подача из блока БДШ дешифратора отпирающих потенциалов на соответствующие ключи блока БПСК процессоров и системы ключей, а также по команде "УС1:=1" происходит подача из блока БУ управления отпирающего потенциала на управляющие входы ключей: Кл 2.1 - Кл 2.16 блока БСК системы ключей (фиг. 1). При этом осуществляется переход на блок 18 алгоритма (фиг. 7).

Режим работы устройства в "режиме по восемь", характеризуется кодом 11 ("ВС1= 1" и "ВС2= 1"). В блоках алгоритма (16 и 17) происходит определение режима работы устройства "режим по восемь" (фиг. 7).

В блоке 16 алгоритма по командам "УС2:=0", "УС3:=0", "УС4:=1" происходит подача соответственно запирающих и отпирающих потенциалов на управляющие входы соответствующих ключей блока БПСК процессоров и системы ключей.

В блоке 17 алгоритма по командам "УС5:=1", "УС6:=1" происходит подача отпирающих потенциалов на управляющие входы соответствующих ключей блока БПСК процессоров и системы ключей. По команде "УС1:=1" происходит подача отпирающего потенциала на управляющие входы ключей блока БСК системы ключей: Кл 2.1 - Кл 2.16. При этом осуществляется переход на блок 18 алгоритма (фиг. 7).

В блоке 18 алгоритма происходит проверка признака P, который характеризует дальнейший выбор режима работы устройства, при этом осуществляется переход на блок 7 алгоритма, либо переход в блок 19 алгоритма (фиг. 7).

В блоке 19 алгоритма фиксируется конец его работы. Алгоритм управления отражает один рабочий цикл работы устройства на заданном режиме.

Блок 5 управления синтезируется на основе ГСА алгоритма управления (фиг. 7) известным способом. Размеченная ГСА работы блока 7 управления приведена на (фиг. 8), где обозначено:

Логические условия

X1 : "УОО" - X4 : "01"

X2 : "ПУСК" - X5 : "10"

X3 : "00" - X6 : "P"

Операторы

Y1 : "СБРОС : =1" - Y8 : "УС6:=0"

Y2 : "ПУСК : =1" - Y9 : "УС1:=1"

Y3 : "УС1:=0" - Y10 : "УС2:=1"

Y4 : "УС2:=0" - Y11 : "УС5:=1"

Y5 : "УС3:=0" - Y12 : "УС3:=1"

Y6 : "УС4:=0" - Y13 : "УС6:=1"

Y7 : "УС5:=0" - Y14 : "УС4:=1"

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДИРОВАНИЯ РЕЧЕВЫХ СИГНАЛОВ | 1993 |

|

RU2120700C1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С УСТРОЙСТВОМ УПРАВЛЕНИЯ | 2013 |

|

RU2535931C1 |

| КОГЕРЕНТНЫЙ ПРИЕМООТВЕТЧИК ФАЗОВОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2319931C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В ДВОИЧНЫЙ УНИТАРНЫЙ КОД | 1994 |

|

RU2097918C1 |

| Устройство для деления | 1983 |

|

SU1151955A1 |

| УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ УПОРЯДОЧИВАЮЩИХ ПОДСТАНОВОК | 1992 |

|

RU2067315C1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для автокомпенсации емкостных токов однофазных замыканий в коротких сетях | 1990 |

|

SU1704222A1 |

| СИСТЕМА РАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2000 |

|

RU2189073C2 |

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для решения задач коммутации процессорных элементов. Техническим результатом является расширение функциональных возможностей и увеличение скорости передачи информации из одного локального вычислительного кольца в другое. Коммутационная система содержит блок-дешифратор, блок процессорных элементов и системы ключей, блок системы ключей, блок выходного канала, блок управления, логические элементы ИЛИ, ИЛИ-НЕ, И-НЕ, НЕ. 1 табл., 8 ил.

Система коммутации процессорных элементов, содержащая блок управления, отличающаяся тем, что дополнительно введены блок-дешифратор, блок процессоров и системы ключей, блок системы ключей и блок выходного канала, причем первый и второй управляющие выходы блока управления соединены соответственно с первым и вторым управляющими входами блока-дешифратора, с первого по пятый управляющие выходы которого соединены соответственно с первого по пятый управляющими входами блока процессоров и системы ключей, информационный выход которого соединен с информационным входом блока системы ключей, управляющий вход которого соединен с третьим управляющим выходом блока управления, информационный выход блока системы ключей соединен с информационным входом блока выходного канала, а первый и второй управляющие входы "Сброс" и "Пуск" блока управления являются внешними входами системы.

| SU 1300488 A1, 30.03.87 | |||

| Межсетевое устройство управления | 1986 |

|

SU1383380A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1273940A1 |

Авторы

Даты

1999-02-27—Публикация

1992-04-20—Подача