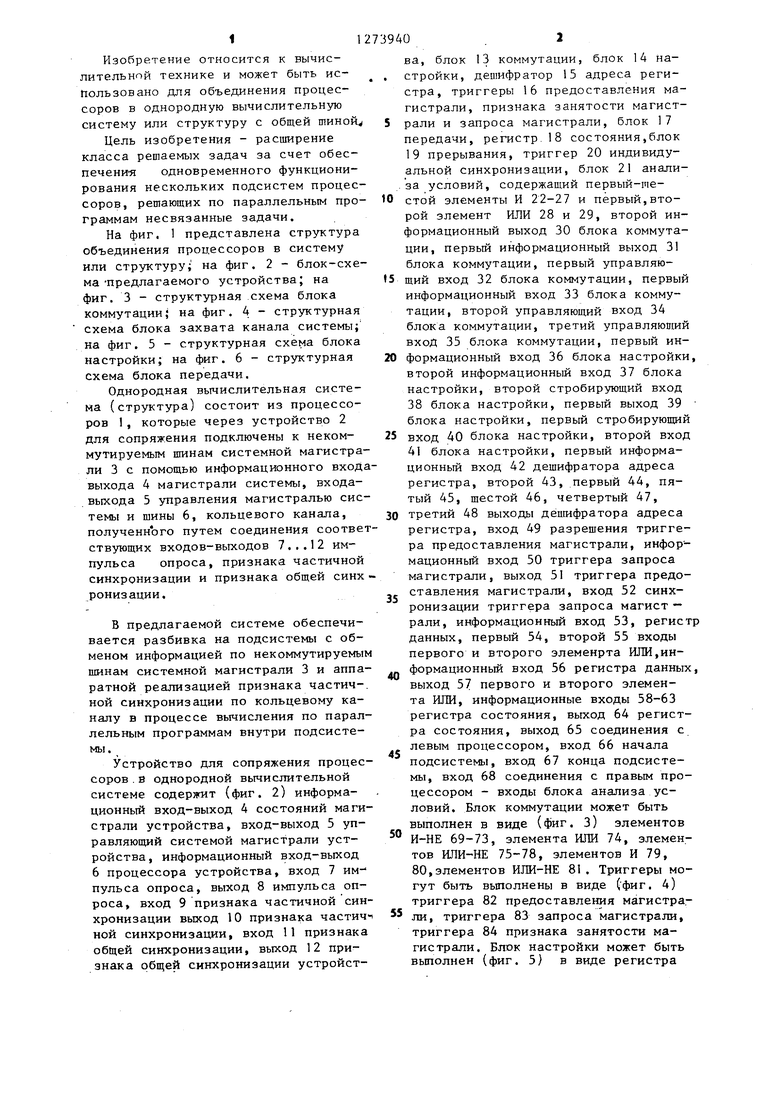

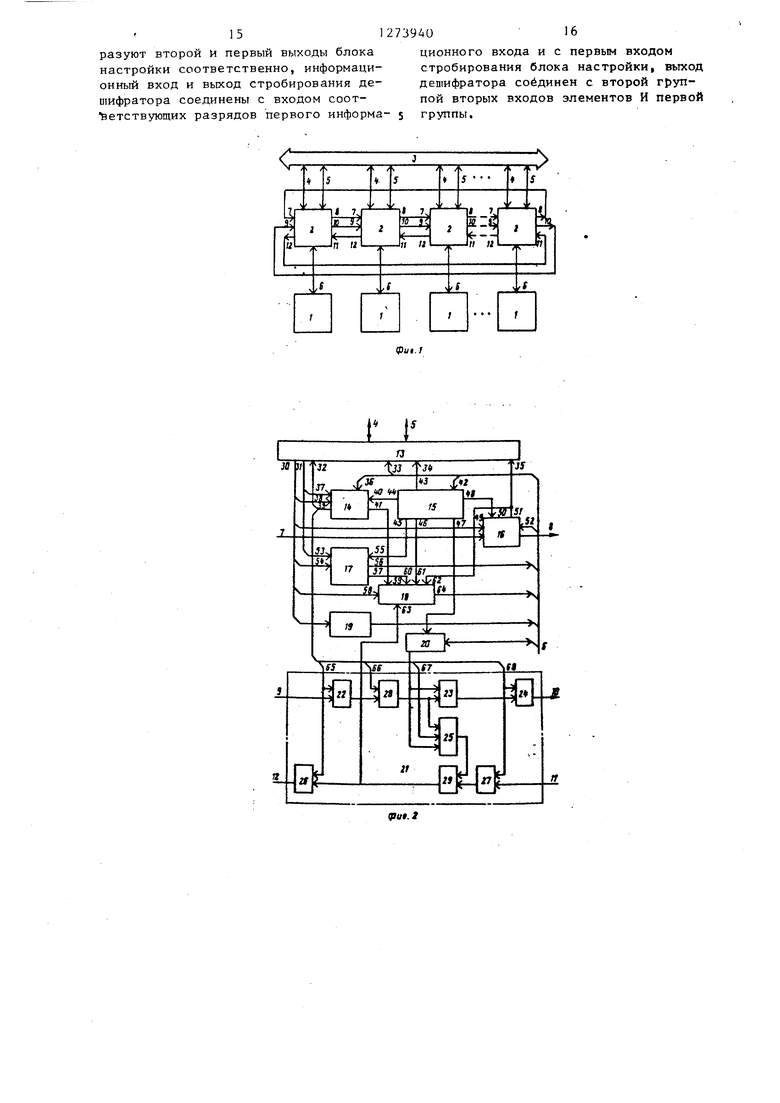

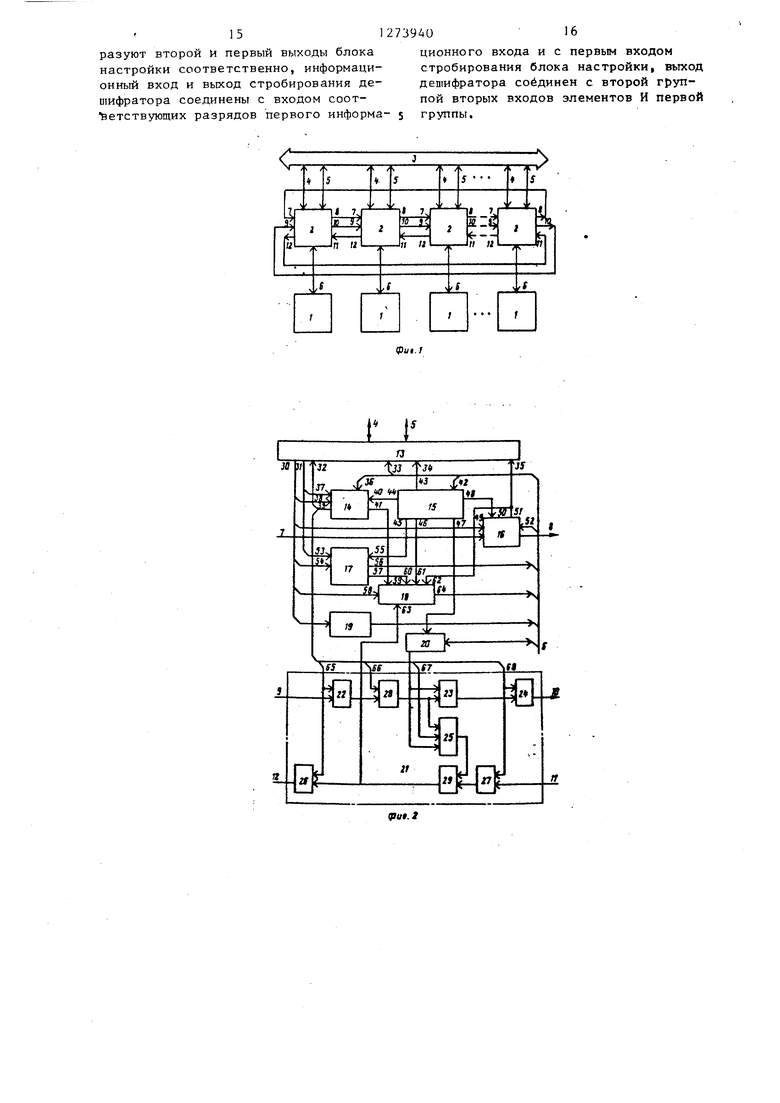

Изобретение относится к вычислительной технике и может быть исПользовано для объединения процессоров в однородную вычислительную систему или структуру с общей шиной Цель изобретения - расширение класса решаемых задач за счет обеспечени-я одновременного функционирования нескольких подсистем процес соров, решающих по параллельным про граммам несвязанные задачи. На фиг. 1 представлена структура объединения процессоров в систему или структуру; на фиг. 2 - блок-схе ма -предлагаемого устройства; на фиг. 3 - структурная схема блока коммутации; на фиг. 4 - структурная схема блока захвата канала системы; на фиг. 5 - структурная схема блока настройки; на фиг. 6 - структурная схема блока передачи. Однородная вычислительная система (структура) состоит из процессоров 1, которые через устройство 2 для сопряжения подключены к некоммутируемым шинам системной магистра ли 3 с помощью информационного вход выхода 4 магистрали системы, входавыхода 5 управления магистралью сис темы и шины 6, кольцевого канала, полученного путем соединения соотве ствующих входов-выходов 7 ... 12 импульса опроса, признака частичной синхронизации и признака общей синх ронизации. В предлагаемой системе обеспечивается разбивка на подсистемы с обменом информацией по некоммутируемы шинам системной магистрали 3 и аппа ратной реализацией признака частимной синхронизации по кольцевому каналу в процессе вычисления по парал лельным программам внутри подсистемы. Устройство для сопряжения процес соров .в однородной вычислительной системе содержит (фиг. 2) информационный вход-выход 4 состояний маги страли устройства, вход-выход 5 управляющий системой магистрали устройства , информационный вход-выход 6 процессора устройства, вход 7 импульса опроса, выход 8 импульса опроса, вход 9 признака частичной син хронизации выход 10 признака частич ной синхронизации, вход 11 признака общей синхронизации, выход 12 признака общей синхронизации устройст0 . 2 ва, блок 13 коммутации, блок 14 настройки, дешифратор 15 адреса регистра, триггеры 16 предоставления магистрали, признака занятости магистрали и запроса магистрали, блок 17 передачи, регистр,18 состояния,блок 19 прерывания, триггер 20 индивидуальной синхронизации, блок 21 анализа условий, содержащий первый-шестой элементы И 22-27 и первый,второй элемент ИЛИ 28 и 29, второй информационный выход 30 блока коммутации, первый информационный выход 31 блока коммутации, первый управляющий вход 32 блока коммутации, первый информационный вход 33 блока коммутации, второй управляющий вход 34 блока коммутации, третий управляющий вход 35 блока коммутации, первый информационный вход 36 блока настройки, второй информационный вход 37 блока настройки, второй стробирующий вход 38 блока настройки, первый выход 39 блока настройки, первый стробируюший вход 40 блока настройки, второй вход 41 блока настройки, первый информационный вход 42 дешифратора адреса регистра, второй 43, первый 44, пятый 45, шестой 46, четвертый 47, третий 48 выходы децмфратора адреса регистра, вход 49 разрешения триггера предоставления магистрали, информационный вход 50 триггера запроса магистрали, выход 51 триггера предоставления магистрали, вход 52 синхронизации триггера запроса магист - рали, информационный вход 53, регистр данных, первый 54, второй 55 входы первого и второго элеменрта ИЛИ,информационный вход 56 регистра данных, выход 57 первого и второго элемента ИЛИ, информационные входы 58-63 регистра состояния, выход 64 регистра состояния, выход 65 соединения с левым процессором, вход 66 начала подсистемы, вход 67 конца подсистемы, вход 68 соединения с правьм процессором - входы блока анализа условий. Блок коммутации может быть выполнен в виде (фиг. 3) элементов И-НЕ 69-73, элемента ИЛИ 74, элементов ИЛИ-НЕ 75-78, элементов И 79, 80,элементов ИЛИ-НЕ 81. Триггеры могут быть выполнены в виде (фиг. 4) триггера 82 предоставления магистрали, триггера 83 запроса магистрали, триггера 84 признака занятости магистрали. Блок настройки может быть выполнен (фиг. 5) в виде регистра

85, двух групп 86 и 87 элементов И, дешифратора 88 физического вдреса устройства. Блок передачи может быть выполнен; в виде (фиг. б) элементов ИЛИ 89-91 и регистра 92. В однородной вычислительной системе (структуре) с общей шиной, построенной с использованием устройства для сопряжения, используется следующий набор системных операций: настройка, частичная синхронизация, захват магистрали системы обмена и общая синхро.низапия.

Операция настройки состоит в подключении устройства для сопряжения через блок 13 коммутации к общей шин системы 3 и выделении подсистем путем ограничения начала и конца под.системы. Для настройки устройства для сопряжения необходимо занести настроечную информацию в регистр 85 (фиг. 5) блока 14 настройки. Формат управляющего слова регистра 85 настройки имеет следующий вид: Управляющее слово регистра настройки ()

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с общей магистралью | 1985 |

|

SU1252790A1 |

| Устройство для сопряжения микроЭВМ с общей магистралью | 1986 |

|

SU1365090A2 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

| Устройство для подключения ЭВМ к системной шине | 1986 |

|

SU1361571A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

| Устройство для сопряжения | 1986 |

|

SU1327116A2 |

| Устройство сопряжения для однороднойВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU851387A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство сопряжения для однородной вычислительной системы | 1981 |

|

SU1068928A1 |

Изобретение относится к вычислительной технике и может быть использовано для объединения нескольких процессоров в однородную вычислительную систему или структуру с общей шиной. Цель изобретения - повышение производительности устройства и расширение класса решаемых задач достигается за счет введения в устройство сопряжения блока и анализа условий, что позволяет в системе с общей шиной одновременно выделить несколько подсистем, ретаклцих набор не связанных между собой задач, при этом исключаются потери времени, связанные с простоями процессоров, не вошедшими в выделенную подсистему. Используется набор системных операций: настройка, частичная синхронизация, захват магистрали системы, обмен и общая синхронизация. Операция настройки состоит в подключении устройства для сопряжения процессоров через блок коммутации к общей шине системы и выделений подсистемы, путем ограничения начала и конца подсистемы. В процессоре выполнения подсистемами параллельных программ процессоры обмениваются информацией. Данное устройство позволяет осуществлять трансляционный обмен внутри подсистем через единую магистраль системы. При этом необходимо выполнить операцию синхронизации внутри подсистемы и операцию захвата систем(Л ной магистрали. Если магистраль свободна, она представляется только тому процессору, .в устройстве для сопряжения которого совпадают в данный момент сигнал требования магистрали и единица в триггере сдвигового регистра. Другие процессоры ждут, м пока магистраль не освободится и бусо дет предоставлена ближайшему из последующих в цепочке процессоров. Операко ция общей синхронизации состоит в том, что один из процессоров подсистемы вызывает прерывание всех процессоров подсистемы, после чего процессоры переходят на новую ветвь параллельных вычислений. 6 ил.

Логический адрес

Выделение подсистемы

О О

Внутренний процессор подсистемы

О 1

Начало подсистемы

1 О

Конец подсистемы

1 1

Процессор-подсистема В разряд ДО заносится информация,которая управляет подключением устройства 2 для сопряжения (фиг, l) к шине 3 системы (первый управляющий вход 32 блока 13 коммутации фиг. 2). Разряды Д1, Д2 содержат код соединительной функции (входы 68 и 65 блока 21 анализа условий), с помощью которой задается коммутация входов 9, 11 и выходов 10, 12 соответственно частичной и общей синхронизации блоков для сопряжения процессоров, входящих в систему. Так, если Д1 и Д2 установлены в 1, то данный процессор имеет связь с двумя соседними процессорами. Если или Д1 (вход 68), или Д2 (вход 65) установ О лены в то связь данного процессора осуществляется соответствен левымправым процессо

Коммутация канала

Не подключено

Подключено ром. Разряды ДЗ и Д4 (входы 66, 67 блока 21 анализа условий) содержат признаки начала и конца подсистемы -соответственно. Так, например, в системе, состоящей из десяти процессоров, организовано три подсистемы: 1-5 процессоры - первая подсистема; 6 процессор - вторая подсистема, 710 процессор - третья подсистема Содержимое управляющих слоев регистров настройки блоков сопряжения приведено в таблице. Продолжение таблиць Настроечная информация в блок 14 настройки может поступить из процессора, связанного с данным устройством для сопряжения по каналу процессора (информационный вход 36), или из другого процессора по общей шине 3 однородной вычислительной систе мы (информационный вход 37). Настройка собственного устройства для сопряжения производится следующим образом. Процессор (не показан) по первому информационному входу 42 заносится в дешифратор 15 адрес регистра 85 (фиг. 5) блока 14 настрой ки. С первого выхода 44 дешифратора 15 на первый стробирующий вход 40 блока настройки поступает сигнал раз решения записи настроечного слова по первому информационному входу 36 через схему И 87 (фиг. 5) в регистр 85 блока 14 настройки. Снятие настройки устройства производится аналогично. но настроечное слово должно содержать все нули. С первого выхода 39 блока 14настройки на первый управляющий вход 32 блока 13 коммутации поступает логическая 1, разрешая прохождение данных через блок 13 коммутации на вход-выход 4 магистрали и далее на общую шину системы и обратно. Настройка устройства для сопряжения по общей шине системы производится следующим образом. Нарастающий процессор (им может быть только процессор с настроенным устройством сопряжения) по адресу, соответствующему системной операции Настройка, передает настроечное слово, в котором кодируется адрес и информация о настройке настраиваемых процессоров подсистемы. При этом по входу-выходу процессора на первый информационный вход 33 блока 13 коммутации первые входы элементов ИНЕ 69 поступает настроечное слово, а с второго выхода 43 дешифратора 15адреса регистра на второй управляющий вход 34 системных сигналов (цепь настройки, первые входы элементов И-НЕ 70-72 и элемента ИЛИ 74) импульсный сигнал логической 1, по которому на вход-выход магистрали 4 устройства для сопряжения поступает настроечное слово, а на управлякмций магистралью 5 вход-выход устройства сигнал Настройка. На все устройства сопряжения из общей шины системы поступает сигнал Настройка, который через элемент РШИНЕ 78 поступает на второй информационный выход 30 блока 13 коммутации, и настроечное слово через элементы ИЛИ-НЕ 81 (фиг. З) поступает на первый информационный выход 31 блока 13 коммутации. Сигнал Настройка поступает на второй информационный вход 37 блока настройки (стробирующие входы группы элементов И 86 и дешифратора 88 физического адреса устройства на фиг, 5),а настроечное слово - на второй стробирующий вход 38 группы элементов И 86 (фиг. 5) и. вход дешифратора 88 физического адреса устройства. Третий управляющий вход группы элементов соединен с выходом дешифратора 88 физического адреса устройства. Дешифратор 88 работает следующим ; образом. Если на его управляюпщй вход поступает сигнал Настройка, а адре.сная часть настроечного слова,по.ступающая на его информационные входы, соответствует адресу данного устройства для сопряжения, то сигнал настройки проходит на управляющий выход дешифратора 88 (логическая 1). Логические сигналы физического адреса устройства устанавливаются на входе дешифратора 88 перемычками перед комплексированием системы. С выхода блока элементов И 86 настроечная информация заносится в регистр 85 настройки. Разрушение настройки выполняется аналогично операции настройки, При этом в разрядах ДО-Д4 настроечного слова записываются нули. После настройки всех устройств для сопряжения в системе выделяется несколько подсистем, процессоры которых переходят к выполнению параллельных программ. В процессе выполнения подсистемы параллельных программ процессоры обмениваются информацией. Предлагаемое устройство для сопряжения позволяет осуществлять трансляционный обмен внутри подсистем через единую магистраль системы. При этом для организации обмена внутри подсистемьт необходимо выполнить операцию синхронизации внутри подсистемы и операцию захвата системной магистрали.

Операции обмена внутри подсистемы предшествует операции синхронизации, которая выполняется блоками для сопряжения, выделенных в подсистему процессоров следующим образом. Процессор, готовый к обмену, устанавливает триггер 20 индивидуальной синхронизации по входу-выходу 6 процессора и выход 47 разрешений дешифратора 15 адреса регистра в единичное состояние и переходит на опрос соответствующего разряда регистра 18 состояния. С выхода триггера 20 сигнал индивидуальной синхронизации поступает на вторые входы второго и четвертого элементов И блока 21 анализа услоВИЙ. В зависимости от состояния Д1, Д2 и ДЗ, Д4 (входы 68, 65, 66, 67) блок 21 вырабатывает следующие сигналы. Если данный процессор является началом подсистемы (см. содержимое

PpH разрядов Д1 , Д2 и ДЗ, ДА процессора I таблиц), то сигнал логической 1 с разрядов ДЗ и Д1 входы 66 и 68 поступает на вторые входы первого

элемента ИЛИ 28 и третьего элемента

И 25, разрешая прохождение сигнала

частичной синхронизации на выход 10 .блока 21. Одновременно сигнал 1 разряда Д1 регистра 85 (фиг. 5) блока 14 настройки подготавливает про5 хождение сигнала общей синхронизации с правого процессора. Если данный процессор является промежуточным процессором подсистемы, то сигнал логической 1 с разрядов Д2, Д1 регист10 ра 85 блока 14 настройки поступает на вторые входы первого 22, третьего 24, пятого 27 и шестого 26 элементов И, разрешая прохождение сигнала частичной синхронизации с левого

Т5 процессора через первые входы первого элемента И 22, первого элемента ИЛИ 28, второго 23, третьего 24 элементов И соответственно и подготавливая первые входы -шестого 26 и пя20 того 27 элементов И для прохождения сигнала общей синхронизации с входа 11 на выход 12 блока сопряжения и вход 63 регистра состояния.

25 Если данный процессор является концом подсисте, то сигнал логической 1 с разрядов Д4, Д2 регистра 85 блока 14 настройки поступает на третий вход четвертого элемента И 25, подготавливая вьфаботку сигнала общей синхронизации подсистемы, и вторые входы первого и пятого элементов И 22, 26 блока 21.

Сигнал общей синхронизации появляется на выходе четвертого элемента

5 И 25 блока 21, если сигнал частичной синхронизации поступил с соседнего блока для сопряжения по входу 9 и с триггера 20 повторной синхронизации. Сигнал общей синхронизации с

0 выхода четвертого элемента И 25 блока сопряжения процессора, назначенно.го концом подсистемы, поступает на выход 12 через второй элемент ИЛИ 29 и пятый элемент И 26 блока 21. В

5 промежуточных процессорах подсистемы сигнал общей синхронизации с входа 11 через подготовленные по вторым входам шестого и пятого элементов И 27 и 26 и второго элемента ИЛИ

0 поступает на вход пятого элемента И процессора начала подсистемы. У всех блоков 21 подсистемы с выходов элементов ИЛИ сигнал общей синхронизации поступает через вход 63 на со5 ответствующий разряд регистра 18 состояния. Процессор, проанализировав состояние этого разряда регистра 18, определяет, что синхронизация выполнена и переходит к операции захвата магистрали 3. Захват магистрали. В операции захвата магистрали может участвовать любой процессор системы. Для захвата магистрали 3 (фиг. 1) системы в бло ке 2 для сопряжения выполняются следующие действия: по входу 52 синIхронизации с входа-выхода 6 процессора и разрешений с третьего выхода 48 дешифратора 15 в триггер 83 (фиг, 4) заносится сигнал требований системной магистрали, поступает на вход триггера 82 и записывается в него в момент разрешения с выхода триггера 84 признака и наличия сигнала разрешения с второго информационного выхода 30 блока 13 коммутации, сигнализирующего о том, что системная магистраль свободна. С выхода 51 триггера 82 сигнал занятости системной магистрали (С,) поступает через вход 62 в соответствующий разряд регистра 18 состояния, сигнализируя связанному с ним процес сору о предоставлении магистрали, и через блок 13 коммутации через элемент НЕ 73 (фиг. З) на управляющий магистралью вход-выход 5 устройства С управляющего магистрального входа выхода 5 сигнал С,j, поступает через элементы 77 блоков 13 коммутации че рез второй информационный выход 30 на вход 49 разрешения триггеров 82 (фиг. 4) всех остальных устройств. системы и удерживае-т их в нулевом состоянии. С выхода 51 триггера 82 сигнал занятости (нуль) записываетс в регистр 18 состояния, сигнализиру связанному с этим устройством проце сору о занятести системной магистра ли. Сигнал требования магистрали может появиться одновременно в нескольких устройствах для сопряжения входящих в разрядные подсистемы.Чтобы исключить возможность конфликта, т.е. чтобы системная магистраль была предоставлена в каждый момент вре мени только одному процессору,триггеры 84 системы соединены в цепочку входами 7 и выходами 8 импульсов опроса, образующую сдвиговый регист в котором циркулируют единицы. Ес ли магистраль свободна, то она предоставлена только тому процессору, в устройстве для сопряжения которого совпадают .в данный момент сигнал 0 . 10 требования магистрали и единица в триггере сдвигового регистра. Ввиду того, что момент возникновения запроса на магистраль (возникновение сигнала требования магистрали) никак не синхронизирован с частотой перемещения единицы по сдвиговому регистру, то предоставление магистрали в случае одновременного запроса его несколькими процессорами псевдослучайно. Другие процессоры ждут, пока магистраль не освободится и будет предоставлена ближайшей из последующих в цепочке процессоров. Обмен. Процессор, в программе которого предусмотрено выполнение передачи в системной операции обмена, посылает по магистрали процессора в дешифратор 15 код, соответствующий операции передачи, при этом с второго выхода 43 дешифратора 15 на второй управляющий вход 34 блока 13 коммутации поступает сигнал Передача (первый и второй входы элементов ИНЕ 70, ИЛИ 74 соответственно). Информационное слово из оперативной памяти по каналу процессора поступает на второй управляющий вход 34 блока 13 коммутации и по информационному входу-выходу 4 магистрали совместно с сигналог- Передача, поступающим на управляющий магистралью вход-выход 5 устройства, в общую магистраль 3 системы. В устройства сопряжения, связанные с процессорами, выполняющими прием системной информации обмена, из общей магистрали системы поступает информация по информационному входувыходу 4 магистрали, сопровождающему сигналом Передача, поступающим из общей шины системы по управляющему магистралью входу-выходу 5 устройства. Информация через блок 13 коммутации (первый информационный выход 31) поступает на вход 53 блока 17 передачи (регистр 84 на фиг.6), а сигнал Передача через блок 13 коммутации (второй информационный выход 30) - на первый вход 54 блока передачи (элемент ИЛИ 89), разрешая запись информации в блок 17 передачи. С выхода элемента ИЛИ 89 сигнал Передача поступает на выход 56 блока 17 передачи и на вход 60 блока 8 ре55гистра состояния, устанавливая соответствующий окончанию приема разРЯД регистра 18. В принимающих уст.ройствах с выхода блока коммутации сигнал Передача поступает также на информационный вход блока 19 пре рывания, с выхода которого по входувыходу 6 в процессор поступает сигнал прерывания, по которому процессор переходит на обслуживание . устройства для сопряжения. Из регист ра 18 состояния информация по входувыходу процессора считывается в процессор, который, проанализировав разряды регистра 18 определяет, что устройством сопряжения выполнена опе рация приема, и считьшает информацию из блока 17 передачи через его выход информационный 56 и вход-выход ароце сора, для чего с выхода 45 дешифратора 15 на вход элемента ИЛИ 89 блока 17 передачи поступает сигнал логической 1 . Операция общей синхронизации(ОС). Операция общей синхронизации состоит в том, что один из процессоров подсистемы вызывает прерывание всех процессоров подсистемы. Процессор, в программе которого предусмотрена инициализация операции общей синхронизации, посылает по входу-выходу процессора в дешифратор 15 код, соответствующий операции Общая син хронизация, при- этом с второго выхода 43 дешифратора 15 на второй управляющий вход 34 блока 13 коммутации поступает сигнал Общая синхронизация. Информационное слово из оперативной памяти по входу-выходу процессора поступает на первый информационный вход 33 блока 13 коммутации и по информационному входувыходу 4 магистрали устройства совместно с сигналом ОС, поступающим на управляющий вход-выход 5 устройства, в общую магистраль системы. В устройствах сопряжения всех процессоров подсистемы поступает информация по информационному входу-выходу 4 магистрали, сопровождающему сигналом ОС, поступающим из магистрали .системы по управляющему выходу-входу 5 устройства. Информация через блок 13 коммутации (первый информационный выход 31) поступает на вход 53 блока передачи, а сигнал ОС через блок 13 коммутации (информационньш выход 30)на вход управления 55 блока 17 передачи (элемент ИЛИ 90, 91, на .6), разрешая запись информации в регистр 92 блока 17 передачи. С выхода элемента ИЛИ 90 сигнал ОС (выход 57 94012 блока 17) по входу 60 заносится в соответствующий разряд регистра 18 состояния. Одновременно сигнал ОС поступает на вход блока 19 прерывания, который посылает через свой выход на вход-выход процессора сигнал требования прерывания (ТПР), по которому процессор переходит на обслуживание устройства до сопряжения.Из регистра 18 состояния информация по входу-выходу процессора считывается в процессор, который, проанализировав разряды регистра 18, определяет, что выполняется операция ОС, считывает информацию из регистра 92 блока 17 передчи через его выход 56 и входвыход процессора, для чего с выхода 45 дешифратора 15 на вход элемента ИЛИ 90 блока 17 передачи поступает сигнал логической I. Информационное слово из регистра 92 воспринимается всеми процессорами как команда, по которой необходимо перейти на новую ветвь параллельных вычислений. Введение в устройство сопряжения блока анализа условий позволяет в системе с общей магистралью одиовременно выделить несколько подсистем, решающих набор не связанных между собой задач. Формула изобретения Устройство для сопряжения процессоров в однородной вычислительной системе, содержащее блок коммутации, блок настройки, девифратор адреса регистра, блок прерывания, регистр состояния, триггер предоставления магистрали, триггер признака занятости магистрали и триггер запроса магистрали, регистр данных и триггер индивидуальной синхронизации. Причем первый и второй информациоиные входывыходы блока коммутации являются ииформациониьм входом-выходом магистрали системы и входом-выходом управления магистралью система соответственно, первые ииформациоиные входы блока коммутации, блока настройки и информационный вход дешифратора адреса регистра соединены с и ормационным входом процессора устройства, первый информационный выход блока коммутации соедииеи с ииформациониьм входом регистра даиных и вторым нформационным входом блока иастройи, соответствующий разряд первого ыхода которого подключен к первому управляющему входу блока коммутации, ,выходы соответствующих разрядов второго информационного выхода блока коммутации подключены к информационному входу блока прерывания, к инфор мационному входу соответствующего ра ряда регистра.состояния, к входу разрешения триггера предоставления магистрали, к второму входу стробирования блока настройки, с первого по четвертый выходы дешифратора адреса регистра подключены к первому входу стробирования блока настройки, к второму управляющему входу блока коммутации, к информационному входу триггера запроса магистрали и к входу синхронизации триггера индивидуальной синхронизации соответственнее, информационные входы соответствующих разрядов регистра состояния подключе ны к соответствующим разрядам второго выхода блока предоставления магистрали, выход которого подключен также к третьему входу блока коммутации, информационный вход триггера индивидуальной синхронизации и вход синхронизации триггера запроса магистрали являются входами соответствующих разрядов информационного входа процессора устройства, выходы блока прерьшания, регистра состояния и регистра данных образует выход процессора устройства, выход триггера запроса магистрали и признака занятости магистрали подключены к информационному входу и входу синхронизации триггера предоставления магистрали соответственно, информацион ный вход и выход триггера признака занятости магистрали являются входом и выходом импульса опроса устройства соответственно, причем блок настройки содержит регистр, дешифратор и первую и вторую группы элементов И, первые входы которых образуют второй и первый входы стробирования блока настройки соответственно, первая группа вторых входов элементов И первой группы и вторые входы элементов И второй группы соединены с входами соответствующих разрядов соответственно первого и второго информа ционных входов блока настройки, выходы элементов И первой и второй Групп подключены к соответствующим разрядам информационного входа регистра, отличающееся тем, что, с целью расширения класса решаемых.задач за счет обеспечения одновременного функционирования нескольких подсистем процессоров, репгающих по параллельным программам несвязанные задачи, в него введены три элемента ИЛИ, первые и вторые входы первого и второго элементов ИЛИ соеди- . нены с выходом соответствующего разряда второго информационного выхода блока коммутации и с пятым выходом дещифратора адреса регистра соответственно, выходы первого и второго элементов ИЛИ подключены к информационным входам соответствующих разрядов регистра состояния и к первому и второму входам третьего элемента ИЛИ, выход которого подключен к входу синхронизации регистра данных, щестой выход дешифратора адреса регистра подключен к соответствующему разряду информационного входа регистра состояния, блок анализа условий, содержащий щесть элементов И и два элемента ИЛИ, первый вход первого элемента И и выход третьего элемента И являются входом и выходом признака частичной синхронизации устройства, первый вход шестого элемента И и выход пятого элемента И являются входом и выходом признака общей синхронизации устройства, выход первого элемента И подключен к первому входу первого элемента ИЛИ блока анализа условий, выход которого подключен к первым входам второго и четвертого элементов И, выходы которых подключены к первьтм входам третьего элемента И и второго элемента ИЛИ блока анализа условий соответственно, выход которого подключен к первому входу пятого элемента Ник информационному входу соответствующего разряда регистра состояния, выходы соответствующих разрядов первого выхода блока настройки соединены с объединенными вторыми входами первого и пятого элементов И, с вторыми входами первого элемента ИЛИ блока анализа условий и четвертого элемента И и с объединенными вторыми входами третьего и шестого элементов И, выход щестого элемента И подключен к второму входу второго элемента ИЛИ блока анализа условий, выход триггера индивидуальной синхронизации подключен к второму входу второго элемента И и к третьему входу четвертого элемента Hi выходы элементов первой и второй групп и регистра блока настройки об15127394016

разуют второй И первый выходы блока ционного входа и с первым входом настройки соответственно, информаци- стробирования блока настройки, выход онный вход и выход стробирования де- дешифратора соединен с второй трупшифратора соединены с входом соот- пой вторых входов элементов И первой етствующих разрядов первого информа- $ группы.

I I

| Устройство для сопряжения распределенных вычислительных систем | 1972 |

|

SU479103A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 758128, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1984-12-04—Подача