Изобретение относится к вычисительной технике и может быть использовано для построения высокопрозводительных многопроцессорных вычислительных систем, предназначенных для обработки данных в реальном масштабе времени.

Цель изобретения - сокращение оборудования.

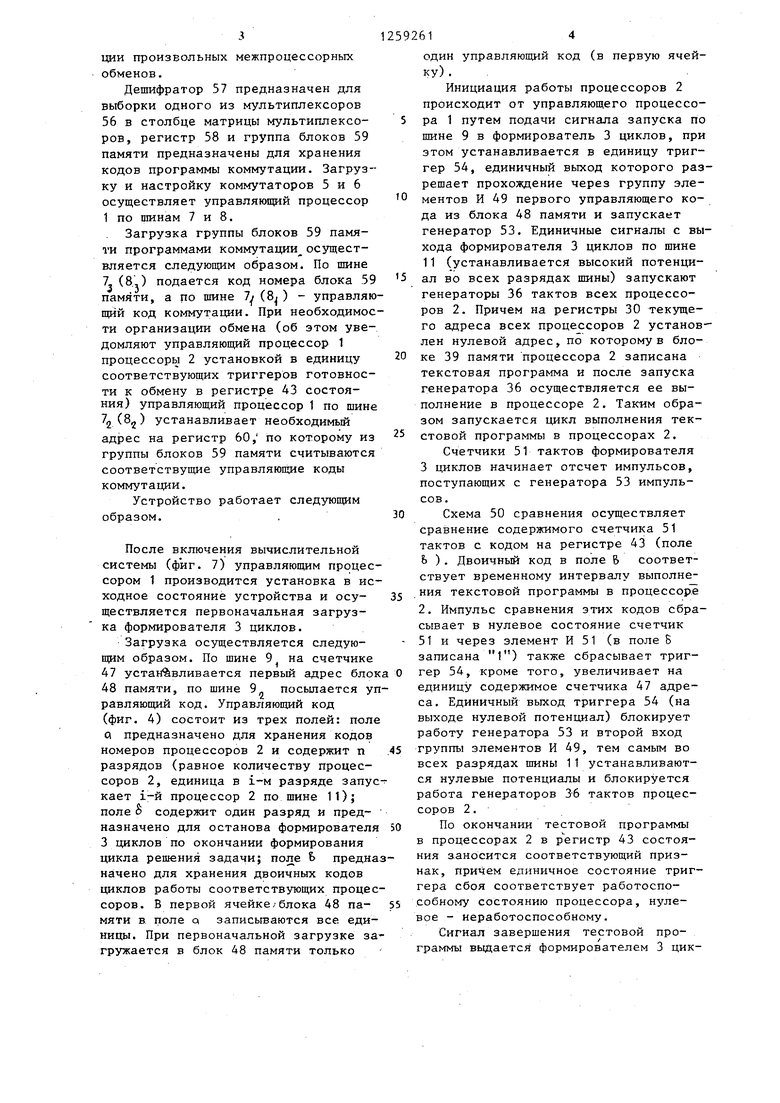

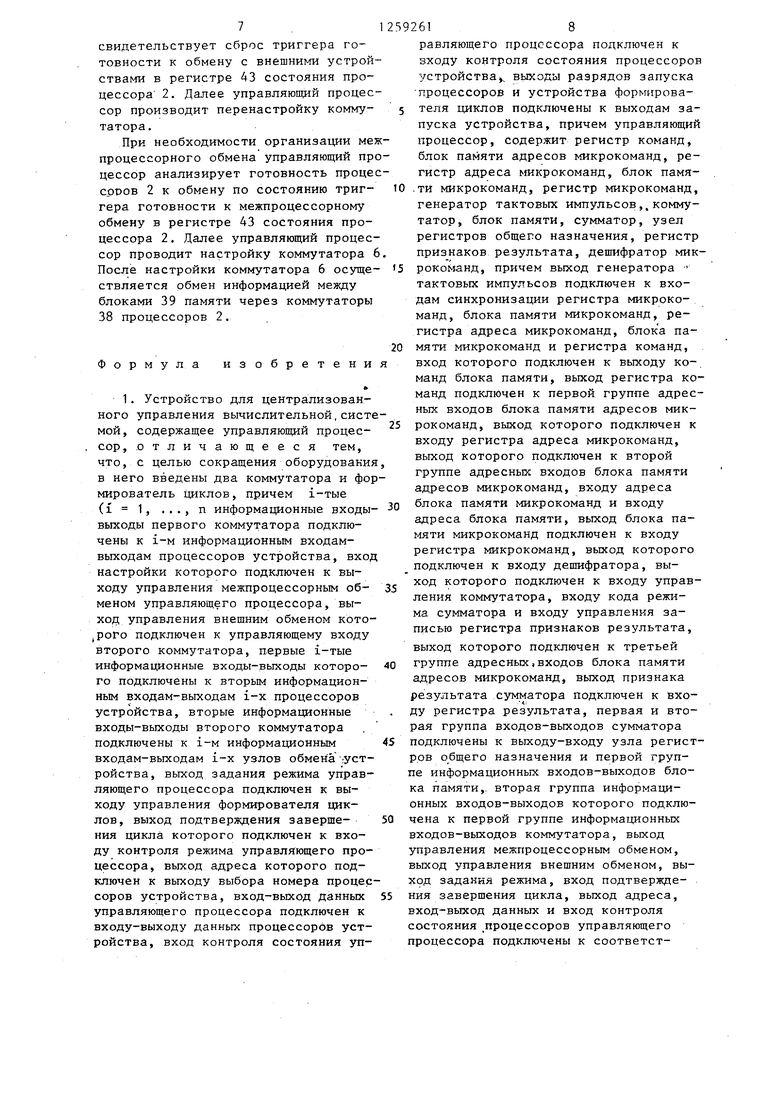

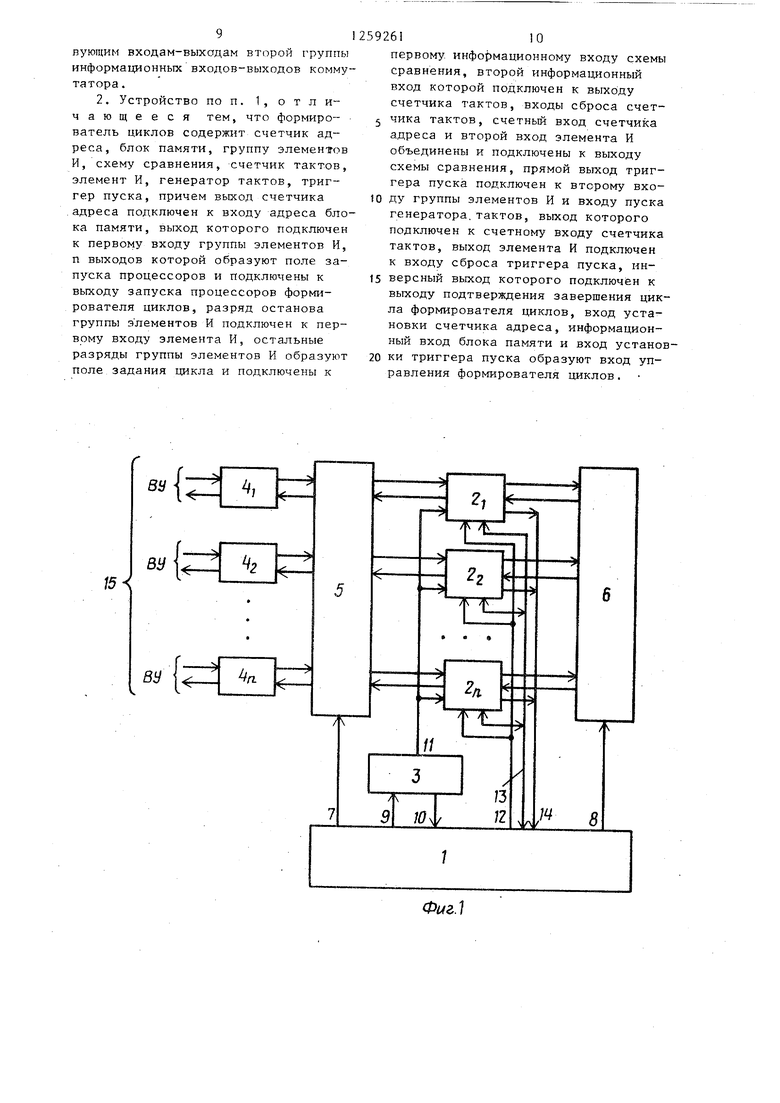

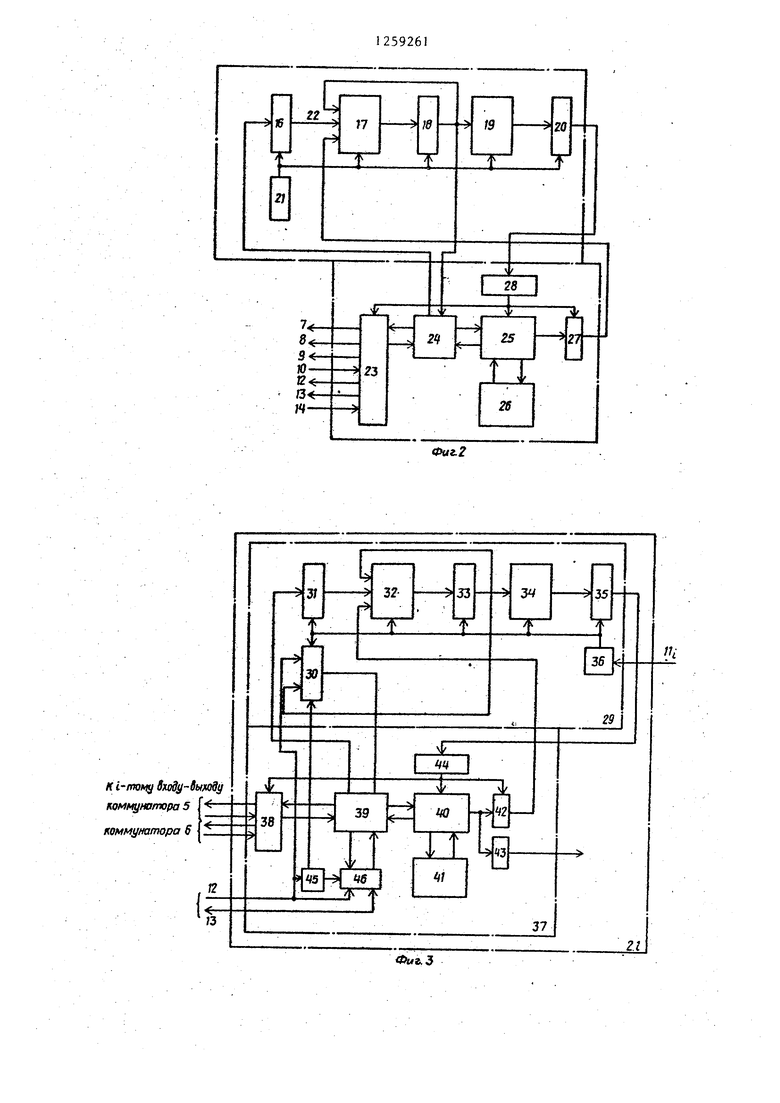

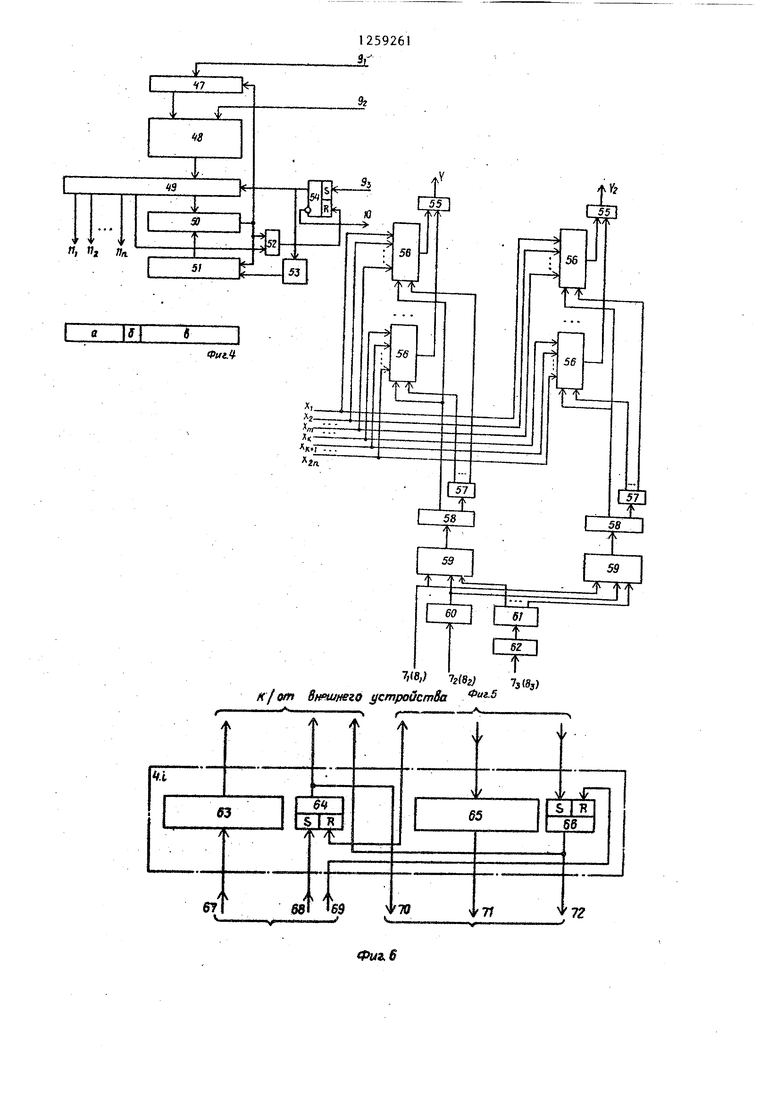

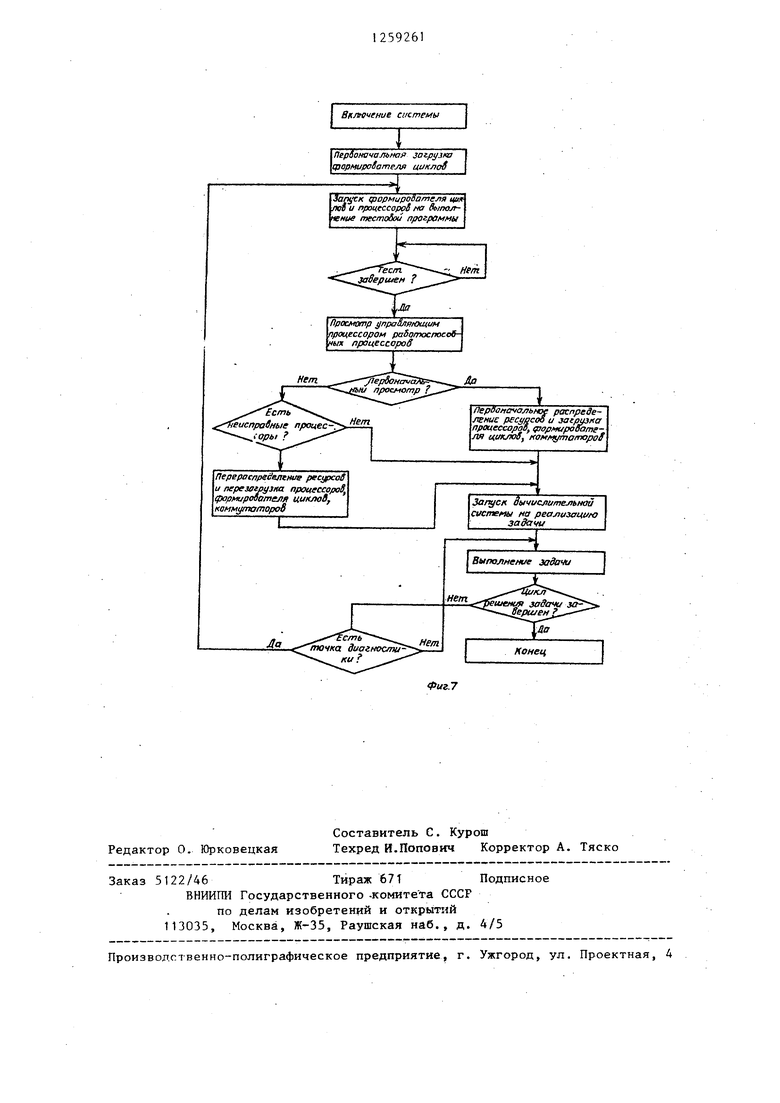

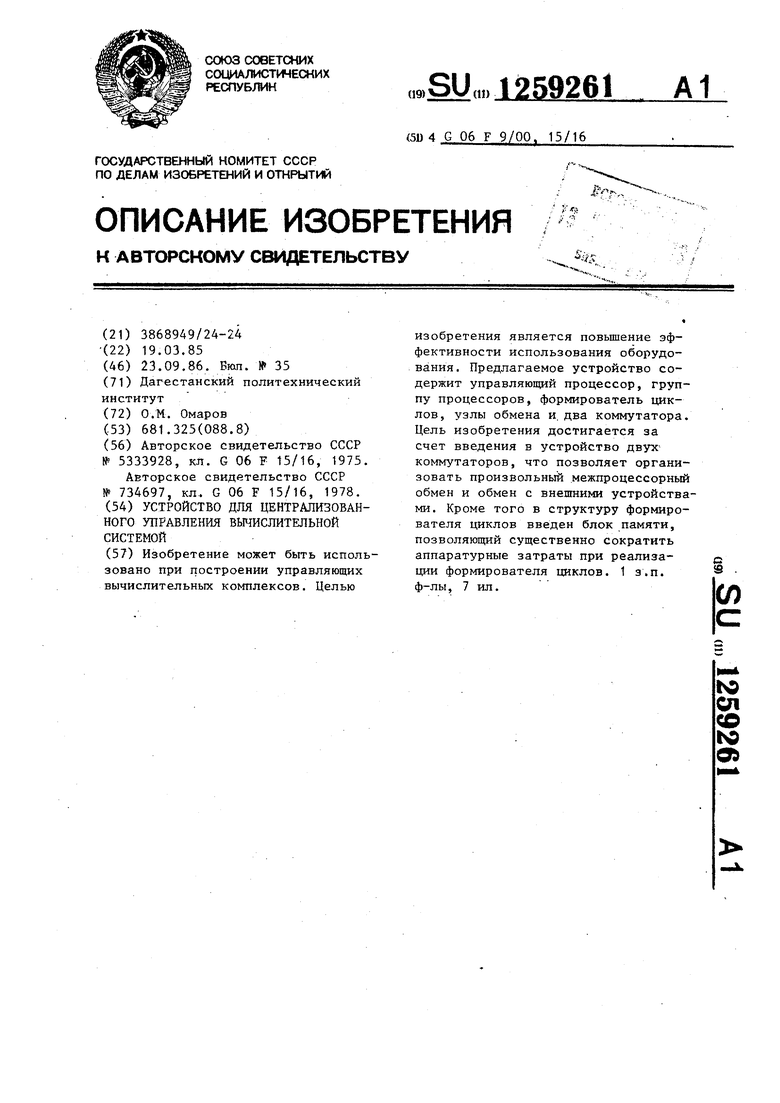

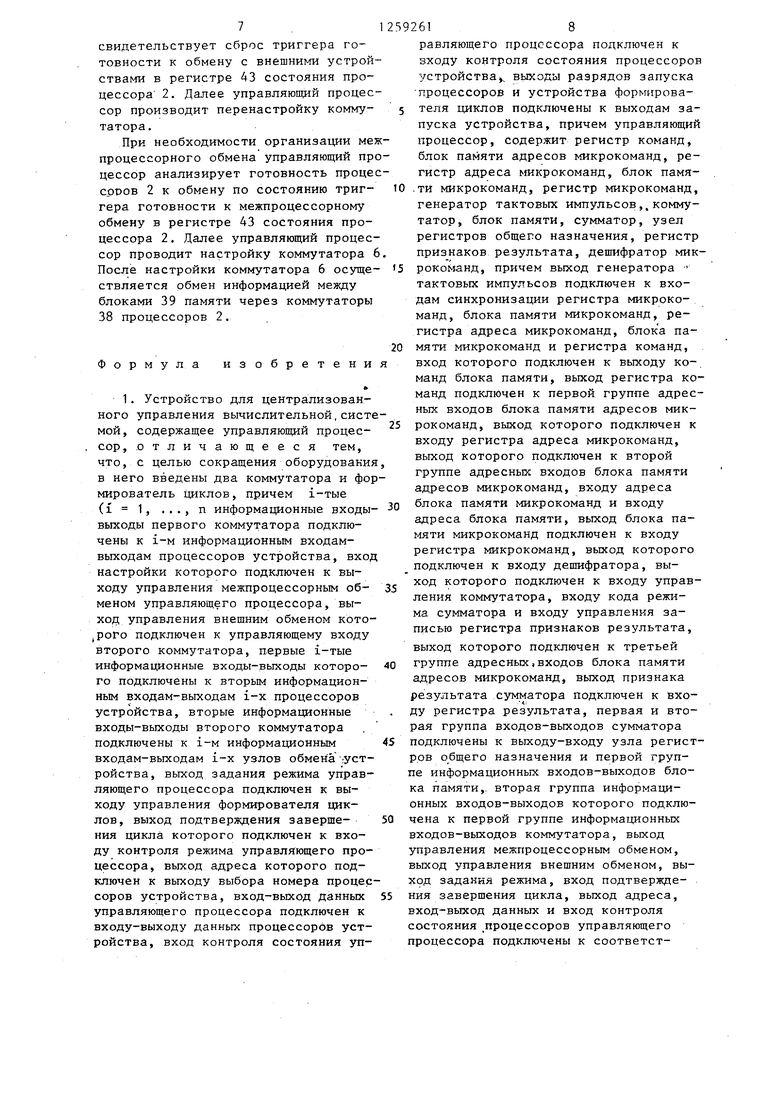

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - пример схемы реализации управляющего процессора; на фиг. 5 - пример схемы реализации процессора; на фиг. 4 - структурная схема формирователя циклов; на фиг. 5 - пример схемы реализации коммутаторов; на фиг. 6 - пример схемы реализации узла обмена; на фиг. 7 - упрощенная блок-схема алгоритма функционирова- ния вычислительной системы.

Система содержит (фиг. 1) управляющий процессор 1, группу процессоров 2 -2. ; формирователь 3 циклов, узлы , обмена, коммутатор 5 внеш- Них обменов, коммутатор 6 межпроцессорных обменов, шины 7 и 8 управления коммутаторами 5 и 6, шины 9 и 10 управления формирователем 3 циклов, выходную Инну 11 формирователя 3 циклов, шины 12-14 управления группой процессоров 2, входы-выходы 15 устройства.

Управляющий процессов 1 (фиг. 2) состоит из регистра 16 команд, блока 17 памяти адресов микрокоманд, регистра 18 адреса микрокоманд, блока 19 памяти микрокоманд, регистра 20 микрокоманд, генератора 21 тактовых импульсов, выхода 22 регистра команд, коммутатора 23, блока 24 памяти, сумматора 25, блока 26 регистров общего назначения, регистра 27 признаков результата и дешифратора 28 микрокоманд.

Каждый процессор 2 содержит (фиг, 3) блок 29 управления, содержащий регистр 30 текущего адреса команд, регистр 31 команд, блок 32 памяти адресов микрокоманд, регистр 33 адреса микрокоманд, блок 34 памяти микрокоманд, регистр 35 микрокоманд, генератор 36 тактовых импульсов, и блок 37 сложения, включающий коммутатор 38, блок 39 памяти, сумматор 40, блок 41 регистров общего назначения, регистр 42 признаков результата, регистр 43 состояния, де0

5

20

25

30

35

40

45

50

55

шифратор 44 микрокоманд, депмфратор 45 номера процессора и коммутатор 46, Регистр 43 состояния содержит три триггера: триггер сбоя, триггер готовности к обмену с внешними устройствами и триггер готовности и межпроцессорному обмену.

Формирователь 3 циклов содержит (фиг. 4) счетчик 47 адреса, блок 48 памяти, группу элементов И 49, схему 50 сравнения, счетчик 51 тактов, элемент И 52, генератор 53 тактовых импульсов и триггер 54 пуска.

Коммутаторы 5 и 6 имеют одинаковую структуру и содержат 2п входов и 2п выходов. Коммутаторы содержат (фиг. 5) группу элементов ИЛИ 55, матрицу мультиплексоров 56, группу дешифраторов 57, группу регистров 58, группу блоков 59 памяти, регистр 60, дешифратор 61 и регистр 62.

Узел обмена содержит (фиг. 6) выходной регистр 63, триггер 64, входной регистр 65, триггер 66, входные шины 67-69 и выходные шины 70-72.

Функционирование системы определяется управляющими программа:ми, записанными в блок 24 памяти управляющего процессора 1, загрузка .и обмен информацией между управляющим процессором 1 и процессорами 2 осуществляется по шинам 12 и 13. Для этого управляющий процессор 1 по шине 12 выдает код номера соответствукяцего процессора 2, который дешифрируется дешифратором 45, в результате чего открывается коммутатор 46 и организуется обмен информаи;ией между блоком 39 памяти соответствующего процессора 2 и управляющим процессором 1 (блоком 24 памяти) через шину 13.

Цикл задачи задается формирователем 3 циклов. При выходе из строя любого из процессоров 2 обеспечивается передача задачи, решаемой на нем и на другие процессоры. Осуществляется это управляющим процессором путем перезагрузки программ и данньк в другие процессоры (в блоки 39 памяти процессоров 2) по шинам 12 и 13. Цри этом меняется цикл решения задачи в исправных процессорах путем записи и формирователь 3 циклов новых кодов управляющих процессоров 1.

Коммутатор 5 предназначен для организации обмена между любьпv и из процессоров 2 и узлов 4 обмена, коммутатор 6 предназначен для организа3

ции произвольных межпроцессорных обменов.

Дешифратор 57 предназначен для выборки одного из мультиплексоров 56 в столбце матрицы мультиплексоров, регистр 58 и группа блоков 59 памяти предназначены для хранения кодов программы коммутации. Загрузку и настройку коммутаторов 5 и 6 осуществляет управляющий процессор 1 по шинам 7 и 8.

Загрузка группы блоков 59 памяти программами коммутации осуществляется следующим образом. По шине 7. (8.) подается код номера блока 59 памяти, а по шине 7 (8 ) - управляющий код коммутации. При необходимости организации обмена (об этом уведомляют управляющий процессор 1 процессоры 2 установкой в единицу соответствующих триггеров готовности к обмену в регистре 43 состояния) управляющий процессор 1 по шине (8 ) устанавливает необходимый адрес на регистр 60, по которому из группы блоков 59 памяти считываются соответствущие управляющие коды коммутации.

Устройство работает следующим образом.

После включения вычислительной системы (фиг. 7) управляющим процессором 1 производится установка в исходное состояние устройства и осуществляется первоначальная загрузка формирователя 3 циклов.

Загрузка осуществляется следующим образом. По шине 9 на счетчике

47устанавливается первый адрес блок

48памяти, по шине 9 посылается уп

равляющий код. Управляющий код (фиг. 4) состоит из трех полей: поле Q предназначено для хранения кодов номеров процессоров 2 и содержит п разрядов (равное количеству процессоров 2, единица в i-м разряде запускает i-й процессор 2 по шине 11); поле Ь содержит один разряд и предназначено для останова формирователя 3 циклов по окончании формирования цикла решения задачи; поле Ь предназначено для хранения двоичных кодов циклов работы соответствующих процессоров. В первой ячейке/ блока 48 па- мяти в поле Q записываются все единицы. При первоначальной загрузке загружается в блок 48 памяти только

го

15

20

25

35

О

Ъ

50 55

2592614

один управляющий код (в первую ячейку) .

Инициация работы процессоров 2 происходит от управляющего процессо- 5 ра 1 путем подачи сигнала запуска по шине 9 в формирователь 3 циклов, при этом устанавливается в единицу триггер 54, единичный выход которого разрешает прохождение через группу элементов И 49 первого управляющего кода из блока 48 памяти и запускает генератор 53. Единичные сигналы с выхода формирователя 3 циклов по шине 11 (устанавливается высокий потенциал во всех разрядах шины) запускают генераторы 36 тактов всех процессоров 2. Причем на регистры 30 текущего адреса всех процессоров 2 установлен нулевой адрес, по которому в блоке 39 памяти процессора 2 записана текстовая программа и после запуска генератора 36 осуществляется ее выполнение в процессоре 2. Таким образом запускается цикл выполнения текстовой программы в процессорах 2.

Счетчики 51 тактов формирователя 3 циклов начинает отсчет импульсов, поступающих с генератора 53 импульсов.

Схема 50 сравнения осуществляет сравнение содержимого счетчика 51 тактов с кодом на регистре 43 (поле Ь ). Двоичный код в поле & соответствует временному интервалу выполнения текстовой программы в процессоре 2. Импульс сравнения этих кодов сбрасывает в нулевое состояние счетчик 51 и через элемент И 51 (в поле Б записана 1) также сбрасывает триггер 54, кроме того, увеличивает на единицу содержимое счетчика 47 адреса. Единичный выход триггера 54 (на выходе нулевой потенциал) блокирует работу генератора 53 и второй вход группы элементов И 49, тем самым во всех разрядах шины 11 устанавливаются нулевые потенциалы и блокируется работа генераторов 36 тактов процессоров 2.

По окончании тестовой программы в процессорах 2 в регистр 43 состояния заносится соответствующий признак, причем единичное состояние триггера сбоя соответствует работоспособному состоянию процессора, нулевое - неработоспособному.

Сигнал завершения тестовой программы выдается формирователем 3 цик30

лов с нулевого выхода (высокий потенциал) триггера 54 по шине 10, который поступает через коммутатор 23 управляющего процессора 1 в блок 24 памяти, где анализируется управляющим процессором 1. Далее управляющий процессор анализирует содержимое регистра 43 состояния процессора 2, для чего по шине через коммутатор 23 заносит в блок 24 памяти. Определив количество и номера работоспособных процессоров 2, управляющий процессор 1 осуществляет распределение ресурсов и производит загрузку процессоров 2 программами и данными следующим образом. По шине 12 выдается номер процессора 2, который дешифруется дешифратором 45,и открывается коммутатор 46, и по шине 13 осуществляется загрузку блока 39 памяти процессора 2. Кроме того, на регистре 30 текущего адреса команд процессора 2 устанавливается начальный адрес ячейки выполняемой программы. Затем осуществляется загрузка формирователя 3 циклов, по шине 9 вьщается адрес ячейки блока 48 памяти, а по шине 92 - управляющий код. По окончании загрузки блока 48 памяти в счетчик 47 записывается начальный адрес ячейки программы фор1ушрования циклов решения задачи. Далее управляющий процессор 1 производит запуск формирователя 3 циклов на решение задачи. Для этого по шине 9д производится установка в единицу триггера 54. При решении задачи в программах процессоров 2 предусматриваются точки диганостики

по достижении которых на регистре 30 текущего адреса команд процессоров 2 устанавливается нулевой адрес (адрес программы тестовой проверки), а формирователь 3 циклов осуществляет запуск процессоров 2 на реализацию тестовой : программы. По окончании тестовой I программы срабатывает схема 50 сравнения (в поле В данного управляющего кода записана 1) и сбрасывается счетчик 51, блокируется генератор 53 импульсов, увеличивается на единицу содержимое счетчика 47, а также сбрасываешься триггер 54, нулевой выход которого оповещает по шине 10 управляющий процессор 1 о завершении тестовой программы. Далее управляющий процессор 1 осуществляет проверку работоспособности процессоров, т.е. анализирует состояние триггера сбоя регистра из состояния процессоров 2. Если все процессоры 2 оказались работоспособ- ными, управляющий процессор 1 осуществляет запуск формирователя 3 циклов, а следовательно, и процессоров 2 на продолжение вьтолнения решаемой задачи. При выходе из строя

одного или нескольких процессоров 2 управляющий процессор 1 производит перераспределение ресурсов и перезагрузку процессоров 2 программами и данными, формирователь 3 циклоп - новыми управляюш;ими кодами, а коммутаторы - новыми соответствующими кодами коммутации. Далее управляющий процессор 1 запускает формирователь 3 циклов на продолжение выполнения

решаемой задачи.

При необходимости организапри обмена информацией между процессорами 2 и внешними устройствами управляющий процессор 1 анализирует готовность процессора 2 к обмену по состоянию триггера готовности к обмену с внешними устройствами в регистре 43 состояния процессора 2. Д;злее управляющий процессор производит настройку коммутатора 5, для чего по шине 7 в регистр 60 заносится адрес , по которому с блоков 59 памяти считываются управляющие коды настройки, при этом осуществляется подключение

соответствующих входов коммутатора к выходам. Обмен информацией мезвду процессором 2 и внешними устройствами осуществляется через узел 4 обмена, обеспечивающий передачу информационньгх и управляющих сигналов. Вьщаваемая с процессора 2 информация с блока 39 памяти через коммутатор 38 по шине 67 заносится в выходной регистр 63, по шине 68 выдается

сигнал сопровождения информации, устанавливающий триггер 64 в единичное состояние. Отсутствие сигнала на шине 70 свидетельствует о приеме внешним устройством информации о готовности приема новой информации. Принимаемая информация поступает с входного регистра 65 по шине 71 через коммутатор 38 в блок 39 памяти и сопровождается сигналом по шине 72.

Сброс триггера 66 по шине 69 свидетельствует о приеме процессором 2 информации и готовности к приему новой информации. Об окончании обмена

7

свидетельствует сброс триггера готовности к обмену с внешними устройствами в регистре 43 состояния процессора 2. Далее управляющий процессор производит перенастройку коммутатора.

При необходимости организации межпроцессорного обмена управляющий процессор анализирует готовность процессоров 2 к обмену по состоянию триггера готовности к межпроцессорному обмену в регистре 43 состояния процессора 2. Далее управляющий процессор проводит настройку коммутатора 6. После настройки коммутатора 6 осуществляется обмен информацией между блоками 39 памяти через коммутаторы 38 процессоров 2.

1

Формула изобретени

1. Устройство для централизованного управления вычислительной,систмой, содержащее управляющий процес- отличающееся тем, с целью сокращения оборудовани

сор,

ЧТО,

в него введены два коммутатора и фомирователь циклов, причем i-тые (i 1, ..., п информационные входы выходы первого коммутатора подключены к i-M информационным входам- выходам процессоров устройства, вхо настройки которого подключен к выходу управления межпроцессорным обменом управляющего процессора, выход управления внешним обменом кото ,рого подключен к управляющему входу второго коммутатора, первые i-тые информационные входы-выходы которого подключены к вторым информационным входам-выходам i-x процессоров устройства, вторые информационные входы-выходы второго коммутатора подключены к i-м информационным входам-выходам i-x узлов обмена (Уст- ройства, выход задания режима управляющего процессора подключен к выходу управления формирователя циклов, выход подтверждения заверще- ния цикла которого подключен к входу контроля режима управляющего процессора, выход адреса которого подключен к выходу выбора номера процессоров устройства, вход-выход данных управляющего процессора подключен к входу-выходу данных процессоров устройства, вход контроля состояния уп

35

40

305

2592618

равляющего процессора подключен к входу контроля состояния процессоров устройства,, выходы разрядов запуска процессоров и устройства формирова- 5 теля циклов подключены к выходам запуска устройства, причем управляющий процессор, содержит регистр команд, блок памяти адресов микрокоманд, регистр адреса ьшкрокоманд, блок памя- 10 .ти микрокоманд, регистр микрокоманд, генератор тактовых импульсов,, коммутатор, блок памяти, сумматор, узел регистров общего назначения, регистр признаков результата, дешифратор мик- 5 , причем выход генератора тактовых импульсов подключен к входам синхронизации регистра микрокоманд, блока памяти микрокоманд, регистра адреса микрокоманд, блока па- 20 мяти микрокоманд и регистра команд, вход которого подключен к выходу команд блока памяти, выход регистра команд подключен к первой группе адресных входов блока памяти адресов мик- 25 рокоманд, выход которого подключен к входу регистра адреса микрокоманд, вьосод которого подключен к второй группе адресных входов блока памяти адресов микрокоманд, входу адреса блока памяти микрокоманд и входу адреса блока памяти, выход блока памяти микрокоманд подключен к входу регистра микрокоманд, выход которого подключен к входу дешифратора, выход которого подключен к входу управления коммутатора, входу кода режима сумматора и входу управления записью регистра признаков результата,

выход которого подключен к третьей группе адресных,входов блока памяти адресов микрокоманд, выход признака результата сумматора подключен к входу регистра результата, первая и вторая группа входов-выходов сумматора подключены к выходу-входу узла регистров общего назначения и первой группе информационных входов-выходов блока памяти,, вторая группа информационных входов-выходов которого подключена к первой группе информатдионных входов-выходов коммутатора, выход управления межпроцессорным обменом, выход управления внешним обменом, выход задания режима, вход подтверждения завершения цикла, выход адреса, вход-выход данных и вход контроля состояния процессоров управляющего процессора подключены к соответст5

0

вующим входам-выходам второй группы информационных входов-выходов коммутатора.

2. Устройство по п. 1, отличающееся тем, что формирователь циклов содержит счетчик адреса, блок памяти, группу элементов И, схему сравнения, счетчик тактов, элемент И, генератор тактов, триггер пуска, причем выход счетчика .адреса подключен к входу адреса блока памяти, выход которого подключен к первому входу группы элементов И, п выходов которой образуют поле запуска процессоров и подключены к выходу запуска процессоров формирователя циклов, разряд останова группы элементов И подключен к первому входу элемента И, остальные разряды группы элементов И образуют поле задания цикла и подключены к

первому, информационному входу схемы сравнения, второй информадаонный вход которой подключен к выходу счетчика тактов, входы сброса счет5 чика тактов, счетньш вход счетчика адреса и второй вход элемента И объединены и подключены к выходу схемы сравнения, прямой выход триггера пуска подключен к второму вхо10 ДУ группы элементов И и входу пуска генератора.тактов, выход которого подключен к счетному входу счетчика тактов, выход элемента И подключен к входу сброса триггера пуска, ин15 версный выход которого подключен к выходу подтверждения завершения цикла формирователя циклов, вход установки счетчика адреса, информационный вход блока памяти и вход установ20 ки триггера пуска образуют вход управления формирователя циклов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для централизованного управления вычислительной системой | 1987 |

|

SU1674146A1 |

| Периферийный процессор для обработки сигналов | 1985 |

|

SU1368889A1 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

Изобретение может быть использовано при построении управляющих вычислительных комплексов. Целью Изобретения является повьшение эффективности использования оборудования. Предлагаемое устройство содержит управляющий процессор, группу процессоров, формирователь циклов, узлы обмена и. два коммутатора. Цель изобретения достигается за счет введения в устройство двух коммутаторов, что позволяет организовать произвольный межпроцессорный обмен и обмен с внешними устройствами. Кроме того в структуру формирователя циклов введен блок памяти, позволяющий существенно сократить аппаратурные затраты при реализации формирователя циклов. 1 з.п. ф-лы, 7 ил. с 9 (Л ю СП ю Од

15

ВУ

Фиг.

Ki-moi 9 у-8ым8у коммунатора 5

коммунатора 6

,; 7г(8г} 7j(8j) Л /еот 8ff u//fezo tfcmpoifcmSa

Вклтчение ctrcmeMU

Пероонача лмая зарубка tpopMUpolamejw циклов

Запуск грормирооателя not и процксаро на 9i nojr- ченив тктойои программы

Просиотр прааляющам процессором работоспособ- чих процессоров

Есть

eucnfxjffHtie процес. iopbi

Первапачальное распреде- леннЕ ресдосоо и засрцзка процессороо, уюрмировате-, ля цак/юо, tfo/ / iii/rna/nopoff

nepepacnpeeejKmis ресурсов и перезагрузка npotieccopoS, дзормирооотеля иичпоб, канмутоторов

Зоп/ск оычис а/тельной системы на реализацию задали

Редактор О. Юрковецкая

Составитель С. Курош

Техред И.Попович Корректор А. Тяско

Заказ 5122/46Тираж 67Т Подписное

ВНИИПИ Государственного -комите та СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Авторское свидетельство СССР № 5333928, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутационное устройство для мультипроцессорной системы | 1976 |

|

SU734697A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-03-19—Подача