Изобретение относится к тельной технике и технике связи я может быть использовано для оргапиза- ции межресурсных связей в многопроцессорных вычислительных системах.

Цель изобретения - упрощение устройства и повьшение его быстродействия.

На фиг. 1 представлена структурная схема ком1-1утационного устройства; на фиг. 2 - пример реализации связи i-ro входа с J-M выходом матричного коммутатора; на фиг.З - граф коммутации и соответствующая ему последовательность команд (программа) коммутации, реализуемая устройством.

Коммутационное устройство содержит первый и второй дешифраторы 1 и 2, блок 3 микропрограммного управления матричный коммутатор 4, информационные входы 5 и информационные выходы 6 которого являются соответственно информационными входами и выходами устройства, последовательно соединенные счетчики 7 и 8, регистры 9-11, причем информационные выходы первого счетчика 7 подключены к адресным входам 12 первой группы матричного коммутатора 4, а информационные входы первого 7 и второго 8 счетчиков, а также первого 9 и второго 10 регистров подключены к соответствующим информационным выходам третьего регистра 11, информационные входы которого подключены к шине .13 настройки устройства, а выходы признаков - к первому и втор ому входам блока 3 уп- равления.

Информационные выходы второго ,. счетчика 8 через первый 1 дешифратор 1 соединены с настроечными входами первой группы 14 матричного коммутатора 4, настроечные входы второй группы 15 которого через второй де10

информационные выходы второго регистра 10 подключены к адресным входам второй группы 17 матричного коммутатора 4„ седьмой выход Олока 3 управления является выходом 18 готовности в устройстве.

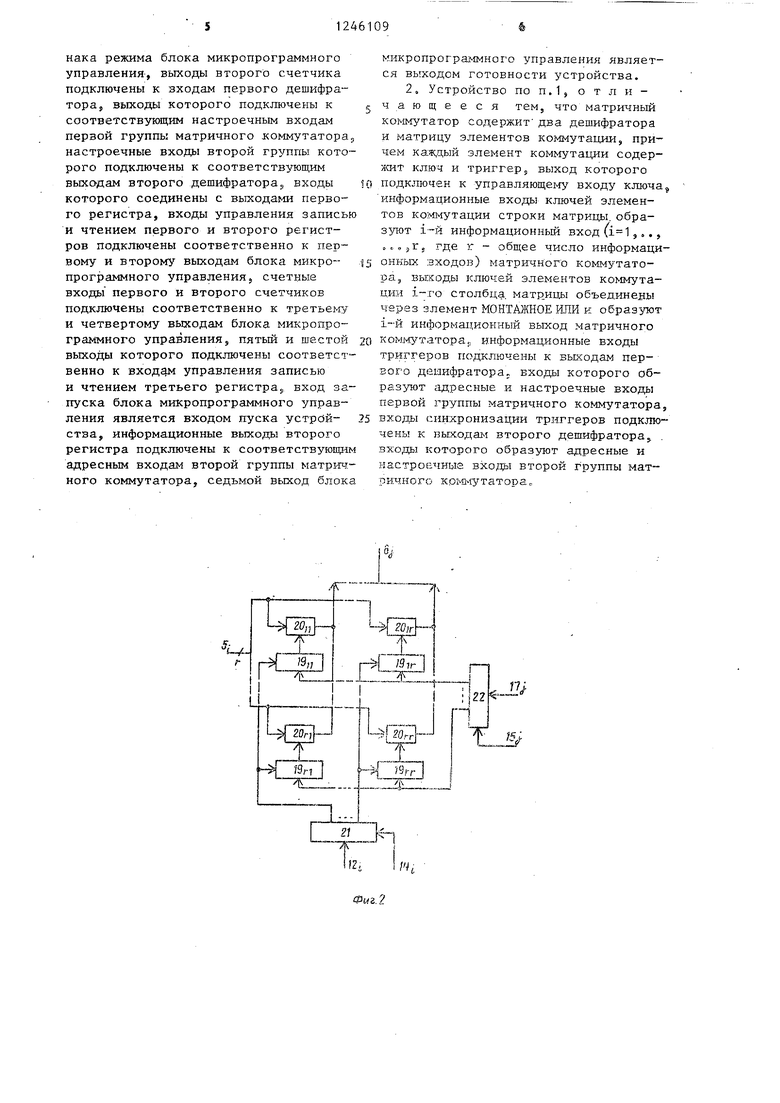

Реализация соединения i-ro входа с J-M выходом матричного коммутатора 4 представлена на фиг. 2 (,...,т, j 1,.... ,п, где m - число информационных входов, п - число информационных выходов). Связь осуществляется с помощью триггеров ,-, ключей и двух дешифраторов - 21 и 22. Каж- 15 дый информационный вход 5 (выход 6) имеет г входящих (исходящих) линий, где г - разрядность коммутируемых информационных слов.

Одноименные выходы ключей 20,-20. 20 объединяются с помощью МОНТАЖНОГО ИЛИ.,

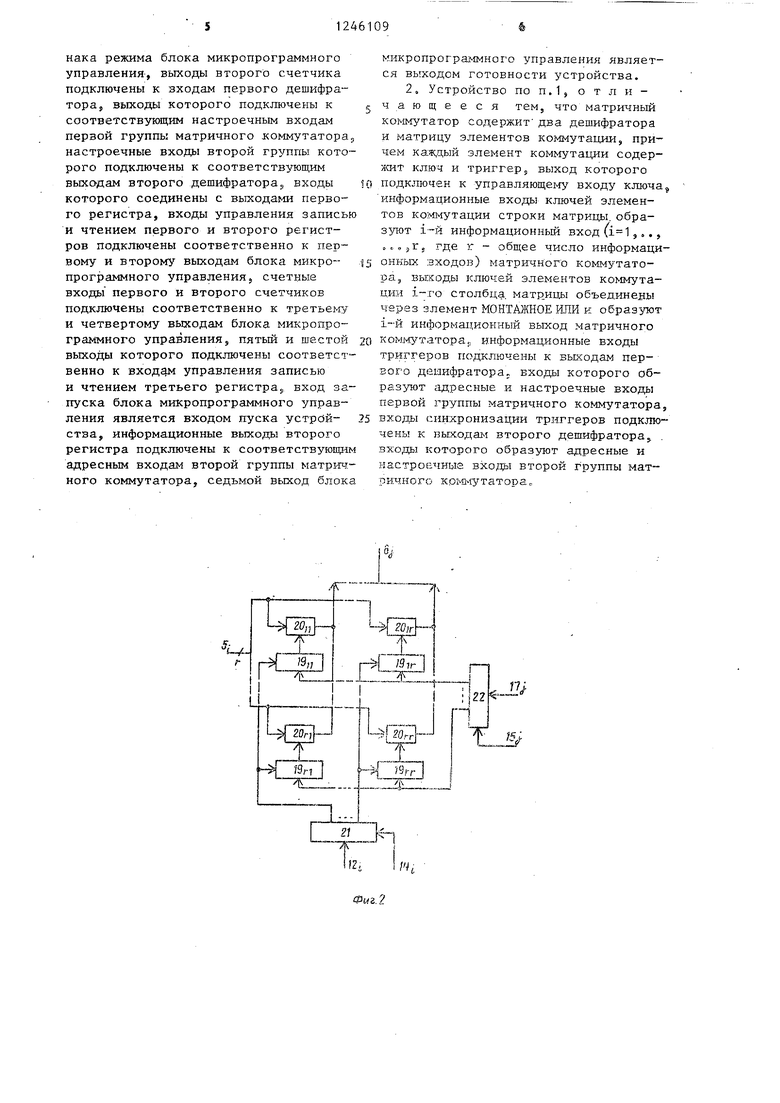

Алгоритм работы устройства показан на фиг. 3, на котором представ- лень граф коммутации, соответствующий 25 виду графа моделирования обыкновенных диф41еренциальных уравнений, и программа коммутации, реализуемая устройством. Каждая команда содержит два признака П и П и адресную часть, в которой может храниться или адрес одного из информационных входов 5 - (признак П.1), или адрес одного из информационных выходов 6 (признак П 0).

Адрес информационного входа А,- (i 1j,6) состоит из адреса какой- либо входящей линии-и адреса самого

30

35

информационного слова, а адрес А|

40

(J 1 10) - из адреса и сходящей линии и адреса информационного слова, содержэлцего эту исходящую линию.

Для организации естественной (ав томатич:еской) адресации информационных входов (выходов вершин графа ком- шифратор 2 подключены к выходам пер- мутации ) вводится признак П. вого 9 регистра, входы управления Если П., 1, то к моменту ввода записью и чтением первого 9 и второго 10 регистров подключены соответственно к первому и второму выходам блока 3 управления, счетные входы первого 7 и второго 8 счетчиков подключены соответственно к третьему и четвертому выходам блока 3 управления, пя50

следуюш;ей команды содержимое первого счетчика 7 по сигналу блока Э управления увеличивается на единицу, если П 0, то содержимое счетчика не изменяется.

Рассмотрим работу устройства при выполнении программы коммутации. Ко- манд1з1 К -К по сигналам блока 3 управления последовательно одна за другой поступают по шине 13 настройки в регистр 11. Затем блок 3 анализирует признаки II и П и формирует соответтый и шестой выходы которого подключены соответственно к входам управления записью и чтением третьего регистра 11.

Третий вход блока 3 управления является входом пуска 16 устройства.

10

2461092

информационные выходы второго регистра 10 подключены к адресным входам второй группы 17 матричного коммутатора 4„ седьмой выход Олока 3 управления является выходом 18 готовности в устройстве.

Реализация соединения i-ro входа с J-M выходом матричного коммутатора 4 представлена на фиг. 2 (,...,т, j 1,.... ,п, где m - число информационных входов, п - число информационных выходов). Связь осуществляется с помощью триггеров ,-, ключей и двух дешифраторов - 21 и 22. Каж- 15 дый информационный вход 5 (выход 6) имеет г входящих (исходящих) линий, где г - разрядность коммутируемых информационных слов.

Одноименные выходы ключей 20,-20. 20 объединяются с помощью МОНТАЖНОГО ИЛИ.,

Алгоритм работы устройства показан на фиг. 3, на котором представ- лень граф коммутации, соответствующий 25 виду графа моделирования обыкновенных диф41еренциальных уравнений, и программа коммутации, реализуемая устройством. Каждая команда содержит два признака П и П и адресную часть, в которой может храниться или адрес одного из информационных входов 5 - (признак П.1), или адрес одного из информационных выходов 6 (признак П 0).

Адрес информационного входа А,- (i 1j,6) состоит из адреса какой- либо входящей линии-и адреса самого

30

35

информационного слова, а адрес А|

(J 1 10) - из адреса и сходящей л нии и адреса информационного слова содержэлцего эту исходящую линию.

Для организации естественной (ав томатич:еской) адресации информационных входов (выходов вершин графа ком- мутации ) вводится признак П. Если П., 1, то к моменту ввода

следуюш;ей команды содержимое первого счетчика 7 по сигналу блока Э управления увеличивается на единицу, если П 0, то содержимое счетчика не изменяется.

Для организации естественной (ав томатич:еской) адресации информационных входов (выходов вершин графа ком- мутации ) вводится признак П. Если П., 1, то к моменту ввода

5

Рассмотрим работу устройства при выполнении программы коммутации. Ко- манд1з1 К -К по сигналам блока 3 управления последовательно одна за другой поступают по шине 13 настройки в регистр 11. Затем блок 3 анализирует признаки II и П и формирует соответствующие сигналы. Так, при выполнени команды V.(E 1) адресная часть команды (А) по сигналу блока 3 управления переписывается из регистра 11 в счетчик 7 и 8. После этого на выходе 18 готовности формируется сигнал запроса на вход следующей коман- .ды К в регистр 11, у которой П 0 .Таккак П.0,то сигналом блока 3 управления выполняется передача адресной части (Ар команды К из регистра 1 в регистры 9 и 10.В результате этих действий триггер 19,

, устанавливается

в единичное состояние и через ключ 20 первая входящая линия информационног входа 5 будет подключена к второй исходящей линии информационного выхода 6, Так же, как и команда Kj, выполняется команда K.j (П,0, ), причем содержимое счетчиков 7 и 8 не изменяется, т.е. производится подключение той же первой входящей линии- информационного входа 5,, но теперь уже к третьей исходящей линии информационного выхода 6, , и т.д. Изменения в последовательности формирования сигналов блоком 3 наступают посл выполнения команды К (признак П 1) В соответствии с единичным значением Щ блок 3 управления увеличивает содержимое счетчика 7 на единицу (устанавливает адрес А.) и осуществляет прием команды К в регистр 11 и передачу адреса А из регистра 11 в регистры 9 и 10, т.е. производится соединение второй входящей линии информационного входа 5 с четвертой исходящей линией информационного выхода 6, . Аналогичным образом устройством выполяются остал1 ные команды программы. После ввода всех команд программы коммутации в устройство заканчивается режим его настройки на требуемые соединения и устройство готово к выполнению обмена информацией между абонентами (процессорами, блоками памяти и т.п.),подключенными к информационным входам 5 и выходам 6 устройства.

Рассмотренный режим настройки устройства характеризуется естественной адресацией информационных входов 5 и принудительной адресацией информационных выходов 6. Кроме того устройство может работать и в более Общем режиме принудительной адресации информационных входов 5 и принудительной адресации информационных выходов 6.

Ввод в предлагаемое устройство двух счетчиков, трех регистров и организация их связей с другими узлами устройства выгодно отличает его от

известного устройства за счет упрощения коммутационного оборудования (отсутствует сложная матрица управления коммутацией, содержащая m регистров сдвига и т логических элементов И, где m - число информационных входящих линий).

Кроме того, предлагаемое у ;трой- ство имеет более высокое быстродействие в режиме его настройки на требуемые соединения, так как в известном устройстве связь дешифраторов с матричным коммутатором выполняется через матрицу управления коммутацией,

которая вносит задержку в прохождение настроечного сигнала дешифратора к элементу памяти матричного коммутатора. В худшем случае эта задержка составляет m тактов, где m - число

разрядов каждого регистра сдвига, входящего в состав матрицы управления коммутацией.

В предлагаемом устройстве за счет непосредственного подключения регистров и счетчиков к матричному коммутатору эта задержка равна 1 такту.

Формул, а изобретения

1. Коммутационное устройство, содержащее первьш и второй дешифраторы, блок микропрограммного управления И матричный коммутатор, информационные входы и выходы которого являются информационными входами и выходами устройства соответственно, о тли- чающееся тем, что, с целью упрощения, в него введены два счетчика и три регистра, причем адресные входы первой группы матричного коммутатора подключены к соответствующим выходам первого счетчика, выход переноса которого подключен к входу переноса второго счетчика, информационные входы первого и второго счетчиков, а также первого и второго регистров подключены к выходам соответствующих разрядов третьего регистра, информационные входы первого и второго старшего разрядов которого подключены к шине настройки устройства и выходы первого и второго старших разрядов третьего регистра подключены к первому и второму входам признака режима блока микропрограммного управления-, выходы второго счетчика подключены к входам первого дешифратора, выходы которого подключены к соответствующим настроечным входам первой группы матричного jcoMMyTaTopa, настроечные входы второй группы которого подключены к соответствующим выхо-дам второго дешифратора,, входы которого соединены с выходами первого регистра, входы управления записью и чтением первого и второго регистров подключены соответственно к первому и второму выходам блока микропрограммного управленияJ счетные входы первого и второго счетчиков подключены соответственно к третьему и четвертому выходам блока микропрограммного управления, пятый и шестой выхоДы которого подключены соответственно к входам управления записью и чтением третьего регистра, вход запуска блока микропрограммного управления является входом пуска устрой- ства, информационные выходы второго регистра подключены к соответствующим адресным входам второй группы матричного коммутатора, седьмой выход блока

5

микропрограммного управления является выходом готовности устройства. 2, Устройство по n.l, о т л и чающееся тем, что матричный коммутатор содержит два дешифратора и матрицу элементов коммутации, причем ка5с,цый элемент коммутации содер- лшт ключ и триггер, выход которого

(s подключен к управляющему входу ключа информационные входы ключей элементов ко умутации строки матрицы, образуют i-й информационный вход(,,., с, „ji- s г - общее число информаци5 онкых входов) матричного коммутатора, вьшоды ключей элементов коммутации i-i o столбца, матр.ицы объединены через элемент МОНТАЖНОЕ ИЛИ к образуют i-й ин(|рормационный выход матричного KOMixtj -татора,, информационные входы триггеров подключены к выходам первого дешифраторар входы которого образуют ;1дресные и настроечные входы первой группы матричного коммутатора, входы синхронизации триггеров подключены к выходам второго дешифратора, входы которого образуют адресные и настроечные входы второй группы матричного к.ом 1утатора„

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1456963A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Коммутационное устройство | 1986 |

|

SU1387006A1 |

| Устройство для коммутации сообщений | 1984 |

|

SU1247879A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

Изобретение относится к области вычислительной техники и техники связи и позволяет упростить конструкцию коммутационного оборудования. 40- Устройство содержит первый и второй дешифраторы 1 и 2, блок 3 микропрограммного управления, матричный коммутатор 4, информационные входы и выходы которого являются одноименными входами устройства, к которым подключаются коммутируемые абоненты, два счетчика 7 и 8 и регистры 9-11. Информационный вход регистра 11 служит для приема в него команд коммутации. После ввода последовательности команд программы коммутации в устройство,в матричном коммутаторе 4 фиксируются заданные соединения и устройство готово к вьшолнению обмена информацией между абонентами. 1 з.п. ф лы, 3 ил. I (/) Is5 4; Cd 18 №

- 19п1

ю

Признаки

Адресная часть

Признаки

Адресная П Пг часть

Кз К

% Кб

Редактор Н. Тупица

Составитель Н. Захарович

Техред Н.Бонкалр Корректор Л. Пилипенко

Заказ 4002/42Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фмг.З

| Устройство неординарной разовой коммутации | 1981 |

|

SU1001469A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Коммутационное устройство для вычислительной системы | 1978 |

|

SU746492A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-23—Публикация

1984-06-29—Подача