Изобретение относится к области автоматики и вычислительной техники, в частности к периферийным устройствам, и может быть использовано для ввода-вывода информации, обмена с дистационно удаленной другим периферийным устройством вычислительной машины.

Известно устройство для регистрации информации (А.С. N 1314328, G 06 F 3/02, Б. И. N 20, 1987), в состав которого входит блок приемопередачи, клавиатура, коммутатор, блок синхронизации, блок управления, индикаторы, блок формирования адреса и блок формирования вызова.

Недостатком данного устройства является низкая достоверность передаваемой информации, которая формируется в приемном устройстве.

В качестве прототипа можно выбрать известное устройство для обмена информацией (А. С. 1497619, G 06 F 13/10, N 28, 1989), содержащее блок приемопередачи, блок источников информации, блок индикации, блок синхронизации, блок центрального управления, пять дешифраторов, блок сигнализации, причем стробирующие входы первого, второго, третьего и четвертого дешифраторов соединены соответственно с первым, вторым, третьим и четвертым выходами команды блока управления, группа выходов первого дешифратора соединена с группой входов выборки блока источников информации, группа информационных выходов которого подключена через шину данных к информационным входам первого и второго регистров, блокам индикации и информационному входу-выходу блока приемопередачи, информационные вход и выход которого являются соответствующими входом и выходом устройства для подключения к информационном выходу и входу ЭВМ, первый и второй тактовые входы, вход строба байта состояния и сброса блока управления подключены соответственно к первому, второму, третьему и четвертому выходам блока синхронизации, вход сброса которого соединен с выходом начальной установки блока источников информации, а пятый выход - с тактовым входом блока приемопередачи, выходы первого и второго регистров подключены к соответствующим информационным входам блока приемников, группа выходов второго дешифратора подключена к группе режимных входов блока сигнализации, первый, второй выходы третьего дешифратора подключены соответственно к стробирующим входам первого регистра и блока индикации, сбросовый вход которого соединен со сбросовым входом второго регистра и блока синхронизации и подключен к пятому выходу команды блока управления, шестой выход команды которого подключен к синхронизирующему входу блока синхронизации, а также устройство содержит блок памяти, блок прерываний, блок задания режима работы, причем адресные входы блока приемопередачи, блока памяти, второго регистра и информационные входы первого-пятого дешифраторов через шину адреса подключены к адресному выходу блока управления, вход-выход данных которого соединен через шину данных с информационным выходом блока выбора режима работы, информационными входами-выходами блока прерываний, блока памяти, группа входов запросов блока прерываний подключена к соответствующим выходу сопровождения данных блока задания режима работы, выходам запроса прерывания блока источников информации, блока приемопередачи и группе выходов запроса прерывания блока приемников, тактовый и стробирующий входы и вход разрешения блока прерываний подключены соответственно к пятому выходу блока синхронизации и седьмому и восьмому выходам команды блока управления, первый и девятый выходы команды которого подключены соответственно к входам чтения и записи блока памяти, а вход запросов прерывания - к выходу блока прерываний, выход четвертого дешифратора подключен к стробирующему входу блока задания режима работы, первый и второй выходы пятого дешифратора - к стробирующим входам блока приемопередачи и второго регистра, управляющий вход которого соединен с третьим выходом команды блока управления и входом записи блока приемопередачи, входы выборки, чтения и сброса которого соединены соответственно с третьим выходом пятого дешифратора и четвертым и пятым выходом команды блока управления, вход выборки блока прерывания соединен с третьим выходом третьего дешифратора, десятый выход команд блока управления соединен с входом выборки блока приемников.

Недостатком данного устройства является также низкая достоверность информации, сформированной в приемном устройстве. Эта низкая достоверность информации, передаваемой дистанционно на приемное устройство с передающего устройства, определяется наличием помех разной природы в передающей среде.

Решаемой задачей предлагаемого изобретения является повышение достоверности передачи информации за счет организации режима работы приемного устройства по командам, поступающим от периферийного передающего устройства, являющимся центром сбора информации повышенной ценности. Повышенная ценность передаваемой информации требует при ее передаче обеспечения повышенной достоверности.

Решение поставленной задачи достигается тем, что в устройстве для обмена информацией, содержащем блок центрального управления и блок приемопередачи, причем последний содержит первый блок памяти, приемник и передатчик, блок сигнализации, дополнительно введены четыре элемента ИЛИ, три формирователя импульсов, элемент сравнения, семь элементов задержки импульсов, два преобразователя кодов, приемник и передатчик, три одновибратора, триггер, два элемента И, два устройства выделения импульса управления, второй блок памяти и делитель частоты, выход которого соединен с входом блока сигнализации, а установочные входы данного делителя частоты соединены с входами задания числа проверок достоверности передаваемой информации устройством, выход элемента сравнения соединен с первым формирователем импульсов, выход которого 2 непосредственно соединен с входом "Сброс" первого блока памяти и через второй элемент задержки импульсов соединен с первым входом триггера, через последовательно соединенный первый одновибратор и первый вход первого элемента ИЛИ с вторым формирователем импульсов, через второй элемент задержки импульсов с входом "Сброс" делителя частоты, а через первый вход второго элемента ИЛИ с входом "Сброс" второго блока памяти, информационные выходы первого и второго блока памяти соединены с соответствующими входами элемента сравнения, вход синхронизации которого соединен с выходом третьего элемента задержки импульсов и через четвертый элемент задержки импульсов с счетным входом делителя частоты и с первым входом первого элемента И, второй вход которого соединен с первым выходом триггера и входом второго одновибратора, выход первого элемента И соединен с вторым входом второго элемента ИЛИ, а через первый вход третьего элемента ИЛИ с входом управления первого преобразователя кодов и с первым входом четвертого элемента ИЛИ, выход второго одновибратора соединен с входом третьего элемента задержки импульсов, а через пятый элемент задержки импульсов с входом "Запись" второго блока памяти, второй выход триггера соединен с первым входом второго элемента И, второй вход которого соединен с выходом приемника и входом третьего формирователя импульсов, выход которого соединен через первое устройство выделения импульсов управления с управляющим входом второго преобразователя кодов и непосредственно с его информационным входом, выходы второго преобразователя кодов соединены с информационными входами второго блока памяти, выходы которого также соединены с информационными входами блока центрального управления, информационные выходы которого соединены с информационными входами первого блока памяти, выход управления блока центрального управления соединен с входом "Запись" первого блока памяти и через шестой элемент задержки импульсов с вторым входом третьего элемента ИЛИ, информационные входы первого преобразователя кодов соединены с выходами первого блока памяти, первый выход первого преобразователя кодов соединен с вторым входом первого элемента ИЛИ, а второй выход первого преобразователя кодов подключен через седьмой элемент задержки импульса с вторым входом триггера и непосредственно к второму входу четвертого элемента ИЛИ, выход которого через третий одновибратор соединен с третьим входом первого элемента ИЛИ, выход второго элемента соединен с четвертым входом первого элемента ИЛИ и через второе устройство выделения импульсов управления с входом "Запись" блока центрального управления, выход второго формирователя импульсов соединен с входом передатчика.

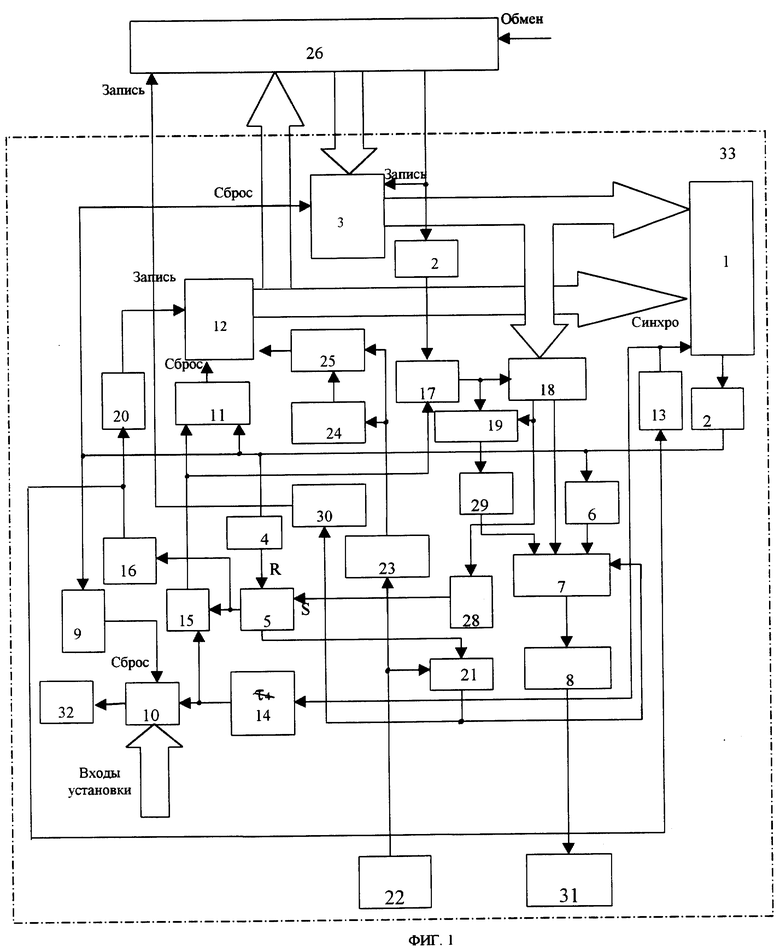

Структурная схема предлагаемого устройства приведена на фиг. 1. В устройстве для обмена информацией выход элемента сравнения ЭС 1 соединен с первым формирователем импульсов ФИ1 2. Выход первого формирователя импульсов ФИ1 2 непосредственно соединен с входом "Сброс" первого блока памяти БП1 3 и через второй элемент задержки импульсов τ1 4 соединен с первым входом триггера Тр 5, через последовательно соединенный первый одновибратор OB1 6 и первый вход первого элемента ИЛИ1 7 с вторым формирователем импульсов ФИ2 8, через второй элемент задержки импульсов τ2 9 с входом "Сброс" делителя частоты ДЧ 10, а через первый вход второго элемента ИЛИ2 11 с входом "Сброс" второго блока памяти БП2 12. Информационные выходы первого БП1 3 и второго блока памяти БП2 12 соединены с соответствующими входами элемента сравнения ЭС 1. Вход синхронизации элемента сравнения ЭС 1 соединен с выходом третьего элемента задержки импульсов τ3 13 и через четвертый элемент задержки импульсов τ4 14 с счетным входом делителя частоты ДЧ 10 и с первым входом первого элемента И1 15. Второй вход первого элемента И1 15 соединен с первым выходом триггера Тр 5 и входом второго одновибратора ОВ2 16. Выход первого элемента И1 15 соединен с вторым входом второго элемента ИЛИ2 11, а через первый вход третьего элемента ИЛИ3 17 с входом управления первого преобразователя кодов ПрК1 18 и с первым входом четвертого элемента ИЛИ4 19. Выход второго одновибратора ОВ2 16 соединен с входом третьего элемента задержки импульсов τ3 13, а через пятый элемент задержки импульсов τ5 20 с входом "Запись" второго блока памяти БП2 12. Второй выход триггера Тр 5 соединен с первым входом второго элемента И2 21, второй вход которого соединен с выходом приемника Пр 22 и входом третьего формирователя импульсов ФИ3 23. Выход третьего формирователя импульсов ФИ3 23 соединен через первое устройство выделения импульсов управления УВИУ1 24 с управляющим входом второго преобразователя кодов ПрК2 25 и непосредственно с его информационным входом. Выходы второго преобразователя кодов ПрК2 25 соединены с информационными входами второго блока памяти БП2 12. Выходы второго блока памяти БП2 12 также соединены с информационными входами блока центрального управления БЦУ 26, информационные выходы которого соединены с информационными входами первого блока памяти БП1 3. Выход управления блока центрального управления БЦУ 26 соединен с входом "Запись" первого блока памяти БП1 3 и через шестой элемент задержки импульсов τ6 27 с вторым входом третьего элемента ИЛИ3 17. Информационные входы первого преобразователя кодов ПрК1 18 соединены с выходами первого блока памяти БП1 3. Первый выход первого преобразователя кодов ПрК1 18 соединен с вторым входом первого элемента ИЛИ1 7, а второй выход первого преобразователя кодов ПрК1 18 подключен через седьмой элемент задержки импульса τ7 28 с вторым входом триггера Тр 5 и непосредственно к второму входу четвертого элемента ИЛИ4 19, выход которого через третий одновибратор ОВ3 29 соединен с третьим входом первого элемента ИЛИ1 7. Выход второго элемента И2 21 соединен с четвертым входом первого элемента ИЛИ1 7 и через второе устройство выделения импульсов управления УВИУ2 30 с входом "Запись" блока центрального управления БЦУ 26. Выход второго формирователя импульсов ФИ2 8 соединен с входом передатчика ПрД 31. Выход делителя частоты ДЧ 10 соединен с входом блока сигнализации БС 32, а установочные входы делителя частоты ДЧ 10 соединены с входами задания числа проверок достоверности передаваемой информации устройством. Все блоки кроме блока центрального управления БЦУ 26 составляют блок приемопередачи 33.

Элемент сравнения 1 может быть реализован, например, в виде цифрового компаратора типа К561ИП2 при его каскадном соединении для обеспечения необходимого количества входов сравнения.

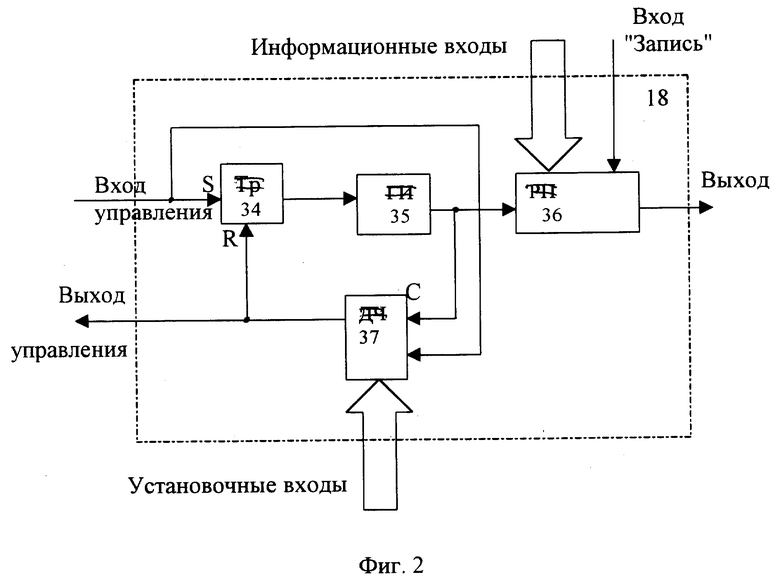

Пример реализации первого (ведущего) преобразователя кодов ПрК 18, осуществляющего преобразование параллельного кода в последовательный, приведен на фиг. 2. В данном устройстве S-вход триггера Тр 34 соединен с входом управления преобразователя кодов ПрК 18, а выход триггера Тр 34 соединен с входом управления генератора импульсов ГИ 35, выход которого соединен с тактирующим входом регистра памяти РП 36, с счетным входом делителя частоты ДЧ 37. Входом установки в исходное состояние делителя частоты ДЧ 37 соединен с S-входом триггера Тр 34, к R-входу которого подключены выход делителя частоты ДЧ 37 и выход управления преобразователя кодов ПрК 18. Информационные входы регистра памяти РП 36 соединены с входами установки кодов преобразователя кодов ПрК 18, а информационные входы делителя частоты ДЧ 37 соединены с входами установки количества разрядов передаваемой информации. Выход регистра памяти РП 36 соединен с выходом преобразователя кодов ПрК 18, а вход записи регистра памяти РП 36 соединен с входом "Запись" преобразователя кодов ПрК 18.

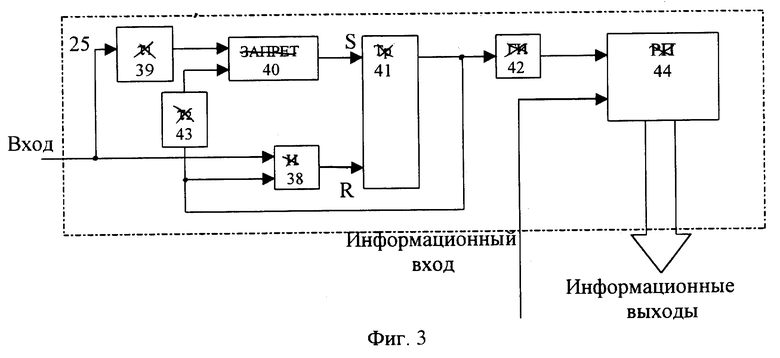

Пример реализации второго (ведомого) преобразователя кодов 25 приведен на фиг. 3. Данное устройство, осуществляющее преобразование последовательного кода в параллельный, может быть реализовано, например, в следующем виде. Вход управления преобразователя кодов ПрК 19 соединен с входом элемента И 38 и через первый элемент задержки сигналов τ1 39 с информационным входом элемента "Запрет" 40, выход которого соединен с S-входом триггера Тр 41, R-вход которого соединен с выходом элемента И 38. Выход триггера Тр 41 соединен с управляющим входом генератора импульсов ГИ 42 и с вторым входом элемента И 38, а через второй элемент задержки импульсов τ2 43 с запрещающим входом элемента "Запрет" 40. Выход генератора импульсов ГИ 42 соединен с тактирующим входом регистра памяти РП 44, информационные выходы которого соединены с информационными выходами преобразователя кодов ПрК 19, а информационный вход которого соединен с информационным входом регистра памяти РП 44. Причем частоты генераторов первого и второго преобразователей кодов 35, 42 должны быть равны.

В исходном состоянии в ОЗУ центрального блока управления 26 занесена информация, передачу которой необходимо осуществить. В ПЗУ заложена программа, обеспечивающая работу устройства по накоплению и хранению в устройстве информации, которая в дальнейшем будет передана на центральное устройство. Центральный блок управления 26 может быть реализован, например, на микропроцессоре (например, К580ИК80), PICконтроллере (например, PIC16C5X) или микроЭВМ (например, СОР800) с соответствующей обвязкой для их функционирования.

В исходном состоянии триггер Тр 5 установлен в состояние, при котором второй элемент И2 21 открыт для прохождения сигнала с выхода приемника 22 на вход первого элемента ИЛИ1 7. Блоки памяти БП1 3, ВП2 12 установлены в нулевое состояние по соответствующим входам установки в исходное состояние. Триггеры 34, 41 преобразователей кодов ПрК1 18, ПрК1 25 установлены в исходное состояние по соответствующим входам установки их в исходное состояние (на схеме не приведены), обеспечивающим торможение генерации соответственно генераторов ГИ1 35, ГИ2 42. В делитель частоты ДЧ 37 первого преобразователя кодов ПрК1 18 занесен коэффициент деления, равный количеству битов в пачке передаваемой информации. В делителе частоты Дч 10 по входам установки введен коэффициент деления, равный допустимому количеству циклов передачи данного пакета информации.

Устройство для обмена информацией работает следующим образом. В исходном состоянии в ОЗУ блока центрального управления БЦУ 26 передающего устройства сформирован необходимый для передачи объем информации, а приемное устройство установлено в исходное состояние, обеспечивающее прием передаваемой информации. При установлении канала связи между двумя устройствами данного типа, один из которых находится в центре сбора информации, а второй в центре приема, на устройстве, находящемся в центре передачи информации (с которого начинается передача информации), оператором нажимается кнопка "Обмен" блока центрального управления БЦУ 26, и первое устройство запускается на передачу информации на второе устройство. При этом через порт выхода блока центрального управления БЦУ 26 информация, накопленная в блоке центрального управления БЦУ 26, поступает на информационные входы первого блока памяти БП1 3. Сигналом "Запись" с блока центрального управления БЦУ 26 эта информация записывается в первый блок памяти БП1 3 и, пройдя на его выходы, поступает на входы первого преобразователя кодов ПРК1 18, который подготавливает ее для передачи по каналу связи, т.е. преобразует ее, например, из параллельного в последовательный вид. Сигналом "Запись" первого блока памяти БП1 3, задержанным на шестом элементе задержки импульса τ6 27, через третий элемент ИЛИ3 17 включается по входу управления на преобразование первый преобразователь кодов ПрК1 18. При этом в регистр памяти РП 36 первого преобразователя кодов ПрК1 18 заносится передаваемая информация с выхода первого блока памяти БП1 3. Сигналом управления с выхода третьего элемента ИЛИ3 17 включается триггер Тр 34 первого преобразователя кодов ПрК1 18 и запускается генератор импульсов ГИ 35, выходные импульсы которого являются тактирующими для регистра памяти РП 36 и на его выходе последовательно появляются разряды передаваемой информации. Тактовые импульсы подсчитываются делителем частоты Дч 37 и при совпадении кода, накопленного в нем, и кода установленного по установочным входам (равного количеству битов передаваемой информации), делитель частоты Дч 37 срабатывает и устанавливает триггер Тр 34 в исходное состояние, выключая генератор импульсов ГИ 35. При этом информация, записанная в регистре памяти РП 34 первого преобразователя кодов ПрК1 18, появится поразрядно на его выходе, а импульс управления, запускающий первый преобразователь кодов ПрК1 18 на преобразование, поступает через четвертый элемент ИЛИ4 9 на вход третьего одновибратора ОВ3 29, который формирует импульс начала передаваемого пакета информации. Данный импульс отличается по параметрам от информационных импульсов, передача которых последует за этим. По окончании передачи информации импульс с выхода делителя частоты Дч 37, пройдя через четвертый элемент ИЛИ4 19, поступает также на третий одновибратор ОВ3 29. При этом также формируется импульс окончания передаваемого пакета информации, отличающийся от передаваемых информационных сигналов. Информация с выхода первого преобразователя кодов ПрК1 18 совместно с импульсами начала и конца передаваемой пачки через первый элемент ИЛИ1 7 и второй формирователь импульсов ФИ1 8 поступает на вход передатчика ПрД 31. Далее передаваемая информация с передающей части одного блока приемопередачи, пройдя по каналу связи, поступает в приемную часть другого блока приемопередачи, структура которых совпадает.

Одновременно выходной импульс управления первого преобразователя импульсов ПрК1 18 поступает через седьмой элемент задержки импульса τ7 28 и взводит триггер Тр 5. При этом закрывается в передающем устройстве на прохождение импульсов второй элемент B2 21 и открывается на прохождение импульсов первый элемент И1 15. Время задержки элемента τ7 28 должно быть немного меньше времени прохождения сигнала между передающей и приемной частями блоков приемопередачи для обмена информацией.

Информация, поступившая на приемник ПР 22 приемной части, проходит через третий формирователь импульсов ФИ3 23 на информационный вход второго преобразователя кодов ПрК2 25, на тактирующий вход которого поступают выделенные на первом устройстве выделения импульсов управления УВИУ1 24 импульсы начала и конца передаваемого пакета информации. При этом в регистр памяти РП 44 второго преобразователя кодов ПрК2 25 по его информационному входу под воздействием тактирующих импульсов с его генератора импульсов ГИ 41 записываются информационные импульсы из передаваемого пакета информации.

Передаваемая информация записывается в регистр памяти РП 44 второго преобразователя кодов ПрК2 25 и появляется на информационных выходах второго устройства преобразования кодов ПрК2 25.

Параллельно поступающая на вход принимающего устройства информация поступает также через открытый в исходном состоянии второй элемент И2 21 и на четвертый вход первого элемента ИЛИ1 7 принимающего устройства и далее на его передатчик ПрД 31. По второму каналу связи между устройствами со стороны приемной части информация поступает на приемник ПР 22 передающей части и проходит через третий формирователь импульсов ФИ3 23 на информационный вход второго преобразователя кодов ПрК2 25, на тактирующий вход которого поступают выделенные на первом устройстве выделения импульсов управления УВИУ1 24 импульсы начала и конца передаваемого пакета информации. При этом в регистр памяти РП 44 второго преобразователя кодов ПрК2 25 по его информационному входу под воздействием тактирующих импульсов с генератора импульсов ГИ 42 записываются информационные импульсы из передаваемого пакета информации.

При срабатывании триггера Тр 5 в передающей части передний фронт импульса с его выхода, выделенный вторым одновибратором OB2 16 и задержанный на пятом элементе задержки импульса τ5 20, поступает на вход "Запись" второго блока памяти БП2 12. При этом во второй блок памяти БП2 12 записывается информация ранее уже преобразованная во втором преобразователе кодов ПрК2 25. Через время, определяемое вторым элементом задержки импульса τ2 13, импульс с выхода второго одновибратора OB2 16 поступает на вход "Синхро" элемента сравнения ЭС 1. При совпадении кодов на его входах, которые совпадают с кодами, накопленными в первом и втором блоке памяти БП1,2 3, 12, на выходе элемента сравнения 1 формируется импульс совпадения, который поступает через первый формирователь импульсов ФИ1 2 на вход "Сброс" первого блока памяти БП1 3, на вход первого одновибратора OB1 6, а также через второй элемент ИЛИ2 11 на вход "Сброс" второго блока памяти БП2 12. Этим импульсом информация, записанная во втором блоке памяти БП2 12, стирается. Этим же импульсом с выхода первого формирователя импульсов ФИ1 2 устанавливается в исходное состояние триггер Тр 5 через время, задаваемое первым элементом задержки τ1 4, закрывая первый элемент И1 15 и включая второй элемент И2 21, а через время, задаваемое вторым элементом задержки импульсов τ2 9, в исходное состояние устанавливается и делитель частоты Дч 10, в котором до этого накапливаются импульсы с входа "Синхро" элемента сравнения ЭС 1, задерженные на четвертом элементе задержки импульсов τ4 14.

Импульс с выхода первого формирователя импульсов ФИ1 2, поступая на первый одновибратор ОВ1 6, формирует сигнал, который через первый элемент ИЛИ1 7, второй формирователь импульсов ФИ2 8 и передатчик ПрД 31 поступает на выход передающего устройства и передается по каналу связи с передающей части на вход принимающей. Первый одновибратор ОВ1 6 формирует импульс подтверждения совпадения переданной и принятой информации, и характеристики этого импульса отличаются по параметрам от информационных импульсов. Например, этот импульс может отличаться от информационных по длительности или амплитуде, что позволяет его обнаружить вторым устройством выделения импульса управления УВИУ2 30 в приемной части. Этот импульс, поступая через приемник ПР 22 принимающей части и пройдя через открытый второй элемент И2 21 принимающей части, поступает на вход второго устройства выделения импульса управления УВИУ2 30, где обнаруживается и подтверждает правильность принятого в принимающей части информации. При этом вторым устройством выделения импульсов управления УВИУ2 30 формируется импульс на занесение принятой информации с второго блока памяти БП2 5 в основное запоминающее устройство блока центрального управления БЦУ 1 принимающей части передачи информации.

Если при обмене информации произошел сбой при передаче информации, то элемент сравнения ЭС 1 передающей части не формирует импульса совпадения. При этом не включается триггер Тр 5. В связи с этим сигнал с выхода четвертого элемента задержки импульса τ4 14 проходит через первый элемент И1 15 и второй элемент ИЛИ2 11 и сбрасывает второй блок памяти БП2 12 в исходное состояние. При этом импульс с выхода третьего элемента задержки импульса τ3 13 поступает через четвертый элемент задержки импульсов τ4 14 на счетный вход делителя частоты Дч 10. Этот же импульс проходит через открытый первый элемент И1 15 и с его выхода через третий элемент ИЛИ3 17 по циклу запускает все устройство для обмена информацией вторично, повторяя описанный выше алгоритм. При отработке данного алгоритма более заданного числа раз, которое задается в исходном состоянии по установочным входам делителя частоты Дч 10 с входов задания числа проверок достоверности передаваемой информации устройства, в устройстве на выходе делителя частоты Дч 10 формируется аварийный сигнал о потере информации, который приводит к включению блока сигнализации БС 32. Сигнал на выходе блока сигнализации БС 32 является основанием для анализа устройства в целом на предмет достоверности его функционирования.

Таким образом, с помощью данных устройств обеспечиваются централизованный дистанционный сбор данных с мест возникновения информации, передача полученных данных и дистанционный прием данных на выбранные приемники, причем информация, полученная на приемниках, совпадает с информацией, находящейся на передающей стороне.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ | 2002 |

|

RU2235357C2 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2109399C1 |

| СПОСОБ ИЗМЕРЕНИЯ СПЕКТРА ИНФОРМАЦИОННЫХ АКУСТИЧЕСКИХ СИГНАЛОВ ТЕЛЕРАДИОВЕЩАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2573248C2 |

| Способ и устройство изменения скорости передачи цифрового звукового сигнала телерадиовещания с предыскажением | 2024 |

|

RU2830465C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| ИЗМЕРИТЕЛЬ ДЛИТЕЛЬНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2001 |

|

RU2210084C2 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2139640C1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2143182C1 |

| МАГНИТОСТРИКЦИОННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090839C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

Изобретение относится к области автоматики и вычислительной техники, в частности к периферийным устройствам, и может быть использовано для ввода-вывода информации, обмена с дистанционно удаленным другим периферийным устройством вычислительной машины. Техническим результатом изобретения является повышение достоверности ввода информации за счет организации режима работы устройства по командам, поступающим от периферийного устройства, являющимся центром сбора информации. Устройство содержит блок приемопередачи, центральный блок управления, семь элементов задержки сигнала, два элемента И и четыре элемента ИЛИ, триггер, два преобразователя кодов, три одновибратора, блок сигнализации, делитель частоты, три формирователя импульсов, два устройства выделения импульса управления, передатчик и приемник, а также элемент сравнения и два блока памяти. Устройство обеспечивает централизованный дистанционный сбор данных с мест возникновения информации, передачу этой информации по каналам связи, дистанционный прием данных на выбранные приемники с повышенной достоверностью принятой информации. 3 ил.

Устройство для обмена информацией, содержащее блок центрального управления и блок приемопередачи, причем последний содержит первый блок памяти, приемник, передатчик и блок сигнализации, отличающееся тем, что в блок приемопередачи введены четыре элемента ИЛИ, три формирователя импульсов, элемент сравнения, семь элементов задержки импульсов, два преобразователя кодов, приемник и передатчик, три одновибратора, триггер, два элемента И, два устройства выделения импульса управления, второй блок памяти и делитель частоты, выход которого соединен с входом блока сигнализации, а установочные входы - с входами задания числа проверок достоверности передаваемой информации устройством, выход элемента сравнения соединен с первым формирователем импульсов, выход которого непосредственно соединен с входом "Сброс" первого блока памяти и через четвертый элемент задержки импульсов соединен с первым входом триггера, через первый одновибратор соединен с первым входом первого элемента ИЛИ, связанного с вторым формирователем импульсов, выход первого формирователя через второй элемент задержки импульсов соединен с входом "Сброс" делителя частоты и с первым входом второго элемента ИЛИ, соединенным с входом "Сброс" второго блока

памяти, информационные выходы первого и второго блоков памяти соединены с соответствующими входами элемента сравнения, вход синхронизации которого соединен с выходом третьего элемента задержки импульсов и через четвертый элемент задержки импульсов с счетным входом делителя частоты и с первым входом первого элемента И, второй вход которого соединен с первым выходом триггера и входом второго одновибратора, выход первого элемента И соединен с вторым входом второго элемента ИЛИ и с первым входом третьего элемента ИЛИ, соединенным с входом управления первого преобразователя кодов и с первым входом четвертого элемента ИЛИ, выход второго одновибратора соединен с входом третьего элемента задержки импульсов, а через пятый элемент задержки импульсов с входом "Запись" второго блока памяти, второй выход триггера соединен с первым входом второго элемента И, второй вход которого соединен с выходом приемника и входом третьего формирователя импульсов, выход которого соединен через первое устройство выделения импульсов управления с управляющим входом второго преобразователя кодов и непосредственно с его информационным входом, выходы второго преобразователя кодов соединены с информационными входами второго блока памяти, выходы которого соединены с информационными входами блока центрального управления, информационные выходы которого соединены с информационными входами первого блока памяти, выход управления блока центрального управления соединен с входом "Запись" первого блока памяти и через шестой элемент задержки импульсов с вторым входом третьего элемента ИЛИ, информационные входы первого преобразователя кодов соединены с выходами первого блока памяти, первый выход первого преобразователя кодов - с вторым входом первого элемента ИЛИ, а второй выход первого преобразователя кодов подключен через седьмой элемент задержки импульсов к второму входу триггера и непосредственно к второму входу четвертого элемента ИЛИ, выход которого через третий одновибратор соединен с третьим входом первого элемента ИЛИ, выход второго элемента И соединен с четвертым входом первого элемента ИЛИ и через второе устройство выделения импульсов управления с входом "Запись" блока центрального управления, выход второго формирователя импульсов соединен с входом передатчика.

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для регистрации информации | 1986 |

|

SU1314328A1 |

| Якубайтис Э.А | |||

| Информационные вычислительные сети | |||

| - М.: Финансы и статистика, 1984, с.184 - 187. | |||

Авторы

Даты

1999-05-20—Публикация

1998-02-16—Подача