Изобретение относится к области цифровой вычислительной техники и может найти применение при построении алгоритмически распределенных устройств микропрограммного управления вычислительных и управляющих систем высокой производительности, проектируемых на однотипных БИС (СБИС) и реализующих параллельные алгоритмы обработки информации.

Известен микропрограммный модуль, содержащий блок памяти микрокоманд, счетчик, регистр микрокоманд, демультиплексор, мультиплексор, триггер пуска, генератор тактовых импульсов, блок элементов ИЛИ, блок ключей с тристабильным выходом, K+1 блоков элементов И (где K - количество входов приема управления, прием информации с которых блокируется), сумматор, элемент И, два элемента ИЛИ (авт.св. СССР N 1427366, кл.G 06 F 9/22, опубл.30.09.88).

Недостатком известного модуля является отсутствие возможности построения управляющих систем, реализующих параллельные алгоритмы управления.

Наиболее близким к предлагаемому устройству по технической сущности является микропрограммное устройство управления, содержащее блок постоянной памяти, блок формирования адреса микрокоманд, регистр начала микропрограммы, регистр состояния параллельных участков, триггер управления, генератор тактовых импульсов, регистр адреса следующей микрокоманды, регистр микроопераций, регистр формата микрокоманды, группу из N-1 элементов И (N-максимальное количество параллельно выполняемых участков микропрограмм), элемент ИЛИ, блок элементов ИЛИ, два элемента И, два блока элементов И, одновибратор и три элемента задержки (авт. св. СССР N 1647566, кл.G 06 F 9/22, опубл. 07.05.91 ).

Недостатками данного устройства являются значительное число внешних входов и выходов, необходимых для организации взаимодействия с другими аналогичными устройствами при формировании управляющих систем, а также существенный рост числа внешних входов и выходов при незначительном увеличении количества устройств в составе управляющей системы.

Технической задачей изобретения является расширение области применения устройства за счет сокращения числа внешних входов и выходов, требуемых для организации взаимодействия с другими идентичными устройствами, и уменьшения степени зависимости этого числа от количества однотипных устройств в составе управляющей системы (размерности управляющей системы) при неизменных функциональной гибкости и быстродействии.

Техническая задача решается тем, что в микропрограммное устройство управления, содержащее блок постоянной памяти, блок формирования адреса микрокоманд, регистр состояния, регистр микроопераций, регистр адреса следующей микрокоманды, регистр формата микрокоманды, триггер управления, генератор тактовых импульсов, первый и второй элементы И, первый элемент ИЛИ, первый одновибратор, первый и второй элементы задержки, причем первый, второй и третий информационные входы блока формирования адреса микрокоманд соединены с входом логических условий устройства, с выходом регистра адреса следующей микрокоманды и с выходом регистра состояния соответственно, первый вход первого элемента ИЛИ является входом запуска устройства, выход первого элемента ИЛИ соединен со счетным входом триггера управления, вход сброса которого соединен с выходом первого одновибратора, прямой выход триггера управления подключен к входу запуска генератора тактовых импульсов, первый выход которого соединен с входом синхронизации регистра формата микрокоманды и входом первого элемента задержки, выход которого подключен к первым входам первого и второго элементов И, второй выход генератора тактовых импульсов соединен с входом синхронизации блока формирования адреса микрокоманд, выход которого соединен с адресным входом блока постоянной памяти, выход микроопераций которого соединен с информационным входом регистра микроопераций, выход формата микрокоманды блока постоянной памяти подключен к информационному входу регистра формата микрокоманды, выход метки опроса состояния параллельных участков которого соединен с управляющим входом блока формирования адреса микрокоманд, выход метки запуска параллельных участков регистра формата микрокоманды подключен к второму входу второго элемента И и к второму входу первого элемента И, выход которого соединен с входом синхронизации регистра микроопераций, выход которого является выходом микроопераций устройства, введены блок памяти начальных адресов, регистр кода логического условия, сумматор, регистр кода инициализации, схема сравнения, буферный регистр, коммутатор адреса, коммутатор кода инициализации, триггер режима, триггер передачи управления, триггер приема управления, первый и второй блоки тристабильных элементов, шина передачи управления, с третьего по пятый элементы И, с второго по седьмой элементы ИЛИ, элемент ИЛИ-НЕ, с второго по пятый одновибраторы, причем входы регистра состояния с первого по (N-1)-й (N-число однотипных устройств в составе управляющей системы) являются входами признаков начала/конца участков устройства с первого по (N-1)-й соответственно, инверсный выход триггера управления соединен с входами второго и третьего одновибраторов, выходы которых соединены с первым и вторым входами второго элемента ИЛИ соответственно, выход которого является выходом признака начала/конца участка устройства, выход метки конца участка регистра формата микрокоманды подключен к третьему входу первого элемента И и к первому входу третьего элемента И, второй вход которого соединен с выходом первого элемента задержки, выход третьего элемента И подключен к первым входам третьего и четвертого элементов ИЛИ и к первому входу пятого элемента ИЛИ, выход которого соединен с входом сброса регистра микроопераций, выход конца работы которого подключен к второму входу четвертого элемента ИЛИ, выход которого соединен с входом первого одновибратора, выход метки запуска параллельных участков регистра формата микрокоманды соединен с третьим входом четвертого элемента ИЛИ, выход второго элемента И подключен к второму входу пятого элемента ИЛИ и к входу установки триггера передачи управления, прямой выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом элемента ИЛИ-НЕ, выход четвертого элемента И подключен к управляющим входам первого и второго блоков тристабильных элементов и к входу четвертого одновибратора, выход которого соединен с входом сброса триггера передачи управления и с вторым входом первого элемента ИЛИ, выход микроопераций блока постоянной памяти соединен с первым информационным входом коммутатора кода инициализации и с информационным входом первого блока тристабильных элементов, выход которого подключен к шине передачи управления, которая соединена с информационным входом второго блока тристабильных элементов, выход которого соединен с входами элемента ИЛИ-НЕ, вход номера операции устройства соединен с адресным входом блока памяти начальных адресов, выход адреса инициализации которого подключен к первому информационному входу коммутатора адреса, выход кода инициализации блока памяти начальных адресов соединен с вторым информационным входом коммутатора кода инициализации, выход которого соединен с информационным входом регистра кода инициализации, выход которого соединен с входом шестого элемента ИЛИ и с первым входом схемы сравнения, выход которого подключен к первому входу пятого элемента И, второй вход которого соединен с выходом шестого элемента ИЛИ, выход пятого элемента И подключен к счетному входу триггера приема управления, инверсный выход которого соединен с входом пятого одновибратора, выход которого соединен с первым входом седьмого элемента ИЛИ, с входами сброса буферного регистра, регистра кода инициализации, триггера приема управления и с третьим входом первого элемента ИЛИ, вход настройки устройства подключен к входу установки триггера режима и к входу второго элемента задержки, выход которого соединен с вторым входом седьмого элемента ИЛИ, счетным входом триггера режима и с вторым входом третьего элемента ИЛИ, выход которого соединен с входом синхронизации регистра кода инициализации, прямой и инверсный выходы триггера режима соединены с первым и вторым управляющим входами коммутатора кода инициализации соответственно, прямой выход триггера режима подключен к первому управляющему входу коммутатора адреса, второй информационный вход которого соединен с выходом адреса блока постоянной памяти, инверсный выход триггера режима соединен с вторым и третьим управляющим входами коммутатора адреса, выход кода логического условия которого соединен с информационным входом регистра кода логического условия, выход которого подключен к второму информационному входу блока формирования адреса микрокоманд, прямой выход триггера приема управления подключен к четвертому и инверсному управляющим входам коммутатора адреса и к входу синхронизации буферного регистра, информационный вход которого соединен с выходом регистра адреса следующей микрокоманды, выход второго блока тристабильных элементов образован выходом кода инициализации и выходом кода коррекции адреса, выход кода инициализации второго блока тристабильных элементов подключен к второму входу схемы сравнения, выход кода коррекции адреса второго блока тристабильных элементов соединен с третьим информационным входом коммутатора адреса, выход адреса которого подключен к первому входу сумматора, второй вход и выход которого соединен с выходом буферного регистра и информационным входом регистра адреса следующей микрокоманды соответственно, первый выход генератора тактовых импульсов подключен к входу синхронизации регистра кода логического условия и к третьему входу седьмого элемента ИЛИ, выход которого подключен к входу синхронизации регистра адреса следующей микрокоманды, а блок формирования адреса микрокоманды содержит первый и второй мультиплексоры, коммутатор условий, первый и второй элементы И и счетчик адреса, причем информационные входы первого и второго мультиплексоров являются первым и третьим информационными входами блока формирования адреса микрокоманд соответственно, выходы первого и второго мультиплексоров соединены с прямым и инверсным информационными входами коммутатора условий соответственно, управляющие входы первого и второго мультиплексоров в объединении с информационным входом счетчика адреса подключены к второму информационному входу блока формирования адреса микрокоманд, вход синхронизации которого соединен с первым входом первого элемента И и прямым входом второго элемента И, выход которого соединен с входом записи счетчика адреса, управляющий вход блока формирования адреса микрокоманд соединен с управляющими входами коммутатора условий, выход которого подключен к инверсному входу второго элемента И и второму входу первого элемента И, выход которого соединен с суммирующим входом счетчика адреса, выход которого является выходом блока формирования адреса микрокоманд.

Сущность изобретения заключается в следующем.

Предлагаемое устройство совместно с другими аналогичными устройствами образует управляющую систему, обеспечивающую возможность реализации комплексных (объединенных) алгоритмов, содержащих как последовательные, так и параллельные участки. Каждое устройство (модуль) системы реализует определенное подмножество участков микропрограмм и в процессе функционирования может осуществлять запуск произвольных групп параллельных участков или передавать управление другим аналогичным модулям, а также производить опрос состояния любых подмножеств параллельных участков и в зависимости от результата опроса переходить к выполнению тех или иных микрокоманд.

В прототипе при запуске (инициализации) группы, включающей p параллельных участков (модулей системы), осуществляется одновременная выдача соответствующего количества различных адресов (адресов передачи управления) и специальных меток начала участков микрокоманд. Для этого используется N-1 (m+1)-разрядных внешних выходов и N-1 (m+1)-разрядных входов для приема адресов передачи управления и указанных меток, где N - число устройств в составе управляющей системы, определяемое максимальным числом параллельно выполняемых участков микропрограмм; m - разрядность адресов передачи управления, соответствующая емкость микропрограммной памяти (блока памяти микропрограмм). Добавление в систему, построенную на основе прототипа, (N+1)-го устройства приводит к необходимости увеличения числа внешних входов и выходов устройств на 2(m+1), а с учетом входов и выходов, используемых для приема и выдачи меток конца параллельных участков, - на 2(m+2). При емкости микропрограммной памяти, равной 256 словам, абсолютное увеличение числа входов и выходов каждого из устройства при включении в систему (N+1)-го модуля составит 20.

Существенная зависимость числа внешних входов и выходов устройств от их числа в состав управляющей системы (размерности системы) существенно ограничивает наращиваемость систем, а следовательно, и класс реализуемых алгоритмов и, кроме того, создает определенные технологические трудности при реализации устройств в виде СБИС.

В предлагаемом устройстве в отличие от прототипа передача управления другим устройствам системы осуществляется через общую шину - шину передачи управления - и реализуется путем выдачи не адресов, а специальных кодов (признаков) инициализации, которые однозначно определяют группы одновременно запускаемых параллельных участков микропрограмм или отдельные последовательные участки. Одновременно запускаемым участкам присваиваются одинаковые коды инициализации (этим участкам соответствует одна и та же вершина распараллеливания), а коды инициализации участков, моменты запуска которых взаимно не согласованы (этим участкам соответствуют различные вершины распараллеливания), являются различными. Одни и те же коды инициализации получают, кроме того, альтернативные участки, закрепленные за одним и тем же устройством.

Введенный способ идентификации участков микропрограмм обеспечивает возможность их физически одновременного запуска путем передачи единственного кода инициализации и несмотря на использование разделяемого во времени ресурса - шины передачи управления - не ведет к снижению быстродействия управляющей системы.

Функционирование системы начинается с ее настройки на выполнение требуемой микропрограммы (операции) s. Настройка производится сразу после подачи на входы модулей системы кода номера, операции Ks. Код номера операции Ks вырабатывается внешним (супервизорным) устройством, одновременно подается на входы всех модулей и адресует специальные блоки памяти начальных адресов, в ячейках которых размещаются коды и адреса инициализации модулей, соответствующие различным операциям.

После поступления на вход модуля Ml кода Ks на выходе блока памяти начальных адресов формируется код инициализации K

После настройки системы внешнее устройство запускает модуль Mi, за которым закреплен начальный последовательный участок s-й микропрограммы, и Mi начинает выполнение микропрограммы с адреса A

Завершая исполнение некоторого участка микропрограммы, модуль Mj осуществляет самонастройку на следующий запуск (прием управления), а именно формирует код инициализации K

В дальнейшем модуль Mk, передающий управление модуля Mj, вырабатывает код инициализации Kk(n) = K

Так как возможно существование нескольких альтернативных вариантов инициализации одного и того же модуля (по различным адресам), например, когда адрес приема управления j-го модуля зависит от результата проверки логических условий другими модулями, модуль Mk при передаче управления другим устройствам вместе с соответствующим кодом инициализации Kk(n) выдает код коррекции адреса dAk(n). После идентификации совпадения кода Kk(n) с кодом инициализации K

Число внешних входов и выходов, используемых для приема/передачи управления, в предлагаемом устройстве определяется как 2(m*+d+1), где d - разрядность кода инициализации, а m* - разрядность кода коррекции адреса. Так как различные микропрограммы не могут выполняться системой одновременно, коды инициализации, присвоенные участкам различных микропрограмм, могут совпадать. Это позволяет значительно снизить значение параметра d.

Для дальнейшего сокращения числа внешних входов и выходов прием (и соответственно передача) меток начала и окончания параллельных участков в предлагаемом устройстве производится по одним и тем же физическим линиям, а регистр состояния выполняется на основе T-триггеров.

Количественная оценка эффективности предлагаемого технического решения по отношению к прототипу приводится в конце описания.

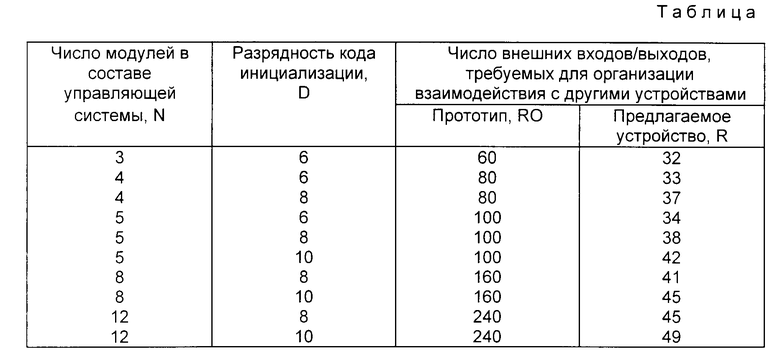

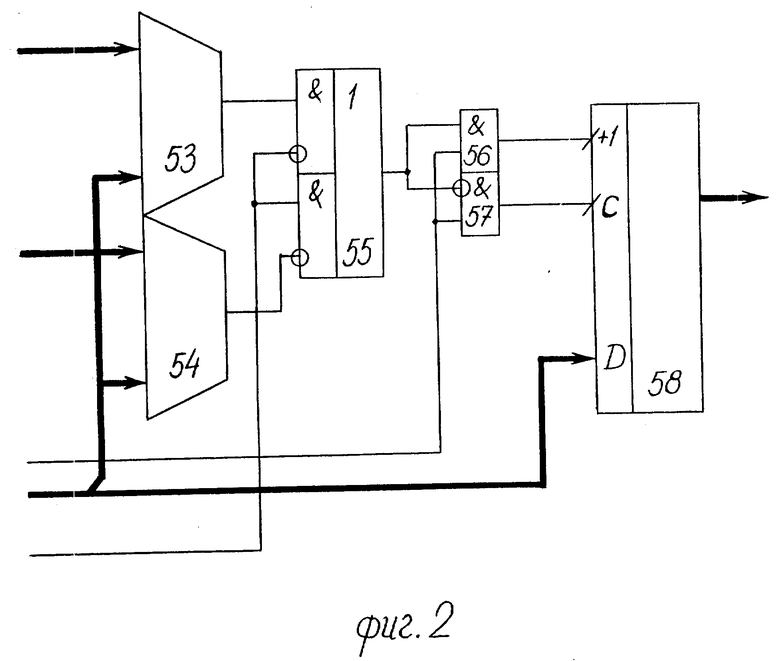

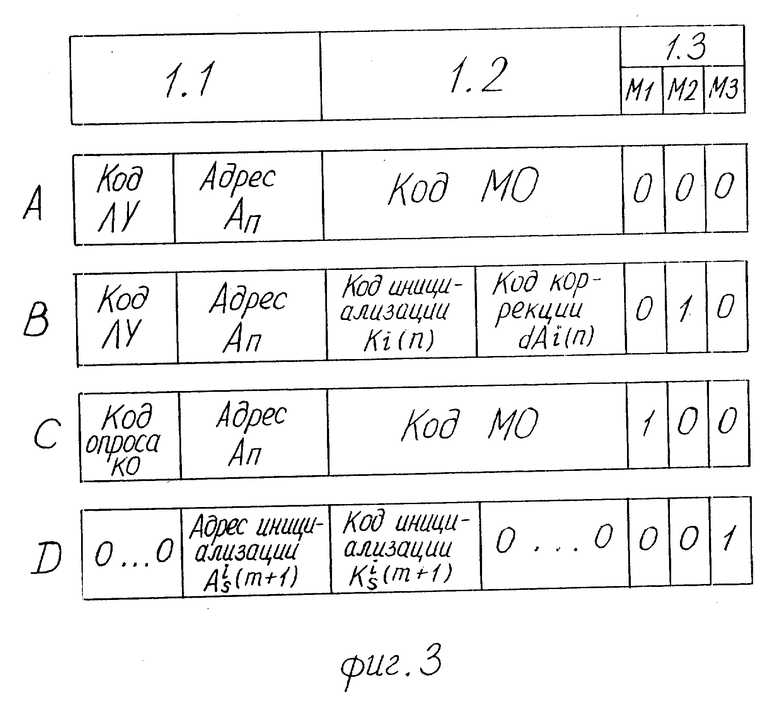

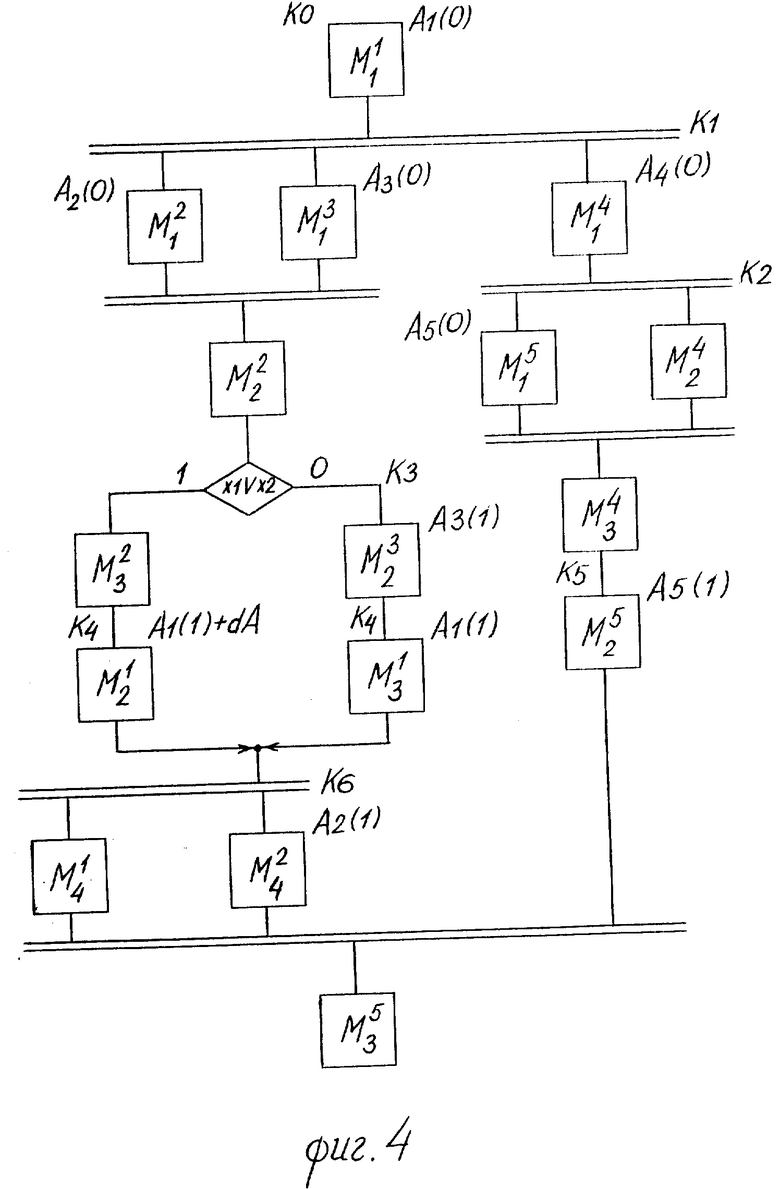

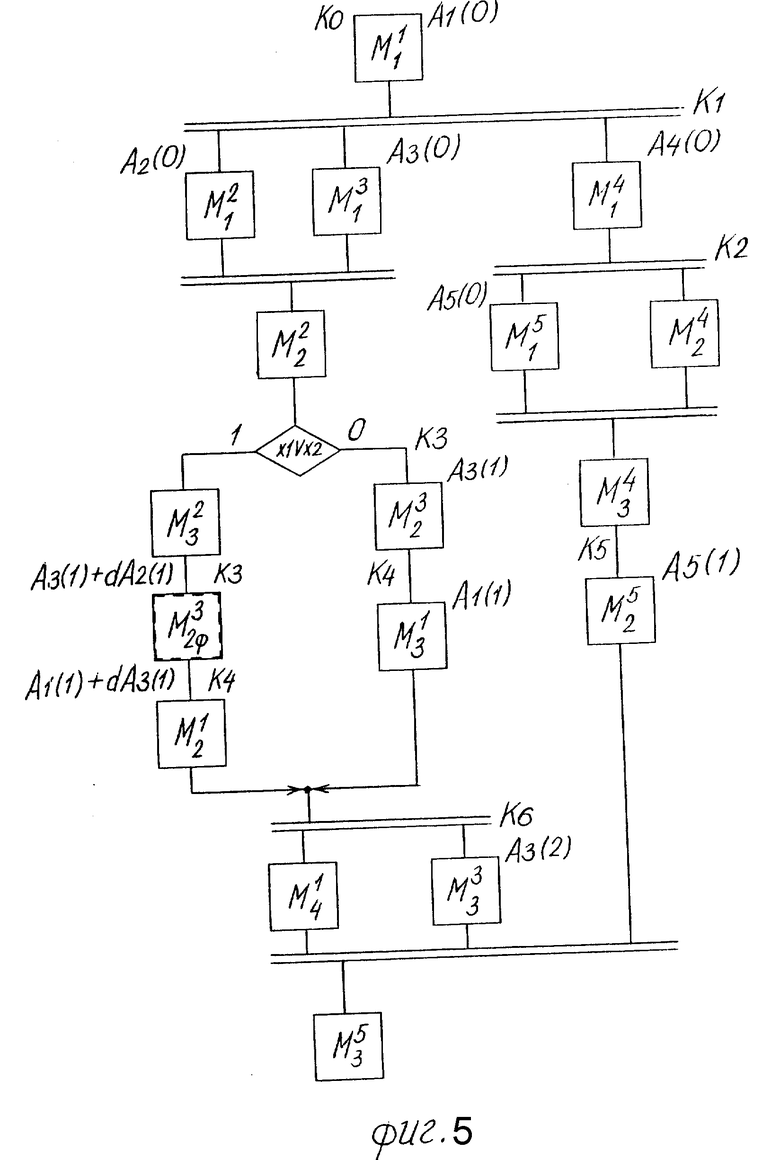

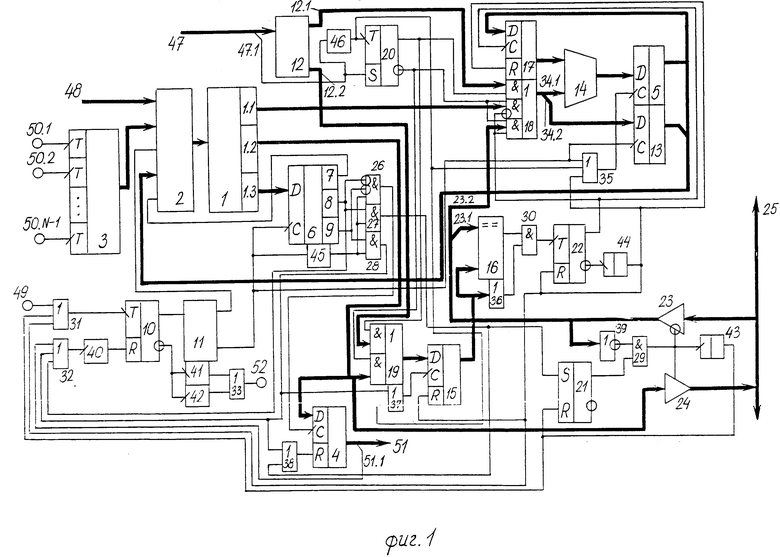

На фиг. 1 представлена функциональная схема микропрограммного устройства управления; на фиг. 2 изображена функциональная схема блока формирования адреса микрокоманд; на фиг. 3 приведены форматы микрокоманд, реализуемые устройством; на фиг. 4 и 5 дан пример параллельного алгоритма управления и его реализации управляющей системой, состоящей из пяти идентичных устройств (модулей).

Микропрограммное устройство управления (фиг.1) содержит блок 1 постоянной памяти, блок 2 формирования адреса микрокоманд, регистр 3 состояния, регистр 4 микроопераций, регистр 5 адреса следующей микрокоманды, регистр 6 формата микрокоманды, триггер 10 управления, генератора 11 тактовых импульсов, первый 26 и второй 27 элементы И, первый элемент ИЛИ 31, первый одновибратор 40, первый 45 и второй 46 элементы задержки, причем первый, второй и третий информационные входы блока 2 формирования адреса микрокоманд соединены с входом 48 логических условий устройства, с выходом регистра 5 адреса следующей микрокоманды и с выходом регистра 3 состояния соответственно, первый вход элемента ИЛИ 31 является входом 49 запуска устройства, выход элемента ИЛИ 31 соединен со счетным входом триггера 10 управления, вход сброса которого соединен с выходом одновибратора 40, прямой выход триггера 10 управления подключен к входу запуска генератора 11 тактовых импульсов, первый выход которого соединен с входом синхронизации регистра 6 формата микрокоманды и входом элемента 45 задержки, выход которого подключен к первым входам элементов И 26 и 27, второй выход генератора 11 тактовых импульсов соединен с входом синхронизации блока 2 формирования адреса микрокоманд, выход которого соединен с адресным входом блока 1 постоянной памяти, выход 1.2 микроопераций которого соединен с информационным входом регистра 4 микрооперации, выход 1.3 формата микрокоманды блока 1 постоянной памяти подключен к информационному входу регистра 6 формата микрокоманды, выход 7 метки опроса состояния параллельных участков которого соединен с управляющим входом блока 2 формирования адреса микрокоманд, выход 8 метки запуска параллельных участков регистра 6 формата микрокоманды подключен к второму входу элемента И 27 и к второму входу элемента И 26, выход которого соединен с входом синхронизации регистра 4 микроопераций, выход которого является выходом 51 микроопераций устройства, а также введенные блок 12 памяти начальных адресов, регистр 13 кода логического условия, сумматор 14, регистр 15 кода инициализации, схему 16 сравнения, буферный регистр 17, коммутатор 18 адреса, коммутатор 19 кода инициализации, триггер 20 режима, триггер 21 передачи управления, триггер 22 приема управления, второй 23 и первый 24 блоки тристабильных элементов, шину 25 передачи управления, третий 28, четвертый 29 и пятый 30 элементы И, четвертый 32, второй 33, седьмой 35, шестой 36, третий 37 и пятый 38 элементы ИЛИ, элемент ИЛИ-НЕ 39, второй 41, третий 42, четвертый 43 и пятый 44 одновибраторы, причем входы регистра 3 состояния с первого по (N-1)-й (N - число однотипных устройство в составе управляющей системы) являются входами 50.1 - 50.N-1 признаков начала/конца участков устройства соответственно, инверсный выход триггера 10 управления соединен с входами одновибраторов 41 и 42, выходы которых соединены с первым и вторым входами элемента ИЛИ 33 соответственно, выход которого является выходом 52 признака начала/конца участка устройства, выход 9 метки конца участка регистра 6 формата микрокоманды подключен к третьему воду элемента И 26 и к первому входу элемента И 28, второй вход которого соединен с выходом элемента 45 задержки, выход элемента И 28 подключен к первым входам элементов ИЛИ 37 и 32 и к первому входу элемента ИЛИ 38, выход которого соединен с входом сброса регистра 4 микроопераций, выход 51.1 конца работы которого подключен к второму входу элемента ИЛИ 32, выход которого соединен с входом одновибратора 40, выход 8 метки запуска параллельных участков регистра 6 формата микрокоманды соединен с третьим входом элемента ИЛИ 32, выход элемента И 27 подключен к второму входу элемента ИЛИ 38 и к входу установки триггера 21 передачи управления, прямой выход которого соединен с первым входом элемента И 29, второй вход которого соединен с выходом элемента ИЛИ-НЕ 39, выход элемента И 29 подключен к управляющим входам блоков тристабильных элементов 23 и 24 и к входам и к входу одновибратора 43, выход которого соединен с входом сброса триггера 21 передачи управления и с вторым входом элемента ИЛИ 31, выход 1.2 микроопераций блока 1 постоянной памяти соединен с первым информационным входом коммутатора 19 кода инициализации и с информационным входом блока тристабильных элементов 24, выход которого подключен к шине 25 передачи управления, которая соединена с информационным входом блока тристабильных элементов 23, выход которого соединен с входами элемента ИЛИ-НЕ 39, вход 47 номера операции устройства соединен с адресным входом блока 12 памяти начальных адресов, выход 12.1 адреса инициализации которого подключен к первому информационному входу коммутатора 18 адреса, выход 12.2 кода инициализации блока 12 памяти начальных адресов соединен с вторым информационным входом регистра 15 кода инициализации, выход которого соединен с входами элемента ИЛИ 36 и с первым входом схемы 16 сравнения, выход которой подключен к первому входу элемента И 30, второй вход которого соединен с выходом элемента ИЛИ 36, выход элемента И 30 подключен к счетному входу триггера 22 приема управления, инверсный выход которого соединен с входом одновибратора 44, выход которого соединен с первым входом одновибратора 44, выход которого соединен с первым входом элемента ИЛИ 35, с входами сброса буферного регистра 17, регистра 15 кода инициализации, триггера 22 приема управления и с третьим входом элемента ИЛИ 31, вход 47.1 настройки устройства подключен к входу установки триггера 20 режима и к входу элемента 46 задержки, выход которого соединен с вторым входом элемента ИЛИ 35, счетным входом триггера 20 режима и с вторым входом элемента ИЛИ 37, выход которого соединен с входом синхронизации регистра 15 кода инициализации, прямой и инверсный выходы триггера 20 режима соединения с первым и вторым управляющими входами коммутатора 19 кода инициализации соответственно, прямой выход триггера 20 режима подключен к первому управляющему входу коммутатора 18 адреса, второй информационный вход которого соединен с выходом 1.1 адреса блока 1 постоянной памяти, инверсный выход триггера 20 режима соединен с вторым и третьим управляющими входами коммутатора 18 адреса, выход 34.2 кода логического условия которого соединен с информационным входом регистра 13 логического условия, выход которого подключен к второму информационному входу блока формирования адреса микрокоманд, прямой выход триггера 22 приема управления подключен к четвертому и инверсному управляющим входам коммутатора 18 адреса и к входу синхронизации буферного регистра 17, информационный вход которого соединен с выходом регистра 5 адреса следующей микрокоманды, выход блока тристабильных элементов 23 образован выходом 23.1 кода инициализации и выходом 23.2 кода коррекции адреса, выход 23.1 кода инициализации блока тристабильных элементов 23 подключен к второму входу схемы 16 сравнения, выход 23.2 кода коррекции адреса блока тристабильных элементов 23 соединен с третьим информационным входом коммутатора 18 адреса, выход 34.1 адреса которого подключен к первому входу сумматора 14, второй вход и выход которого соединены с выходом буферного регистра 17 и информационным входом регистра 5 адреса следующей микрокоманды соответственно, первый выход генератора 11 тактовых импульсов подключен к входу синхронизации регистра 13 кода логического условия и к третьему входу синхронизации регистра 5 адреса следующей микрокоманды.

Блок формирования адреса микрокоманд (фиг.2) содержит первый 53 и второй 54 мультиплексоры, коммутатор 55 условий, первый 56 и второй 57 элементы И и счетчик 58 адреса, причем информационные входы мультиплексоров 553 и 54 являются первым и третьим информационными входами блока формирования адреса микрокоманд соответственно, выходы мультиплексоров 53 и 54 соединены с прямым и инверсным информационными входами коммутатора 55 условий соответственно, управляющие входы мультиплексоров 53 и 54 в объединении с информационным входом счетчика 58 адреса подключен к второму информационному входу блока формирования адреса микрокоманд, вход синхронизации которого соединен с первым входом элемента И 56 и прямым входом элемента И 57, выход которого соединен с входом записи счетчика 58 адреса, управляющий вход блока формирования адреса микрокоманд соединен с управляющими входами коммутатора 55 условий, выход которого подключен к инверсному входу элемента И 57 и второму входу элемента И 56, выход которого соединен с суммирующим входом счетчика 58 адреса, выход которого является выходом блока формирования адреса микрокоманд.

Назначение функциональных элементов и блока предлагаемого устройства (фиг.1) состоит в следующем.

Блок постоянной памяти предназначен для постоянного хранения и выдачи микрокоманд, составляющих параллельные и последовательные участки микропрограммы, закрепленные за текущим устройством.

Регистр 3 состояния служит для хранения, модификации и выдачи вектора текущего состояния управляющей системы.

Регистр 4 микроопераций служит для приема и выдачи на выход 51 устройства кодов микроопераций.

Регистр 5 адреса следующей микрокоманды предназначен для временного хранения адресов инициализации и адресов принудительного перехода соответственно после выполнения процедуры настройки (самонастройки) устройства и в режиме реализации микропрограмм.

Регистр 6 формата микрокоманды предназначен для временного хранения признака формата считываемых из блока 1 микрокоманд и формирования управляющих меток M1, M2 и M3, определяющих режим их обработки.

Генератор 11 тактовых импульсов служит для формирования двух сдвинутых относительно друг друга на полпериода импульсных последовательностей t1 и t2, синхронизирующих работу различных элементов устройства.

Триггер 10 управляющим служит для управления запуском и остановом генератора 11, а также для индикации текущего состояния устройства.

Блок 12 памяти начальных адресов предназначен для постоянного хранения и выдачи кодов и адресов инициализации устройства, соответствующих различным микропрограммам (операциям).

Регистр 13 кода логического условия обеспечивает временное сохранение кодов логических условий и кодов опроса состояния параллельных участков, поступающих с выхода 1.1 блока 1.

Сумматор 14 служит для коррекции адресов инициализации устройства. Сумматор 14 не имеет специальных управляющих входов и модифицированный адрес инициализации (результат) появляется на его выходе непосредственно после подачи на его выходе исходного адреса инициализации и кода коррекции адреса (первого и второго операндов).

Регистр 15 кода инициализации служит для размещения и выдачи кодов инициализации устройства.

Схема 16 сравнения предназначена для сравнения кодов инициализации параллельных или последовательных участков, поступающих от модулей, функционирующих в режиме передачи управления, с кодом инициализации текущего устройства, размещенным в регистре 15.

Буферный регистр 17 предназначен для временного хранения и выдачи исходного адреса инициализации устройства на вход сумматора 14 при реализации режима коррекции адреса инициализации.

Коммутатор 18 адреса служит для подключения входа сумматора 14 и информационного входа регистра 13 либо к выходу 12.1 блока 12, либо к выходу 1.1 блока 1, либо к выходу блока 23 в зависимости от значений сигналов на управляющих входах.

Коммутатор 19 кода инициализации предназначен для подключения информационного входа регистра 15 или к выходу 12.2 блока 12, или к выходу 1.2 блока 1 в зависимости от значений сигналов на управляющих входах.

Триггер 20 режима служит для индикации текущего режима работы устройства и управления коммутаторами 18 и 19.

Шина 25 передачи управления введена для организации возможности передачи кодов инициализации и коррекции адреса при реализации устройством режима передачи управления.

Триггер 21 передачи управления служит для управления выдачей информации на шине 25 при реализации режима передачи управления.

Триггер 22 приема управления предназначен для управления коммутатором 18 и процессом коррекции адреса инициализации при приеме управления со стороны другого устройства.

Блоки 23 и 24 тристабильных элементов предназначены соответственно для блокировки/разрежения приема управляющей информации с шины 25 и выдачи информации на шину 25.

Элемент ИЛИ 36 служит для формирования сигнала состояния регистра 15 кода инициализации.

Элемент И 30 обеспечивает блокировку срабатывания триггера 22 при отсутствии кода инициализации в регистре 15 (при нулевом состоянии регистра 15).

Элемент ИЛИ-НЕ 39 служит для формирования сигнала состояния шины 25 передачи управления.

Элемент И 29 обеспечивает блокировку процесса выдачи управляющей информации при наличии информации на шине 25.

Одновибратор 40 предназначен для формирования импульса останова устройства, обеспечивающего надежное переключение триггера 10.

Элемент 45 задержки обеспечивает сдвиг момента подачи тактового импульса t2 с выхода генератора 11 на входы элементов И 26 - 28 на время формирования сигналов - управляющих меток на выходах регистра 6 формата микрокоманды.

Элемент И 26 предназначен для управления прохождением импульса t2 с выхода элемента 45 на вход синхронизации регистра 4.

Элемент И 27 служит для управления прохождением импульса t2 с выхода элемента 45 на вход сброса регистра 4 и вход установки триггера 21.

Элемент И 28 используется для управления передачей импульса t2 с выхода элемента 45 на вход сброса регистра 4, вход синхронизации регистра 15 и вход элемента ИЛИ 32.

Элемент ИЛИ 32 служит для объединения сигналов с выхода 8 регистра 6, с выхода элемента И 28, с выхода 51.1 конца работы регистра 4 и формирования сигнала возбуждения одновибратора 40.

Одновибраторы 41 и 42 предназначены для формирования соответственно импульса R - метки начала участка микропрограммы и импульса Q - метки конца участка, причем одновибратор 41 реагирует на отрицательный (l > 0), а одновибратор 42 - на положительный (0 > l) перепад уровня сигнала на входе.

Элемент ИЛИ 33 обеспечивает объединение импульсов R и Q и формирование обобщенного сигнала (импульса) - метки изменения состояния устройства.

Элемент 40 задержки обеспечивает сдвиг момента подачи импульса настройки на входы синхронизации регистров 5 и 15 и установки триггера 20 в нулевое состояние на время формирования адреса инициализации на выходе сумматора 14.

Элемент ИЛИ 37 предназначен для объединения сигналов синхронизации записи кода инициализации в регистр 15, поступающих с выхода элемента И 28 и элемента 46 задержки в режимах самонастройки и настройки соответственно.

Элемент ИЛИ 38 обеспечивает объединение сигналов сброса регистра 4, поступающих с выходов элементов И 27 и 28 в режимах соответственно передачи управления и завершения параллельного или последовательного участка микропрограмм.

Одновибратор 43 служит для формирования импульса, обеспечивающего сброс триггера 21 и инициализацию устройства после завершения процесса передачи управления; одновибратор 43 реагирует на положительный перепад уровня сигнала на его входе и формирует импульс с задержкой, величина которой определяется требуемым временем фиксации информации на шине 25.

Одновибратор 44 предназначен для формирования импульса, осуществляющего фиксации адреса инициализации в регистре 5, сброс регистров 17, 15, триггера 22 и запуск устройства в режиме приема управления; одновибратор 44 срабатывает по отрицательному перепаду уровня сигнала на его выходе и вырабатывает импульс с задержкой, соответствующей времени окончания процесса коррекции адреса инициализации и формирования окончательного (исполнительного) адреса микрокоманды на выходе сумматора 14.

Элемент ИЛИ 35 служит для объединения сигналов, синхронизирующих процесс записи информации в регистр 5.

Предположим, что предлагаемое устройство включено в состав мультимикропрограммной управляющей системы, содержащей N идентичных устройств (модулей) и реализующей комплексную микропрограмму. Работу системы рассмотрим на примере функционирования одного из модулей, например модуля Mi, и будем пояснять примером реализации микропрограммы параллельного алгоритма управления, изображенного на фиг.4.

Первоначально все регистры и триггеры, входящие с состав устройства (фиг.1), а также счетчик 58 адреса (фиг.2) находятся в состоянии логического нуля. Нулевой сигнал с прямого выхода триггера 10 управления запрещает работу генератора 11 тактовых импульсов; нулевой код с выхода регистра 15 кода инициализации через элемент ИЛИ 36 блокирует элемент И 30, а нулевой код с выхода регистра 4 поступает на выход 51 микроопераций устройства. В блоке 1 в ячейках с ненулевыми адресами размещены микрокоманды, образующие параллельные и последовательные участки микропрограмм, закрепленные за текущим устройством, а в ячейках блока 12 памяти начальных адресов записаны коды и адреса инициализации, соответствующие различным операциям (микропрограмм).

Функционирование управляющей системы начинается с момента подачи на входы ее модулей кода номера выполняемой операции s. Код операции (КОП) формируется устройством управления верхнего уровня (УУВУ), например центральным процессором, и в сопровождении импульса настройки одновременно передается на входы 47 номера операции всех устройств в составе системы. КОП с входа 47 модуля Mi поступает на адресный вход блока 12 и формирует на его выходе код настройки L

Импульс настройки с входа 47.1 устройства поступает на вход установки триггера 20 и переключает его в единичное состояние, инициируя тем самым начало процесса настройки устройства на реализацию микропрограммы s. Одновременно импульс настройки передается на вход элемента 46 задержки. Единичный и нулевой сигналы, образующиеся соответственно на прямом и инверсном выходах триггера 20, поступают на управляющие входы коммутаторов 18 и 19 и настраивают их соответственно на прием адреса инициализации с выхода 12.1 блока 12 и на прием кода инициализации с выхода 12.2 блока 12. Код инициализации модуля K

Импульс настройки со сдвигом во времени, достаточным для фиксации кода настройки L

В то же время адрес инициализации A

Одновременно импульс настройки с выхода элемента 46 (фиг. 1) поступает на счетный вход триггера 20 и задним фронтом возвращает его в исходное состояние. Нулевой и единичный сигналы, возникающие соответственно на прямом и инверсном выходах триггера 20, поступают на управляющие входы коммутаторов 18 и 19 и настраивают их на прием информации соответственно с выхода 1.1 и выхода 1.2 блока 1.

На этом процесс настройки i-го устройства на реализацию микропрограммы s завершается. Аналогично осуществляется настройки остальных устройств.

В результате настройки системы на реализацию алгоритма (микропрограммы), представленного на фиг. 4, в регистры 5 первого, второго, третьего, четвертого, пятого устройств записываются адреса инициализации A1(0), A2(0), A3(0), A4(0), A5(0), соответствующие участкам (начальным микрокомандам участков) M

После настройки системы на выполнение s-й микропрограммы на вход 49 устройства (модуля) Mi, за которым закреплен начальный последовательный участок данной микропрограммы (в рассматриваемом примере модуля M1), подается импульс запуска. Этот импульс через элемент ИЛИ 31 поступает на счетный вход триггера 10 и устанавливает триггер 10 в единичное состояние. Единичный сигнал с прямого выхода триггера 10 поступает на вход запуска генератора 11 и разрешает формирование на его входах импульсных последовательностей t1 и t2. Одновременно отрицательный перепад уровня сигнала, возникающий на инверсном входе триггера 10, воздействует на одновибратор 41 и возбуждает на его выходе импульс R.

Импульс R через элемент ИЛИ 33 проходит на выход 52 устройства, поступает на входы 50.i остальных аналогичных устройств и передним фронтом устанавливает i-е разряды регистров 3 в состояние логической единицы, "сообщая" тем самым о начале реализации микропрограммы (функционирования i-го устройства). Таким образом, в регистре 3 каждого устройства системы формируется код (вектор), отображающий текущее состояние остальных устройств. В рассматриваемом примере (фиг. 4) после инициализации последовательного участка M

Первый импульс t1 с выхода генератора 11 поступает на вход синхронизации блока 2 формирования адреса микрокоманд (фиг. 2) и передается на первый вход элемента И 56 и прямой вход элемента И 57. Так как элемент И 56 заблокирован нулевым сигналом с выхода коммутатора 55 условий, а элемент И 57 открыт, импульс t1 через элемент И 57 проходит на вход записи счетчика 58 и передним фронтом фиксирует в нем ранее сформированный адрес инициализации A

Предположим, что считанная микрокоманда имеет формат A (фиг. 3). В этом случае на выходе 1.1 блока 1 появляется принудительный адрес следующей микрокоманды Aп и код опрашиваемого логического условия (логических условий) ЛУ, на выходе 1.1 формируется код микроопераций M0, а на выходе 1.3 образуются значения управляющих меток M1, M2 и M3, определяющие формат и способ обработки считанной микрокоманды (для микрокоманды формата A M1 = M2 = M3 = 0).

Поскольку триггеры 20 и 22 находятся в состоянии логического нуля, адрес принудительного перехода Aп и код логического условия с выхода 1.1 блока 1 через коммутатор 18 поступают соответственно на первый вход сумматора 14 и информационный вход регистра 13. Адрес Aп без модификации проходит на выход сумматора 14 и устанавливается на информационном входе регистра 5.

Одновременно код микроопераций с выхода 1.2 блока 1 подается на информационный вход регистра 4, а признак формата микрокоманды "000" с выхода 1.3 блока 1 поступает на информационный вход регистра 6. Импульс t2 с первого выхода генератора 11 поступает на входы синхронизации регистров 6, 13 и через элемент ИЛИ 35 на вход синхронизации регистра 5 и передним фронтом производит запись соответствующих полей считанной микрокоманды. Кроме того, импульс t2 подается на вход элемента 45 задержки.

Нулевой сигнал с выхода 9 регистра 6 блокирует элемент И 28, а нулевой сигнал с выхода 8 регистра 6 формирует нулевой сигнал на выходе элемента И 27, а также открывает элемент И 26. Импульс t2 со сдвигом во времени, соответствующим установлению информации на выходах регистра 6, появляется на выходе элемента 45 и, проходя через элемент 26 на вход синхронизации регистра 4, производит запись в регистр 4 кода микроопераций. Данный код с выхода регистра 4 передается на выход 51 устройства и инициирует выполнение требуемых микроопераций объектом управления.

Нулевой сигнал с выхода 7 регистра 6 поступает на управляющие входы коммутатора 55 условий (фиг. 2) и коммутирует его выход с выходом мультиплексора 53, на информационном входе которого формируются значения логических условий, поступающие с входа 48 логических условий устройства (фиг. 1). В то же время адрес Aп с выхода регистра 5 совместно с кодом логических условий с выхода регистра 13 подается на второй информационный вход блока 2. Затем адрес Aп поступает (фиг. 2) на информационный вход счетчика 58 адреса, а код логических условий подается на управляющий вход мультиплексора 53. Если хотя бы одно из опрашиваемых логических условий истинно, то на выходе мультиплексора 53 возникает сигнал логической единицы, в противном случае на выходе мультиплексора 53 сохраняется нулевой потенциал.

Пусть все опрашиваемые логические условия ложны. Тогда нулевой сигнал с выхода мультиплексора 53 через коммутатор 55 условий проходит на входы элементов И 56 и 57 и разрешает прохождение импульсов через элемент И 57, блокируя при этом элемент И 56. Очередной импульс t1 с выхода генератора 11 через элемент И 57 поступает на вход записи счетчика 58 и производит запись присутствующего на его информационном входе адреса принудительного перехода Aп. Таким образом, осуществляется принудительная адресация следующей микрокоманды.

Пусть теперь некоторые из требуемых логических условий истинны. Тогда на выходе мультиплексора 53 устанавливается единичный сигнал. Этот сигнал через коммутатор 55 условий поступает на входы элементов И 56 и 57 и блокирует элемент И 57, открывая элемент И 56. Импульс t1 через элемент И 56 подается на следующий вход счетчика 58 и передним фронтом увеличивает его содержимое, т. е. адрес инициации A

Далее адрес следующей микрокоманды, сформированной одним из двух указанных выше способов, с выхода счетчика 58 адреса передается (фиг. 1) на адресный вход блока 1 и обеспечивает считывание второй микрокоманды реализуемого участка микропрограммы. Будем считать, что и вторая микрокоманда этого участка имеет формат A. Адрес следующей микрокоманды и код логических условий с выхода 1.1 блока 1 через коммутатор 18 вновь поступают на первый вход сумматора 14 и информационный вход регистра 13 соответственно. Адрес следующей микрокоманды (адрес принудительного перехода Aп) проходит на информационный вход регистра 5. Код микроопераций с выхода 1.2 блока 1 передается на информационный вход регистра 4, а признак формата микрокоманды - на информационный вход регистра 6.

Очередной импульс t2 с выхода генератора 11 фиксирует адрес Aп в регистре 5, код логического условия - в регистре 13, признак формата (вновь имеющий вид "ООО") - в регистре 6. Импульс t2 через элемент 45 задержки и элемент И 26 проходит на вход синхронизации регистра 4 и производит запись кода микроопераций. Далее код микроопераций с выхода регистра 4 поступает на выход 51 устройства, а адрес Aп и код логического условия с выходов регистров 5 и 13 соответственно - на второй информационный вход блока 2 формирование адреса микрокоманд. На выходе блока 2 аналогично рассмотренному формируется исполнительный адрес следующей микрокоманды и из блока 1 считывается третья микрокоманда реализуемого участка микропрограммы.

Далее осуществляется считывание и обработка четвертой, пятой, ..., h-й микрокоманд и устройство продолжает функционировать аналогичным образом до тех пор, пока очередная считанная из блока 1 микрокоманда не будет иметь формат B (фиг. 3). Аналогично осуществляется выполнение других последовательностей и параллельных участков микропрограммы, и в общем случае исполнение участка завершается после считывания устройством как микрокоманды формата B, так и микрокоманд форматов C и D (фиг. 3).

В дальнейшем при описании работы устройства будем полагать, что реализуемый рассматриваемым устройством участок микропрограммы не является начальным.

1. Предположим, что очередная появившаяся на выходе блока 1 микрокоманда имеет формат D. В этом случае i-й модуль системы переходит в режим окончания выполнения параллельного или последовательного участка микропрограммы, осуществляет самонастройку на последующий запуск от другого аналогичного устройства и входит в состояние ожидания.

На выходе 1.3 блока 1 образуется признак формата "001", на выходе 1.1 устанавливается адрес инициации A

Адрес инициализации через коммутатор 18 проходит на первый вход сумматора 14 и, так как на втором входе сумматора 14 находится нулевой код с выхода регистра 17, передается на информационный вход регистра 5; нулевой код логических условий через коммутатор 18 поступает на информационный вход регистра 13. Код инициализации K

Поскольку рассматриваемая микрокоманда имеет формат D, на выходах 7 и 8 регистра 6 появляется нулевой, а на выходе 9 - единичный уровень сигнала (метка M3 конца участка микропрограммы). Нулевой сигнал с выхода 8 регистра 6 блокирует элемент И 27, а единичная метка M3 открывает элемент И 28 и, кроме того формирует нулевой сигнал на выходе элемента И 26. Импульс t2 с выхода генератора 11 проходит через элемент 45 задержки и передается на выход элемента И 28. Далее указанный импульс, во-первых, через элемент ИЛИ 37 поступает на вход синхронизации регистра 15 и передним фронтом записывает в регистр 15 код инициации K

Код инициации K

Импульс Q через элемент ИЛИ 33 проходит на выход 52 устройства и, поступая затем на входы 50.i остальных аналогичных устройств, возвращает i-е разряды (триггеры) регистров 3 в исходное состояние логического нуля. Таким образом, i-й модуль "информирует" другие модули о завершении выполнения закрепленного за ним участка микропрограммы и переходе в пассивное состояние.

2. Если очередная считанная из блока 1 микрокоманда имеет формат B (фиг. 3), то устройство переходит в режим инициализации группы параллельных участков или передачи управления другому (другим) аналогичному устройству.

На выходе 1.1 блока 1 являются адрес следующей микрокоманды (адрес принудительного перехода Aп) и код логических условий, на выходе 1.3 образуется признак формата "010" (M2 = 1), а на выходе 1.2 блока 1 формируется управляющее сообщение MSi(n) = Ki(n) # dAi(n), где n - порядковый номер процесса передачи управления для i-го устройства, (модуля) , Ki(n) - код инициализации параллельных участков, dAi(n) - код коррекции адреса приема управления (инициализации).

Адрес следующей микрокоманды Aп через коммутатор 18 и сумматор 14 проходит на информационный вход регистра 5, код логических условий через коммутатор 18 передается на информационный вход регистра 13, а управляющее сообщение MSi(n) поступает на информационный вход блока 24 тристабильных элементов. Импульс t2 с выхода генератора 11 поступает на входы синхронизации регистров 6, 5 и 13 и фиксирует в них соответственно признак формата микрокоманды "010", адрес Aп и код опрашиваемых логических условий. Нулевой сигнал, образующийся на выходе 9 регистра 6, блокирует элемент И 28, а единичный сигнал - метка M2 запуска параллельных участков (передачи управления) с выхода 8 блокирует элемент И 26 и открывает элемент И 27.

В то же время единичный сигнал с выхода 8 регистра 6 через элемент ИЛИ 32 воздействует на одновибратор 40, формирует на его выходе импульс останова и тем самым переводит триггер 10 в нулевое состояние. Нулевой сигнал с прямого выхода триггера 10 выключает генератор 11, а положительный перепад уровня сигнала с инверсного выхода формирует на выходе одновибратора 42 импульс Q. Импульс Q через элемент ИЛИ 33 поступает на выход 52 устройства и, как было показано ранее, временно возвращает i-е разряды регистров 3 остальных устройств в состояние логического нуля, i-е устройство приостанавливает процесс выполнения микропрограммы.

Одновременно импульс t2 с выхода генератора 11 поступает на вход элемента 45 задержки, появляется на его выходе со сдвигом во времени (достаточным для установления требуемых уровней сигнала на выходах регистра 6) и проходит на выход открытого элемента И 27. Далее импульс t2, во-первых, через элемент ИЛИ 38 устанавливает регистр 4 в состояние логического нуля и, во-вторых, поступает на вход установки триггера 21 передачи управления и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 21 открывает элемент И 29.

Сигнал с шины 25 передачи управления через первоначально открытый нулевым сигналом с выхода элемента И 29 блок 23 поступает на входы элемента ИЛИ-НЕ 39 и формирует на его выходе сигнал состояния шины 25. Если шина 25 занята (осуществляется передача управления между другими модулями системы), то на входах элемента 39 присутствует ненулевой код, а на выходе соответственно формируется сигнал логического нуля. Этот сигнал блокирует элемент И 29 и нулевой сигнал с выхода элемента И 29 не допускает срабатывания одновибратора 43, а также устанавливает выходы блока 24 в состояние высокого импеданса, отключая тем самым выход 1.2 блока 1 от шины 25. Как только шина 25 освобождается, на входах элемента 39 появляется нулевой код, а на выходе формируется сигнал логической единицы. Данный сигнал проходит на выход открытого элемента И 29 и блокирует элементы блока 23, одновременно открывая элементы блока 24. Управляющее сообщение MSi(n) через блок 24 передается на шину 25 и далее поступает на информационные входы блоков 23 остальных модулей управляющей системы.

Одновременно положительный перепад потенциала с выхода элемента И 29 воздействует одновибратор 43 и со сдвигом, соответствующим допустимому времени передачи информации на шину 25, формирует на его выходе импульс. Импульс с выхода одновибратора 43, во-первых, поступает на вход сброса триггера 21, возвращает триггер 21 в нулевое состояние и тем самым вновь блокирует элемент И 29 и соответственно активизирует блок 23 и переводит в высокоимпедансное состояние выходы блока 24, а во-вторых, через элемент ИЛИ 31 подается на счетный вход триггера 10 и переключает его в единичное состояние. Единичный сигнал с прямого выхода триггера 10 запускает генератор 11, а отрицательный перепад уровня сигнала с инверсного выхода формирует импульс R на выходе одновибратора 41. Импульс R через элемент ИЛИ 33 проходит на выход 52 устройства и "информирует" другие устройства управляющей системы о возобновлении выполнения микропрограммы.

Импульс t1 с выхода генератора 11 поступает на вход синхронизации блока 2 формирования адреса микрокоманд и аналогично рассмотренному ранее формирует на его выходе исполнительный адрес очередной микрокоманды. Адрес с выхода блока 2 подается на адресный вход блока 1 и обеспечивает считывание следующей микрокоманды реализуемого участка микропрограммы.

Если i-й модуль системы после инициализации других модулей в соответствии с выполняемым алгоритмом должен перейти в состояние ожидания, то очередная считываемая микрокоманда имеет формат D (фиг. 3) и модуль в соответствии с описанным выше порядком реализации микрокоманд формата D (см. п. 1) осуществляет самонастройку на последующий запуск от другого устройства системы и прекращает работу. Если же очередная микрокоманда имеет формат A, B или C, то модуль переходит к реализации параллельного участка микропрограммы.

В рассматриваемом примере (фиг. 4) модуль M1 завершает выполнение начального последовательного участка M

Прием и анализ управляющих сообщений, выдаваемых при передаче управления или инициализации других модулей системы, рассмотрим на примере функционирования модуля Mj (j≠i).

Управляющее сообщение MSi(n) с шины 25 передачи управления проходит через открытый блок 23 тристабильных элементов. Дале код инициализации Ki(n) поступает на второй вход схемы 16 сравнения и сравнивается с кодом инициализации j-го модуля K

Если Ki(n) не совпадает с кодом K

В противном случае (Ki(n) = K

В свою очередь, отрицательный перепад уровня сигнала с инверсного выхода триггера 22 воздействует на одновибратор 44 и с задержкой во времени, требуемой для формирования модифицированного адреса инициализации на выходе сумматора 14, возбуждает на выходе одновибратора 44 импульс. Этот импульс, во-первых, через элемент ИЛИ 35 проходит на вход синхронизации регистра 5 и передним фронтом обеспечивает запись полученного адреса A

В то же время единичный сигнал с прямого выхода триггера 10 запускает генератор 11, а отрицательный перепад уровня сигнала с инверсного выхода формирует импульс R на выходе одновибратора 41. Импульс R через элемент ИЛИ 33 поступает на выход 52 устройства и устанавливает в единичное состояние j-е разряды регистров 3 других устройств, "сообщая" тем самым о начале выполнения участка микропрограммы. "Скорректированный" адрес инициализации с выхода регистра 5 передается на информационный вход счетчика 58 адреса (фиг. 1 и 2), а нулевой код логических условий с выхода регистра 13 поступает на управляющий вход мультиплексора 53 и формирует на его выходе нулевой сигнал. Поскольку в регистре 6 находится код "001" (см. п. 1), нулевой сигнал с выхода 7 регистра 6 поступает на управляющий вход коммутатора 55 условий и подключает его выход к выходу мультиплексора 53. Нулевой сигнал с выхода мультиплексора 53 через коммутатор 55 проходит на входы элементов И 56 и 57 и блокирует элемент И 56, разрешая в то же время прохождение импульсов через элемент И 57.

Импульс t1 с выхода генератора 11 поступает на вход синхронизации блока 2, проходит через открытый элемент И 57 на вход записи счетчика 58 и производит запись адреса инициализации A

В рассматриваемом примере (фиг. 4) код инициализации K1(1), выдаваемый модулем M1 после выполнения участка M

В случае, если модуль Mi реализует только некоторые из альтернативных участков какого-либо фрагмента микропрограммы, то за данным модулем закрепляются фиктивные участки, каждый из которых образован единственной микрокомандой формата D (фиг. 3), обеспечивающей перенастройку устройства на следующий запуск. Указанный случай иллюстрируется на фиг. 5: за модулем M3 закреплен альтернативный участок M

Таким образом, независимо от значения логического условия x1\/x2 обеспечивается возможность запуска модуля M3 после поступления кода инициализации K1(2)=K6 с адреса A3(2).

В процессе функционирования i-й модуль может опрашивать состояние других модулей системы (параллельных участков) и использовать результат опроса в качестве логического условия. Переход устройства в режим опроса состояния параллельных участков осуществляется после появления на выходе блока 1 микрокоманды формата C (фиг. 3). На выходе 1.1 блока 1 формируются адреса следующей микрокоманды (адрес принудительного перехода Aп) и код опроса параллельных участков (КО), на выходе 1.2 появляется код микроопераций, а на выходе 1.3 - признак формата микрокоманды "100" (M1=1).

Адрес Aп через коммутатор 18 и сумматор 14 проходит на информационный вход регистра 5, код опроса параллельных участков КО через коммутатор 18 поступает на информационный вход регистра 13, а код микроопераций - на информационный вход регистра 4. Очередной импульс t2 с выходе генератора 11 поступает на входы синхронизации регистров 5, 6 и 13 и производит запись адреса Aп, кода "100" и кода КО. Нулевые сигналы с выходов 8 и 9 регистра 6 блокируют элементы И 27 и 28 и открывают элемент И 26, а единичный сигнал - метка M1 опроса состояния параллельных участков - поступает на управляющий вход блока 2 (фиг. 2) и коммутирует выход коммутатора 55 с выходом мультиплексора 54. Одновременно импульс t2, пройдя через элемент 45 задержки (фиг. 1) и открытый элемент И 26, подается на вход синхронизации регистра 4, фиксирует код микроопераций и тем самым инициирует выполнение требуемых микроопераций объектом управления.

Адрес Aп с выхода регистра 5 передается (фиг. 2) на информационный вход счетчика 58 адреса, а код опроса параллельных участков КО с выхода регистра 13 подается на управляющий вход мультиплексора 54, на информационный вход которого поступает вектор (код) состояния управляющей системы, формируемый на выходе регистра 3 (фиг. 1, 2). В соответствии с кодом КО, единичные разряды которого определяют опрашиваемые устройства (участки), на выходе мультиплексора 54 образуется обобщенный сигнал, характеризующий состояние опрашиваемых параллельных участков: завершены/не завершены.

Первоначально предположим, что среди опрашиваемых параллельных участков имеются незавершенные. Тогда сигнал на выходе мультиплексора 54 принимает единичное значение и блокирует коммутатор 55, формируя на его выходе сигнал логического нуля. Нулевой сигнал с выхода коммутатора 55 разрешает прохождение импульсов через элемент И 57, закрывая при этом элемент И 56. Очередной импульс t1 с выхода генератора 11 через элемент И 57 проходит на вход записи счетчика 58 и производит запись адреса Aп, осуществляя тем самым принудительную адресацию следующей микрокоманды.

Теперь допустим, что все требуемые (опрашиваемые) параллельные участки завершены. Тогда на выходе мультиплексора 54 образуется нулевой сигнал. Этот сигнал поступает на инверсный информационный вход коммутатора 55 условий и устанавливает на выходе коммутатора 55 единичный сигнал. Единичный сигнал с выхода коммутатора 55 разрешает работу элемент И 56 и блокирует элемент И 57. Импульс t1 через элемент И 56 передается на суммирующий вход счетчика 58 и увеличивает его содержимое на единицу, обеспечивая естественный порядок адресации следующей микрокоманды.

Исполнительный адрес следующей микрокоманды, сформированный с учетом текущего состояния определенного подмножества параллельных участков, с выхода счетчика 58 поступает на адресный вход блока 1 (фиг. 1) и обеспечивает считывание очередной микрокоманды. Далее работа устройства аналогична функционированию в ранее рассмотренном режиме выполнения последовательного участка микропрограммы.

Функционирование предлагаемого устройства завершается в случае, если в операционной части считанной микрокоманды указана единичная метка конца работы. После записи операционной части микрокоманды в регистр 4 код микроопераций поступает на выход 51 устройства, а метка конца работы появляется на выходе 51.1. Единичный сигнал с выхода 51.1 через элемент ИЛИ 32 проходит на вход одновибратора 40 и формирует на его выходе импульс останова устройства. Данный импульс поступает на вход сброса триггера 10, устанавливает этот триггер в состояние логического нуля и, таким образом, выключает генератор 11. Считывание микрокоманд из блока 1 прекращается, состояние регистров 3 всех устройств управляющей системы становится нулевым и устройство переходит в состояние ожидания сигнала на исполнение очередной операции.

Реализация алгоритма, изображенного на фиг. 4, завершается после выполнения последовательного участка M

Оценим эффективность предлагаемого технического решения по отношению к прототипу.

Число внешних входов и выходов устройств, требуемых для построения управляющей системы, содержащей N+1 модулей, при использовании прототипа составляет R0=2N(m+2), где  , M - емкость микропрограммной памяти,

, M - емкость микропрограммной памяти,  - ближайшее целое число, не меньшее a. Из указанных R0 входов/выходов 2mN предназначены для приема/выдачи адресов передачи управления и 4N - для приема/выдачи меток начала/конца параллельных участков микропрограмм.

- ближайшее целое число, не меньшее a. Из указанных R0 входов/выходов 2mN предназначены для приема/выдачи адресов передачи управления и 4N - для приема/выдачи меток начала/конца параллельных участков микропрограмм.

При построении системы из N+1 однотипных модулей на основе предлагаемого устройства требуемое число внешних входов и выходов составляет R= 2(m*+D)+N+1, где m* ≤ m - разрядность кода коррекции адреса, D=maxi{di},  - необходимая разрядность кода инициализации для i-й микропрограммы, Ci - число различных точек инициализации участков (вершин распараллеливания) для i-й микропрограмм. Как правило (см., например, фиг. 4), число Ci значительно меньше числа параллельных и последовательных участков микропрограммы и тем более микрокоманд, поэтому D < m. Из указанных R внешних входов и выходов 2(m*+D) используются для приема и выдачи управляющих сообщений, один выход - для выдачи управляющей метки начала/конца участка и N входов - для приема управляющих меток от других устройств.

- необходимая разрядность кода инициализации для i-й микропрограммы, Ci - число различных точек инициализации участков (вершин распараллеливания) для i-й микропрограмм. Как правило (см., например, фиг. 4), число Ci значительно меньше числа параллельных и последовательных участков микропрограммы и тем более микрокоманд, поэтому D < m. Из указанных R внешних входов и выходов 2(m*+D) используются для приема и выдачи управляющих сообщений, один выход - для выдачи управляющей метки начала/конца участка и N входов - для приема управляющих меток от других устройств.

Соответственно значений величин R0 и R для различных значений N и D при условии, что m*= m= 8, дается в таблице. Анализ данных, представленных в таблице, показывает, что с увеличением числа модулей N разность R0-R существенно возрастает и применение прототипа при построении систем, содержащих более 8-10 модулей, нецелесообразно (особенно при реализации устройств в виде СБИС). В то же время предлагаемое устройство может использоваться при построении управляющих систем, включающих более 10 модулей (максимальное число модулей ограничивается только нагрузочной способностью элементов блока 24 и элемента ИЛИ 33 (фиг. 1)). Так как инициализация группы параллельных участков в системе, построенной на базе предлагаемого устройства, осуществляется одновременно, то при реализации алгоритмов (микропрограмм), не содержащих нескольких одновременно запускаемых групп параллельных участков, быстродействие системы не снижается. При наличии указанных групп участков быстродействие системы несколько снижается (вследствие невозможности одновременной передачи по шине 25 нескольких управляющих сообщений и необходимости ожидания освобождения шины), однако вероятность появления значительного числа таких групп невелика.

Таким образом, введение в состав устройства дополнительные элементы и обусловленные ими связи обеспечивают существенное сокращение числа внешних входов и выходов устройства и снижение зависимости этого числа от размерности N управляющей системы при сохранении исходного уровня функциональной гибкости системы и практически без потерь быстродействия. Указанные особенности позволяют существенно расширить область целесообразного применения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| УСТРОЙСТВО ПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2146064C1 |

| МОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2112269C1 |

| МОДУЛЬ МУЛЬТИМИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1999 |

|

RU2151421C1 |

| МОДУЛЬ СИСТЕМЫ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2145434C1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1999 |

|

RU2168198C1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ | 2000 |

|

RU2166793C1 |

Изобретение относится к области цифровой вычислительной техники, применяется при построении алгоритмически распределенных устройств (систем) микропрограммного управления вычислительных и управляющих систем высокой производительности. Устройство содержит блоки постоянной памяти и формирования адреса микрокоманд, регистры состояния, микроопераций, адреса следующей микрокоманды и формата микрокоманды, триггер управления, генератор тактовых импульсов, два элемента И, элемент ИЛИ, одновибратор, два элемента задержки, блок памяти начальных адресов, регистры кода логического условия и кода инициализации, сумматор, схему сравнения, буферный регистр, коммутаторы адреса и кода инициализации, триггеры режима, передачи управления и приема управления, два блока тристабильных элементов, шину передачи управления, три элемента И, шесть элементов ИЛИ, элемент ИЛИ-НЕ и четыре одновибратора. 1 з.п. ф-лы, 1 табл., 5 ил.

| US, патент, 4799151, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| DE, патент, 3311475, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| FR, заявка, 2472781, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1427366, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| SU, авторское свидетельство, 1647566, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-05-20—Публикация

1997-03-25—Подача