Изобретение относится к электронике и предназначено для использования в интегральных микросхемах на комплементарных транзисторах структуры металл-диэлектрик-полупроводник (КМДП).

Известно использование в КМДП-схемах в качестве источников опорного напряжения делителей напряжения, образованных последовательно соединенными МДП-транзисторами, например, см. статью Y.P. Tsividis "Design Considerations in Single-Channel MOS Analog Integrated Circuits - A Tutarial." IEEE Journal of Solid-State Circuits, Vol. SC-13, N. 3, June 1978, p. 385, Fig. 4. Недостатком подобных устройств является зависимость вырабатываемых опорных напряжений от напряжения питания.

В значительной степени эта зависимость уменьшена в источнике опорного напряжения, описанном в патенте США N 4507572, НКИ 307-295 R, МКИ H 03 R 3/353, G 05 F 3/08, опубликованном 26 марта 1985 г. Данное устройство по технической сущности наиболее близко к изобретению.

Наиболее близкий аналог содержит первый и второй резисторы, с первого по третий МДП-транзисторы с индуцированным каналом p-типа, истоки которых подключены к шине положительного напряжения питания, а затворы соединены и подключены к стоку первого p-МДП-транзистора, первый и второй МДП-транзисторы с индуцированным каналом n-типа, затворы которых соединены и подключены к соединенным стокам вторых p- и n-МДП-транзисторов, сток первого p-МДП-транзистора соединен со стоком первого n-МДП-транзистора, исток которого подключен к первому выводу первого резистора, сток третьего p-МДП-транзистора соединен с первым выводом второго резистора и является выходом опорного напряжения, вторые выводы первого и второго резисторов и исток второго n-МДП-транзистора подключены к шине отрицательного напряжения питания. Устройство работает следующим образом. Первый и второй p-МДП-транзисторы образуют токовое зеркало, формирующее ток стока второго p-МДП-транзистора, увеличенный по отношению к току стока первого p-МДП-транзистора в пропорции, равной отношению крутизн этих транзисторов. Ток стока IС второго p-МДП-транзистора протекает в шину отрицательного напряжения питания через канал второго n-МДП-транзистора, обуславливая возникновение напряжения между его истоком и затвором UЗИ в соответствии с известной формулой

IC = β(UЗИ-UП)2,

где β и UП - соответственно крутизна и пороговое напряжение МДП-транзистора. Первый n-МДП-транзистор, проводя меньший, чем второй n-МДП-транзистор ток и обладая не меньшей, чем у него крутизной, согласно той же формуле имеет меньшее, чем у второго n-МДП-транзистора напряжение затвор-исток. Эта разность, будучи приложенной к первому резистору, определяет величину тока стока первого p-МДП-транзистора.

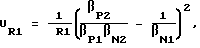

Приняв пороговые напряжения у транзисторов одинакового типа проводимости равными, можно вывести следующую формулу для напряжения на первом резисторе:

где βN1, βN2, βP1, βP2 - крутизны первого и второго n-МДП-транзисторов, первого и второго p-МДП-транзисторов соответственно, а R1 - сопротивление первого резистора.

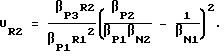

Выходное напряжение источника формирует второй резистор, в котором протекает ток стока третьего p-МДП-транзистора, состоящий в пропорции к току первого резистора, равной отношению крутизн βP3 и βP1 третьего и первого p-МДП-транзисторов, таким образом

Недостатком этого устройства являются зависимость вырабатываемого опорного напряжения от величин крутизн n-канальных МДП-транзисторов, подверженных дестабилизирующему воздействию различных производственных и эксплуатационных факторов.

Влияние параметров p-МДП-транзисторов и резисторов выражается через отношения их крутизн и сопротивлений соответственно, которые можно считать постоянными, так как при интегральном исполнении определяются только конструкцией: они соответственно прямо и обратно пропорциональны отношениям ширин и длин каналов транзисторов и тел резисторов.

Задачей настоящего изобретения является достижение технического результата, заключающегося в повышении стабильности выходного опорного напряжения источника.

Поставленная задача решается тем, что в источник опорного напряжения, содержащий первый и второй резисторы, с первого по третий МДП-транзисторы с индуцированным каналом первого типа проводимости, истоки которых подключены к первой шине напряжения питания, а затворы соединены и подключены к стоку первого МДП-транзистора первого типа, первый и второй МДП-транзисторы с индуцированным каналом второго типа проводимости, затворы которых соединены и подключены к соединенным стокам вторых МДП-транзисторов первого и второго типов, сток первого МДП-транзистора первого типа соединен со стоком первого МДП-транзистора второго типа, исток которого подключен к первому выводу первого резистора, сток третьего МДП-транзистора первого типа соединен с первым выводом второго резистора и является выходом опорного напряжения, второй вывод второго резистора соединен с истоком второго МДП-транзистора второго типа, введены первый и второй диоды на p-n-переходах, области первого типа проводимости которых подключены ко вторым выводам первого и второго резисторов соответственно, а области второго типа проводимости соединены со второй шиной напряжения питания.

Таким образом, отличительными признаками изобретения является то, что в устройство введены первый и второй диоды и изменены связи.

Указанное выполнение источника опорного напряжения позволяет снизить зависимость выходного напряжения от параметров МДП-транзисторов и получить температурную стабилизацию по ширине запрещенной зоны полупроводникового материала диодов.

Проведенные патентные исследования подтвердили новизну изобретения, а также показали, что в литературе отсутствуют данные, указывающие на влияние отличий патентуемого изобретения на достижение технического результата. Поэтому следует считать, что патентуемое изобретение соответствует критериям новизны и изобретательского уровня.

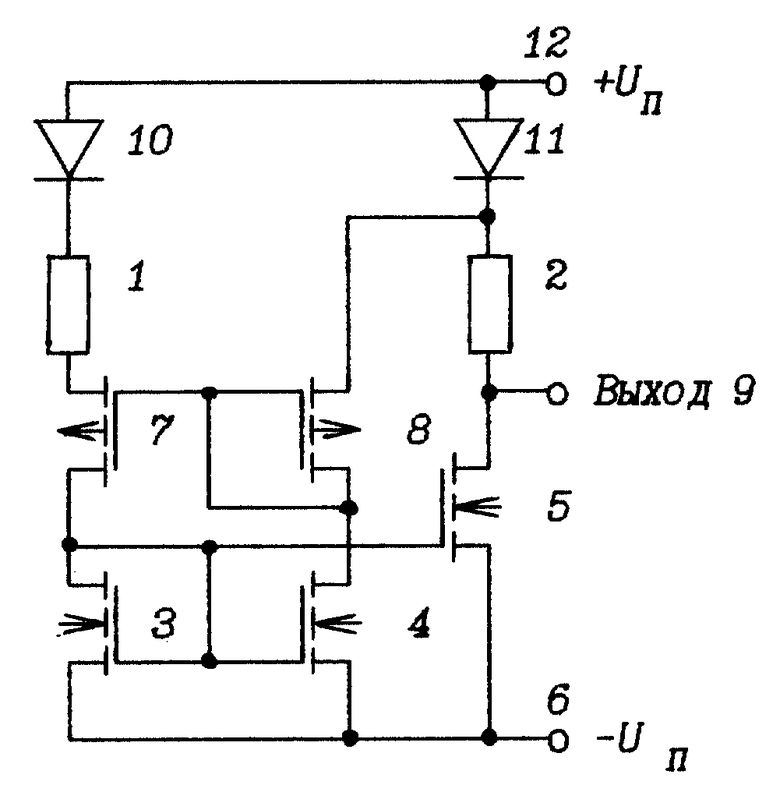

Изобретение поясняется чертежом, на котором изображена принципиальная электрическая схема источника опорного напряжения.

Для упрощения понимания работы схемы на чертеже и в последующем описании проводимости полупроводников первого и второго типов представлены соответственно как n-тип и p-тип, а первое и второе напряжения питания - соответственно как отрицательное и положительное.

Источник опорного напряжения cодержит первый и второй резисторы 1 и 2, с первого по третий МДП-транзисторы 3-5 с индуцированным каналом n-типа проводимости, истоки которых подключены к отрицательной шине 6 напряжения питания, а затворы соединены и подключены к стоку первого n-МДП-транзистора 3, первый и второй МДП-транзисторы 7 и 8 с индуцированным каналом p-типа проводимости, затворы которых соединены и подключены к соединенным стокам вторых МДП-транзисторов 4 и 8 n- и p-типов, сток первого n-МДП-транзистора 3 соединен со стоком первого p-МДП-транзистора 7, исток которого подключен к первому выводу первого резистора 1, сток третьего n-МДП-транзистора 5 соединен с первым выводом второго резистора 2 и является выходом 9 опорного напряжения, первый и второй диоды 10 и 11, аноды которых соединены с положительной шиной 12 напряжения питания, катод первого диода подключен ко второму выводу первого резистора 1, а катод второго диода 11 соединен с истоком второго p-МДП-транзистора 8 и вторым выводом второго резистора 2.

Устройство работает следующим образом.

N-МДП-транзисторы 3, 4 и 5 образуют токовое зеркало, в котором формируемые токи стоков n-МДП-транзисторов 4 и 5 равны определяющему току стока n-МДП-транзистора 3, увеличенному пропорционально отношениям крутизн β транзисторов 4 и 5 к крутизне транзистора 3. Отношение крутизн p-МДП-транзисторов 7 и 8 равно отношению крутизн n-МДП-транзисторов 3 и 4, что обеспечивает равенство напряжений UИ7, UИ8 на их истоках.

Пользуясь известной формулой для вольт-амперной характеристики МДП-транзистора в области насыщения, когда прямо приложенное напряжение между его стоком и истоком UСИ превосходит превышение напряжением затвор-исток UЗИ своего порогового значения UП - UСИ > UЗИ - UП,

IC = β(UЗИ-UП)2, (1)

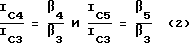

где IС - ток стока, а β - крутизна, и приняв значения пороговых напряжений UП равными для транзисторов одного типа, легко вывести равенства

для транзисторов 3, 4 и 5, имеющих одинаковые напряжения затвор-исток, и доказать равенство

UЗИ7 - UЗИ8 (3)

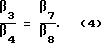

для транзисторов 7 и 8, токи стоков которых соответственно равны токам стоков транзисторов 3 и 4 и, следовательно, относятся как β3/β4 согласно (2), а крутизны пропорциональны крутизнам транзисторов 3 и 4 -

Из выражения (3) следует равенство напряжений на истоках транзисторов 7 и 8, имеющих соединенные затворы.

Площадь p-n-перехода SD диода 10 превосходит площадь диода II, поэтому напряжение на диоде 11 вследствие большей плотности тока выше, чем на диоде 10.

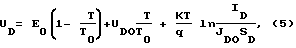

Зависимость напряжения UD на полупроводниковом диоде от протекающего тока ID и абсолютной температуры T может быть выражена формулой

где E0 - ширина запрещенной зоны полупроводникового материала, при T0 = 298 К у кремния E0 = 1,205 В;

K = 1,38 • 10-23 Дж/град - постоянная Больцмана;

q = 1,6 • 10-19 Кл - заряд электрона;

UD0 - напряжение на диоде при плотности тока JD0 и температуре T0;

SD - площадь p-n-перехода диода.

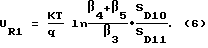

Приняв ток диода 10 равным току IС3 стока n-МДП-транзистора 3 и ток второго диода 11 равным сумме токов IС4 и IС5 стока n-МДП-транзисторов 4 и 5, по формулам (2) и (5) можно выразить разность напряжений на диодах 10 и 11, приложенную к резистору 1,

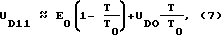

Смещение выходного опорного напряжения относительно положительного напряжения питания равно напряжению на диоде 11, которое можно записать как

сложенному с напряжением на резисторе 2, определяемому напряжением на резисторе 1 согласно формуле

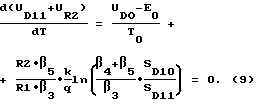

Формулы (6) - (8) демонстрируют устойчивость вырабатываемого напряжения к воздействию дестабилизирующих факторов тем, что в них присутствуют только конструктивные параметры элементов схемы, физический параметр E0 полупроводникового материала и опорная точка UD0 вольт-амперной характеристики диодов, являющаяся константой для каждого конкретного производственно-технологического процесса. Условием температурной компенсации опорного напряжения является равенство нулю производной от сумм UD11 и UR2 по температуре:

Из формулы (9) можно заключить, что термокомпенсация будет достигнута, если конструктивные параметры элементов схемы позволят выполнить равенство

Таким образом, высокая стабильность источника опорного напряжения достигается тем, что вырабатываемое им напряжение определяется конструктивными параметрами элементов, задающими отношения сопротивлений резисторов, крутизн МДП-транзисторов одинаковых типов проводимости и площадей диодов, не зависящих от воздействий производственных и эксплуатационных факторов, и реализации принципа температурной компенсации по ширине запрещенной зоны.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОЧНИК ОПОРНОГО НАПРЯЖЕНИЯ | 2018 |

|

RU2673243C1 |

| ИСТОЧНИК ТОКА | 2016 |

|

RU2620592C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ ЭСЛ-КМОП | 1994 |

|

RU2097914C1 |

| УСТРОЙСТВО СЛОЖЕНИЯ С УСКОРЕННЫМ ПЕРЕНОСОМ | 2000 |

|

RU2198421C2 |

| ЛОГИЧЕСКИЙ ВЕНТИЛЬ | 2014 |

|

RU2546302C1 |

| УСИЛИТЕЛЬ МОЩНОСТИ | 1991 |

|

RU2017324C1 |

| СХЕМА УПРАВЛЕНИЯ ПОСЛЕДОВАТЕЛЬНЫМ КЛЮЧОМ НА МДП-ТРАНЗИСТОРЕ | 2006 |

|

RU2312456C1 |

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| ОДНОТАКТНЫЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 1992 |

|

RU2009604C1 |

| ИСТОЧНИК ОБРАЗЦОВЫХ НАПРЯЖЕНИЙ | 1993 |

|

RU2076351C1 |

Изобретение относится к электронике и предназначено для использования в интегральных микросхемах на КМДП-транзисторах, его задачей является повышение стабильности выходного опорного напряжения источника, достигаемое за счет введения первого и второго диодов (10, 11) и изменения связей. На схеме устройства обозначены также первый и второй резисторы (1 и 2), с первого по третий n-МДП-транзисторы (3 - 5), отрицательная шина (6) напряжения питания, первый и второй n-МДП-транзисторы (7 и 8), выход (9) опорного напряжения и положительная шина (12) напряжения питания. Технический результат: изобретение позволяет скомпенсировать отклонения параметров элементов под влиянием различных производственных и эксплуатационных факторов и реализовать принцип температурной компенсации по ширине запрещенной зоны. 1 ил.

Источник опорного напряжения, содержащий первый и второй резисторы, с первого по третий МДП-транзисторы с индуцированным каналом первого типа проводимости, истоки которых подключены к первой шине напряжения питания, а затворы соединены и подключены к стоку первого МДП-транзистора первого типа, первый и второй МДП-транзисторы с индуцированным каналом второго типа проводимости, затворы которых соединены и подключены к соединенным стокам вторых МДП-транзисторов первого и второго типов, сток первого МДП-транзистора первого типа соединен со стоком первого МДП-транзистора второго типа, исток которого подключен к первому выводу первого резистора, сток третьего МДП-транзистора первого типа соединен с первым выводом второго резистора и является выходом опорного напряжения, второй вывод второго резистора соединен с истоком второго МДП-транзистора второго типа, отличающийся тем, что в него введены первый и второй диоды на p-n-переходах, области первого типа проводимости которых подключены ко вторым выводам первого и второго резисторов соответственно, а области второго типа проводимости соединены со второй шиной напряжения питания.

| US 4507572 A, 26.03.85 | |||

| Высоковольтный стабилизатор напряжения | 1982 |

|

SU1026130A1 |

| ПРИСПОСОБЛЕНИЕ ДЛЯ УСИЛЕНИЯ ЗВУКА | 1921 |

|

SU7804A1 |

| US 4571536 A, 18.02.86 | |||

| US 3522521 A1, 04.08.70. | |||

Авторы

Даты

1999-06-10—Публикация

1998-04-29—Подача