Данное изобретение относится к электронным устройствам, в частности к усилителям, и может применяться для построения интегральных схем.

Известное техническое решение [Д. Коннелли. Аналоговые интегральные схемы, перевод с англ. М.: Мир, 1977, с. 118, фиг. 333] содержит входную дифференциальную пару на транзисторе Т5 и Т6, отражатель тока ОТ-1 на транзисторах Т1 и Т2, отражатель тока ОТ-2 на транзисторах Т3 и Т4 и источник стабильного тока.

Недостатком его является невысокий коэффициент усилия.

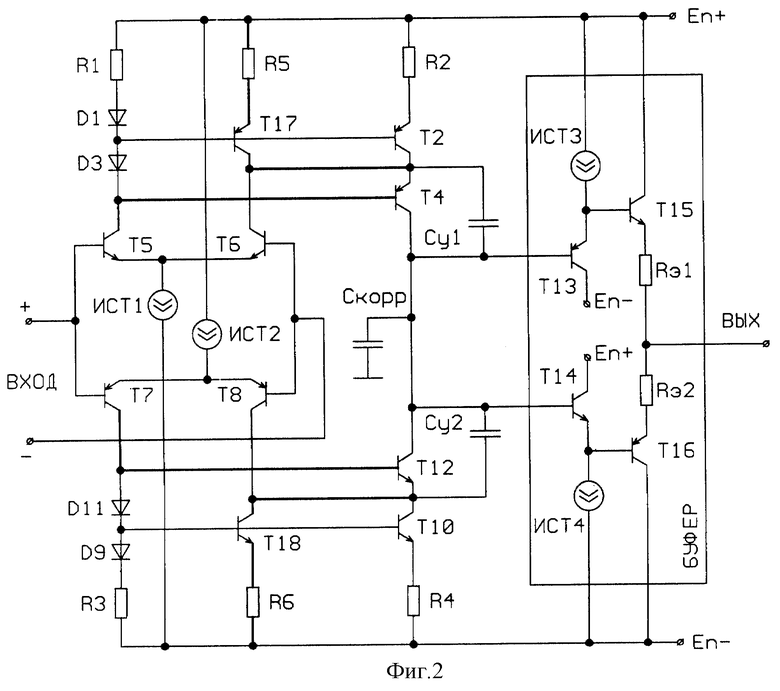

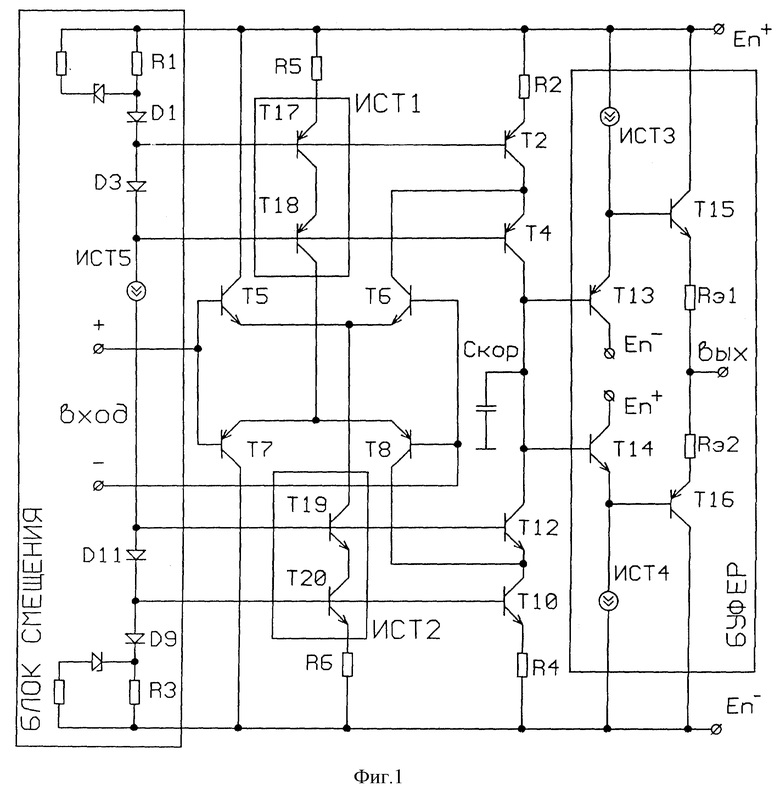

Наиболее близким техническим решением является двухтактный операционный усилитель с основным усилительным блоком (фиг.1) [Dr. Yohn Lidgey, Analogue Action, 1 GHz gain-bandwidth operational amplifiers, Electronics & wireless world, Sep, 1989, T9, OY EL2038 Elarttec], содержащий первую входную дифференциальную пару на транзисторах Т5, Т6 первого типа проводимости со связанными между собой эмиттерами, базы которых подключены к входным клеммам (+) и (-) соответственно, при этом коллектор транзистора Т5 подключен к шине источника положительного питания Еn +, а коллектор транзистора Т6 соединен с коллектором транзистора Т2 и с эмиттером транзистора Т4, коллектор которого соединен с коллектором транзистора Т12 и входом буфера, база транзистора Т4 соединена с базой транзистора Т18 и с катодом диода D3 и с одним концом источника стабильного тока ИСТ5, а анод диода D3 соединен с катодом диода D1, анод которого соединен через резистор R1 с источником положительного напряжения Еn + и с базами транзисторов Т17 и Т18, эмиттеры которых через резисторы R5 и R2 соответственно подключены к источнику положительного напряжения Еn +, при этом коллектор транзистора Т17 соединен с эмиттером транзистора Т18, коллектор которого соединен с эмиттерами транзисторов Т7, Т8; вторую входную дифференциальную пару на транзисторах Т7, Т8 второго типа проводимости со связанными между собой эмиттерами, базы которых подключены к базам транзисторов Т5, Т6 и входным клеммам (+) и (-) соответственно, при этом коллектор транзистора Т7 подключен к шине источника отрицательного питания Еn -, а коллектор транзистора Т8 соединен с коллектором транзистора Т10 и с эмиттером транзистора Т12 и со входом буферного выходного каскада, а база транзистора Т12 соединена с базой транзистора Т19 и с анодом диода D11 и со вторым концом источника стабильного тока ИСТ5, а катод диода D11 соединен с анодом диода D9, а катод диода D9 через резистор R3 соединен с шиной источника отрицательного напряжения Еn - и с базами транзисторов Т10 и Т20, причем коллектор транзистора Т20 соединен с эмиттером транзистора Т19, коллектор которого соединен с эмиттерами транзисторов Т5 и Т6.

Недостатком прототипа является ограниченный (невысокий) коэффициент усиления напряжения из-за использования одного (двухтактного) каскада усиления.

Задачей данного изобретения является достижение технического результата, заключающегося в увеличении коэффициента усиления без сужения частотной полосы пропускания, повышении скорости нарастания выходного сигнала при уменьшении потребляемой мощности основного усилительного блока путем введения двух управляемых источников подпитки In1 и In2, выполненных на транзисторах Т17, Т18 и резисторах R5 и R6 соответственно, которые обеспечивают режим пониженной потребляемой мощности транзисторов Т4 и Т12 по постоянному току и согласованного с входным сигналом управления коллекторными токами транзисторов Т4 и Т12 в динамическом режиме с помощью диодов D3 и D11 соответственно, а также введением двух ускоряющих конденсаторов Cy1 и Су2, исключающих усилительный каскад на транзисторах Т4 и Т12 в области высоких частот, что позволяет уменьшить емкость основного корректирующего конденсатора Скор.

Поставленная задача достигается тем (см. фиг.2), что в основной усилительный блок двухтактного операционного усилителя, содержащий первую входную дифференциальную пару на транзисторах Т5 и Т6 первого типа проводимости, базы которых подключены к входным клеммам (+) и (-), а их эмиттеры соединены между собой, и с одним концом источника стабильного тока ИСТ-1, второй конец которого подключен к источнику отрицательного напряжения En -, отражатель тока ОТ-1 на транзисторе Т2 и диоде D1 и отражатель тока ОТ-2 на транзисторе Т4 и диоде D3, при этом анод диода D1 и эмиттер транзистора Т2 через резисторы R1 и R2 соответственно соединены с шиной источника положительного напряжения Еn +, а база транзистора Т2 соединена с катодом диода D1 и с анодом диода D3, коллектор транзистора Т2 соединен с эмиттером транзистора Т4 и с коллектором транзистора Т6, а коллектор транзистора Т4 соединен со входом буферного каскада и с коллектором транзистора Т12, вторую входную дифференциальную пару на транзисторах Т7 и Т8 второго типа проводимости, базы которых соединены соответственно с базами транзисторов Т5 и Т6, а их эмиттеры соединены между собой и с одним концом источника стабильного тока ИСТ-2, второй конец которого подключен к источнику положительного напряжения Еn +, отражатель тока ОТ-3 на транзисторе Т10 и диоде D9 и отражатель тока ОТ-4 на транзисторе Т12 и диоде D11, при этом катод диода D9 и эмиттер транзистора Т10 через резисторы R3 и R4 соответственно соединены с шиной источника отрицательного питания Еn -, а база транзистора Т10 соединена с анодом диода D9 и с катодом диода D11, а коллектор транзистора Т10 соединен с эмиттером транзистора Т12 и с коллектором транзистора Т8, введены два управляемых источника тока подпитки In1, и In2, первый источник подпитки In1 образован транзистором Т17 и резистором R5, причем база транзистора Т17 соединена с катодом диода D1, а эмиттер транзистора Т17 соединен через резистор R5 с источником положительного напряжения Еn +, коллектор транзистора Т17 соединен с эмиттером транзистора Т4 и с одним концом ускоряющего конденсатора Cy1, второй конец которого соединен с коллектором транзистора Т4, база которого подключена к коллектору транзистора Т5 и к катоду диода D3, второй источник подпитки In2 образован транзисторами Т18 и резистором R6, причем база транзистора Т18 соединена с анодом диода D9, а эмиттер транзистора Т18 соединен через резистор R6 с источником отрицательного напряжения En -, коллектор транзистора Т18 соединен с эмиттером транзистора Т12 и с одним концом ускоряющего конденсатора Су2, второй конец которого соединен с коллектором транзистора Т12, база которого подключена к коллектору транзистора Т7 и к аноду диода D11.

Таким образом, отличительными признаками предлагаемого изобретения являются введение управляемых источников тока подпитки In1 и In2 на транзисторах Т17 и Т18 и резисторах R5 и R6 соответственно, двух ускоряющих конденсаторов Су1 и Су2 и новых связей, а именно соединение базы транзистора Т4 с катодом диода D3 и коллектором транзистора Т5 и соединение базы транзистора Т12 с анодом диода D11 и коллектором транзистора Т7, что дает возможность в 4-5 раз увеличить коэффициент усиления по напряжению, уменьшить на 30% потребляемую мощность основного усилительного блока при сохранении полосы пропускания и повысить скорость нарастания выходного сигнала.

Эффект повышения коэффициента усиления достигается тем, что транзистор Т4(Т12) работает в активном режиме с пониженной потребляемой мощностью, определяемой током подпитки In1(In2). Ток подпитки In1(In2) выбирается меньше, чем ток источника постоянного тока ИСТ1 (ИСТ2), поэтому в статическом режиме крутизна транзистора Т4(Т12) в 4-5 раз меньше крутизны входного транзистора Т5(Т7).

В динамическом режиме при подаче на вход транзистора Т5 положительной полуволны синусоидального сигнала транзистор Т4 имеет такую же крутизну, что и транзистор Т5 и диод D3, а поскольку транзистор Т2 с диодом D1 и транзистор Т4 с диодом D3 образуют соответственно два отражателя тока, то приращение коллекторного тока ΔIk1 транзистора Т5, вызванного действием входного синусоидального сигнала ΔUвх. полностью передается транзистором Т4 на вход буферного каскада. Коэффициент усиления по напряжению будет определяться следующим выражением:

КU=КUпрототип•n,

где n=S5/S4≈1/2•Iист/In1>>(4-5);

S5 и S4 - крутизны транзисторов Т5 и Т4 в статическом режиме.

Таким образом, проведенные патентные исследования подтвердили новизну изобретения, а также показали, что в литературе отсутствуют данные, указывающие влияние отличительных признаков на достижение указанного технического результата.

Устройство работает следующим образом. В статистическом режиме (входной сигнал ΔUвх = 0) ток источника стабильного тока ИСТ1 делится поровну между эмиттерами транзисторов Т5 и Т6. Коллекторный ток транзистора Т5 протекает через диоды D3 и D1 и резистор R1 к источнику положительного напряжения Еn +, а коллекторный ток транзистора Т6 полностью протекает к коллектору транзистора Т2 и резистору R2 к источнику отрицательного напряжения Еn -. Коллекторный ток транзистора Т2 и ток диода D1 одинаковы, так как они образуют верхний отражатель тока ОТ-1. Коллекторный ток транзистора Т4 определяется только током подпитки In1, величина которого выбирается в 5-10 раз меньше, чем ток источника стабильного тока ИСТ1. Вместе с тем величина напряжения эмиттер-база транзистора Т4 по постоянному току такая же, как и у диода D3, поэтому транзистор Т4 по постоянному току работает в активном режиме с пониженной потребляемой мощностью.

Крутизна транзистора Т4 почти на порядок меньше, чем крутизна входного транзистора Т5. Если бы ток подпитки In1 транзистора Т4 равнялся коллекторному току транзистора Т5, а его база была бы подключена к источнику постоянного напряжения, как это имеет место в прототипе, то усиление каскада определялось бы следующим соотношением:

где Rвх,Б - входное сопротивление буферного каскада;

rk4 и rk12- сопротивления коллекторных переходов транзисторов Т4 и Т12;

rэ5 - дифференциальное сопротивление эмиттерного перехода Т5;

S5=1/rэ - крутизна транзистора Т5.

Поскольку крутизна транзистора Т4 меньше, чем крутизна транзистора Т5, то усиление будет определяться соотношением:

КU≈-(S5•Rвх,Б)•1/2(S5/S4)................,

где S4 - крутизна транзистора Т4;

S5/S4≈8÷10.

В динамическом режиме (например, при подаче на вход транзистора Т5 положительной полуволны синусоидального сигнала) приращение коллекторного тока ΔIк5 транзистора Т5 через отражатель тока ОТ-1 (диод D 1 и транзистор Т2) полностью передается в транзистор Т2, а поскольку диод D3 и транзистор Т4 по переменному току образуют отражатель тока ОТ-2, то приращение коллекторного тока ΔIk2 = ΔIk5 полностью поступает в эмиттер транзистора Т4 и выделяется в виде напряжения на входном сопротивлении буфера. Вместе с тем на эмиттере транзистора Т4 выделяется напряжение, которое больше входного в 1/2(S5/S4) раз, в тоже время транзистор Т4 совместно с диодом Д3 образует "каскад", работающий в режиме токового управления, поэтому сужения полосы пропускания частот не происходит. Более того, введение ускоряющего конденсатора Cy1 позволяет на высоких частотах исключить часть усиления, получаемого с помощью транзистора Т4. Это дает возможность уменьшить в 1,5 раза частотно-корректирующую емкость Скор и тем самым сохранить частотную полосу пропускания для малого сигнала и повысить скорость нарастания выходного сигнала для большого сигнала. При подаче на базы транзисторов Т5 и Т7 отрицательной полуволны работает нижняя часть двухтактного усилителя. Таким образом, верхняя часть усилителя усиливает положительную полуволну, а нижняя - отрицательную.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСТОЧНИК ОБРАЗЦОВЫХ НАПРЯЖЕНИЙ | 1993 |

|

RU2076351C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ ЭСЛ-КМОП | 1994 |

|

RU2097914C1 |

| СИММЕТРИЧНЫЙ МУЛЬТИПЛЕКСОР НА КОМПЛЕМЕНТАРНЫХ МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК (КМОП) ТРАНЗИСТОРАХ | 2018 |

|

RU2689820C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ЗАПИСИ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1994 |

|

RU2097843C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 1995 |

|

RU2099814C1 |

| Преобразователь напряжения в длительность импульсов | 1990 |

|

SU1785071A1 |

| РЕГУЛИРУЕМЫЙ ПРЕЦИЗИОННЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ДВУПОЛЯРНЫМ ВЫХОДОМ | 1991 |

|

RU2037871C1 |

| БИКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1996 |

|

RU2106719C1 |

| СТРУКТУРА - КРЕМНИЙ НА ИЗОЛЯТОРЕ ДЛЯ СБИС (ВАРИАНТЫ) | 1998 |

|

RU2149482C1 |

| Устройство активного контроля | 1975 |

|

SU588106A1 |

Изобретение относится к электронным устройствам, в частности к усилителям, и может применяться для построения интегральных схем. Двухтактный операционный усилитель с повышенным коэффициентом усиления содержит основной блок усиления, выполненный на двух параллельно включенных входных дифференциальных парах, образованных транзисторами первого и второго типа проводимости соответственно. Нагрузкой каждой дифференциальной пары является двухъярусный отражатель тока соответствующего типа проводимости, причем транзисторы нижнего яруса каждого отражателя тока позволяют обеспечить дополнительное усиление за счет различной крутизны усилительных транзисторов Т4 и Т12 в статическом и динамическом режимах соответственно. Введены два управляемых источника подпитки In1 и In2 для задания режима пониженной потребляемой мощности транзисторов Т4 и Т12 в статическом режиме и согласованного с входным сигналом управления их динамическими характеристиками по переменному току с помощью диодов D3 и D11, а также двух ускоряющих конденсаторов Cy1 и Су2, исключающих усилительный каскад на транзисторах Т4 и Т 12 в области высоких частот, что позволяет уменьшить емкость основного корректирующего конденсатора Скор. Технический результат: увеличение коэффициента усиления без сужения частотной полосы пропускания, повышение скорости нарастания выходного сигнала при уменьшении потребляемой мощности основного усилительного блока. 2 ил.

Двухтактный операционный усилитель, содержащий первую входную дифференциальную пару на транзисторах Т5 и Т6 первого типа проводимости, базы которых подключены к входным клеммам (+) и (-), а их эмиттеры соединены между собой и с одним концом источника стабильного тока ИСТ-1, второй конец которого подключен к источнику отрицательного напряжения Еn -, отражатель тока ОТ-1 на транзисторе Т2 и диоде D1 и отражатель тока ОТ-2 на транзисторе Т4 и диоде D3, при этом анод диода D1 и эмиттер транзистора Т2 через резисторы R1 и R2 соответственно соединены с шиной источника положительного напряжения Еn +, а база транзистора Т2 соединена с катодом диода D1 и с анодом диода D3, коллектор транзистора Т2 соединен с эмиттером транзистора Т4 и с коллектором транзистора Т6, а коллектор транзистора Т4 соединен со входом буферного каскада и с коллектором транзистора Т12, вторую входную дифференциальную пару на транзисторах Т7 и Т8 второго типа проводимости, базы которых соединены соответственно с базами транзисторов Т5 и Т6, а их эмиттеры соединены между собой и с одним концом источника стабильного тока ИСТ-2, второй конец которого подключен к источнику положительного напряжения Еn +, отражатель тока ОТ-3 на транзисторе Т10 и диоде D9 и отражатель тока ОТ-4 на транзисторе Т12 и диоде D11, при этом катод диода D9 и эмиттер транзистора Т10 через резисторы R3 и R4 соответственно соединены с шиной источника отрицательного питания Еn -, а база транзистора Т10 соединена с анодом диода D9 и с катодом диода D11, а коллектор транзистора Т10 соединен с эмиттером транзистора Т12 и с коллектором транзистора Т8, отличающийся тем, что в него введены два управляемых источника тока подпитки In1 и In2, первый источник тока подпитки In1 образован транзистором Т17 и резистором R5, причем база транзистора Т17 соединена с катодом диода D1, а эмиттер транзистора Т17 соединен через резистор R5 с источником положительного напряжения Еn +, коллектор транзистора Т17 соединен с эмиттером транзистора Т4 и с одним концом ускоряющего конденсатора Cy1, второй конец которого соединен с коллектором транзистора Т4, база которого подключена к коллектору транзистора Т5 и к катоду диода D3, второй источник подпитки In2 образован транзисторами Т18 и резистором R6, причем база транзистора Т18 соединена с анодом диода D9, а эмиттер транзистора Т18 соединен через резистор R6 с источником отрицательного напряжения En -, коллектор транзистора Т18 соединен с эмиттером транзистора Т12 и с одним концом ускоряющего конденсатора Су2, второй конец которого соединен с коллектором транзистора Т12, база которого подключена к коллектору транзистора Т7 и к аноду диода D11.

| Dr | |||

| Yohn Lidgey, Analogue Action, 1 GHz gain-bandwidth operational amplifiers | |||

| Electronics & wireless world, Sep, 1989, T.9, OY EL2038 Elarttec | |||

| Операционный усилитель | 1983 |

|

SU1160530A1 |

| Операционный усилитель | 1986 |

|

SU1396242A1 |

| ПОЛОННИКОВ Д.Е | |||

| Операционные усилители: Принципы построения, теория, схемотехника | |||

| - М.: Энергоатомиздат, 1983, с | |||

| Приспособление, увеличивающее число оборотов движущихся колес паровоза | 1919 |

|

SU146A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

2002-11-20—Публикация

2000-06-08—Подача