Изобретение относится к электронике и предназначено для использования в цифровых вычислительных устройствах.

Известны устройства, в которых сложение чисел выполняется поразрядно с помощью последовательной цепи сумматоров, см., например, Киносита К., Асада К. , Карацу О. Логическое проектирование СБИС: Пер. с япон. - М.: Мир, 1988, с. 67, рис.2.26. С увеличением числа разрядов суммируемых чисел в таких схемах значительно удлиняется цепочка распространения сигналов от входов младших разрядов слагаемых до выхода старшего разряда суммы и поэтому растет наихудшее значение временной задержки, что является недостатком.

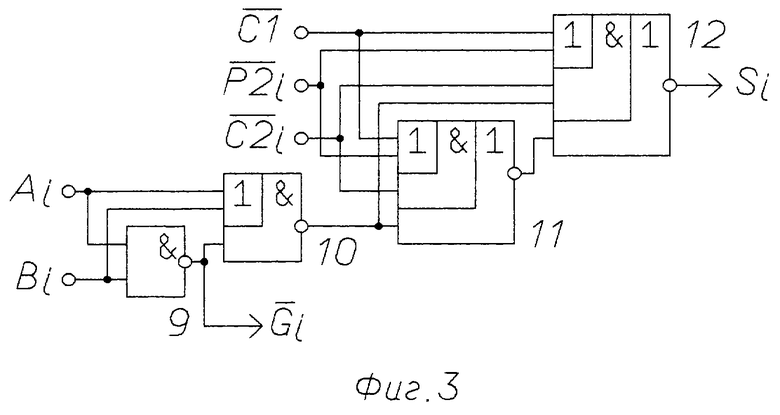

Уменьшить время выполнения суммирования позволяет использование в устройствах сложения пирамидальной схемы ускоренного переноса (см. Киносита К., Асада К., Карацу О. Логическое проектирование СБИС: Пер. с япон., - М.: Мир, 1988, с. 69, рис.2.27 и 2.28). В этой схеме сигнал переноса в каждый разряд формируется непосредственно из сигналов предыдущих разрядов суммируемых чисел по древовидному алгоритму, позволяющему укоротить цепочки переноса. Если разрядность устройства сложения с ускоренным переносом такова, что в цепи формирования переносов нечетное число каскадов инвертирующих элементов, их сигналы представлены с инверсией. В качестве сумматоров в таком устройстве используется последовательное подключение схем ИСКЛЮЧАЮЩЕЕ 2ИЛИ и РАВНОЗНАЧНОСТЬ 2, в котором первая ступень выполняет сложение пары соответствующих разрядов суммируемых чисел, получаемых непосредственно со входов устройства, а вторая прибавляет к результату перенос, сигнал которого поступает с задержкой с выхода схемы переноса.

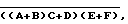

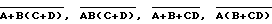

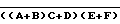

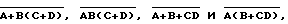

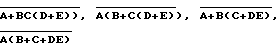

Известное решение схемы ИСКЛЮЧАЮЩЕЕ 2ИЛИ содержит элемент 2ИЛИ-НЕ и элемент, выполняющий функцию вида  здесь и далее переменные А, В и С соответствуют сигналам, поступающим на первый, второй и третий входы элементов, (см. Доп. а.с. СССР 1429315, МКП Н 03 К 19/094, опубликованное 7 октября 1988 г., бюлл. 37), а известное решение схемы РАВНОЗНАЧНОСТЬ 2 содержит элемент 2ИЛИ-НЕ и элемент, выполняющий функцию вида

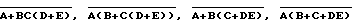

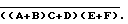

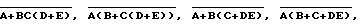

здесь и далее переменные А, В и С соответствуют сигналам, поступающим на первый, второй и третий входы элементов, (см. Доп. а.с. СССР 1429315, МКП Н 03 К 19/094, опубликованное 7 октября 1988 г., бюлл. 37), а известное решение схемы РАВНОЗНАЧНОСТЬ 2 содержит элемент 2ИЛИ-НЕ и элемент, выполняющий функцию вида  (см. Патент Японии 4-38009, МКП G 06 F 7/50, опубликованный 23 июня 1992 г.).

(см. Патент Японии 4-38009, МКП G 06 F 7/50, опубликованный 23 июня 1992 г.).

Перестановка в последовательности схем ИСКЛЮЧАЮЩЕЕ 2ИЛИ и РАВНОЗНАЧНОСТЬ 2 позволяет использовать в качестве входного элемента подходящий формирователь сигнала возникновения переноса или распространения переноса, выполняющий функцию 2И-НЕ или 2ИЛИ-НЕ соответственно.

Данное устройство по технической сущности наиболее близко к изобретению.

Наиболее близкий аналог содержит сумматоры-формирователи сигналов возникновения переноса и сумматоры-формирователи сигналов распространения переноса.

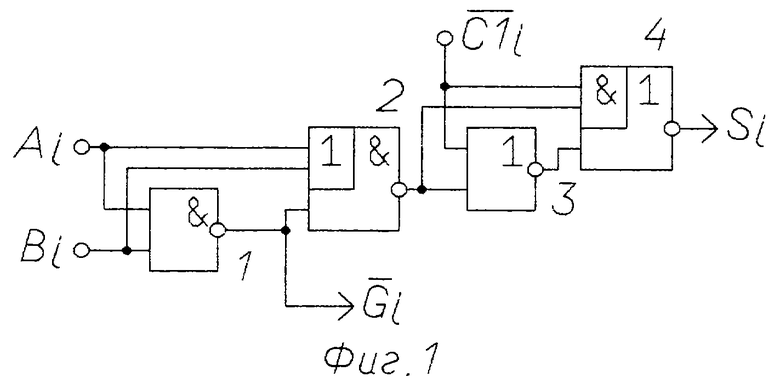

Каждый сумматор-формирователь сигнала возникновения переноса (Фиг.1) состоит из первого элемента 1 2И-НЕ, второго элемента 2, выполняющего функцию вида  третьего элемента 3 2ИЛИ-НЕ и четвертого элемента 4 -

третьего элемента 3 2ИЛИ-НЕ и четвертого элемента 4 -  Входы первого элемента 1 соответственно соединены с первым и вторым входами второго элемента 2 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 1 является выходом

Входы первого элемента 1 соответственно соединены с первым и вторым входами второго элемента 2 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 1 является выходом  инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 2. Выход третьего элемента 3 соединен с первыми входом четвертого элемента 4, второй вход которого вместе с первым входом третьего элемента 3 подключен к выходу второго элемента 2. Второй вход третьего элемента 3 и третий вход четвертого элемента 4 соединены и подключены к соответствующему входу

инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 2. Выход третьего элемента 3 соединен с первыми входом четвертого элемента 4, второй вход которого вместе с первым входом третьего элемента 3 подключен к выходу второго элемента 2. Второй вход третьего элемента 3 и третий вход четвертого элемента 4 соединены и подключены к соответствующему входу  инверсии сигнала переноса. Выход четвертого элемента 4 является выходом Si соответствующего разряда суммы.

инверсии сигнала переноса. Выход четвертого элемента 4 является выходом Si соответствующего разряда суммы.

Каждый сумматор-формирователь сигнала распространения переноса (Фиг.2) состоит из первого элемента 5 2ИЛИ-НЕ, второго элемента 6, выполняющего функцию вида  третьего элемента 7 2И-НЕ и четвертого элемента 8 -

третьего элемента 7 2И-НЕ и четвертого элемента 8 -  Входы первого элемента 5 соответственно соединены с первым и вторым входами второго элемента 6 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 5 является выходом

Входы первого элемента 5 соответственно соединены с первым и вторым входами второго элемента 6 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 5 является выходом  инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 6. Выход третьего элемента 7 соединен с первым входом четвертого элемента 8, второй вход которого вместе с первым входом третьего элемента 7 подключен к выходу второго элемента 6. Второй вход третьего элемента 7 и третий вход четвертого элемента 8 соединены и подключены к соответствующему входу

инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 6. Выход третьего элемента 7 соединен с первым входом четвертого элемента 8, второй вход которого вместе с первым входом третьего элемента 7 подключен к выходу второго элемента 6. Второй вход третьего элемента 7 и третий вход четвертого элемента 8 соединены и подключены к соответствующему входу  инверсии сигнала переноса. Выход четвертого элемента 8 является выходом Si соответствующего разряда суммы.

инверсии сигнала переноса. Выход четвертого элемента 8 является выходом Si соответствующего разряда суммы.

Устройство-аналог работает следующим образом.

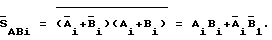

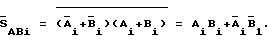

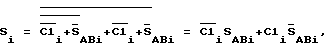

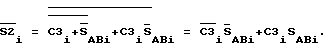

В каждом сумматоре-формирователе сигнала возникновения переноса первый элемент 1 2И-НЕ выполняет дизъюнкцию инверсий суммируемых разрядов Аi и Вi, логическое умножение которой на дизъюнкцию повторений разрядов Аi и Вi с последующей инверсией, осуществляемых вторым элементом 2  позволяет получить инверсию суммы разрядов Аi и Вi согласно формуле

позволяет получить инверсию суммы разрядов Аi и Вi согласно формуле

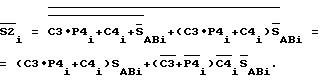

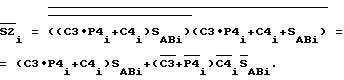

Сложение суммы SABi и переноса С1i, сигналы которых поступают с инверсией, выполняют третий и четвертый элементы 3 и 4 по формуле

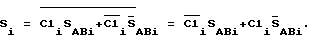

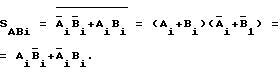

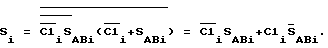

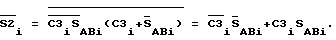

В каждом сумматоре-формирователе сигнала распространения переноса первый элемент 5 2ИЛИ-НЕ производит логическое умножение инверсий суммируемых разрядов Аi и Вi. Инверсия дизъюнкции его выходного сигнала с конъюнкцией повторений разрядов Аi и Вi, выполняемая вторым элементом 6  является суммой разрядов Аi и Вi, как показывает формула

является суммой разрядов Аi и Вi, как показывает формула

Сумма SABi складывается с переносом С1i, поступающим в инверсном представлении, с помощью третьего и четвертого элементов 7 и 8 в соответствии со следующей формулой:

Недостаток устройства-аналога заключается в разнице задержек сигналов, поступающих на входы второй ступени сложения, образуемой элементами 3, 4 и 7, 8. Это вызвано большей сложностью схем переноса, особенно в старшие разряды, по сравнению со схемой первой ступени сложения на элементах 1, 2 и 5, 6.

Задачей настоящего изобретения является достижение технического результата, заключающегося в получении возможности выравнивания быстродействия первых ступеней суммирования и цепей формирования переносов, а также замены сложной схемы переноса на несколько более простых с меньшими задержками или подключения дополнительных схем переноса с целью повышения разрядности устройства сложения без увеличения количества каскадов задержки.

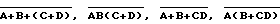

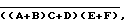

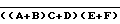

Поставленная задача решается тем, что в устройстве сложения с ускоренным переносом, содержащем с первой по четвертую группы сумматоров, имеющих две разновидности: сумматор-формирователь сигнала возникновения переноса и сумматор-формирователь сигнала распространения переноса, каждый сумматор-формирователь сигнала возникновения переноса состоит из первого элемента 2И-НЕ, второго элемента, выполняющего функцию вида  третьего элемента

третьего элемента  и четвертого элемента

и четвертого элемента  здесь и далее переменные А, В, С, D, Е, F обозначают сигналы, соответствующие с первого по шестой входам элементов, входы первого элемента соответственно соединены с первым и вторым входами второго элемента и подключены к соответствующим входам разрядов суммируемых чисел, выход первого элемента является выходом инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента, выход третьего элемента соединен с первым входом четвертого элемента, второй вход которого вместе с первым входом третьего элемента подключен к выходу второго элемента, каждый сумматор-формирователь сигнала распространения переноса состоит из первого элемента 2ИЛИ-НЕ, второго элемента, выполняющего функцию вида

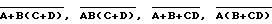

здесь и далее переменные А, В, С, D, Е, F обозначают сигналы, соответствующие с первого по шестой входам элементов, входы первого элемента соответственно соединены с первым и вторым входами второго элемента и подключены к соответствующим входам разрядов суммируемых чисел, выход первого элемента является выходом инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента, выход третьего элемента соединен с первым входом четвертого элемента, второй вход которого вместе с первым входом третьего элемента подключен к выходу второго элемента, каждый сумматор-формирователь сигнала распространения переноса состоит из первого элемента 2ИЛИ-НЕ, второго элемента, выполняющего функцию вида  третьего элемента

третьего элемента  и четвертого элемента

и четвертого элемента  входы первого элемента соответственно соединены с первым и вторым входами второго элемента и подключены к соответствующим входам разрядов суммируемых чисел, выход первого элемента является выходом инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента, выход третьего элемента соединен с первым входом четвертого элемента, второй вход которого вместе с первым входом третьего элемента подключен к выходу второго элемента, в каждом сумматоре первой группы второй вход третьего элемента и третий вход четвертого элемента соединены и подключены к соответствующему входу инверсии сигнала переноса из первой группы разрядов суммируемых чисел, выходы четвертых элементов сумматоров первой и второй групп являются выходами соответствующих разрядов суммы, в каждом сумматоре-формирователе сигнала возникновения переноса второй группы функция третьего элемента расширена до вида

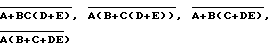

входы первого элемента соответственно соединены с первым и вторым входами второго элемента и подключены к соответствующим входам разрядов суммируемых чисел, выход первого элемента является выходом инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента, выход третьего элемента соединен с первым входом четвертого элемента, второй вход которого вместе с первым входом третьего элемента подключен к выходу второго элемента, в каждом сумматоре первой группы второй вход третьего элемента и третий вход четвертого элемента соединены и подключены к соответствующему входу инверсии сигнала переноса из первой группы разрядов суммируемых чисел, выходы четвертых элементов сумматоров первой и второй групп являются выходами соответствующих разрядов суммы, в каждом сумматоре-формирователе сигнала возникновения переноса второй группы функция третьего элемента расширена до вида  а функция четвертого элемента расширена до вида

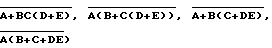

а функция четвертого элемента расширена до вида  в каждом сумматоре-формирователе сигнала распространения переноса второй группы функция третьего элемента расширена до вида

в каждом сумматоре-формирователе сигнала распространения переноса второй группы функция третьего элемента расширена до вида  а функция четвертого элемента расширена до вида

а функция четвертого элемента расширена до вида

В каждом сумматоре второй группы второй вход третьего элемента и третий вход четвертого элемента соединены и подключены к соответствующему входу инверсии сигнала переноса из второй группы разрядов суммируемых чисел, третий вход третьего элемента вместе с четвертым входом четвертого элемента подключен к соответствующему входу инверсии сигнала распространения переноса второй группой разрядов суммируемых чисел, четвертый вход третьего элемента и пятый вход четвертого элемента соединены и подключены ко входу инверсии старшего сигнала переноса из первой группы разрядов суммируемых чисел.

В каждом сумматоре-формирователе сигнала возникновения переноса третьей группы добавлены пятый элемент-инвертор и шестой элемент 2И-НЕ, первый вход которого соединен с первым входом третьего элемента, второй вход которого и третий вход четвертого элемента соединены и подключены к соответствующему входу сигнала переноса из третьей группы разрядов суммируемых чисел, вход пятого элемента вместе со вторым входом шестого элемента подключен к соответствующему входу сигнала распространения переноса третьей группой разрядов суммируемых чисел.

В каждом сумматоре-формирователе сигнала распространения переноса третьей группы добавлены пятый и шестой элементы 2И-НЕ, первый вход пятого элемента соединен с первым входом третьего элемента, второй вход которого и третий вход четвертого элемента соединены и подключены к соответствующему входу сигнала переноса из третьей группы разрядов суммируемых чисел, второй вход пятого элемента вместе с первым входом шестого элемента подключен к соответствующему входу сигнала распространения переноса третьей группой разрядов суммируемых чисел, второй вход шестого элемента подключен к выходу пятого элемента.

В каждом сумматоре-формирователе сигнала возникновения переноса четвертой группы функция третьего элемента расширена до вида  а функция четвертого элемента расширена до вида

а функция четвертого элемента расширена до вида  добавлены пятый элемент 2И-НЕ и шестой элемент 3И-НЕ, первый вход которого подключен к первому входу третьего элемента, второй вход которого и третий вход четвертого элемента соединены и подключены к соответствующему входу сигнала переноса из четвертой группы разрядов суммируемых чисел, третий вход третьего элемента вместе с четвертым входом четвертого элемента, первым входом пятого элемента и вторым входом шестого элемента подключен к соответствующему входу сигнала распространения переноса четвертой группой разрядов суммируемых чисел, четвертый вход третьего элемента и пятый вход четвертого элемента соединены и подключены ко входу старшего сигнала переноса из третьей группы разрядов суммируемых чисел, второй вход пятого элемента и третий вход шестого элемента соединены со входом старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел.

добавлены пятый элемент 2И-НЕ и шестой элемент 3И-НЕ, первый вход которого подключен к первому входу третьего элемента, второй вход которого и третий вход четвертого элемента соединены и подключены к соответствующему входу сигнала переноса из четвертой группы разрядов суммируемых чисел, третий вход третьего элемента вместе с четвертым входом четвертого элемента, первым входом пятого элемента и вторым входом шестого элемента подключен к соответствующему входу сигнала распространения переноса четвертой группой разрядов суммируемых чисел, четвертый вход третьего элемента и пятый вход четвертого элемента соединены и подключены ко входу старшего сигнала переноса из третьей группы разрядов суммируемых чисел, второй вход пятого элемента и третий вход шестого элемента соединены со входом старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел.

В каждом сумматоре-формирователе сигнала распространения переноса четвертой группы функция третьего элемента расширена до вида  а функция четвертого элемента расширена до вида

а функция четвертого элемента расширена до вида  добавлены пятый и шестой элементы 3И-НЕ, первый вход пятого элемента подключен к первому входу третьего элемента, второй вход которого и третий вход четвертого элемента соединены и подключены к соответствующему входу сигнала переноса из четвертой группы разрядов суммируемых чисел, третий вход третьего элемента вместе с четвертым входом четвертого элемента, вторым входом пятого элемента и первым входом шестого элемента подключен к соответствующему входу сигнала распространения переноса четвертой группой разрядов суммируемых чисел, четвертый вход третьего элемента и пятый вход четвертого элемента соединены и подключены ко входу старшего сигнала переноса из третьей группы разрядов суммируемых чисел, третий вход пятого элемента и второй вход шестого элемента соединены со входом старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел, а третий вход шестого элемента подключен к выходу пятого элемента.

добавлены пятый и шестой элементы 3И-НЕ, первый вход пятого элемента подключен к первому входу третьего элемента, второй вход которого и третий вход четвертого элемента соединены и подключены к соответствующему входу сигнала переноса из четвертой группы разрядов суммируемых чисел, третий вход третьего элемента вместе с четвертым входом четвертого элемента, вторым входом пятого элемента и первым входом шестого элемента подключен к соответствующему входу сигнала распространения переноса четвертой группой разрядов суммируемых чисел, четвертый вход третьего элемента и пятый вход четвертого элемента соединены и подключены ко входу старшего сигнала переноса из третьей группы разрядов суммируемых чисел, третий вход пятого элемента и второй вход шестого элемента соединены со входом старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел, а третий вход шестого элемента подключен к выходу пятого элемента.

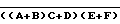

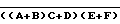

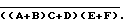

В каждом сумматоре третьей и четвертой групп добавлены седьмой элемент, выполняющий функцию вида  и восьмой элемент

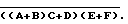

и восьмой элемент  у которых первые, вторые и третьи входы соответственно соединены и подключены ко входам инверсий старших сигналов переноса из разрядов первой группы суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из разрядов второй группы суммируемых чисел, четвертый вход седьмого элемента соединен с выходом пятого элемента, четвертый, пятый и шестой входы восьмого элемента подключены к выходам шестого, седьмого и четвертого элементов соответственно, выход восьмого элемента является выходом соответствующего разряда суммы.

у которых первые, вторые и третьи входы соответственно соединены и подключены ко входам инверсий старших сигналов переноса из разрядов первой группы суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из разрядов второй группы суммируемых чисел, четвертый вход седьмого элемента соединен с выходом пятого элемента, четвертый, пятый и шестой входы восьмого элемента подключены к выходам шестого, седьмого и четвертого элементов соответственно, выход восьмого элемента является выходом соответствующего разряда суммы.

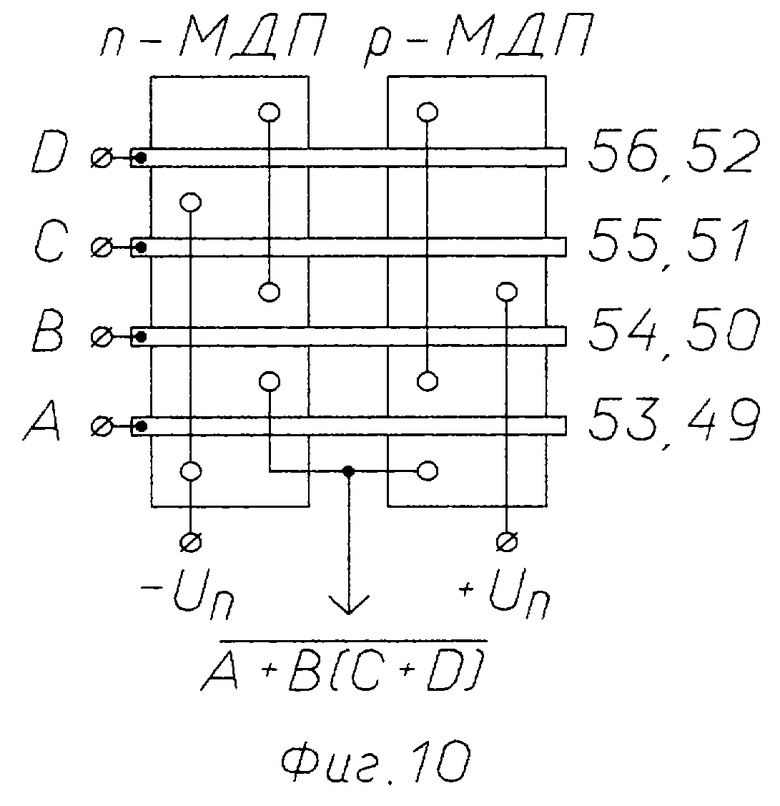

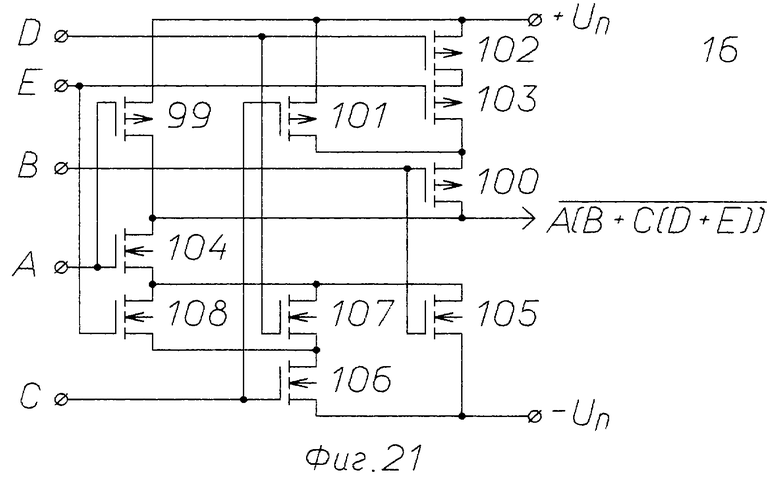

Каждый элемент устройства сложения с ускоренным переносом выполнен на транзисторах МДП-структуры с индуцированными каналами р- и n-типов проводимости, третьи элементы  сумматоров второй и четвертой групп содержат по четыре МДП-транзистора р-типа и по четыре n-МДП-транзистора, затворы которых по порядку подключены к первым-четвертым входам (А, В, С, D соответственно), седьмой элемент

сумматоров второй и четвертой групп содержат по четыре МДП-транзистора р-типа и по четыре n-МДП-транзистора, затворы которых по порядку подключены к первым-четвертым входам (А, В, С, D соответственно), седьмой элемент  сумматоров третьей и четвертой групп содержит по четыре МДП-транзистора р- и n-типа, затворы которых в обратном порядке подключены к первому-четвертому входам.

сумматоров третьей и четвертой групп содержит по четыре МДП-транзистора р- и n-типа, затворы которых в обратном порядке подключены к первому-четвертому входам.

В третьем элементе  каждого сумматора-формирователя сигнала возникновения переноса второй группы и в седьмом элементе

каждого сумматора-формирователя сигнала возникновения переноса второй группы и в седьмом элементе  каждого сумматора третьей и четвертой групп стоки первого р-МДП-, первого и второго n-МДП-транзисторов соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоками второго и четвертого р-МДП-транзисторов, исток четвертого р-МДП-транзистора подключен к стоку третьего МДП-транзистора р-типа, исток которого вместе с истоком второго р-МДП-транзистора подключен к шине положительного напряжения питания, исток второго МДП-транзистора n-типа соединен со стоками третьего и четвертого n-МДП-транзисторов, истоки которых вместе с истоком первого n-МДП-транзистора подключены к шине отрицательного напряжения питания.

каждого сумматора третьей и четвертой групп стоки первого р-МДП-, первого и второго n-МДП-транзисторов соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоками второго и четвертого р-МДП-транзисторов, исток четвертого р-МДП-транзистора подключен к стоку третьего МДП-транзистора р-типа, исток которого вместе с истоком второго р-МДП-транзистора подключен к шине положительного напряжения питания, исток второго МДП-транзистора n-типа соединен со стоками третьего и четвертого n-МДП-транзисторов, истоки которых вместе с истоком первого n-МДП-транзистора подключены к шине отрицательного напряжения питания.

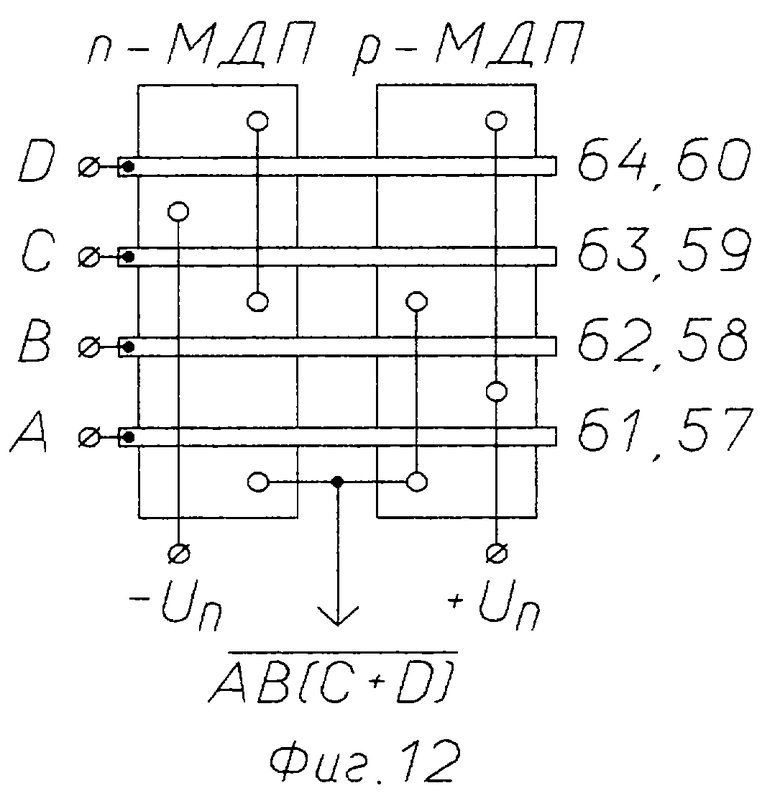

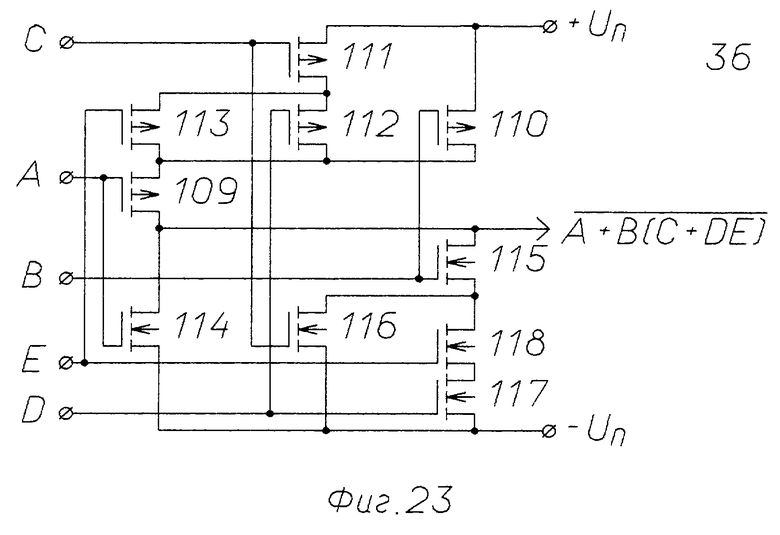

В третьем элементе  каждого сумматора-формирователя сигнала распространения переноса второй группы стоки с первого по третий МДП-транзисторов р-типа и сток первого МДП-транзистора n-типа соединены и являются выходом элемента, исток третьего р-МДП-транзистора соединен со стоком четвертого МДП-транзистора р-типа, исток которого вместе с истоками первого и второго р-МДП-транзисторов подключен к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоком второго n-МДП-транзистора, исток которого соединен со стоками третьего и четвертого МДП-транзисторов n-типа, истоки которых подключены к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса второй группы стоки с первого по третий МДП-транзисторов р-типа и сток первого МДП-транзистора n-типа соединены и являются выходом элемента, исток третьего р-МДП-транзистора соединен со стоком четвертого МДП-транзистора р-типа, исток которого вместе с истоками первого и второго р-МДП-транзисторов подключен к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоком второго n-МДП-транзистора, исток которого соединен со стоками третьего и четвертого МДП-транзисторов n-типа, истоки которых подключены к шине отрицательного напряжения питания.

В третьем элементе  каждого сумматора-формирователя сигнала возникновения переноса четвертой группы сток первого МДП-транзистора р-типа и стоки с первого по третий МДП-транзисторов n-типа соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоком второго р-МДП-транзистора, исток которого соединен со стоками третьего и четвертого МДП-транзисторов р-типа, истоки которых подключены к шине положительного напряжения питания, исток третьего n-МДП-транзистора соединен со стоком четвертого МДП-транзистора n-типа, исток которого вместе с истоками первого и второго n-МДП-транзисторов подключен к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала возникновения переноса четвертой группы сток первого МДП-транзистора р-типа и стоки с первого по третий МДП-транзисторов n-типа соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоком второго р-МДП-транзистора, исток которого соединен со стоками третьего и четвертого МДП-транзисторов р-типа, истоки которых подключены к шине положительного напряжения питания, исток третьего n-МДП-транзистора соединен со стоком четвертого МДП-транзистора n-типа, исток которого вместе с истоками первого и второго n-МДП-транзисторов подключен к шине отрицательного напряжения питания.

В третьем элементе  каждого сумматора-формирователя сигнала распространения переноса четвертой группы стоки первого и второго р-МДП-, первого n-МДП-транзисторов соединены и являются выходом элемента, исток второго МДП-транзистора р-типа соединен со стоками третьего и четвертого р-МДП-транзисторов, истоки которых вместе с истоком первого р-МДП-транзистора подключены к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоками второго и четвертого n-МДП-транзисторов, исток четвертого n-МДП-транзистора подключен к стоку третьего МДП-транзистора n-типа, исток которого вместе с истоком второго n-МДП-транзистора подключен к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса четвертой группы стоки первого и второго р-МДП-, первого n-МДП-транзисторов соединены и являются выходом элемента, исток второго МДП-транзистора р-типа соединен со стоками третьего и четвертого р-МДП-транзисторов, истоки которых вместе с истоком первого р-МДП-транзистора подключены к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоками второго и четвертого n-МДП-транзисторов, исток четвертого n-МДП-транзистора подключен к стоку третьего МДП-транзистора n-типа, исток которого вместе с истоком второго n-МДП-транзистора подключен к шине отрицательного напряжения питания.

Четвертые элементы

сумматоров второй и четвертой групп содержат по пять МДП-транзисторов р-типа и по пять n-МДП-транзисторов, затворы которых по порядку подключены к первым-пятым входам (A, B, C, D, E соответственно), в четвертом элементе  каждого сумматора-формирователя сигнала возникновения переноса второй группы стоки первого р-МДП-, первого и второго n-МДП-транзисторов соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоками второго, третьего и четвертого р-МДП-транзисторов, исток четвертого р-МДП-транзистора подключен к стоку пятого МДП-транзистора р-типа, исток которого вместе с истоками второго и третьего р-МДП-транзисторов подключен к шине положительного напряжения питания, исток второго МДП-транзистора n-типа подключен к стоку третьего n-МДП-транзистора, исток которого соединен со стоками четвертого и пятого n-МДП-транзисторов, истоки которых вместе с истоком первого n-МДП-транзистора подключены к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала возникновения переноса второй группы стоки первого р-МДП-, первого и второго n-МДП-транзисторов соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоками второго, третьего и четвертого р-МДП-транзисторов, исток четвертого р-МДП-транзистора подключен к стоку пятого МДП-транзистора р-типа, исток которого вместе с истоками второго и третьего р-МДП-транзисторов подключен к шине положительного напряжения питания, исток второго МДП-транзистора n-типа подключен к стоку третьего n-МДП-транзистора, исток которого соединен со стоками четвертого и пятого n-МДП-транзисторов, истоки которых вместе с истоком первого n-МДП-транзистора подключены к шине отрицательного напряжения питания.

В четвертом элементе  каждого сумматора-формирователя сигнала распространения переноса второй группы стоки первого и второго МДП-транзисторов р-типа и сток первого МДП-транзистора n-типа соединены и являются выходом элемента, исток второго р-МДП-транзистора соединен со стоками третьего и пятого МДП-транзисторов р-типа, исток пятого р-МДП-транзистора соединен со стоком четвертого МДП-транзистора р-типа, исток которого вместе с истоками первого и третьего р-МДП-транзисторов подключен к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоками второго, четвертого и пятого n-МДП-транзисторов, истоки четвертого и пятого МДП-транзисторов n-типа соединены со стоком третьего n-МДП-транзистора, исток которого вместе с истоком второго МДП-транзистора n-типа подключен к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса второй группы стоки первого и второго МДП-транзисторов р-типа и сток первого МДП-транзистора n-типа соединены и являются выходом элемента, исток второго р-МДП-транзистора соединен со стоками третьего и пятого МДП-транзисторов р-типа, исток пятого р-МДП-транзистора соединен со стоком четвертого МДП-транзистора р-типа, исток которого вместе с истоками первого и третьего р-МДП-транзисторов подключен к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоками второго, четвертого и пятого n-МДП-транзисторов, истоки четвертого и пятого МДП-транзисторов n-типа соединены со стоком третьего n-МДП-транзистора, исток которого вместе с истоком второго МДП-транзистора n-типа подключен к шине отрицательного напряжения питания.

В четвертом элементе  каждого сумматора-формирователя сигнала возникновения переноса четвертой группы стоки первого р-МДП-, первого и второго n-МДП-транзисторов соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоками второго, четвертого и пятого р-МДП-транзисторов, истоки четвертого и пятого р-МДП-транзисторов подключены к стоку третьего МДП-транзистора р-типа, исток которого вместе с истоком второго р-МДП-транзистора подключен к шине положительного напряжения питания, исток второго МДП-транзистора n-типа соединен со стоками третьего и пятого n-МДП-транзисторов, исток пятого МДП-транзистора n-типа соединен со стоком четвертого n-МДП-транзистора, исток которого вместе с истоками первого и третьего n-МДП-транзисторов подключен к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала возникновения переноса четвертой группы стоки первого р-МДП-, первого и второго n-МДП-транзисторов соединены и являются выходом элемента, исток первого МДП-транзистора р-типа соединен со стоками второго, четвертого и пятого р-МДП-транзисторов, истоки четвертого и пятого р-МДП-транзисторов подключены к стоку третьего МДП-транзистора р-типа, исток которого вместе с истоком второго р-МДП-транзистора подключен к шине положительного напряжения питания, исток второго МДП-транзистора n-типа соединен со стоками третьего и пятого n-МДП-транзисторов, исток пятого МДП-транзистора n-типа соединен со стоком четвертого n-МДП-транзистора, исток которого вместе с истоками первого и третьего n-МДП-транзисторов подключен к шине отрицательного напряжения питания.

В четвертом элементе  каждого сумматора-формирователя сигнала распространения переноса четвертой группы стоки первого и второго р-МДП- и первого n-МДП-транзисторов соединены и являются выходом элемента, исток второго МДП-транзистора р-типа подключен к стоку третьего р-МДП-транзистора, исток которого соединен со стоками четвертого и пятого р-МДП-транзисторов, истоки которых вместе с истоком первого р-МДП-транзистора подключены к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоками второго, третьего и четвертого n-МДП-транзисторов, исток четвертого n-МДП-транзистора подключен к стоку пятого МДП-транзистора n-типа, исток которого вместе с истоками второго и третьего n-МДП-транзисторов подключен к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса четвертой группы стоки первого и второго р-МДП- и первого n-МДП-транзисторов соединены и являются выходом элемента, исток второго МДП-транзистора р-типа подключен к стоку третьего р-МДП-транзистора, исток которого соединен со стоками четвертого и пятого р-МДП-транзисторов, истоки которых вместе с истоком первого р-МДП-транзистора подключены к шине положительного напряжения питания, исток первого МДП-транзистора n-типа соединен со стоками второго, третьего и четвертого n-МДП-транзисторов, исток четвертого n-МДП-транзистора подключен к стоку пятого МДП-транзистора n-типа, исток которого вместе с истоками второго и третьего n-МДП-транзисторов подключен к шине отрицательного напряжения питания.

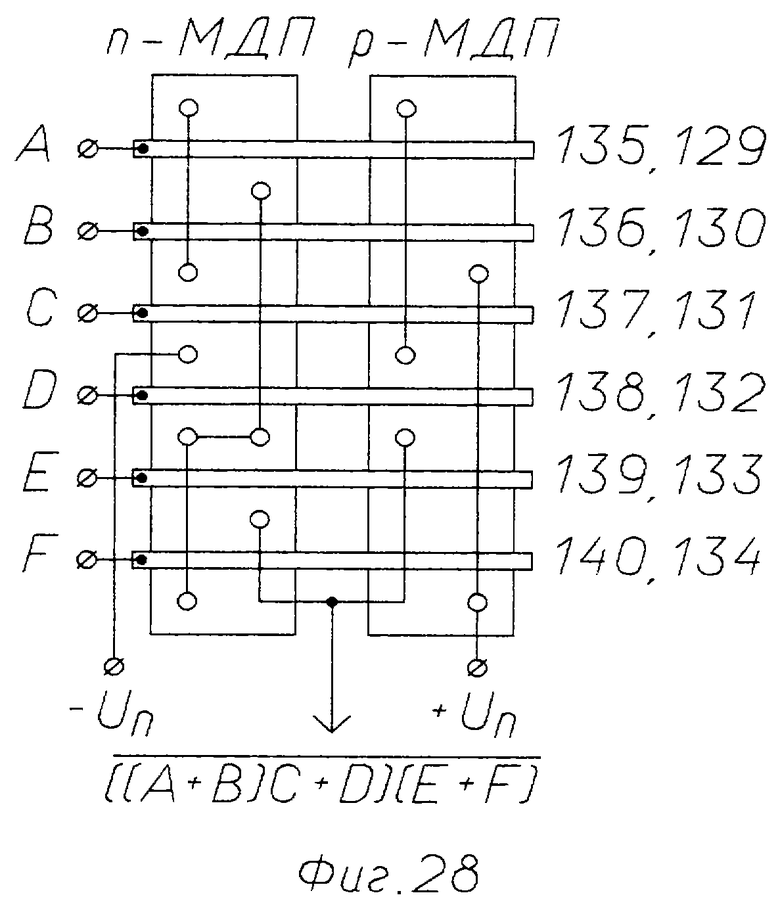

Восьмой элемент  каждого сумматора третьей и четвертой групп содержит по шесть МДП-транзисторов р- и n-типа, затворы которых по порядку подключены к первому-шестому входам (A, B, C, D, E, F соответственно), стоки четвертого и пятого МДП-транзисторов р-типа и стоки пятого и шестого МДП-транзисторов n-типа соединены и являются выходом элемента, исток четвертого р-МДП-транзистора соединен со стоками первого и третьего МДП-транзисторов р-типа, истоки первого и пятого р-МДП-транзисторов соответственно соединены со стоками второго и шестого МДП-транзисторов р-типа, истоки которых вместе с истоком третьего р-МДП-транзистора подключены к шине положительного напряжения питания, истоки пятого и шестого МДП-транзисторов n-типа соединены со стоками первого, второго и четвертого n-МДП-транзисторов, истоки первого и второго МДП-транзисторов n-типа соединены со стоком третьего n-МДП-транзистора, исток которого вместе с истоком четвертого МДП-транзистора n-типа подключен к шине отрицательного напряжения питания.

каждого сумматора третьей и четвертой групп содержит по шесть МДП-транзисторов р- и n-типа, затворы которых по порядку подключены к первому-шестому входам (A, B, C, D, E, F соответственно), стоки четвертого и пятого МДП-транзисторов р-типа и стоки пятого и шестого МДП-транзисторов n-типа соединены и являются выходом элемента, исток четвертого р-МДП-транзистора соединен со стоками первого и третьего МДП-транзисторов р-типа, истоки первого и пятого р-МДП-транзисторов соответственно соединены со стоками второго и шестого МДП-транзисторов р-типа, истоки которых вместе с истоком третьего р-МДП-транзистора подключены к шине положительного напряжения питания, истоки пятого и шестого МДП-транзисторов n-типа соединены со стоками первого, второго и четвертого n-МДП-транзисторов, истоки первого и второго МДП-транзисторов n-типа соединены со стоком третьего n-МДП-транзистора, исток которого вместе с истоком четвертого МДП-транзистора n-типа подключен к шине отрицательного напряжения питания.

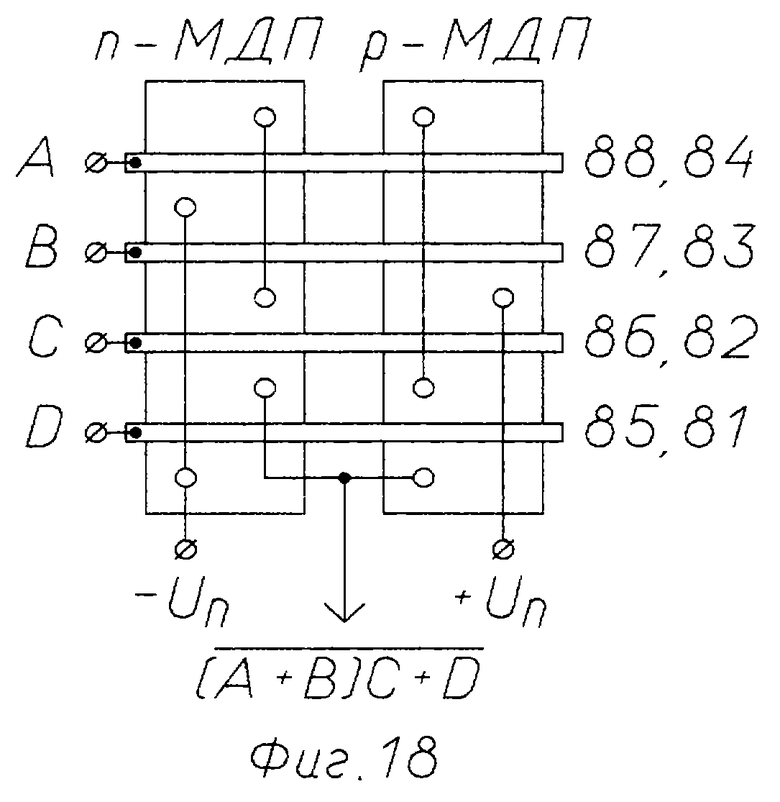

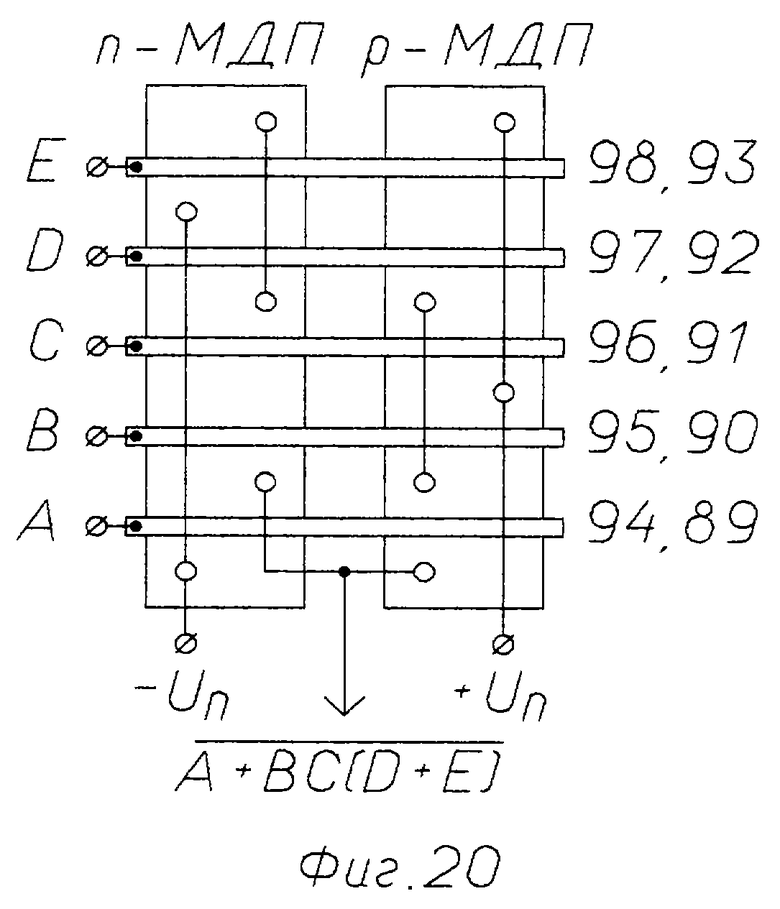

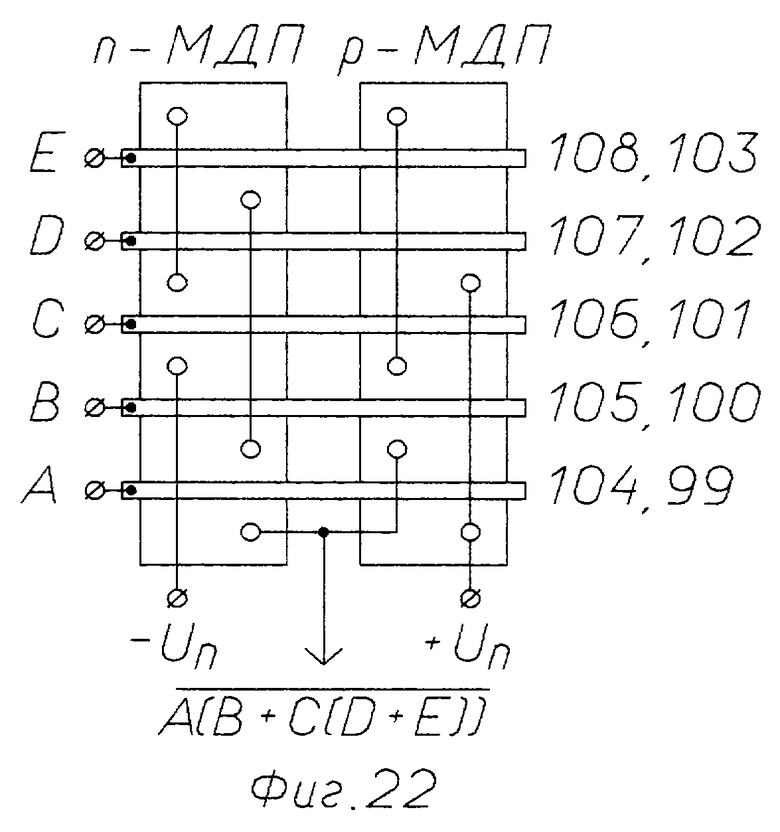

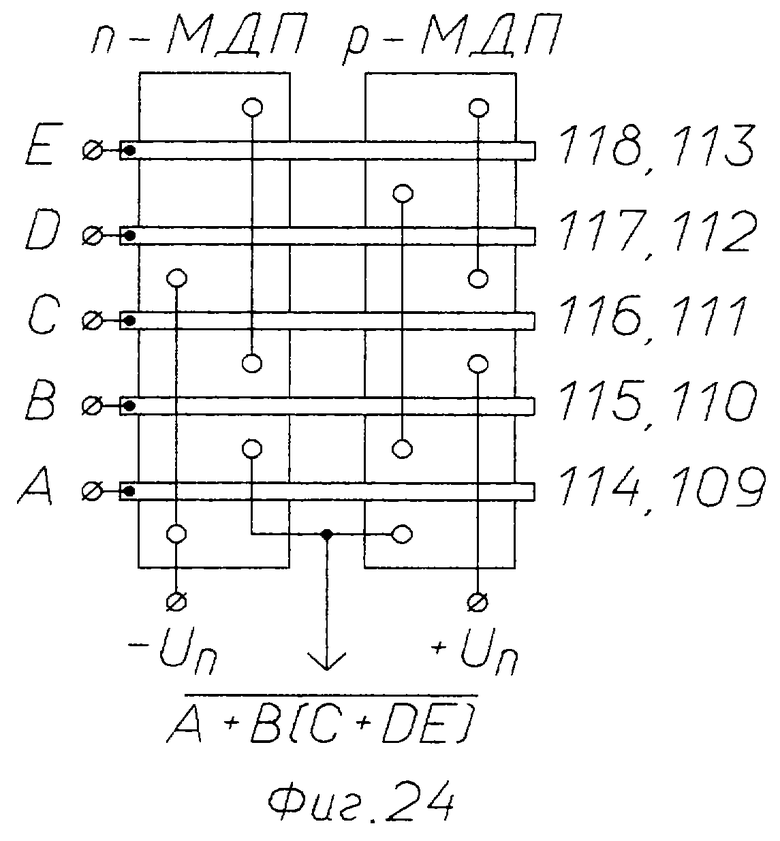

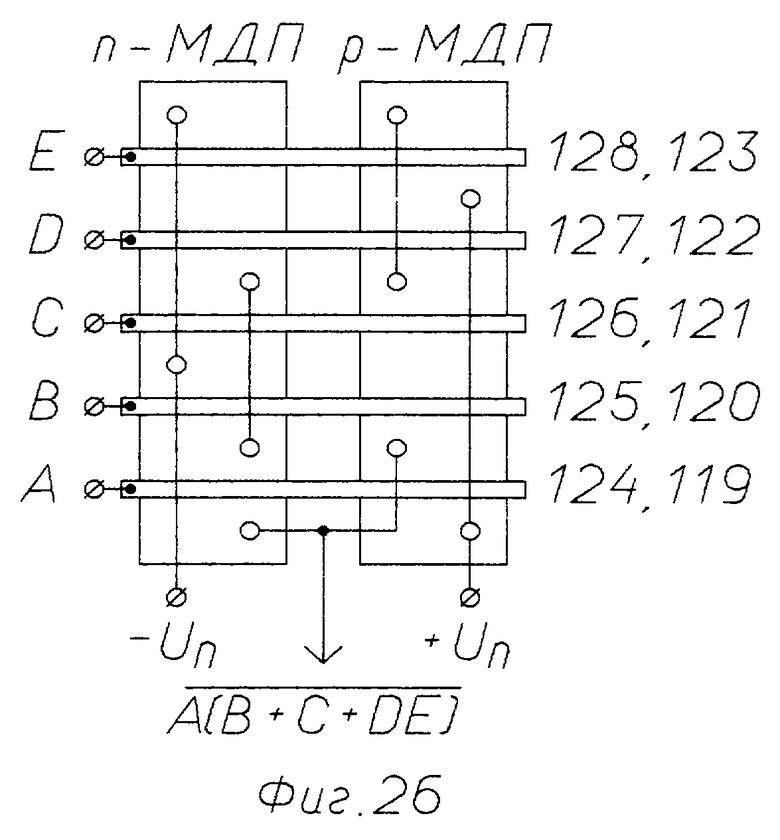

Конструктивно каждый элемент устройства сложения с ускоренным переносом выполнен в виде двух смежных продольными сторонами областей МДП-структур р- и n-типов проводимости, пересеченных поперек общими полосками затворов, разделяющими МДП-структуры на области истоков-стоков соответствующих типов проводимости, в конструкциях третьих элементов  сумматоров второй и четвертой групп содержится по четыре полоски затворов, соединенных по порядку с первыми-четвертыми входами элементов, в конструкции седьмого элемента

сумматоров второй и четвертой групп содержится по четыре полоски затворов, соединенных по порядку с первыми-четвертыми входами элементов, в конструкции седьмого элемента  сумматоров третьей и четвертой групп содержится четыре полоски затворов, соединенных в обратном порядке с первым-четвертым входами элемента.

сумматоров третьей и четвертой групп содержится четыре полоски затворов, соединенных в обратном порядке с первым-четвертым входами элемента.

У третьего элемента  каждого сумматора-формирователя сигнала возникновения переноса второй группы и у седьмого элемента

каждого сумматора-формирователя сигнала возникновения переноса второй группы и у седьмого элемента  каждого сумматора третьей и четвертой групп крайняя со стороны первой полоски затворов область истока-стока р-типа и n-область истока-стока между первой и второй полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а р-область истока-стока между второй и третьей полосками затворов подключена к шине положительного напряжения питания, области истоков-стоков n-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а n-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине отрицательного напряжения питания.

каждого сумматора третьей и четвертой групп крайняя со стороны первой полоски затворов область истока-стока р-типа и n-область истока-стока между первой и второй полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а р-область истока-стока между второй и третьей полосками затворов подключена к шине положительного напряжения питания, области истоков-стоков n-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а n-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине отрицательного напряжения питания.

У третьего элемента  каждого сумматора-формирователя сигнала распространения переноса второй группы крайние со стороны первой полоски затворов области истоков-стоков р- и n-типов и р-область истока-стока между второй и третьей полосками затворов соединены с выходом элемента, а области истоков-стоков р-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а n-область истока-стока между третьей и четвертой полосками затворов подключена к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса второй группы крайние со стороны первой полоски затворов области истоков-стоков р- и n-типов и р-область истока-стока между второй и третьей полосками затворов соединены с выходом элемента, а области истоков-стоков р-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а n-область истока-стока между третьей и четвертой полосками затворов подключена к шине отрицательного напряжения питания.

У третьего элемента  каждого сумматора-формирователя сигнала возникновения переноса четвертой группы крайние со стороны первой полоски затворов области истоков-стоков р- и n-типов и n-область истока-стока между второй и третьей полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а р-область истока-стока между третьей и четвертой полосками затворов подключена к шине положительного напряжения питания, области истоков-стоков n-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов подключены к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала возникновения переноса четвертой группы крайние со стороны первой полоски затворов области истоков-стоков р- и n-типов и n-область истока-стока между второй и третьей полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а р-область истока-стока между третьей и четвертой полосками затворов подключена к шине положительного напряжения питания, области истоков-стоков n-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов подключены к шине отрицательного напряжения питания.

У третьего элемента  каждого сумматора-формирователя сигнала распространения переноса четвертой группы область истока-стока р-типа между первой и второй полосками затворов и крайняя со стороны первой полоски затворов n-область истока-стока соединены с выходом элемента, области истоков-стоков р-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов соединены, n-область истока-стока между второй и третьей полосками затворов подключена к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса четвертой группы область истока-стока р-типа между первой и второй полосками затворов и крайняя со стороны первой полоски затворов n-область истока-стока соединены с выходом элемента, области истоков-стоков р-типа между второй и третьей полосками затворов и крайняя со стороны четвертой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между первой и второй полосками затворов и крайняя со стороны четвертой полоски затворов соединены, n-область истока-стока между второй и третьей полосками затворов подключена к шине отрицательного напряжения питания.

В конструкциях четвертых элементов  сумматоров второй и четвертой групп содержится по пять полосок затворов, соединенных по порядку с первыми - пятыми входами элементов, у четвертого элемента

сумматоров второй и четвертой групп содержится по пять полосок затворов, соединенных по порядку с первыми - пятыми входами элементов, у четвертого элемента  каждого сумматора-формирователя сигнала возникновения переноса второй группы крайняя со стороны первой полоски затворов область истока-стока р-типа и n-область истока-стока между первой и второй полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между первой и второй и между третьей и четвертой полосками затворов соединены, а р-области истоков-стоков между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов соединены, а n-области истоков-стоков, крайняя со стороны первой полоски затворов и между четвертой и пятой полосками затворов подключены к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала возникновения переноса второй группы крайняя со стороны первой полоски затворов область истока-стока р-типа и n-область истока-стока между первой и второй полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между первой и второй и между третьей и четвертой полосками затворов соединены, а р-области истоков-стоков между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов соединены, а n-области истоков-стоков, крайняя со стороны первой полоски затворов и между четвертой и пятой полосками затворов подключены к шине отрицательного напряжения питания.

У четвертого элемента  каждого сумматора-формирователя сигнала распространения переноса второй группы область истока-стока р-типа между первой и второй полосками затворов и крайняя со стороны первой полоски затворов n-область истока-стока соединены с выходом элемента, области истоков-стоков р-типа между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между первой и второй и между четвертой и пятой полосками затворов соединены, также соединены n-области истоков-стоков между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов, а n-область истока-стока между второй и третьей полосками затворов подключена к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса второй группы область истока-стока р-типа между первой и второй полосками затворов и крайняя со стороны первой полоски затворов n-область истока-стока соединены с выходом элемента, области истоков-стоков р-типа между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа между первой и второй и между четвертой и пятой полосками затворов соединены, также соединены n-области истоков-стоков между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов, а n-область истока-стока между второй и третьей полосками затворов подключена к шине отрицательного напряжения питания.

У четвертого элемента  каждого сумматора-формирователя сигнала возникновения переноса четвертой группы крайняя со стороны первой полоски затворов р-область истока-стока и область истока-стока n-типа между первой и второй полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между первой и второй и между четвертой и пятой полосками затворов соединены, также соединены р-области истоков-стоков между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов, р-область истока-стока между второй и третьей полосками затворов подключена к шине положительного напряжения питания, области истоков-стоков n-типа между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала возникновения переноса четвертой группы крайняя со стороны первой полоски затворов р-область истока-стока и область истока-стока n-типа между первой и второй полосками затворов соединены с выходом элемента, области истоков-стоков р-типа между первой и второй и между четвертой и пятой полосками затворов соединены, также соединены р-области истоков-стоков между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов, р-область истока-стока между второй и третьей полосками затворов подключена к шине положительного напряжения питания, области истоков-стоков n-типа между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов подключены к шине отрицательного напряжения питания.

У четвертого элемента  каждого сумматора-формирователя сигнала распространения переноса четвертой группы р-область истока-стока между первой и второй полосками затворов и крайняя со стороны первой полоски затвора область истока-стока n-типа соединены с выходом элемента, области истоков-стоков р-типа между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между четвертой и пятой полосками затворов подключены к шине положительного напряжения питания, n-области истоков-стоков между первой и второй и между третьей и четвертой полосками затворов соединены, а n-области истока-стока между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов подключены к шине отрицательного напряжения питания.

каждого сумматора-формирователя сигнала распространения переноса четвертой группы р-область истока-стока между первой и второй полосками затворов и крайняя со стороны первой полоски затвора область истока-стока n-типа соединены с выходом элемента, области истоков-стоков р-типа между третьей и четвертой полосками затворов и крайняя со стороны пятой полоски затворов соединены, а р-области истоков-стоков, крайняя со стороны первой полоски затворов и между четвертой и пятой полосками затворов подключены к шине положительного напряжения питания, n-области истоков-стоков между первой и второй и между третьей и четвертой полосками затворов соединены, а n-области истока-стока между второй и третьей полосками затворов и крайняя со стороны пятой полоски затворов подключены к шине отрицательного напряжения питания.

В конструкции восьмого элемента  каждого сумматора третьей и четвертой групп содержится шесть полосок затворов, соединенных по порядку с первым-шестым входами элемента, область истока-стока р-типа между четвертой и пятой полосками затворов и n-область истока-стока между пятой и шестой полосками затворов соединены с выходом элемента, области истоков-стоков р-типа, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов соединены, а р-области истоков-стоков между второй и третьей полосками затворов и крайняя со стороны шестой полоски затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа, крайняя со стороны первой полоски затворов и между второй и третьей полосками затворов соединены, также соединены n-области истоков-стоков между первой и второй полосками затворов, между четвертой и пятой полосками затворов и крайняя со стороны шестой полоски затворов, n-область истока-стока между третьей и четвертой полосками затворов подключена к шине отрицательного напряжения питания.

каждого сумматора третьей и четвертой групп содержится шесть полосок затворов, соединенных по порядку с первым-шестым входами элемента, область истока-стока р-типа между четвертой и пятой полосками затворов и n-область истока-стока между пятой и шестой полосками затворов соединены с выходом элемента, области истоков-стоков р-типа, крайняя со стороны первой полоски затворов и между третьей и четвертой полосками затворов соединены, а р-области истоков-стоков между второй и третьей полосками затворов и крайняя со стороны шестой полоски затворов подключены к шине положительного напряжения питания, области истоков-стоков n-типа, крайняя со стороны первой полоски затворов и между второй и третьей полосками затворов соединены, также соединены n-области истоков-стоков между первой и второй полосками затворов, между четвертой и пятой полосками затворов и крайняя со стороны шестой полоски затворов, n-область истока-стока между третьей и четвертой полосками затворов подключена к шине отрицательного напряжения питания.

Таким образом, отличительными признаками изобретения является наличие дополнительных элементов, их связи, схемотехническое и конструктивное выполнение элементов.

Указанное выполнение устройства сложения с ускоренным переносом позволяет формировать разряды суммы, используя сигналы переноса и распространения переноса, вырабатываемые для разных групп разрядов суммируемых чисел с помощью более простых схем, обладающих меньшей задержкой, и выровнять задержки в цепях.

Проведенные патентные исследования подтвердили новизну изобретения, а также показали, что в литературе отсутствуют данные, указывающие на влияние отличий патентуемого изобретения на достижение технического результата. Поэтому следует считать, что патентуемое изобретение соответствует критериям новизны и изобретательского уровня.

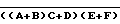

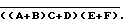

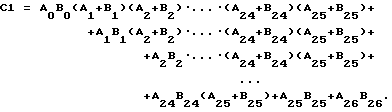

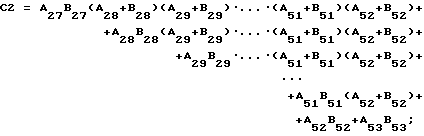

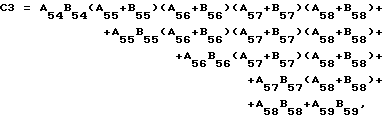

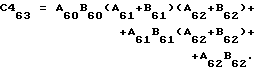

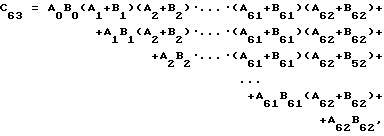

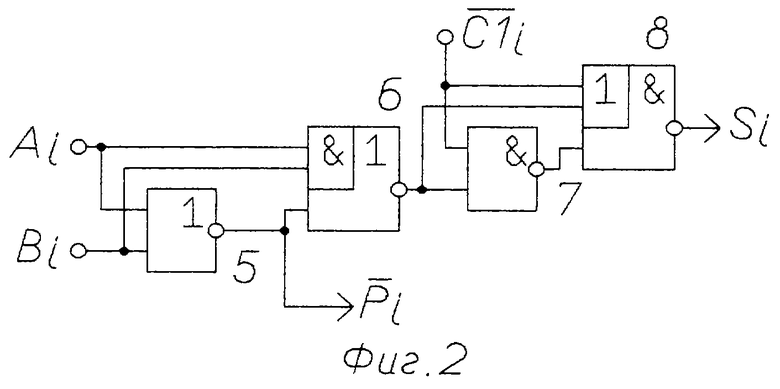

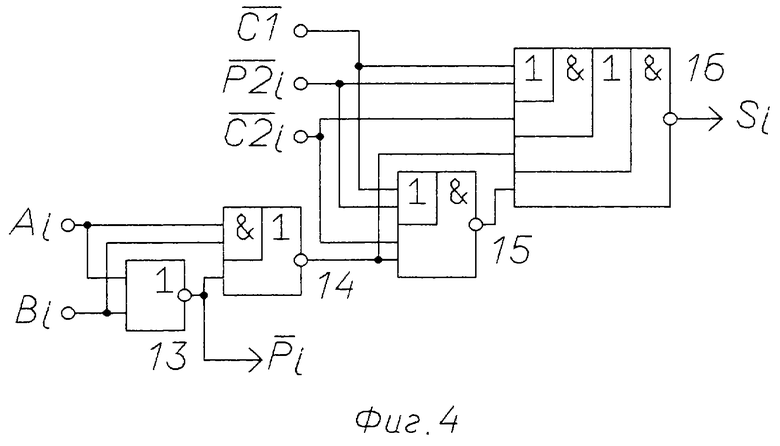

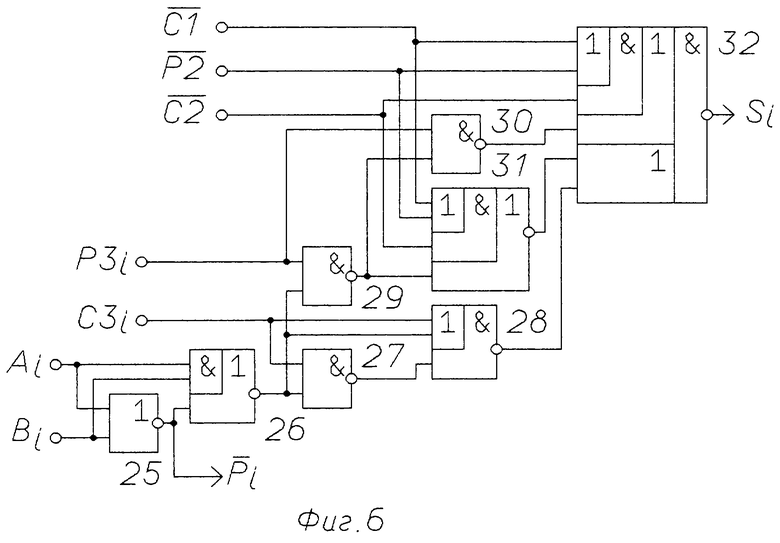

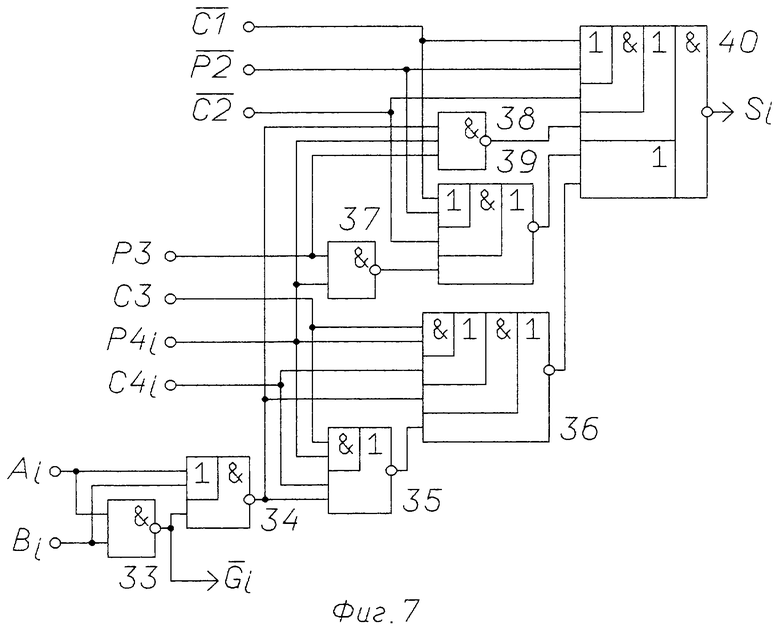

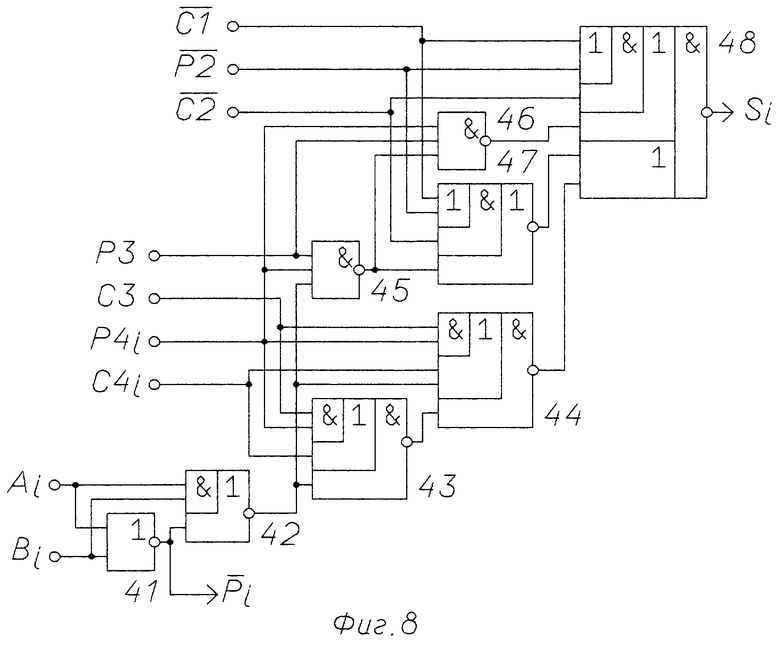

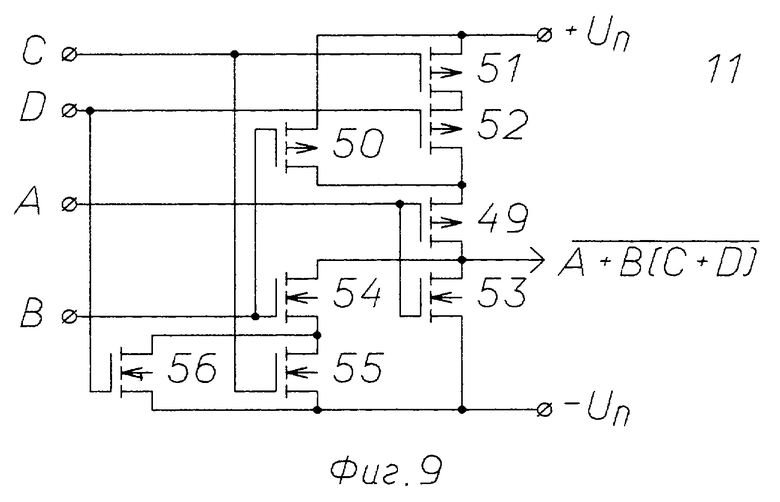

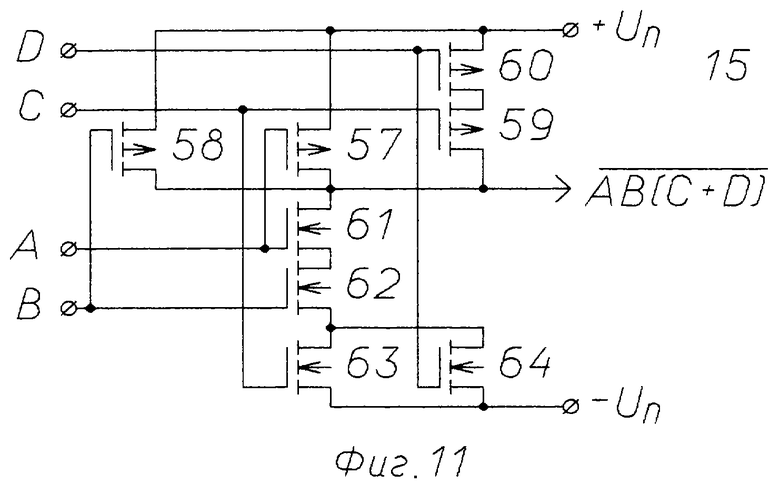

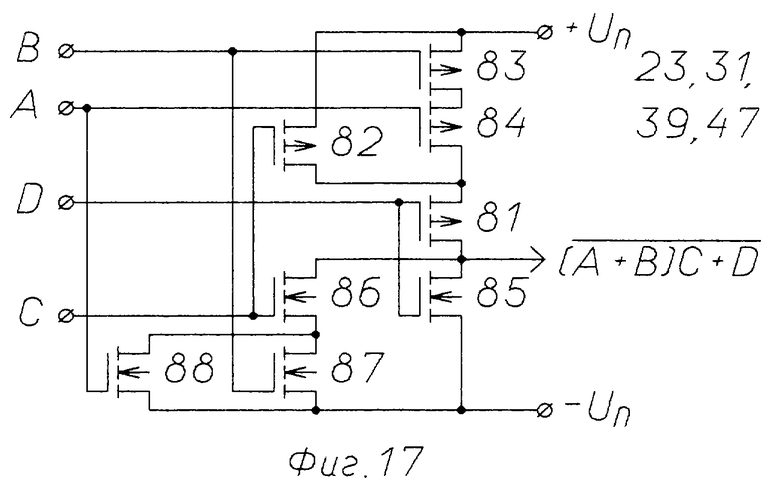

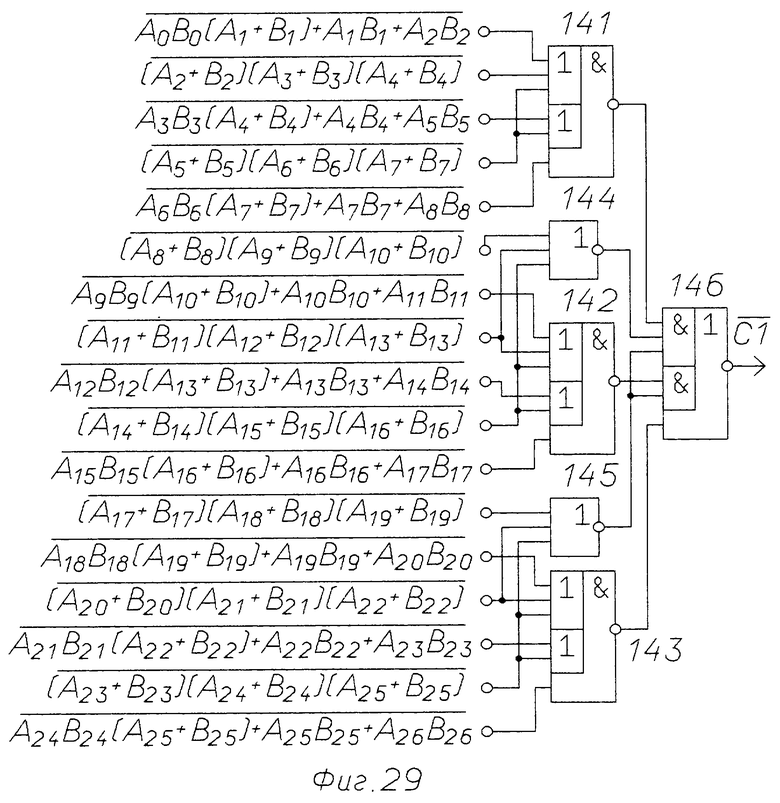

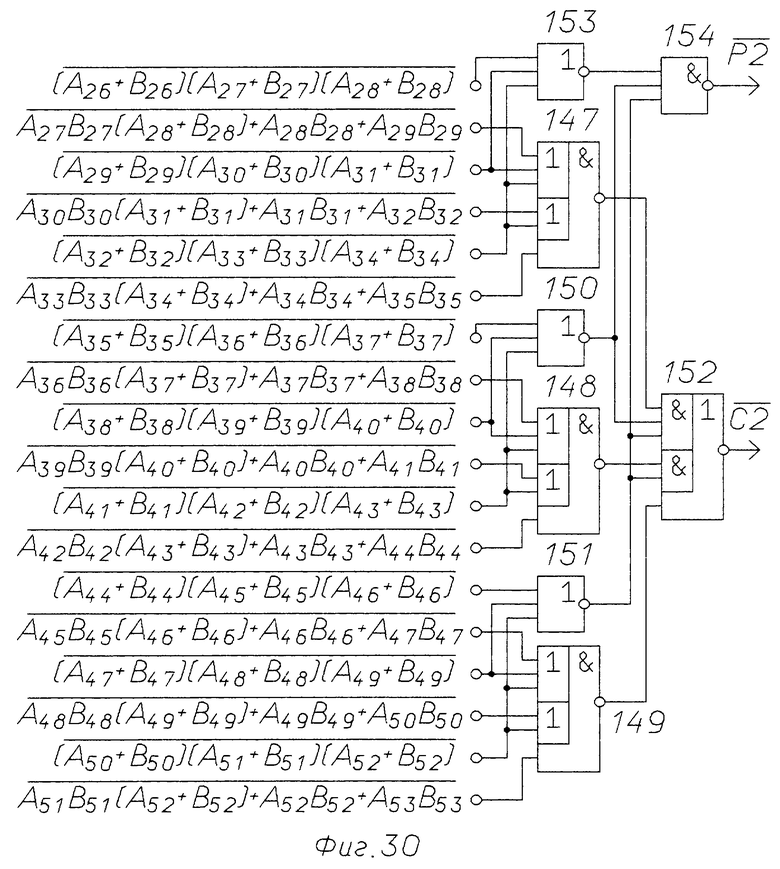

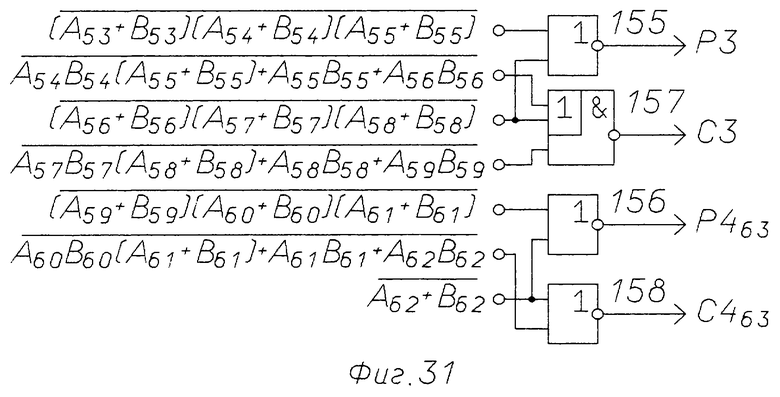

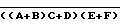

Изобретение поясняется чертежами, на которых изображены схемы составных частей устройства сложения с ускоренным переносом - сумматоров-формирователей сигналов возникновения переноса с первой по четвертую групп на фиг.1, фиг. 3, фиг. 5 и фиг.7 соответственно и сумматоров-формирователей сигналов распространения переноса с первой по четвертую групп - фиг.2, фиг.4, фиг.6 и фиг. 8 соответственно. Схемы сумматоров первой группы повторяют схемы сумматоров ближайшего аналога изобретения. Принципиальные схемы новых элементов устройства и схемы их конструктивного выполнения представляют фиг.9 - фиг. 28. На фиг.29 - фиг.31 изображен вариант выполнения схем переноса для 64-разрядного устройства сложения с ускоренным переносом.

Устройство содержит с первой по четвертую группы сумматоров, имеющих две разновидности: сумматор-формирователь сигнала возникновения переноса и сумматор-формирователь сигнала распространения переноса.

Каждый сумматор-формирователь сигнала возникновения переноса первой группы (Фиг. 1) состоит из первого элемента 1 2И-НЕ, второго элемента 2, выполняющего функцию вида  третьего элемента 3 2ИЛИ-НЕ и четвертого элемента 4 -

третьего элемента 3 2ИЛИ-НЕ и четвертого элемента 4 -  Входы первого элемента 1 соответственно соединены с первым и вторым входами второго элемента 2 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 1 является выходом

Входы первого элемента 1 соответственно соединены с первым и вторым входами второго элемента 2 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 1 является выходом  инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 2. Выход третьего элемента 3 соединен с первыми входом четвертого элемента 4, второй вход которого вместе с первым входом третьего элемента 3 подключен к выходу второго элемента 2. Второй вход третьего элемента 3 и третий вход четвертого элемента 4 соединены и подключены к соответствующему входу

инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 2. Выход третьего элемента 3 соединен с первыми входом четвертого элемента 4, второй вход которого вместе с первым входом третьего элемента 3 подключен к выходу второго элемента 2. Второй вход третьего элемента 3 и третий вход четвертого элемента 4 соединены и подключены к соответствующему входу  инверсии сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 4 является выходом Si соответствующего разряда суммы.

инверсии сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 4 является выходом Si соответствующего разряда суммы.

Каждый сумматор-формирователь сигнала распространения переноса первой группы (Фиг. 2) состоит из первого элемента 5 2ИЛИ-НЕ, второго элемента 6, выполняющего функцию вида  третьего элемента 7 2И-НЕ и четвертого элемента 8 -

третьего элемента 7 2И-НЕ и четвертого элемента 8 -  . Входы первого элемента 5 соответственно соединены с первым и вторым входами второго элемента 6 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 5 является выходом

. Входы первого элемента 5 соответственно соединены с первым и вторым входами второго элемента 6 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 5 является выходом  инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 6. Выход третьего элемента 7 соединен с первым входом четвертого элемента 8, второй вход которого вместе с первым входом третьего элемента 7 подключен к выходу второго элемента 6. Второй вход третьего элемента 7 и третий вход четвертого элемента 8 соединены и подключены к соответствующему входу

инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 6. Выход третьего элемента 7 соединен с первым входом четвертого элемента 8, второй вход которого вместе с первым входом третьего элемента 7 подключен к выходу второго элемента 6. Второй вход третьего элемента 7 и третий вход четвертого элемента 8 соединены и подключены к соответствующему входу  инверсии сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 8 является выходом Si соответствующего разряда суммы.

инверсии сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 8 является выходом Si соответствующего разряда суммы.

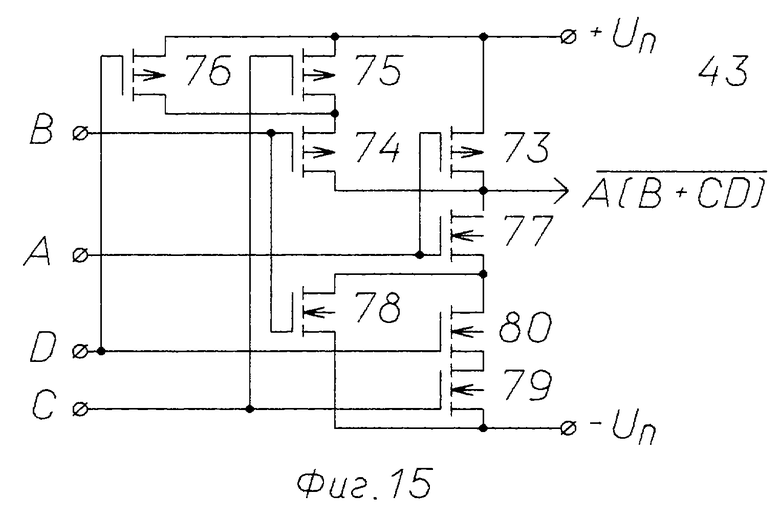

Каждый сумматор-формирователь сигнала возникновения переноса второй группы (Фиг. 3) состоит из первого элемента 9 2И-НЕ, второго элемента 10, выполняющего функцию вида  третьего элемента 11 -

третьего элемента 11 -  и четвертого элемента 12 -

и четвертого элемента 12 -  Входы первого элемента 9 соответственно соединены с первым и вторым входами второго элемента 10 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 9 является выходом

Входы первого элемента 9 соответственно соединены с первым и вторым входами второго элемента 10 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 9 является выходом  инверсии соответствующего сигнала возникновения переноса

инверсии соответствующего сигнала возникновения переноса

и подключен к третьему входу второго элемента 10. Выход третьего элемента 11 соединен с первым входом четвертого элемента 12, второй вход которого вместе с первым входом третьего элемента 11 подключен к выходу второго элемента 10. Второй, третий и четвертый входы третьего элемента 11 соответственно соединены с третьим, четвертым и пятым входами четвертого элемента 12 и подключены к соответствующим входам  инверсий сигналов переноса и распространения переноса, относящихся ко второй группе разрядов суммируемых чисел, и ко входу

инверсий сигналов переноса и распространения переноса, относящихся ко второй группе разрядов суммируемых чисел, и ко входу  инверсии старшего сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 12 является выходом Si соответствующего разряда суммы.

инверсии старшего сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 12 является выходом Si соответствующего разряда суммы.

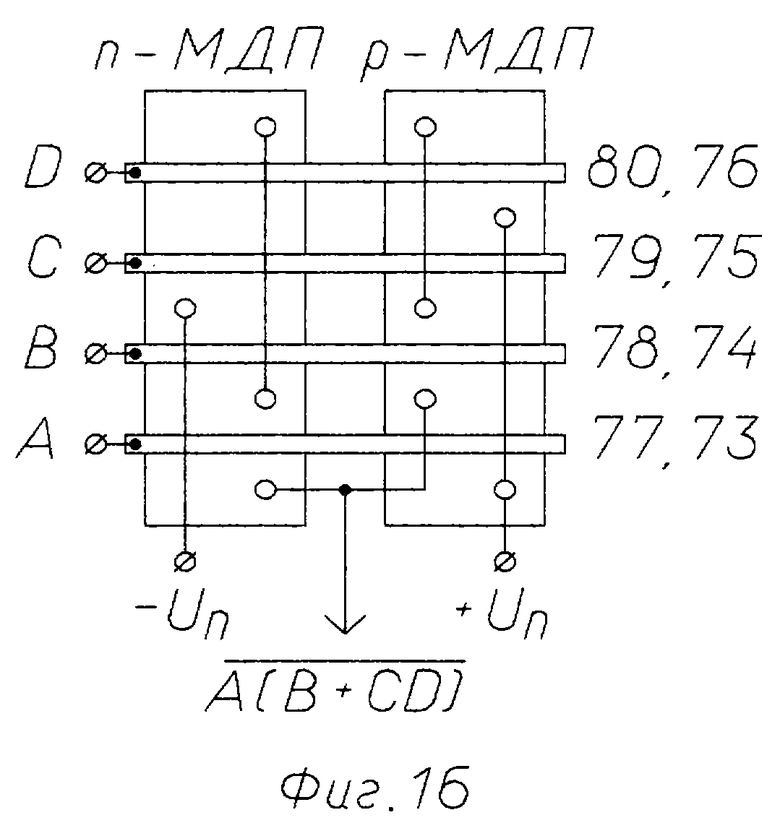

Каждый сумматор-формирователь сигнала распространения переноса второй группы (Фиг.4) состоит из первого элемента 13 2ИЛИ-НЕ, второго элемента 14, выполняющего функцию вида  , третьего элемента 15 -

, третьего элемента 15 -  и четвертого элемента 16 -

и четвертого элемента 16 -  Входы первого элемента 13 соответственно соединены с первым и вторым входами второго элемента 14 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 13 является выходом

Входы первого элемента 13 соответственно соединены с первым и вторым входами второго элемента 14 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 13 является выходом  инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 14. Выход третьего элемента 15 соединен с первым входом четвертого элемента 16, второй вход которого и первый вход третьего элемента 15 подключены к выходу второго элемента 14. Второй, третий и четвертый входы третьего элемента 15 соответственно соединены с третьим, четвертым и пятым входами четвертого элемента 16 и подключены к соответствующим входам

инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 14. Выход третьего элемента 15 соединен с первым входом четвертого элемента 16, второй вход которого и первый вход третьего элемента 15 подключены к выходу второго элемента 14. Второй, третий и четвертый входы третьего элемента 15 соответственно соединены с третьим, четвертым и пятым входами четвертого элемента 16 и подключены к соответствующим входам  инверсий сигналов переноса и распространения переноса, относящихся ко второй группе разрядов суммируемых чисел, и ко входу

инверсий сигналов переноса и распространения переноса, относящихся ко второй группе разрядов суммируемых чисел, и ко входу  инверсии старшего сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 16 является выходом Si соответствующего разряда суммы.

инверсии старшего сигнала переноса из первой группы разрядов суммируемых чисел. Выход четвертого элемента 16 является выходом Si соответствующего разряда суммы.

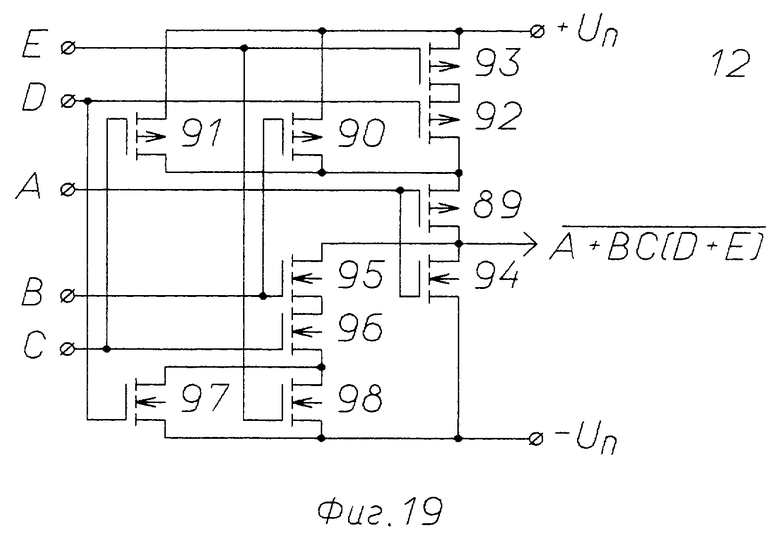

Каждый сумматор-формирователь сигнала возникновения переноса третьей группы (Фиг. 5) состоит из первого элемента 17 2И-НЕ, второго элемента 18, выполняющего функцию вида  третьего элемента 19 2ИЛИ-НЕ, четвертого элемента 20 -

третьего элемента 19 2ИЛИ-НЕ, четвертого элемента 20 -  пятого элемента-инвертора 21, шестого элемента 22 2И-НЕ, седьмого элемента 23 -

пятого элемента-инвертора 21, шестого элемента 22 2И-НЕ, седьмого элемента 23 -  и восьмого элемента 24 -

и восьмого элемента 24 -  Входы первого элемента 17 соответственно соединены с первым и вторым входами второго элемента 18 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 17 является выходом

Входы первого элемента 17 соответственно соединены с первым и вторым входами второго элемента 18 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 17 является выходом  инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 18. Выход третьего элемента 19 соединен с первым входом четвертого элемента 20, второй вход которого вместе с первыми входами третьего элемента 19 и шестого элемента 22 подключены к выходу второго элемента 18. Второй вход третьего элемента 19 и третий вход четвертого элемента 20 соединены и подключены к соответствующему входу С3i сигнала переноса из третьей группы разрядов суммируемых чисел. Вход пятого элемента 21 вместе со вторым входом шестого элемента 22 подключен к соответствующему входу Р3i сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 23 и 24 соответственно соединены и подключены ко входам

инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 18. Выход третьего элемента 19 соединен с первым входом четвертого элемента 20, второй вход которого вместе с первыми входами третьего элемента 19 и шестого элемента 22 подключены к выходу второго элемента 18. Второй вход третьего элемента 19 и третий вход четвертого элемента 20 соединены и подключены к соответствующему входу С3i сигнала переноса из третьей группы разрядов суммируемых чисел. Вход пятого элемента 21 вместе со вторым входом шестого элемента 22 подключен к соответствующему входу Р3i сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 23 и 24 соответственно соединены и подключены ко входам  инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 23 соединен с выходом пятого элемента 21. Четвертый, пятый и шестой входы восьмого элемента 24 подключены к выходам шестого, седьмого и четвертого элементов 22, 23 и 20 соответственно. Выход восьмого элемента 24 является выходом Si соответствующего разряда суммы.

инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 23 соединен с выходом пятого элемента 21. Четвертый, пятый и шестой входы восьмого элемента 24 подключены к выходам шестого, седьмого и четвертого элементов 22, 23 и 20 соответственно. Выход восьмого элемента 24 является выходом Si соответствующего разряда суммы.

Каждый сумматор-формирователь сигнала распространения переноса третьей группы (Фиг.6) состоит из первого элемента 25 2ИЛИ-НЕ, второго элемента 26, выполняющего функцию вида  третьего элемента 27 2И-НЕ, четвертого элемента 28 -

третьего элемента 27 2И-НЕ, четвертого элемента 28 -  пятого и шестого элементов 29 и 30 2И-НЕ, седьмого элемента 31 -

пятого и шестого элементов 29 и 30 2И-НЕ, седьмого элемента 31 -  и восьмого элемента 32 -

и восьмого элемента 32 -  Входы первого элемента 25 соответственно соединены с первым и вторым входами второго элемента 26 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 25 является выходом

Входы первого элемента 25 соответственно соединены с первым и вторым входами второго элемента 26 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 25 является выходом  инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 26. Выход третьего элемента 27 соединен с первым входом четвертого элемента 28, второй вход которого вместе с первыми входами третьего и пятого элементов 27 и 29 подключен к выходу второго элемента 26. Второй вход третьего элемента 27 и третий вход четвертого элемента 28 соединены и подключены к соответствующему входу С3i сигнала переноса из третьей группы разрядов суммируемых чисел. Второй вход пятого элемента 29 вместе с первым входом шестого элемента 30 подключен к соответствующему входу Р3i сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 31 и 32 соответственно соединены и подключены ко входам

инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 26. Выход третьего элемента 27 соединен с первым входом четвертого элемента 28, второй вход которого вместе с первыми входами третьего и пятого элементов 27 и 29 подключен к выходу второго элемента 26. Второй вход третьего элемента 27 и третий вход четвертого элемента 28 соединены и подключены к соответствующему входу С3i сигнала переноса из третьей группы разрядов суммируемых чисел. Второй вход пятого элемента 29 вместе с первым входом шестого элемента 30 подключен к соответствующему входу Р3i сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 31 и 32 соответственно соединены и подключены ко входам  инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 31 и второй вход шестого элемента 30 соединены с выходом пятого элемента 29. Четвертый, пятый и шестой входы восьмого элемента 32 подключены к выходам шестого, седьмого и четвертого элементов 30, 31 и 28 соответственно. Выход восьмого элемента 32 является выходом Si соответствующего разряда суммы.

инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 31 и второй вход шестого элемента 30 соединены с выходом пятого элемента 29. Четвертый, пятый и шестой входы восьмого элемента 32 подключены к выходам шестого, седьмого и четвертого элементов 30, 31 и 28 соответственно. Выход восьмого элемента 32 является выходом Si соответствующего разряда суммы.

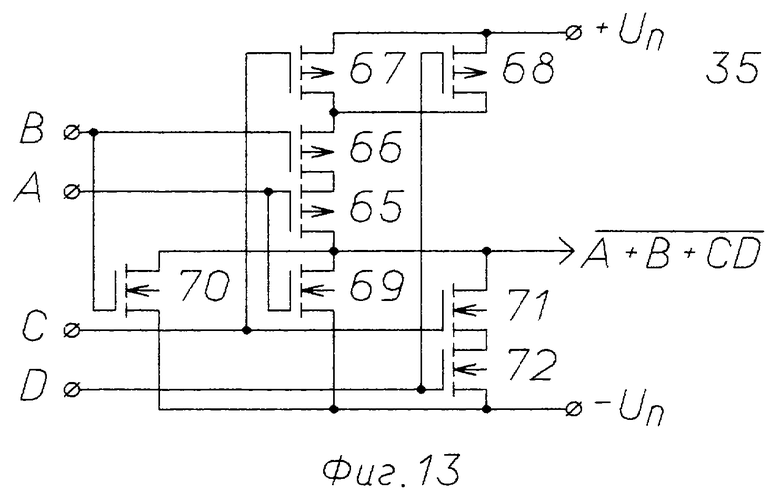

Каждый сумматор-формирователь сигнала возникновения переноса четвертой группы (Фиг. 7) состоит из первого элемента 33 2И-НЕ, второго элемента 34, выполняющего функцию вида  третьего элемента 35 -

третьего элемента 35 -  четвертого элемента 36 -

четвертого элемента 36 -  пятого элемента 37 2И-НЕ, шестого элемента 38 3И-НЕ, седьмого элемента 39 -

пятого элемента 37 2И-НЕ, шестого элемента 38 3И-НЕ, седьмого элемента 39 -  и восьмого элемента 40 -

и восьмого элемента 40 -  . Входы первого элемента 33 соответственно соединены с первым и вторым входами второго элемента 34 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 33 является выходом

. Входы первого элемента 33 соответственно соединены с первым и вторым входами второго элемента 34 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 33 является выходом  инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 34. Выход третьего элемента 35 соединен с первым входом четвертого элемента 36, второй вход которого вместе с первыми входами третьего и шестого элементов 35 и 38 подключен к выходу второго элемента 34. Второй вход третьего элемента 35 и третий вход четвертого элемента 36 соединены и подключены к соответствующему входу С4i сигнала переноса из четвертой группы разрядов суммируемых чисел. Третий вход третьего элемента 35, четвертый вход четвертого элемента 36, первый вход пятого элемента 37 и второй вход шестого элемента 38 соединены с соответствующим входом Р4i сигнала распространения переноса четвертой группой разрядов суммируемых чисел. Четвертый вход третьего элемента 35 вместе с пятым входом четвертого элемента 36 подключен ко входу С3 старшего сигнала переноса из третьей группы разрядов суммируемых чисел, а второй вход пятого элемента 37 и третий вход шестого элемента 38 соединены со входом Р3 старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 39 и 40 соответственно соединены и подключены ко входам

инверсии соответствующего сигнала возникновения переноса и подключен к третьему входу второго элемента 34. Выход третьего элемента 35 соединен с первым входом четвертого элемента 36, второй вход которого вместе с первыми входами третьего и шестого элементов 35 и 38 подключен к выходу второго элемента 34. Второй вход третьего элемента 35 и третий вход четвертого элемента 36 соединены и подключены к соответствующему входу С4i сигнала переноса из четвертой группы разрядов суммируемых чисел. Третий вход третьего элемента 35, четвертый вход четвертого элемента 36, первый вход пятого элемента 37 и второй вход шестого элемента 38 соединены с соответствующим входом Р4i сигнала распространения переноса четвертой группой разрядов суммируемых чисел. Четвертый вход третьего элемента 35 вместе с пятым входом четвертого элемента 36 подключен ко входу С3 старшего сигнала переноса из третьей группы разрядов суммируемых чисел, а второй вход пятого элемента 37 и третий вход шестого элемента 38 соединены со входом Р3 старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 39 и 40 соответственно соединены и подключены ко входам  инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 39 соединен с выходом пятого элемента 37. Четвертый, пятый и шестой входы восьмого элемента 40 подключены к выходам шестого, седьмого и четвертого элементов 38, 39 и 36 соответственно. Выход восьмого элемента 40 является выходом Si соответствующего разряда суммы.

инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 39 соединен с выходом пятого элемента 37. Четвертый, пятый и шестой входы восьмого элемента 40 подключены к выходам шестого, седьмого и четвертого элементов 38, 39 и 36 соответственно. Выход восьмого элемента 40 является выходом Si соответствующего разряда суммы.

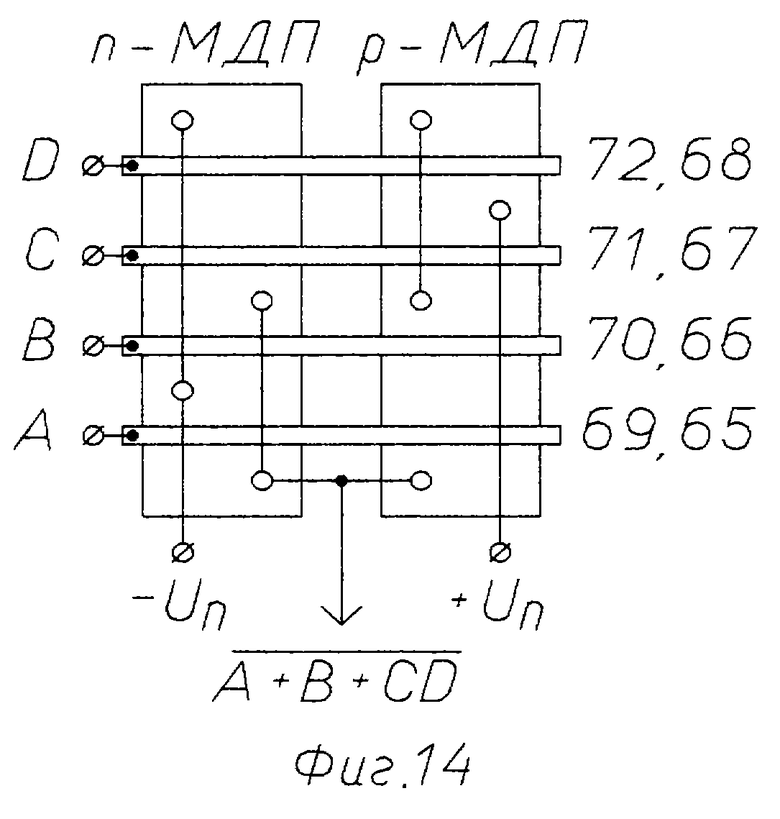

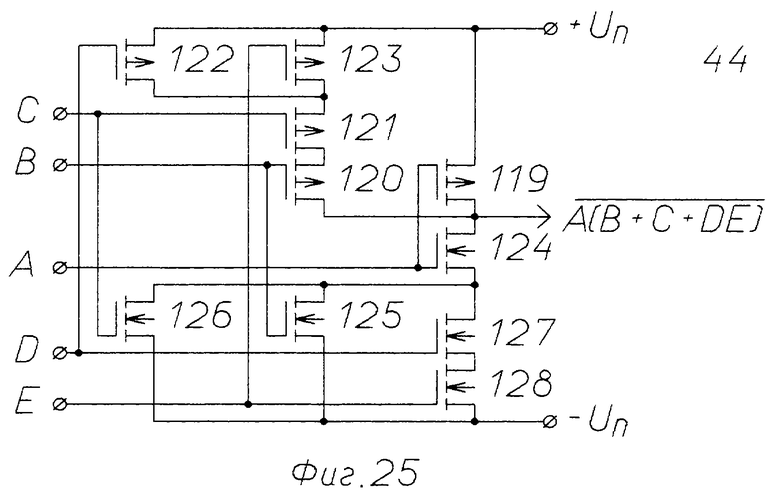

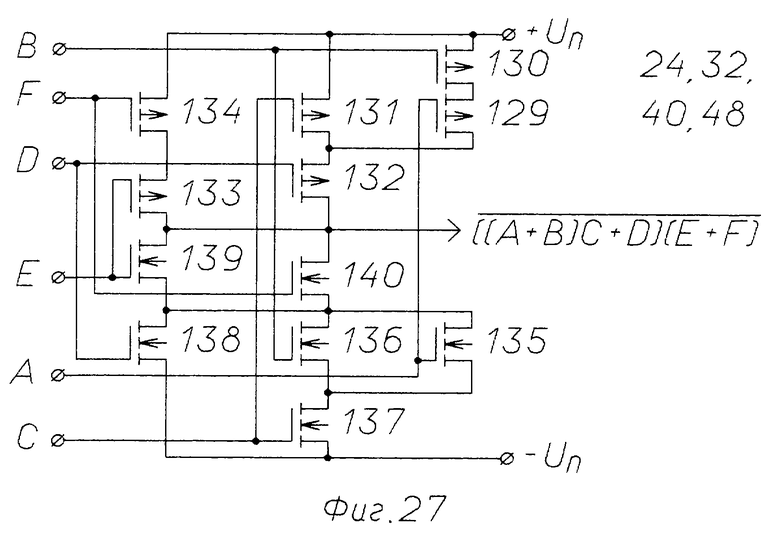

Каждый сумматор-формирователь сигнала распространения переноса четвертой группы (Фиг.8) состоит из первого элемента 41 2ИЛИ-НЕ, второго элемента 42, выполняющего функцию вида  третьего элемента 43 -

третьего элемента 43 -  четвертого элемента 44 -

четвертого элемента 44 -  пятого и шестого элементов 45 и 46 3И-НЕ, седьмого элемента 47 -

пятого и шестого элементов 45 и 46 3И-НЕ, седьмого элемента 47 -  и восьмого элемента 48 -

и восьмого элемента 48 -  Входы первого элемента 41 соответственно соединены с первым и вторым входами второго элемента 42 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 41 является выходом

Входы первого элемента 41 соответственно соединены с первым и вторым входами второго элемента 42 и подключены к соответствующим входам Аi, Вi разрядов суммируемых чисел. Выход первого элемента 41 является выходом  инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 42. Выход третьего элемента 43 соединен с первым входом четвертого элемента 44, второй вход которого вместе с первыми входами третьего и пятого элементов 43 и 45 подключен к выходу второго элемента 42. Второй вход третьего элемента 43 и третий вход четвертого элемента 44 соединены с соответствующим входом C4i сигнала переноса из четвертой группы разрядов суммируемых чисел. Третий вход третьего элемента 43, четвертый вход четвертого элемента 44, второй вход пятого элемента 45 и первый вход шестого элемента 46 соединены с соответствующим входом Р4i сигнала распространения переноса четвертой группой разрядов суммируемых чисел. Четвертый вход третьего элемента 43 вместе с пятым входом четвертого элемента 44 подключены ко входу С3 старшего сигнала переноса из третьей группы разрядов суммируемых чисел, а третий вход пятого элемента 45 и второй вход шестого элемента 46 соединены со входом Р3 старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 47 и 48 соответственно соединены и подключены ко входам

инверсии соответствующего сигнала распространения переноса и подключен к третьему входу второго элемента 42. Выход третьего элемента 43 соединен с первым входом четвертого элемента 44, второй вход которого вместе с первыми входами третьего и пятого элементов 43 и 45 подключен к выходу второго элемента 42. Второй вход третьего элемента 43 и третий вход четвертого элемента 44 соединены с соответствующим входом C4i сигнала переноса из четвертой группы разрядов суммируемых чисел. Третий вход третьего элемента 43, четвертый вход четвертого элемента 44, второй вход пятого элемента 45 и первый вход шестого элемента 46 соединены с соответствующим входом Р4i сигнала распространения переноса четвертой группой разрядов суммируемых чисел. Четвертый вход третьего элемента 43 вместе с пятым входом четвертого элемента 44 подключены ко входу С3 старшего сигнала переноса из третьей группы разрядов суммируемых чисел, а третий вход пятого элемента 45 и второй вход шестого элемента 46 соединены со входом Р3 старшего сигнала распространения переноса третьей группой разрядов суммируемых чисел. Первые, вторые и третьи входы седьмого и восьмого элементов 47 и 48 соответственно соединены и подключены ко входам  инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 47 соединен с выходом пятого элемента 45. Четвертый, пятый и шестой входы восьмого элемента 48 подключены к выходам шестого, седьмого и четвертого элементов 46, 47 и 44 соответственно. Выход восьмого элемента 48 является выходом Si соответствующего разряда суммы.

инверсий старших сигналов переноса из первой группы разрядов суммируемых чисел, распространения переноса второй группой разрядов суммируемых чисел и переноса из второй группы разрядов суммируемых чисел. Четвертый вход седьмого элемента 47 соединен с выходом пятого элемента 45. Четвертый, пятый и шестой входы восьмого элемента 48 подключены к выходам шестого, седьмого и четвертого элементов 46, 47 и 44 соответственно. Выход восьмого элемента 48 является выходом Si соответствующего разряда суммы.

Устройство работает следующим образом.

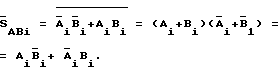

В сумматорах-формирователях сигналов возникновения переноса первой-четвертой групп элементы 1, 9, 17 и 33 2И-НЕ вырабатывают соответствующие сигналы  возникновения переноса в виде дизъюнкций пар инверсий суммируемых разрядов Аi и Вi. Конъюнкции

возникновения переноса в виде дизъюнкций пар инверсий суммируемых разрядов Аi и Вi. Конъюнкции  с дизъюнкциями повторений Аi, Вi и последующую инверсию выполняют элементы 2, 10, 18 и 34

с дизъюнкциями повторений Аi, Вi и последующую инверсию выполняют элементы 2, 10, 18 и 34  , выходными сигналами которых являются инверсии сумм SABi разрядов Аi и Вi в соответствии с формулой

, выходными сигналами которых являются инверсии сумм SABi разрядов Аi и Вi в соответствии с формулой

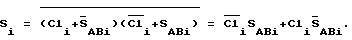

В сумматорах-формирователях сигналов распространения переноса первой-четвертой групп элементы 5, 13, 25 и 41 2ИЛИ-НЕ выполняют логическое умножение инверсий суммируемых разрядов Аi и Вi, результаты которого соответствуют сигналам  распространения переноса. Инверсии дизъюнкций выходных сигналов элементов 5, 13, 25 и 41 с конъюнкциями повторений разрядов Аi и Вi, выполняемые элементами 6, 14, 26 и 42

распространения переноса. Инверсии дизъюнкций выходных сигналов элементов 5, 13, 25 и 41 с конъюнкциями повторений разрядов Аi и Вi, выполняемые элементами 6, 14, 26 и 42  являются суммами SABi разрядов Аi и Вi согласно формуле

являются суммами SABi разрядов Аi и Вi согласно формуле

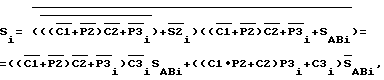

В первой группе сложение суммы SABi с переносом С1i, сигналы которых поступают с инверсией, в сумматорах-формирователях сигналов возникновения переноса выполняют элементы 3 и 4 по формуле

а в сумматорах-формирователях сигналов распространения переноса - элементы 7 и 8 в соответствии с формулой

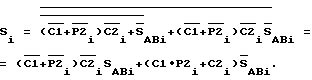

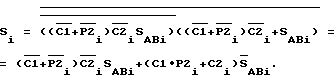

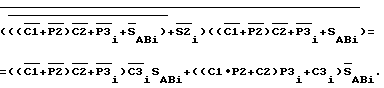

Во второй группе к суммам SABi прибавляются перенос С1 из первой группы разрядов при положительном значении соответствующих признаков Р2i распространения переносов второй группой разрядов или соответствующие переносы С2i из второй группы разрядов. В сумматорах-формирователях сигналов возникновения переноса сложение инверсии сигнала SABi с инверсиями сигналов переноса выполняют элементы 11 и 12 по формуле

В сумматорах-формирователях сигналов распространения переноса сложение повторения сигнала SABi с инверсиями сигналов переноса осуществляют элементы 15 и 16 согласно формуле

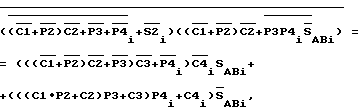

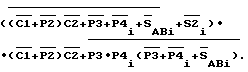

В третьей и четвертой группах сумматоров сложение выполняется в три ступени.

На второй ступени сумматоров третьей группы производится сложение соответствующих сумм SABi и поступающих в тождественном виде сигналов переноса С3i. В сумматорах-формирователях сигналов возникновения переноса вторую ступень образуют элементы 19 и 20, они работают согласно формуле

В сумматорах-формирователях сигналов распространения переноса вторая ступень выполнена на элементах 27 и 28, работу которых описывает формула